Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 120                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 144-TQFP                                                                          |

| Supplier Device Package    | 144-TQFP (16x16)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024ecm144t-i-ph |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                          |             |                |                                |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|--------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                    |

| ERXD0    | 61                     | 41              | B32             | 81                       | I           | ST             | Ethernet Receive Data 0        |

| ERXD1    | 58                     | 42              | B26             | 66                       | I           | ST             | Ethernet Receive Data 1        |

| ERXD2    | 57                     | 43              | A31             | 67                       | I           | ST             | Ethernet Receive Data 2        |

| ERXD3    | 56                     | 44              | A40             | 82                       |             | ST             | Ethernet Receive Data 3        |

| ERXERR   | 64                     | 35              | A30             | 65                       | -           | ST             | Ethernet Receive Error Input   |

| ERXDV    | 62                     | 12              | B40             | 101                      | I           | ST             | Ethernet Receive Data Valid    |

| ERXCLK   | 63                     | 16              | B12             | 27                       | I           | ST             | Ethernet Receive Clock         |

| ETXD0    | 2                      | 86              | A5              | 7                        | 0           | —              | Ethernet Transmit Data 0       |

| ETXD1    | 3                      | 85              | B4              | 8                        | 0           | —              | Ethernet Transmit Data 1       |

| ETXD2    | 43                     | 79              | B17             | 43                       | 0           | —              | Ethernet Transmit Data 2       |

| ETXD3    | 46                     | 80              | A22             | 44                       | 0           | —              | Ethernet Transmit Data 3       |

| ETXERR   | 50                     | 87              | B44             | 114                      | 0           | —              | Ethernet Transmit Error        |

| ETXEN    | 1                      | 77              | A57             | 120                      | 0           | —              | Ethernet Transmit Enable       |

| ETXCLK   | 51                     | 78              | B47             | 121                      | I           | ST             | Ethernet Transmit Clock        |

| ECOL     | 44                     | 10              | B33             | 83                       | Ι           | ST             | Ethernet Collision Detect      |

| ECRS     | 45                     | 11              | A47             | 100                      |             | ST             | Ethernet Carrier Sense         |

| EMDC     | 30                     | 70              | B39             | 99                       | 0           | —              | Ethernet Management Data Clock |

| EMDIO    | 49                     | 71              | A55             | 115                      | I/O         | —              | Ethernet Management Data       |

| Legend:  | CMOS = C               | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power         |

## TABLE 1-16: ETHERNET MII I/O DESCRIPTIONS

Legend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output

PPS = Peripheral Pin Select

I = Input

## TABLE 1-17: ETHERNET RMII PINOUT I/O DESCRIPTIONS

|          |                        | Pin Nu          | mber            |                          |             |                |                                   |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                       |

|          |                        |                 |                 | E                        | thernet I   | VII Interfac   | e                                 |

| ERXD0    | 61                     | 41              | B32             | 81                       | I           | ST             | Ethernet Receive Data 0           |

| ERXD1    | 58                     | 42              | B26             | 66                       | I           | ST             | Ethernet Receive Data 1           |

| ERXERR   | 64                     | 35              | A30             | 65                       | I           | ST             | Ethernet Receive Error Input      |

| ETXD0    | 2                      | 86              | A5              | 7                        | 0           | —              | Ethernet Transmit Data 0          |

| ETXD1    | 3                      | 85              | B4              | 8                        | 0           | —              | Ethernet Transmit Data 1          |

| ETXEN    | 1                      | 77              | A57             | 120                      | 0           | —              | Ethernet Transmit Enable          |

| EMDC     | 30                     | 70              | B39             | 99                       | 0           | —              | Ethernet Management Data Clock    |

| EMDIO    | 49                     | 71              | A55             | 115                      | I/O         | —              | Ethernet Management Data          |

| EREFCLK  | 63                     | 16              | B12             | 27                       | I           | ST             | Ethernet Reference Clock          |

| ECRSDV   | 62                     | 12              | B40             | 101                      | I           | ST             | Ethernet Carrier Sense Data Valid |

| Legend:  | CMOS = CI              | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power            |

Legend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog inputP = PowerO = OutputI = InputPPS = Peripheral Pin Select

# 2.7.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

Crystals with a speed of 4 MHz to 12 MHz that meet the following requirements will meet the PIC32MZ EC oscillation requirements when configured, as depicted in Figure 8-1.

- 1. Manufacturer Drive Level (min)  $\leq$  10  $\mu$ W (hard requirements, 1  $\mu$ W preferred).

- 2. Manufacturer ESR  $\leq 50\Omega$  (hard requirement, lower is better).

```

2.7.1.1 Calculating XTAL Capacitive Loading:

```

- 1. PIC32 CIN = COUT =  $\sim$ 4 pF (PIC32 OSCI and OSCO package pin capacitance).

- 2. C1MFG = C2MFG = Manufacturer Recommended Load Capacitance.

- CLOAD = {([CIN + C1MFG] [C2MFG + COUT]) / [CIN + C1MFG + C2MFG + COUT]} + estimated PCB stray capacitance (2.5 pF).

(Simplified) CLOAD = (((CIN + C1MFG)/2) + 2.5 pF).

Actual C1, C2 Load value to use:

- C2 = CLOAD

- C1 = (CLOAD 2 pF)

Note: These recommendations are atypical, and are only applicable to the PIC32MZ EC family.

## 2.7.1.2 Validated Crystals

Temperature Range: (-45°C to +110°C)

VDD = 2.4V to 3.6V, RP = 1 M\Omega, RK = 10  $k\Omega$

• ABLS-12.000 MHz-L4Q-T (12 MHz surface mount)

**Note:** These recommendations are atypical, and only applicable to the PIC32MZ EC family.

#### 2.7.1.3 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

## 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

## 2.9 Designing for High-Speed Peripherals

The PIC32MZ EC family devices have peripherals that operate at frequencies much higher than typical for an embedded environment. Table 2-1 lists the peripherals that produce high-speed signals on their external pins:

#### TABLE 2-1: PERIPHERALS THAT PRODUCE HS SIGNALS ON EXTERNAL PINS

| Peripheral | High-Speed Signal Pins | Maximum<br>Speed on<br>Signal Pin |

|------------|------------------------|-----------------------------------|

| EBI        | EBIAx, EBIDx           | 50 MHz                            |

| SQI1       | SQICLK, SQICSX, SQIDx  | 50 MHz                            |

| HS USB     | D+, D-                 | 480 MHz                           |

Due to these high-speed signals, it is important to take into consideration several factors when designing a product that uses these peripherals, as well as the PCB on which these components will be placed. Adhering to these recommendations will help achieve the following goals:

- Minimize the effects of electromagnetic interference to the proper operation of the product

- Ensure signals arrive at their intended destination at the same time

- Minimize crosstalk

- Maintain signal integrity

- Reduce system noise

- Minimize ground bounce and power sag

NOTES:

## TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)

| ess (                       |                                 | σ         |       |       |       |       |              |       |          | В                     | its  |      |      |      |              |                     |          |                       | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|--------------|-------|----------|-----------------------|------|------|------|------|--------------|---------------------|----------|-----------------------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11        | 26/10 | 25/9     | 24/8                  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3         | 18/2                | 17/1     | 16/0                  | All Resets |

| 0050                        | IPC43                           | 31:16     | _     |       | —     |       | I2C4MIP<2:0  | >     | I2C4MI   | S<1:0>                | _    |      |      |      | I2C4SIP<2:0  | >                   | I2C4SIS  | S<1:0>                | 0000       |

| 03F0                        | IPC43                           | 15:0      | _     | _     | _     |       | I2C4BIP<2:0: | >     | I2C4BIS  | S<1:0>                | _    | _    | _    |      | U4TXIP<2:0:  | >                   | U4TXIS   | S<1:0>                | 0000       |

| 0400                        | 10044                           | 31:16     |       | _     | —     |       | U5EIP<2:0>   |       | U5EIS    | <1:0>                 | _    | _    | _    | SF   | PI5TXIP<2:0: | <sub>&gt;</sub> (2) | SPI5TXIS | S<1:0> <b>(2)</b>     | 0000       |

| 0400                        | IPC44                           | 15:0      | _     | _     | —     | S     | PI5RXIP<2:0  | (2)   | SPI5RXIS | S<1:0> <sup>(2)</sup> | _    | _    | —    | S    | PI5EIP<2:0>  | (2)                 | SPI5EIS  | <1:0> <sup>(2)</sup>  | 0000       |

| 0440                        | IPC45                           | 31:16     | _     | _     | _     |       | I2C5SIP<2:0: | >     | 12C5S18  | S<1:0>                | _    | _    | _    |      | I2C5BIP<2:0  | >                   | I2C5BI   | S<1:0>                | 0000       |

| 0410                        | IPC45                           | 15:0      |       | _     | —     |       | U5TXIP<2:0>  | •     | U5TXIS   | S<1:0>                | _    | _    | _    |      | U5RXIP<2:0   | >                   | U5RXIS   | S<1:0>                | 0000       |

| 0400                        | 10040                           | 31:16     | _     | _     | -     | S     | PI6TXIP<2:0> | .(2)  | SPI6TXIS | S<1:0> <sup>(2)</sup> | -    | _    | _    | SF   | PI6RXIP<2:0: | > <sup>(2)</sup>    | SPI6RXIS | 6<1:0> <sup>(2)</sup> | 0000       |

| 0420                        | IPC46                           | 15:0      | _     | _     | _     | ;     | SPI6EIP<2:0> | (2)   | SPI6EIS  | <1:0> <sup>(2)</sup>  | _    | _    | _    | I    | 2C5MIP<2:0   | >                   | I2C5MI   | S<1:0>                | 0000       |

| 0.400                       | 100.17                          | 31:16     | _     | -     | _     | _     | _            | _     | _        | _                     | _    |      | -    |      | U6TXIP<2:0:  | >                   | U6TXIS   | S<1:0>                | 0000       |

| 0430                        | IPC47                           | 15:0      | _     | -     | _     |       | U6RXIP<2:0   | >     | U6RXIS   | S<1:0>                | _    |      | -    |      | U6EIP<2:0>   |                     | U6EIS    | <1:0>                 | 0000       |

| 05.40                       | 055000                          | 31:16     | _     | _     | _     | _     | _            | _     | _        | _                     | _    | _    | _    | _    | _            | _                   | VOFF<    | 17:16>                | 0000       |

| 0540                        | OFF000                          | 15:0      |       |       |       |       |              |       |          | VOFF<15:1             | >    |      |      |      |              |                     |          | _                     | 0000       |

| 05.4.4                      | OFF001                          | 31:16     | _     | _     | _     | _     | _            | _     | _        | _                     | _    | _    | _    | _    | —            | _                   | VOFF<    | 17:16>                | 0000       |

| 0544                        | OFF001                          | 15:0      |       |       |       |       |              |       |          | VOFF<15:1             | >    |      |      |      |              |                     |          | _                     | 0000       |

| 05.40                       | 055000                          | 31:16     | _     | _     | _     | _     | _            | _     | _        | _                     | _    | _    | _    | _    | _            | _                   | VOFF<    | 17:16>                | 0000       |

| 0548                        | OFF002                          | 15:0      |       |       |       |       |              |       |          | VOFF<15:1             | >    |      |      |      |              |                     |          | —                     | 0000       |

| 0540                        | 055000                          | 31:16     | _     | _     | _     | _     | _            | _     | _        | _                     | _    | _    | _    | _    | _            | _                   | VOFF<    | 17:16>                | 0000       |

| 054C                        | OFF003                          | 15:0      |       |       |       |       |              |       |          | VOFF<15:1             | >    |      |      |      |              |                     |          | _                     | 0000       |

| 0550                        | 055004                          | 31:16     |       | _     | _     | _     | _            | _     | —        | _                     | _    | _    | —    |      | _            | —                   | VOFF<    | 17:16>                | 0000       |

| 0550                        | OFF004                          | 15:0      |       |       |       |       |              |       |          | VOFF<15:1             | >    |      |      |      | •            |                     |          | _                     | 0000       |

| 0554                        | OFFOOF                          | 31:16     |       | _     | _     | _     | _            | _     | —        | _                     | _    | _    | —    |      | _            | —                   | VOFF<    | 17:16>                | 0000       |

| 0554                        | OFF005                          | 15:0      |       |       |       |       |              |       |          | VOFF<15:1             | >    |      |      |      |              |                     |          | _                     | 0000       |

| 0550                        | OFF006                          | 31:16     | _     | _     | _     | _     | _            | _     | _        | _                     | _    | _    | _    | _    | —            | _                   | VOFF<    | 17:16>                | 0000       |

| 0558                        | OFF006                          | 15:0      |       |       |       |       |              |       |          | VOFF<15:1             | >    |      |      |      |              |                     |          | _                     | 0000       |

| 0550                        | 055007                          | 31:16     | _     | _     | _     | _     | _            | _     | _        | _                     | _    | _    | _    | _    | —            | _                   | VOFF<    | 17:16>                | 0000       |

| 055C                        | OFF007                          | 15:0      |       |       |       |       |              |       |          | VOFF<15:1             | >    |      |      |      | •            |                     |          | _                     | 0000       |

| 0500                        | 055000                          | 31:16     | _     | —     | _     | _     | _            | _     | _        | —                     | _    | —    | —    | _    | —            | _                   | VOFF<    | 17:16>                | 0000       |

| 0560                        | OFF008                          | 15:0      |       |       |       |       |              |       |          | VOFF<15:1             | >    |      |      |      |              |                     |          | —                     | 0000       |

| 050 (                       | 055000                          | 31:16     | —     | —     | —     | —     | —            | —     | —        | —                     | _    | —    | —    |      | —            | —                   | VOFF<    | 17:16>                | 0000       |

| 0564                        | OFF009                          | 15:0      |       |       |       |       |              |       |          | VOFF<15:1             | >    |      |      |      |              |                     | •        | _                     | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: This bit or register is not available on 64-pin devices.

3: This bit or register is not available on devices without a CAN module.

4: This bit or register is not available on 100-pin devices.

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

7: This bit or register is not available on devices without a Crypto module.

8: This bit or register is not available on 124-pin devices.

## 9.2 Prefetch Control Registers

## TABLE 9-1: PREFETCH REGISTER MAP

| ess (                      |                                 | е         |       | Bits  |       |       |        |          |      |      |      |      |       |        |          |      |          |      |           |  |  |  |  |  |  |  |  |  |  | s |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|--------|----------|------|------|------|------|-------|--------|----------|------|----------|------|-----------|--|--|--|--|--|--|--|--|--|--|---|

| Virtual Addres<br>(BF8E_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11  | 26/10    | 25/9 | 24/8 | 23/7 | 22/6 | 21/5  | 20/4   | 19/3     | 18/2 | 17/1     | 16/0 | All Reset |  |  |  |  |  |  |  |  |  |  |   |

|                            | DDEOON                          | 31:16     |       | _     |       | -     | _      | PFMSECEN | _    | _    |      | _    | _     | _      | _        | _    | _        |      | 0000      |  |  |  |  |  |  |  |  |  |  |   |

| 0000                       | PRECON                          | 15:0      | —     | —     | _     | —     | —      | _        | —    | —    | —    | _    | PREFE | N<1:0> | —        | F    | FMWS<2:0 | >    | 0007      |  |  |  |  |  |  |  |  |  |  |   |

| 0040                       | DDEOTAT                         | 31:16     | _     | _     |       | _     | PFMDED | PFMSEC   | _    | _    | _    | _    | _     | _      | _        | —    | _        | _    | 0000      |  |  |  |  |  |  |  |  |  |  |   |

| 0010                       | PRESTAT                         | 15:0      | _     | _     | _     | —     | _      | _        | _    | _    |      |      |       | PFMSEC | CNT<7:0> |      |          |      | 0000      |  |  |  |  |  |  |  |  |  |  |   |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

## TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |       |       |       |       |             |       |      | Bit     | s      |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|-------|-------------|-------|------|---------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9 | 24/8    | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 15B0                        | DCH7ECON                        | 31:16         | —     | —     | —     | _     |             | _     |      | —       |        |        |        | CHAIR  | Q<7:0> |        |        |        | 00FF       |

| 1360                        |                                 | 15:0          |       |       |       | CHSIR | Q<7:0>      |       |      |         | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN |        |        | _      | FF00       |

| 1500                        | DCH7INT                         | 31:16         | _     | _     | —     | —     | _           | —     | _    | _       | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 1300                        | DOM/INT                         | 15:0          | _     | —     | —     | —     | —           | —     | —    | —       | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 15D0                        | DCH7SSA                         | 31:16         |       |       |       |       |             |       |      | CHSSA   | 31.0>  |        |        |        |        |        |        |        | 0000       |

| 1020                        |                                 | 15:0          |       |       |       |       |             |       |      | 01100/1 | 01.02  |        |        |        |        |        |        |        | 0000       |

| 15E0                        | DCH7DSA                         | 31:16         |       |       |       |       |             |       |      | CHDSA   | <31:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0          |       |       |       |       |             |       |      |         |        |        |        |        |        |        |        |        | 0000       |

| 15F0                        | DCH7SSIZ                        | 31:16         | _     | _     | —     | —     | _           | _     | _    | -       | -      | _      | _      | _      | _      | _      |        |        | 0000       |

|                             |                                 | 15:0          |       |       |       |       |             |       |      | CHSSIZ  |        |        |        |        |        |        |        |        | 0000       |

| 1600                        | DCH7DSIZ                        | 31:16         | _     | _     | —     | _     | _           | _     | _    | -       | -      | —      |        | _      | _      | —      |        |        | 0000       |

|                             |                                 | 15:0          |       |       |       |       |             |       |      | CHDSIZ  |        |        |        |        |        |        |        |        | 0000       |

| 1610                        | DCH7SPTR                        | 31:16         | _     | _     | —     | —     | —           | —     | _    |         | -      | —      |        | _      | —      | —      | —      |        | 0000       |

|                             |                                 | 15:0          |       |       |       |       |             |       |      | CHSPTR  |        |        |        |        |        |        |        |        | 0000       |

| 1620                        | DCH7DPTR                        | 31:16         | _     | _     | _     | _     | _           | _     | _    | -       | -      | _      | _      | _      | _      | —      |        |        | 0000       |

|                             |                                 | 15:0          |       |       |       |       |             |       |      | CHDPTR  | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1630                        | DCH7CSIZ                        | 31:16         | _     |       | —     | _     | _           | _     | _    | -       | -      | _      | _      | _      | _      | _      |        |        | 0000       |

|                             |                                 | 15:0          |       |       |       |       |             |       |      | CHCSIZ  |        |        |        |        |        |        |        |        | 0000       |

| 1640                        | DCH7CPTR                        | 31:16         | _     | —     | —     |       | _           | _     | _    |         |        | —      |        | —      | —      | _      |        |        | 0000       |

|                             |                                 | 15:0          |       |       |       |       |             |       |      | CHCPTR  |        |        |        |        |        |        |        |        | 0000       |

| 1650                        | DCH7DAT                         | 31:16<br>15:0 | _     | —     | —     | _     | _           | _     | _    |         |        | —      |        | —      | —      | —      |        |        | 0000       |

|                             |                                 |               |       |       |       |       | 10' Booot y |       |      | CHPDAT  | <15:0> |        |        |        |        |        |        |        | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# REGISTER 11-5: USBIE0CSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 0)

|              | 1-                |                   | /                 |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|              | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0, HC         | R/W-0            | R/W-0, HC        |

| 31:24        |                   |                   |                   |                   |                   |                   |                  | FLSHFIFO         |

|              | —                 | _                 | —                 |                   | DISPING           | DTWREN            | DATATGGL         | FLOHFIFU         |

|              | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/C-0, HS         | R/W-0, HS         | R-0, HS           | R-0              | R-0              |

| 23:16        | SVCSETEND         | SVCRPR            | SENDSTALL         | SETUPEND          | DATAEND           | SENTSTALL         | TXPKTRDY         | RXPKTRDY         |

|              | NAKTMOUT          | STATPKT           | REQPKT            | ERROR             | SETUPPKT          | RXSTALL           |                  | NAFNINDI         |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | —                 | —                 | —                 | —                 |                   | —                 | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7.0          |                   | _                 |                   | _                 |                   | _                 | _                | _                |

| Legend:           | HC = Hardware Cleared | HS = Hardware Set         |                    |  |  |  |  |

|-------------------|-----------------------|---------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, re | ad as '0'          |  |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |  |

#### bit 31-28 Unimplemented: Read as '0'

- bit 27 **DISPING:** Disable Ping tokens control bit (*Host mode*)

- 1 = USB Module will not issue PING tokens in data and status phases of a Hi-Speed Control transfer

0 = Ping tokens are issued

- bit 26 DTWREN: Data Toggle Write Enable bit (*Host mode*)

1 = Enable the current state of the Endpoint 0 data toggle to be written. Automatically cleared.

0 = Disable data toggle write

- bit 25 **DATATGGL:** Data Toggle bit (*Host mode*) When read, this bit indicates the current state of the Endpoint 0 data toggle. If DTWREN = 1, this bit is writable with the desired setting.

- If DTWREN = 0, this bit is read-only.

- bit 24 FLSHFIFO: Flush FIFO Control bit

- 1 = Flush the next packet to be transmitted/read from the Endpoint 0 FIFO. The FIFO pointer is reset and the TXPKTRDY/RXPKTRDY bit is cleared. Automatically cleared when the operation completes. Should only be used when TXPKTRDY/RXPKTRDY = 1.

- 0 = No Flush operation

#### bit 23 SVCSETEND: Clear SETUPEND Control bit (Device mode)

- 1 = Clear the SETUPEND bit in this register. This bit is automatically cleared.

- 0 = Do not clear

#### NAKTMOUT: NAK Time-out Control bit (Host mode)

- 1 = Endpoint 0 is halted following the receipt of NAK responses for longer than the time set by the NAKLIM<4:0> bits (USBICSR<28:24>)

- 0 = Allow the endpoint to continue

- bit 22 **SVCRPR:** Serviced RXPKTRDY Clear Control bit (*Device mode*)

- 1 = Clear the RXPKTRDY bit in this register. This bit is automatically cleared.

- 0 = Do not clear

#### STATPKT: Status Stage Transaction Control bit (Host mode)

- 1 = When set at the same time as the TXPKTRDY or REQPKT bit is set, performs a status stage transaction

- 0 = Do not perform a status stage transaction

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | VPLEN             | N<7:0>            |                   |                  |                  |

| 22.46        | R/W-0             | R/W-1             | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0            | R/W-0            |

| 23:16        |                   | WTCO              | N<3:0>            |                   |                   | WTID              | <3:0>            |                  |

| 15.0         | R-1               | R-0               | R-0               | R-0               | R-1               | R-1               | R-0              | R-0              |

| 15:8         |                   | DMACHA            | NS<3:0>           |                   |                   | RAMBI             | 「S<3:0>          |                  |

| 7.0          | R-0               | R-1               | R-1               | R-1               | R-0               | R-1               | R-1              | R-1              |

| 7:0          |                   | RXENDF            | PTS<3:0>          |                   |                   | TXENDP            | 'TS<3:0>         |                  |

## **REGISTER 11-16: USBINFO: USB INFORMATION REGISTER**

## Legend:

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-24 VPLEN<7:0>: VBUS pulsing charge length bits

Sets the duration of the VBUS pulsing charge in units of 546.1  $\mu s.$  (The default setting corresponds to 32.77 ms.)

- bit 23-20 WTCON<3:0>: Connect/Disconnect filter control bits Sets the wait to be applied to allow for the connect/disconnect filter in units of 533.3 ns. The default setting corresponds to 2.667 μs.

- bit 19-6 WTID<3:0>: ID delay valid control bits

Sets the delay to be applied from IDPULLUP being asserted to IDDIG being considered valid in units of 4.369ms. The default setting corresponds to 52.43ms.

#### bit 15-12 DMACHANS<3:0>: DMA Channels bits

These read-only bits provide the number of DMA channels in the USB module. For the PIC32MZ EC family, this number is 8.

### bit 11-8 **RAMBITS<3:0>:** RAM address bus width bits

These read-only bits provide the width of the RAM address bus. For the PIC32MZ EC family, this number is 12.

#### bit 7-4 RXENDPTS<3:0>: Included RX Endpoints bits

This read-only register gives the number of RX endpoints in the design. For the PIC32MZ EC family, this number is 7.

bit 3-0 TXENDPTS<3:0>: Included TX Endpoints bits

These read-only bits provide the number of TX endpoints in the design. For the PIC32MZ EC family, this number is 7.

# 16.1 Watchdog Timer Control Registers

# TABLE 16-1: WATCHDOG TIMER REGISTER MAP

| ess                        |                       | e         |                                | Bits  |       |       |       |       |      |      |          |      |      |      |      | s    |      |      |           |

|----------------------------|-----------------------|-----------|--------------------------------|-------|-------|-------|-------|-------|------|------|----------|------|------|------|------|------|------|------|-----------|

| Virtual Addres<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15                          | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7     | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 0000                       | WDTCON <sup>(1)</sup> | 31:16     |                                |       |       |       |       |       |      | WDTC | LRKEY<15 | i:0> |      |      |      |      |      |      | 0000      |

| 0800                       | WDTCON()              | 15:0      | ON SWDTPS<4:0> WDTWINEN - x0xx |       |       |       |       |       |      |      |          | x0xx |      |      |      |      |      |      |           |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                            | —                 | _                 | —                 | —                 | -                 | —                | —                |  |

| 00.40        | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                          | —                 | _                 | -                 | —                 | -                 | —                | —                |  |

| 45.0         | R/W-0                      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CLKDIV<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R/W-0            |  |

|              |                            |                   |                   |                   | _                 |                   | STABLE           | EN               |  |

#### REGISTER 20-5: SQI1CLKCON: SQI CLOCK CONTROL REGISTER

## Legend:

| 0                                 |                  |                                    |                    |   |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|---|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |   |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown | 1 |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-8 CLKDIV<7:0>: SQI Clock TsQI Frequency Select bit<sup>(1)</sup>

10000000 = Base clock TBC is divided by 512 01000000 = Base clock TBC is divided by 256 00100000 = Base clock TBC is divided by 128 00010000 = Base clock TBC is divided by 64 00001000 = Base clock TBC is divided by 32 00000100 = Base clock TBC is divided by 16 00000010 = Base clock TBC is divided by 8 00000001 = Base clock TBC is divided by 4 00000000 = Base clock TBC is divided by 2

Setting these bits to '0000000' specifies the highest frequency of the SQI clock.

- bit 7-2 Unimplemented: Read as '0'

- bit 1 STABLE: TSQI Clock Stable Select bit

This bit is set to '1' when the SQI clock, TsQI, is stable after writing a '1' to the EN bit.

- 1 = Tsqi clock is stable

- 0 = TSQI clock is not stable

#### bit 0 EN: TSQI Clock Enable Select bit

When clock oscillation is stable, the SQI module will set the STABLE bit to '1'.

1 = Enable the SQI clock (TSQI) (when clock oscillation is stable, the SQI module sets the STABLE bit to '1')

Disable the SQI clock (TsQI) (the SQI module should stop its clock to enter a low power state); SFRs can still be accessed, as they use PBCLK5

# **Note 1:** Refer to Table in **Section 37.0 "Electrical Characteristics**" for the maximum clock frequency specifications.

#### REGISTER 24-3: EBISMTX: EXTERNAL BUS INTERFACE STATIC MEMORY TIMING REGISTER ('x' = 0-2)

|              | ( /                          | ( = 0-2)                   |                   |                   |                     |                          |                  |                  |

|--------------|------------------------------|----------------------------|-------------------|-------------------|---------------------|--------------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7            | Bit<br>30/22/14/6          | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2        | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0                          | U-0                        | U-0               | U-0               | U-0                 | R/W-1                    | R/W-0            | R/W-0            |

| 31:24        | —                            | _                          | —                 | —                 | —                   | RDYMODE                  | PAGESI           | ZE<1:0>          |

| 00.40        | R/W-0                        | R/W-0                      | R/W-0             | R/W-1             | R/W-1               | R/W-1                    | R/W-0            | R/W-0            |

| 23:16        | PAGEMODE                     | E TPRC<3:0> <sup>(1)</sup> |                   |                   |                     | TBTA<2:0> <sup>(1)</sup> |                  |                  |

| 45.0         | R/W-0                        | R/W-0                      | R/W-1             | R/W-0             | R/W-1               | R/W-1                    | R/W-0            | R/W-1            |

| 15:8         | TWP<5:0> <sup>(1)</sup>      |                            |                   |                   |                     | •                        | TWR<             | :1:0> <b>(1)</b> |

| 7:0          | R/W-0                        | R/W-1                      | R/W-0             | R/W-0             | R/W-1               | R/W-0                    | R/W-1            | R/W-1            |

|              | TAS<1:0> <sup>(1)</sup> TRC- |                            |                   | TRC<              | 5:0> <sup>(1)</sup> |                          |                  |                  |

#### Legend:

| 5                                 |                  |                                    |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-27 Unimplemented: Read as '0'

|           | Unimplemented. Read as 0                                                                          |

|-----------|---------------------------------------------------------------------------------------------------|

| bit 26    | RDYMODE: Data Ready Device Select bit                                                             |

|           | The device associated with register set 'x' is a data-ready device, and will use the EBIRDYx pin. |

|           | 1 = EBIRDYx input is used                                                                         |

|           | 0 = EBIRDYx input is not used                                                                     |

| bit 25-24 | PAGESIZE<1:0>: Page Size for Page Mode Device bits                                                |

|           | 11 = 32-word page                                                                                 |

|           | 10 = 16-word page                                                                                 |

|           | 01 = 8-word page                                                                                  |

|           | 00 = 4-word page                                                                                  |

| bit 23    | PAGEMODE: Memory Device Page Mode Support bit                                                     |

|           | 1 = Device supports Page mode                                                                     |

|           | 0 = Device does not support Page mode                                                             |

| bit 22-19 | <b>TPRC&lt;3:0&gt;:</b> Page Mode Read Cycle Time bits <sup>(1)</sup>                             |

|           |                                                                                                   |

Read cycle time is TPRC + 1 clock cycle.

- bit 18-16 **TBTA<2:0>:** Data Bus Turnaround Time bits<sup>(1)</sup> Clock cycles (0-7) for static memory between read-to-write, write-to-read, and read-to-read when Chip Select changes.

- bit 15-10 **TWP<5:0>:** Write Pulse Width bits<sup>(1)</sup>

- Write pulse width is TWP + 1 clock cycle.

- bit 9-8 **TWR<1:0>:** Write Address/Data Hold Time bits<sup>(1)</sup> Number of clock cycles to hold address or data on the bus.

- bit 7-6 TAS<1:0>: Write Address Setup Time bits<sup>(1)</sup>

Clock cycles for address setup time. A value of '0' is only valid in the case of SSRAM.

bit 5-0 TRC<5:0>: Read Cycle Time bits<sup>(1)</sup>

- Read cycle time is TRC + 1 clock cycle.

- Note 1: Please refer to Section 47. "External Bus Interface (EBI)" (DS60001245) in the "PIC32 Family Reference Manual" for the EBI timing diagrams and additional information.

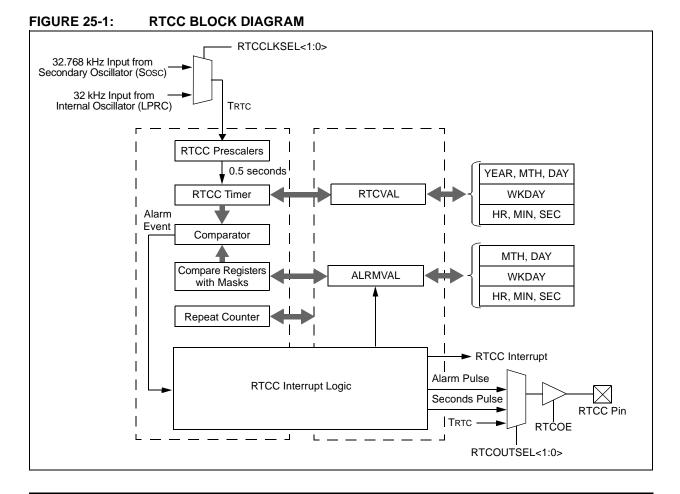

# 25.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Lowpower optimization provides extended battery lifetime while keeping track of time. The following are key features of the RTCC module:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- Provides calendar: Weekday, date, month and year

- Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month, and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap year correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- Calibrates up to 260 ppm of crystal error

- Uses external 32.768 kHz crystal or 32 kHz internal oscillator

- Alarm pulse, seconds clock, or internal clock output on RTCC pin

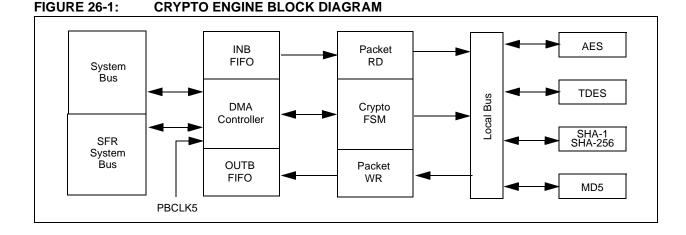

# 26.0 CRYPTO ENGINE

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 49. "Crypto Engine (CE) and Random Number Generator (RNG)" (DS60001246), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Crypto Engine is intended to accelerate applications that need cryptographic functions. By executing these functions in the hardware module, software overhead is reduced, and actions such as encryption, decryption, and authentication can execute much more quickly.

The Crypto Engine uses an internal descriptor-based DMA for efficient programming of the security association data and packet pointers (allowing scatter/gather data fetching). An intelligent state machine schedules the Crypto Engines based on the protocol selection and packet boundaries. The hard-ware engines can perform the encryption and authentication in sequence or in parallel.

| Note: | To avoid cache coherency problems on    |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | devices with L1 cache, Crypto buffers   |  |  |  |  |  |  |

|       | must only be allocated or accessed from |  |  |  |  |  |  |

|       | the KSEG1 segment.                      |  |  |  |  |  |  |

Key features of the Crypto Engine include:

- Bulk ciphers and hash engines

- Integrated DMA to off-load processing:

- Buffer descriptor-based

- Secure association per buffer descriptor

- · Some functions can execute in parallel

Bulk ciphers that are handled by the Crypto Engine include:

- AES:

- 128-bit, 192-bit, and 256-bit key sizes

- CBC, ECB, CTR, CFB, and OFB modes

- DES/TDES:

- CBC, ECB, CFB, and OFB modes

Authentication engines that are available through the Crypto Engine include:

- SHA-1

- SHA-256

- MD-5

- AES-GCM

- HMAC operation (for all authentication engines)

The rate of data that can be processed by the Crypto Engine depends on a number of factors, including:

- Which engine is in use

- Whether the engines are used in parallel or in series

- The demands on source and destination memories by other parts of the system (i.e., CPU, DMA, etc.)

- The speed of PBCLK5, which drives the Crypto Engine

Table 26-1 shows typical performance for various engines.

#### TABLE 26-1: CRYPTO ENGINE PERFORMANCE

| Engine/<br>Algorithm | Performance<br>Factor<br>(Mbps/MHz) | Maximum Mbps<br>(PBCLK5 = 100 MHz) |

|----------------------|-------------------------------------|------------------------------------|

| DES                  | 14.4                                | 1440                               |

| TDES                 | 6.6                                 | 660                                |

| AES-128              | 9.0                                 | 900                                |

| AES-192              | 7.9                                 | 790                                |

| AES-256              | 7.2                                 | 720                                |

| MD5                  | 15.6                                | 1560                               |

| SHA-1                | 13.2                                | 1320                               |

| SHA-256              | 9.3                                 | 930                                |

## REGISTER 26-5: CESTAT: CRYPTO ENGINE STATUS REGISTER (CONTINUED)

- bit 16 ACTIVE: Buffer Descriptor Processor Status bit

- 1 = BDP is active

- 0 = BDP is idle

- bit 15-0 **BDCTRL<15:0>:** Descriptor Control Word Status bits These bits contain the current descriptor control word.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                     | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | —                 | _                   | -                 | _                 | —                 | _                | —                |

| 15.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ON                | COE               | CPOL <sup>(1)</sup> | -                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

|              | EVPOL             | _<1:0>            |                     | CREF              | —                 | —                 | CCH              | <1:0>            |

#### REGISTER 31-1: CMxCON: COMPARATOR CONTROL REGISTER

#### Legend:

| R = Readable bit  | = Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |  |  |

|-------------------|---------------------------------|----------------------|------------------------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: Comparator ON bit

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(1)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 =Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

#### bit 4 CREF: Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 01.04        | r-0               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |

| 45.0         | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 15:8         | _                 | —                 | _                 | _                 | _                 | _                 | _                | _                |

|              | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 |                  | _                |

### REGISTER 34-1: DEVSIGN0/ADEVSIGN0: DEVICE SIGNATURE WORD 0 REGISTER

| Legend:           | r = Reserved bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 Reserved: Write as '0'

bit 30-0 Reserved: Write as '1'

**Note:** The DEVSIGN1 through DEVSIGN3 and ADEVSIGN1 through ADEVSIGN3 registers are used for Quad Word programming operation when programming the DEVSIGN0/ADESIGN0 registers, and do not contain any valid information.

## REGISTER 34-2: DEVCP0/ADEVCP0: DEVICE CODE-PROTECT 0 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | r-1               | r-1               | r-1               | R/P               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | _                 | —                 | —                 | CP                | —                 | _                 | _                | _                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        | _                 | —                 | —                 | _                 | —                 | _                 | _                | —                |

| 45.0         | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 15:8         | _                 | —                 | —                 | _                 | —                 | _                 | _                | _                |

| 7.0          | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| Legend:           | r = Reserved bit | P = Programmable bit               |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-29 Reserved: Write as '1'

bit 28 **CP:** Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device. 1 = Protection is disabled

0 = Protection is enabled

bit 27-0 Reserved: Write as '1'

Note: The DEVCP1 through DEVCP3 and ADEVCP1 through ADEVCP3 registers are used for Quad Word programming operation when programming the DEVCP0/ADEVCP0 registers, and do not contain any valid information.

#### REGISTER 34-5: DEVCFG2/ADEVCFG2: DEVICE CONFIGURATION WORD 2 (CONTINUED)

- bit 3 **Reserved:** Write as '1'

- bit 2-0 FPLLIDIV<2:0>: PLL Input Divider bits

- 111 = Divide by 8

- 110 = Divide by 7

- 101 = Divide by 6

- 100 = Divide by 5

- 011 =Divide by 4

- 010 = Divide by 3

- 001 = Divide by 2

- 000 = Divide by 1

| AC CHARACTERISTICS |         |                               | JIREMENTS (MASTER MODE) (CONTINUED)Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                     |      |       |                                        |

|--------------------|---------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|----------------------------------------|

| Param.<br>No.      | Symbol  | bol Characteristics           |                                                                                                                                                                                    | Min. <sup>(1)</sup> | Max. | Units | Conditions                             |

| IM21               | TR:SCL  | SDAx and SCLx                 | 100 kHz mode                                                                                                                                                                       | —                   | 1000 | ns    | CB is specified to be                  |

|                    |         | Rise Time                     | 400 kHz mode                                                                                                                                                                       | 20 + 0.1 Св         | 300  | ns    | from 10 to 400 pF                      |

|                    |         |                               | 1 MHz mode<br>(Note 2)                                                                                                                                                             | —                   | 300  | ns    |                                        |

| IM25               | TSU:DAT | Data Input<br>Setup Time      | 100 kHz mode                                                                                                                                                                       | 250                 | —    | ns    | —                                      |

|                    |         |                               | 400 kHz mode                                                                                                                                                                       | 100                 | _    | ns    |                                        |

|                    |         |                               | 1 MHz mode<br>(Note 2)                                                                                                                                                             | 100                 | _    | ns    |                                        |

| IM26               | THD:DAT | Data Input<br>Hold Time       | 100 kHz mode                                                                                                                                                                       | 0                   | —    | μs    | —                                      |

|                    |         |                               | 400 kHz mode                                                                                                                                                                       | 0                   | 0.9  | μs    | 1                                      |

|                    |         |                               | 1 MHz mode<br>(Note 2)                                                                                                                                                             | 0                   | 0.3  | μs    |                                        |

| IM30               | TSU:STA | Start Condition<br>Setup Time | 100 kHz mode                                                                                                                                                                       | TPBCLK2 * (BRG + 2) | _    | μs    | Only relevant for<br>Repeated Start    |

|                    |         |                               | 400 kHz mode                                                                                                                                                                       | TPBCLK2 * (BRG + 2) | _    | μs    |                                        |

|                    |         |                               | 1 MHz mode<br>(Note 2)                                                                                                                                                             | Трвськ2 * (BRG + 2) | _    | μs    | condition                              |

| IM31               | Thd:sta | Start Condition<br>Hold Time  | 100 kHz mode                                                                                                                                                                       | TPBCLK2 * (BRG + 2) | Ι    | μS    | After this period, the                 |

|                    |         |                               | 400 kHz mode                                                                                                                                                                       | TPBCLK2 * (BRG + 2) | _    | μs    | first clock pulse is                   |

|                    |         |                               | 1 MHz mode<br>(Note 2)                                                                                                                                                             | Трвськ2 * (BRG + 2) | _    | μs    | generated                              |

| IM33               | Tsu:sto | Stop Condition<br>Setup Time  | 100 kHz mode                                                                                                                                                                       | TPBCLK2 * (BRG + 2) | _    | μs    | —                                      |

|                    |         |                               | 400 kHz mode                                                                                                                                                                       | TPBCLK2 * (BRG + 2) |      | μS    |                                        |

|                    |         |                               | 1 MHz mode<br>(Note 2)                                                                                                                                                             | Трвськ2 * (BRG + 2) | _    | μs    |                                        |

| IM34               | THD:STO | Stop Condition                | 100 kHz mode                                                                                                                                                                       | TPBCLK2 * (BRG + 2) | —    | ns    | —                                      |

|                    |         | Hold Time                     | 400 kHz mode                                                                                                                                                                       | TPBCLK2 * (BRG + 2) | _    | ns    | -                                      |

|                    |         |                               | 1 MHz mode<br>(Note 2)                                                                                                                                                             | Трвськ2 * (BRG + 2) | _    | ns    |                                        |

| IM40               | TAA:SCL | Output Valid<br>from Clock    | 100 kHz mode                                                                                                                                                                       | —                   | 3500 | ns    | —                                      |

|                    |         |                               | 400 kHz mode                                                                                                                                                                       | —                   | 1000 | ns    | —                                      |

|                    |         |                               | 1 MHz mode<br>(Note 2)                                                                                                                                                             | —                   | 350  | ns    | —                                      |

| IM45               | TBF:SDA | Bus Free Time                 | 100 kHz mode                                                                                                                                                                       | 4.7                 | —    | μs    | The amount of time                     |

|                    |         |                               | 400 kHz mode                                                                                                                                                                       | 1.3                 | —    | μs    | the bus must be free                   |

|                    |         |                               | 1 MHz mode<br>(Note 2)                                                                                                                                                             | 0.5                 | _    | μs    | before a new<br>transmission can start |

| IM50               | Св      | Bus Capacitive Loading        |                                                                                                                                                                                    | —                   | _    | pF    | See parameter DO58                     |

| IM51               | Tpgd    | Pulse Gobbler De              | elay                                                                                                                                                                               | 52                  | 312  | ns    | See Note 3                             |

## TABLE 37-35: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE) (CONTINUED)

**Note 1:** BRG is the value of the  $I^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

3: The typical value for this parameter is 104 ns.

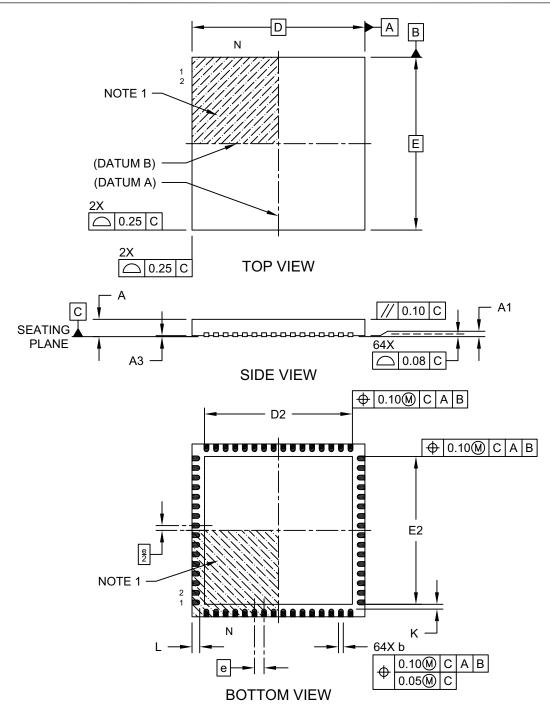

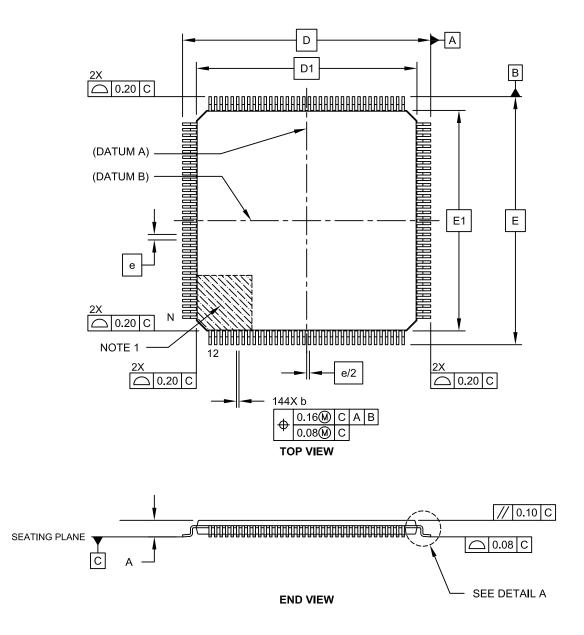

## 39.2 Package Details