Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 120                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 144-LQFP                                                                          |

| Supplier Device Package    | 144-LQFP (20x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024ecm144t-i-pl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

|          |                        | Pin Nu          | mber            |                          |             |                |                       |  |  |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description           |  |  |

| AN36     | _                      |                 | B4              | 8                        | Ι           | Analog         | Analog Input Channels |  |  |

| AN37     | _                      | —               | B12             | 27                       | I           | Analog         |                       |  |  |

| AN38     | _                      | _               | B17             | 43                       | I           | Analog         |                       |  |  |

| AN39     | _                      | _               | A22             | 44                       | I           | Analog         |                       |  |  |

| AN40     | _                      | _               | A30             | 65                       | I           | Analog         |                       |  |  |

| AN41     | _                      | _               | B26             | 66                       | I           | Analog         |                       |  |  |

| AN42     | _                      | _               | A31             | 67                       | I           | Analog         |                       |  |  |

| AN45     | 11                     | 20              | B11             | 25                       | I           | Analog         |                       |  |  |

| AN46     | 17                     | 26              | B14             | 37                       | I           | Analog         |                       |  |  |

| AN47     | 18                     | 27              | A19             | 38                       | I           | Analog         | 1                     |  |  |

| AN48     | 21                     | 32              | B18             | 47                       | I           | Analog         |                       |  |  |

| AN49     | 22                     | 33              | A23             | 48                       | I           | Analog         | 1                     |  |  |

### TABLE 1-1: ADC1 PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog input O = Output PPS = Peripheral Pin Select P = Power I = Input

# 4.1.1 BOOT FLASH SEQUENCE AND CONFIGURATION SPACES

Sequence space is used to identify which boot Flash is aliased by aliased regions. If the value programmed into the TSEQ<15:0> bits of the BF1SEQ0 word is equal to or greater than the value programmed into the TSEQ<15:0> bits of the BF2SEQ0 word, Boot Flash 1 is aliased by the lower boot alias region, and Boot Flash 2 is aliased by the upper boot alias region. If TSEQ<15:0> bits of BF2SEQ0 is greater than TSEQ<15:0> bits of BF1SEQ0, the opposite is true (see Table 4-2 and Table 4-3 for BFxSEQ0 word memory locations).

The CSEQ<15:0> bits must contain the complement value of the TSEQ<15:0> bits; otherwise, the value of TSEQ<15:0> is considered invalid, and an alternate sequence is used. See **Section 4.1.2 "Alternate Sequence and Configuration Words"** for more information.

Once boot Flash memories are aliased, configuration space located in the lower boot alias region is used as the basis for the Configuration words, DEVSIGNO, DEVCPO, and DEVCFGx (and the associated alternate configuration registers). This means that the boot Flash region to be aliased by lower boot alias region memory must contain configuration values in the appropriate memory locations.

| Note: | Do not use word program operation |

|-------|-----------------------------------|

|       | (NVMOP<3:0> = 0001) when program- |

|       | ming data into the sequence and   |

|       | configuration spaces.             |

# 4.1.2 ALTERNATE SEQUENCE AND CONFIGURATION WORDS

Every word in the configuration space and sequence space has an associated alternate word (designated by the letter A as the first letter in the name of the word). During device start-up, primary words are read and if uncorrectable ECC errors are found, the BCFGERR (RCON<27>) flag is set and alternate words are used. If uncorrectable ECC errors are found in primary and alternate words, the BCFGFAIL (RCON<26>) flag is set and the default configuration is used.

#### **TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)**

| ess)                        |                                 | Ð             |              |              |             |              |                 |              |              | B              | lits |      |      |      |      |      |       |        | s          |

|-----------------------------|---------------------------------|---------------|--------------|--------------|-------------|--------------|-----------------|--------------|--------------|----------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14        | 29/13       | 28/12        | 27/11           | 26/10        | 25/9         | 24/8           | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

| 05A4                        | OFFOOF                          | 31:16         | -            | —            | _           | _            | —               | _            | —            | —              | _    | _    | _    | —    | —    | _    | VOFF< | 17:16> | 0000       |

| 05A4                        | OFF025                          | 15:0          |              |              |             |              |                 |              |              | VOFF<15:1      | >    |      |      |      |      |      |       | -      | 0000       |

| 05A8                        | OFF026                          | 31:16         | _            | -            | _           | —            | -               | _            | -            | —              | _    | _    | —    | —    | _    | —    | VOFF< | 17:16> | 0000       |

| USAO                        | OFF020                          | 15:0          |              |              |             |              |                 |              |              | VOFF<15:1      | >    |      |      |      |      |      |       | —      | 0000       |

| 05AC                        | OFF027                          | 31:16         | _            | _            | —           | —            | _               | —            | _            | —              | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0070                        | 011021                          | 15:0          |              |              |             | •            |                 |              |              | VOFF<15:1      | >    |      |      |      | _    |      |       | —      | 0000       |

| 05B0                        | OFF028                          | 31:16         | —            | —            | —           | —            | —               | —            | —            | —              | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0020                        | 011020                          | 15:0          |              |              |             |              |                 |              |              | VOFF<15:1      | >    |      |      |      |      |      | 1     | —      | 0000       |

| 05B4                        | OFF029                          | 31:16         | —            | —            | —           | —            | —               | —            | —            | —              | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

|                             |                                 | 15:0          |              |              |             |              |                 |              |              | VOFF<15:1      | >    |      |      |      |      |      |       | —      | 0000       |

| 05B8                        | OFF030                          | 31:16         | _            | —            | _           | —            | —               | —            | —            | —              | —    | —    | —    | _    | _    | —    | VOFF< |        | 0000       |

|                             |                                 | 15:0          |              |              |             |              |                 |              |              | VOFF<15:1      |      |      |      |      |      |      |       | —      | 0000       |

| 05BC                        | OFF031                          | 31:16         | _            | —            | _           | —            | —               | _            | _            | —              | _    | _    | _    | _    | —    | _    | VOFF< |        | 0000       |

|                             | OFF032                          | 15:0          |              |              |             | -            |                 |              |              | VOFF<15:1      |      |      |      |      |      |      |       | —      | 0000       |

| 05C0                        |                                 | 31:16         | _            | _            | _           | _            | —               | _            | —            | —              | —    | —    | —    |      | —    | —    | VOFF< | 1      | 0000       |

|                             |                                 | 15:0          |              |              |             | 1            |                 |              |              | VOFF<15:1      |      |      |      |      | r    |      |       |        | 0000       |

| 05C4                        | OFF033                          | 31:16         |              | _            |             | _            | —               | —            | —            | -              | _    | —    | _    |      |      | —    | VOFF< |        | 0000       |

|                             |                                 | 15:0          |              |              |             |              |                 |              | _            | VOFF<15:1      | >    | _    |      |      |      |      | VOFF  | -      | 0000       |

| 05C8                        | OFF034                          | 31:16<br>15:0 | _            |              | _           |              |                 | _            |              | —<br>VOFF<15:1 |      |      | _    |      |      | —    | VOFF< |        | 0000       |

|                             |                                 | 31:16         |              |              |             |              |                 | _            | _            |                | >    |      |      |      |      | _    | VOFF< |        | 0000       |

| 05CC                        | OFF035                          | 15:0          |              |              |             |              | _               |              | _            | VOFF<15:1      |      | _    |      |      | _    |      | VOITS |        | 0000       |

|                             |                                 | 31:16         |              | _            |             |              | _               | _            | _            | _              | _    |      |      |      | _    |      | VOFF< |        | 0000       |

| 05D0                        | OFF036                          | 15:0          |              |              |             |              |                 |              |              | VOFF<15:1      |      |      |      |      |      |      | Voirs |        | 0000       |

|                             |                                 | 31:16         | _            | _            | _           | _            | _               | _            | _            | _              | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 05D4                        | OFF037                          | 15:0          |              |              |             |              |                 |              |              | VOFF<15:1      |      |      |      |      |      |      |       | _      | 0000       |

|                             |                                 | 31:16         |              |              |             |              |                 |              | _            | _              | _    |      |      |      |      |      | VOFF< |        | 0000       |

| 05D8                        | OFF038                          | 15:0          |              |              |             |              |                 |              |              | VOFF<15:1      |      |      |      |      |      |      |       | _      | 0000       |

|                             |                                 | 31:16         | _            | _            | _           | _            | _               | _            | _            | _              | _    | _    | _    | _    | _    | _    | VOFF< |        | 0000       |

| 05DC                        | OFF039                          | 15:0          |              |              |             |              |                 |              |              | VOFF<15:1      |      |      |      |      |      |      |       | _      | 0000       |

| Legen                       | <b>d:</b> x = u                 | 1 1           | n value on F | Reset; — = u | unimplement | ted, read as | '0'. Reset valu | es are shown | in hexadecim |                |      |      |      |      |      |      |       |        |            |

DS60001191G-page 130

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Note 1: Registers" for more information.

This bit or register is not available on 64-pin devices. 2:

This bit or register is not available on devices without a CAN module. 3:

This bit or register is not available on 100-pin devices. 4:

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

7: This bit or register is not available on devices without a Crypto module.

8: This bit or register is not available on 124-pin devices.

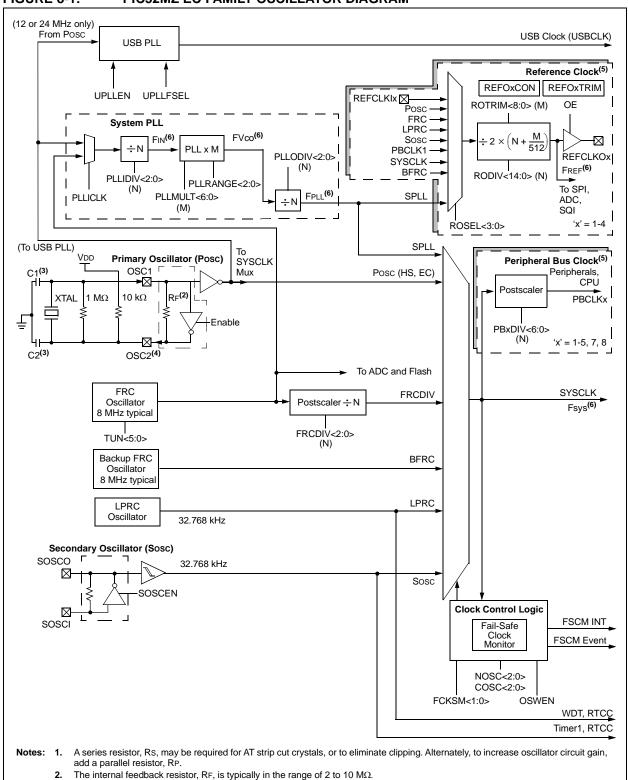

## FIGURE 8-1: PIC32MZ EC FAMILY OSCILLATOR DIAGRAM

3. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for help in deter-

mining the best oscillator components.

- PBCLK1 divided by 2 is available on the OSC2 pin in certain clock modes.

Shaded regions indicate multiple instantiations of a peripheral or feature.

- Shaded regions indicate multiple instantiations of a peripheral or feature.

Refer to Table 37-19 in Section 37.0 "Electrical Characteristics" for frequency limitations.

### REGISTER 11-4: USBCSR3: USB CONTROL STATUS REGISTER 3 (CONTINUED)

bit 19-16 ENDPOINT<3:0>: Endpoint Registers Select bits

- bit 15-11 **Unimplemented:** Read as '0'

- bit 10-0 RFRMNUM<10:0>: Last Received Frame Number bits

# PIC32MZ Embedded Connectivity (EC) Family

## REGISTER 11-7: USBIE0CSR3: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 3 (ENDPOINT 0)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | R-x               | R-x               | R-0               | R-x               | R-x               | R-x               | R-1              | R-0              |  |

| 31:24        | MPRXEN            | MPTXEN            | BIGEND            | HBRXEN            | HBTXEN            | DYNFIFOS          | SOFTCONE         | UTMIDWID         |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | _                 | _                 | _                 | —                 | —                 | —                 | —                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         | _                 | _                 | _                 | _                 | —                 | —                 | —                | —                |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 |                   | _                |                  |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31 MPRXEN: Automatic Amalgamation Option bit

- 1 = Automatic amalgamation of bulk packets is done

- 0 = No automatic amalgamation

- bit 30 **MPTXEN:** Automatic Splitting Option bit 1 = Automatic splitting of bulk packets is done

- Automatic splitting of bulk packets

- 0 = No automatic splitting

- bit 29 BIGEND: Byte Ordering Option bit

- 1 = Big Endian ordering

- 0 = Little Endian ordering

- bit 28 HBRXEN: High-bandwidth RX ISO Option bit

1 = High-bandwidth RX ISO endpoint support is selected

0 = No High-bandwidth RX ISO support

- bit 27 **HBTXEN:** High-bandwidth TX ISO Option bit 1 = High-bandwidth TX ISO endpoint support is selected 0 = No High-bandwidth TX ISO support

- bit 26 **DYNFIFOS:** Dynamic FIFO Sizing Option bit 1 = Dynamic FIFO sizing is supported 0 = No Dynamic FIFO sizing

- bit 25 SOFTCONE: Soft Connect/Disconnect Option bit 1 = Soft Connect/Disconnect is supported 0 = Soft Connect/Disconnect is not supported

- bit 24 UTMIDWID: UTMI+ Data Width Option bit Always '0', indicating 8-bit UTMI+ data width

- bit 23-0 Unimplemented: Read as '0'

### REGISTER 11-8: USBIENCSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 1-7)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | AUTOSET           | ISO               | MODE              |                   |                   | DMAREQMD          | —                | —                |

|              |                   | —                 | MODE              | DIMAREQUIN        | FREDATIG          |                   | DATAWEN          | DATATGGL         |

|              | R/W-0, HS         | R/W-0, HC         | R/W-0, HS         | R/W-0             | R/W-0             | R/W-0, HS         | R/W-0            | R/W-0, HC        |

| 23:16        | INCOMPTX          | CLRDT             | SENTSTALL         | SENDSTALL         | FLUSH             | UNDERRUN          | FIFONE           | TXPKTRDY         |

|              | NAKTMOUT          | GLRDT             | RXSTALL           | SETUPPKT          | FLUSH             | ERROR             |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   | MULT<4:0>         |                   |                   | T                 | XMAXP<10:8       | >                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | <p<7:0></p<7:0>   |                   |                   |                  |                  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31 AUTOSET: Auto Set Control bit

- 1 = TXPKTRDY will be automatically set when data of the maximum packet size (value in TXMAXP) is loaded into the TX FIFO. If a packet of less than the maximum packet size is loaded, then TXPKTRDY will have to be set manually.

- 0 = TXPKTRDY must be set manually for all packet sizes

- bit 30 **ISO:** Isochronous TX Endpoint Enable bit (Device mode)

- 1 = Enables the endpoint for Isochronous transfers

- 0 = Disables the endpoint for lsochronous transfers and enables it for Bulk or Interrupt transfers. This bit only has an effect in Device mode. In Host mode, it always returns '0'.

- bit 29 MODE: Endpoint Direction Control bit

- 1 = Endpoint is TX

- 0 = Endpoint is RX

This bit only has any effect where the same endpoint FIFO is used for both TX and RX transactions.

- bit 28 DMAREQEN: Endpoint DMA Request Enable bit

- 1 = DMA requests are enabled for this endpoint

- 0 = DMA requests are disabled for this endpoint

- bit 27 **FRCDATTG:** Force Endpoint Data Toggle Control bit

- 1 = Forces the endpoint data toggle to switch and the data packet to be cleared from the FIFO, regardless of whether an ACK was received.

- 0 = No forced behavior

- bit 26 DMAREQMD: Endpoint DMA Request Mode Control bit

- 1 = DMA Request Mode 1

- 0 = DMA Request Mode 0

This bit must not be cleared either before or in the same cycle as the above DMAREQEN bit is cleared.

- bit 25 DATAWEN: Data Toggle Write Enable bit (Host mode)

- 1 = Enable the current state of the TX Endpoint data toggle (DATATGGL) to be written

- 0 = Disables writing the DATATGGL bit

- bit 24 **DATATGGL:** Data Toggle Control bit (Host mode)

When read, this bit indicates the current state of the TX Endpoint data toggle. If DATAWEN = 1, this bit may be written with the required setting of the data toggle. If DATAWEN = 0, any value written to this bit is ignored.

#### **USBIENCSR1: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 1** REGISTER 11-9: (ENDPOINT 1-7) (CONTINUED) bit 26 DATATWEN: Data Toggle Write Enable Control bit (Host mode) 1 = DATATGGL can be written 0 = DATATGGL is not writable bit 25 **DATATGGL:** Data Toggle bit (Host mode) When read, this bit indicates the current state of the endpoint data toggle. If DATATWEN = 1, this bit may be written with the required setting of the data toggle. If DATATWEN = 0, any value written to this bit is ignored. bit 24 **INCOMPRX:** Incomplete Packet Status bit 1 = The packet in the RX FIFO during a high-bandwidth Isochronous/Interrupt transfer is incomplete because parts of the data were not received 0 = Written by then software to clear this bit In anything other than Isochronous transfer, this bit will always return '0'. bit 23 **CLRDT:** Clear Data Toggle Control bit 1 = Reset the endpoint data toggle to '0' 0 = Leave endpoint data toggle alone bit 22 SENTSTALL: STALL Handshake Status bit (Device mode) 1 = STALL handshake is transmitted 0 = Written by the software to clear this bit **RXSTALL:** STALL Handshake Receive Status bit (*Host mode*) 1 = A STALL handshake has been received. An interrupt is generated. 0 = Written by the software to clear this bit bit 21 SENDSTALL: STALL Handshake Control bit (Device mode) 1 = Issue a STALL handshake 0 = Terminate stall condition **REQPKT:** IN Transaction Request Control bit (Host mode) 1 = Request an IN transaction. 0 = No request This bit is cleared when RXPKTRDY is set. bit 20 FLUSH: Flush FIFO Control bit 1 = Flush the next packet to be read from the endpoint RX FIFO. The FIFO pointer is reset and the RXPKTRDY bit is cleared. This should only be used when RXPKTRDY is set. If the FIFO is doublebuffered, FLUSH may need to be set twice to completely clear the FIFO. 0 = Normal FIFO operation This bit is automatically cleared. bit 19 DATAERR: Data Packet Error Status bit (Device mode) 1 = The data packet has a CRC or bit-stuff error.

- = The data packet has a CRC

- 0 = No data error

This bit is cleared when RXPKTRDY is cleared. This bit is only valid when the endpoint is operating in ISO mode. In Bulk mode, it always returns '0'.

#### DERRNAKT: Data Error/NAK Time-out Status bit (Host mode)

- 1 = The data packet has a CRC or bit-stuff error. In Bulk mode, the RX endpoint is halted following the receipt of NAK responses for longer than the time set as the NAK limit.

- 0 = No data or NAK time-out error

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |  |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | NRSTX            | NRST             |  |  |

| 23:16        | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-0             | R/W-1            | R/W-0            |  |  |

| 23.10        | LSEOF<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-1             | R/W-1            | R/W-1            |  |  |

| 10.0         | FSEOF<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-1             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R.W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | HSEOF<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 11-17: USBEOFRST: USB END-OF-FRAME/SOFT RESET CONTROL REGISTER

## Legend:

| Logonan           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-26 Unimplemented: Read as '0'

- bit 25 NRSTX: Reset of XCLK Domain bit

- 1 = Reset the XCLK domain, which is clock recovered from the received data by the PHY

- 0 = Normal operation

- bit 24 NRST: Reset of CLK Domain bit

- $\ensuremath{\mathtt{1}}$  = Reset the CLK domain, which is clock recovered from the peripheral bus

- 0 = Normal operation

- bit 23-16 LSEOF<7:0>: Low-Speed EOF bits These bits set the Low-Speed transaction in units of 1.067 μs (default setting is 121.6 μs) prior to the EOF to stop new transactions from beginning.

## bit 15-8 **FSEOF<7:0>:** Full-Speed EOF bits These bits set the Full-Speed transaction in units of 533.3 μs (default setting is 63.46 μs) prior to the EOF to stop new transactions from beginning.

#### bit 7-0 **HSEOF<7:0>:** Hi-Speed EOF bits These bits set the Hi-Speed transaction in units of 133.3 μs (default setting is 17.07 μs) prior to the EOF to stop new transactions from beginning.

# PIC32MZ Embedded Connectivity (EC) Family

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | _                 |                   | _                 | —                 | _                 | —                | —                |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | _                 |                   | —                 | _                 | —                | —                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8      | —                 | —                 | _                 |                   | —                 | _                 | —                | —                |

| 7.0       | R-0, HC           | R-0, HC           | R-0, HC           | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R-0              |

| 7:0       | BAD1              | BAD2              | DMTEVENT          |                   |                   |                   |                  | WINOPN           |

## REGISTER 15-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

| Legend:           | HC = Hardware Cleared |                       |                    |

|-------------------|-----------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared  | x = Bit is unknown |

| bit 31-8 | Unimplemented: Read as '0'                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | BAD1: Bad STEP1<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP1<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP1<7:0> value was not detected                                                                                     |

| bit 6    | BAD2: Bad STEP2<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP2<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP2<7:0> value was not detected                                                                                     |

| bit 5    | DMTEVENT: Deadman Timer Event bit                                                                                                   |

|          | 1 = Deadman timer event was detected (counter expired or bad STEP1<7:0> or STEP2<7:0> value was entered prior to counter increment) |

|          | 0 = Deadman timer even was not detected                                                                                             |

| bit 4-1  | Unimplemented: Read as '0'                                                                                                          |

| bit 0    | WINOPN: Deadman Timer Clear Window bit                                                                                              |

|          | 1 = Deadman timer clear window is open                                                                                              |

|          | 0 = Deadman timer clear window is not open                                                                                          |

|          |                                                                                                                                     |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-----------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0                  | U-0                   | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | —                 | -                    | -                     | _                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0                   | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | -                    | _                     | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0                   | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | -                    | —                     | —                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0                 | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | OC32              | OCFLT <sup>(1)</sup> | OCTSEL <sup>(2)</sup> |                   | OCM<2:0>         |                  |

### REGISTER 18-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

- 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 **OCFLT:** PWM Fault Condition Status bit<sup>(1)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 OCTSEL: Output Compare Timer Select bit<sup>(2)</sup>

- 1 = Timery is the clock source for this Output Compare module

- 0 = Timerx is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

- **2:** Refer to Table 18-1 for Timerx and Timery selections.

## 19.1 SPI Control Registers

## TABLE 19-1: SPI1 THROUGH SPI6 REGISTER MAP

| ess                         |                                 |               |               |         |        |              |              |              |           | Bi      | ts      |           |        |          |             |          |        |         |            |

|-----------------------------|---------------------------------|---------------|---------------|---------|--------|--------------|--------------|--------------|-----------|---------|---------|-----------|--------|----------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9      | 24/8    | 23/7    | 22/6      | 21/5   | 20/4     | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 1000                        | SPI1CON                         | 31:16         | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FI           | RMCNT<2:0 | )>      | MCLKSEL | —         | —      | —        | —           | —        | SPIFE  | ENHBUF  | 0000       |

| 1000                        | SFILCON                         | 15:0          | ON            | -       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE     | SSEN    | CKP       | MSTEN  | DISSDI   | STXISE      | EL<1:0>  | SRXIS  | EL<1:0> | 0000       |

| 1010                        | SPI1STAT                        | 31:16         | —             | —       | —      |              |              | BUFELM<4:    | :0>       |         | —       | —         | —      |          | TX          | BUFELM<4 |        |         | 0000       |

| 1010                        |                                 | 15:0          | _             | —       | —      | FRMERR       | SPIBUSY      | —            | —         | SPITUR  | SRMT    | SPIROV    | SPIRBE | —        | SPITBE      |          | SPITBF | SPIRBF  | 0008       |

| 1020                        | SPI1BUF                         | 31:16<br>15:0 |               |         |        |              |              |              |           | DATA<   | :31:0>  |           |        |          |             |          |        |         | 0000       |

| 1020                        | SPI1BRG                         | 31:16         |               | —       | —      | _            | —            | _            | _         | _       | _       | _         | —      | —        | _           | —        | —      | —       | 0000       |

| 1030                        | SFIIDKG                         | 15:0          |               |         | —      |              |              |              |           |         | E       | 8RG<12:0> |        |          |             |          |        |         | 0000       |

|                             |                                 | 31:16         | —             | _       | —      | _            | —            | —            | —         | _       | —       | —         |        | _        | —           |          | —      | —       | 0000       |

| 1040                        | SPI1CON2                        | 15:0          | SPI<br>SGNEXT | _       | —      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR  | AUDEN   | —         | _      | _        | AUD<br>MONO | —        | AUDMO  | DD<1:0> | 0000       |

| 1200                        | SPI2CON                         | 31:16         | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FI           | RMCNT<2:0 | )>      | MCLKSEL | —         | _      | _        | —           |          | SPIFE  | ENHBUF  | 0000       |

| 1200                        | 01 120011                       | 15:0          | ON            | —       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE     | SSEN    | CKP       | MSTEN  | DISSDI   | STXISE      |          |        | EL<1:0> | 0000       |

| 1210                        | SPI2STAT                        | 31:16         | _             | _       |        |              |              | BUFELM<4:    | :0>       |         | —       | —         |        |          |             | BUFELM<4 |        | 1       | 0000       |

| 1210                        |                                 | 15:0          | _             | —       | —      | FRMERR       | SPIBUSY      | —            |           | SPITUR  | SRMT    | SPIROV    | SPIRBE | —        | SPITBE      |          | SPITBF | SPIRBF  |            |

| 1220                        | SPI2BUF                         | 31:16<br>15:0 |               |         |        |              |              |              |           | DATA<   | :31:0>  |           |        |          |             |          |        |         | 0000       |

| 1230                        | SPI2BRG                         | 31:16         | _             | _       | —      |              | —            | _            | —         |         | —       | —         | —      | —        | —           | —        | —      | —       | 0000       |

| 1230                        |                                 | 15:0          | _             | _       | —      | _            | _            | _            | —         |         |         |           |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16         | —             | _       | —      |              | _            | —            | —         | —       | _       | —         |        |          | —           | _        | _      | —       | 0000       |

| 1240                        | SPI2CON2                        | 15:0          | SPI<br>SGNEXT | —       | —      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR  | AUDEN   | —         | —      | —        | AUD<br>MONO | —        | AUDMO  |         | 0000       |

| 1400                        | SPI3CON                         | 31:16         | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      |              | RMCNT<2:0 |         | MCLKSEL | —         | _      | —        | —           |          | SPIFE  | ENHBUF  |            |

| 1100                        |                                 | 15:0          | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE     | SSEN    | CKP       | MSTEN  | DISSDI   | STXISE      |          | SRXIS  | EL<1:0> | 0000       |

| 1410                        | SPI3STAT                        | 31:16         | _             | _       |        |              |              | BUFELM<4:    | :0>       | 0017110 | -       | -         | -      |          |             | BUFELM<4 |        | 000005  | 0000       |

|                             |                                 | 15:0          | —             | —       | —      | FRMERR       | SPIBUSY      | _            | _         | SPITUR  | SRMT    | SPIROV    | SPIRBE | _        | SPITBE      |          | SPITBF | SPIRBF  | 0008       |

| 1420                        | SPI3BUF                         | 31:16<br>15:0 |               |         |        |              |              |              |           | DATA<   | :31:0>  |           |        |          |             |          |        |         | 0000       |

| 1/130                       | SPI3BRG                         | 31:16         | _             | —       | —      |              | —            | -            | —         | -       | _       | _         | —      | _        | —           |          | —      | —       | 0000       |

| 1430                        |                                 | 15:0          | _             | —       | —      | _            | —            |              | —         |         |         |           |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16         | —             | —       | —      | —            | —            | —            | —         | —       | —       | —         | —      | —        | —           | —        | -      | —       | 0000       |

| 1440                        | SPI3CON2                        | 15:0          | SPI<br>SGNEXT | —       | —      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR  | AUDEN   | —         | _      | _        | AUD<br>MONO | —        | AUDMO  | DC<1:0> | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | —                 |                   |                   |                   |                   |                  | _                |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | _                 | —                 | _                 | _                 | _                 | F                 | REGSEL<2:0>      |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | M                 | IEMTYPE<2:0       | )>                |                   | M                 | EMSIZE<4:0>       | (1)              |                  |  |

## **REGISTER 24-2:** EBIMSKx: EXTERNAL BUS INTERFACE ADDRESS MASK REGISTER ('x' = 0-3)

## Legend:

| R = Readable bit  | W = Writable bit | = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|---------------------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                              | x = Bit is unknown |  |  |

#### bit 31-11 Unimplemented: Read as '0'

| bit 10-8 | REGSEL<2:0>: Timing Register Set for Chip Select 'x' bits                                                      |

|----------|----------------------------------------------------------------------------------------------------------------|

|          | 111 = Reserved                                                                                                 |

|          | •                                                                                                              |

|          | •                                                                                                              |

|          | •<br>011 = Reserved                                                                                            |

|          | 011 = Reserved<br>010 = Use EBISMT2                                                                            |

|          | 001 = Use EBISMT2                                                                                              |

|          | 000 = Use EBISMT0                                                                                              |

| bit 7-5  |                                                                                                                |

| DIL 7-5  | <b>MEMTYPE&lt;2:0&gt;:</b> Select Memory Type for Chip Select 'x' bits                                         |

|          | 111 = Reserved                                                                                                 |

|          | •                                                                                                              |

|          | •                                                                                                              |

|          | 011 = Reserved                                                                                                 |

|          | 010 = NOR-Flash                                                                                                |

|          | 001 = SRAM                                                                                                     |

|          | 000 = Reserved                                                                                                 |

| bit 4-0  | <b>MEMSIZE</b> <4:0>: Select Memory Size for Chip Select 'x' bits <sup>(1)</sup>                               |

|          | 11111 = Reserved                                                                                               |

|          | •                                                                                                              |

|          | •                                                                                                              |

|          | 01010 = Reserved                                                                                               |

|          | 01001 = 16  MB                                                                                                 |

|          | 01000 = 8 MB                                                                                                   |

|          | 00111 = 4 MB                                                                                                   |

|          | 00110 = 2 MB                                                                                                   |

|          | 00101 <b>1 MD</b>                                                                                              |

|          | 00101 = 1 MB                                                                                                   |

|          | 00101 = 1  MB<br>00100 = 512  KB                                                                               |

|          | 00100 = 512 KB<br>00011 = 256 KB                                                                               |

|          | 00100 = 512 KB<br>00011 = 256 KB<br>00010 = 128 KB                                                             |

|          | 00100 = 512 KB<br>00011 = 256 KB<br>00010 = 128 KB<br>00001 = 64 KB (smaller memories alias within this range) |

|          | 00100 = 512 KB<br>00011 = 256 KB<br>00010 = 128 KB                                                             |

## **Note 1:** The specified value for these bits depends on the number of available address lines. Refer to the specific device pin table (Table 2 through Table 5) for the available address lines.

## 26.1 Crypto Engine Control Registers

## TABLE 26-2: CRYPTO ENGINE REGISTER MAP

| ess                         |                  | 6             |                             |         |       |       |          |       |        | E      | Bits          |       |        |        |         |         |         |        | 6          |

|-----------------------------|------------------|---------------|-----------------------------|---------|-------|-------|----------|-------|--------|--------|---------------|-------|--------|--------|---------|---------|---------|--------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15                       | 30/14   | 29/13 | 28/12 | 27/11    | 26/10 | 25/9   | 24/8   | 23/7          | 22/6  | 21/5   | 20/4   | 19/3    | 18/2    | 17/1    | 16/0   | All Resets |

| 5000                        | CEVER            | 31:16         |                             |         |       |       |          |       |        |        |               |       |        |        |         | 0000    |         |        |            |

| 3000                        | OEVER            | 15:0          |                             |         |       |       |          |       |        |        |               |       |        |        |         | 0000    |         |        |            |

| 5004                        | CECON            | 31:16         | _                           |         |       |       |          |       |        |        |               |       |        |        | —       | 0000    |         |        |            |

|                             |                  | 15:0          | -                           | —       | —     | —     | —        | —     | —      | —      | —             | SWRST | SWAPEN | —      | —       | BDPCHST | BDPPLEN | DMAEN  | 0000       |

| 5008                        | CEBDADDR         | 31:16         |                             |         |       |       |          |       |        | BDPAD  | DR<31:0>      |       |        |        |         |         |         |        | 0000       |

|                             | -                | 15:0          |                             | 0000    |       |       |          |       |        |        |               |       |        |        |         |         |         |        |            |

| 500C                        | CEBDPADDR        | 31:16         |                             |         |       |       |          |       |        | BASEAD | DDR<31:0      | >     |        |        |         |         |         |        | 0000       |

|                             |                  | 15:0          |                             |         |       | -     |          |       |        | 05.4.0 |               |       |        | DDOT 1 | TE 0.0  |         | OTADT   |        | 0000       |

| 5010                        | CESTAT           | 31:16<br>15:0 | ER                          | RMODE<2 | 2:0>  | E     | RROP<2:0 | >     | ERRPHA |        | —<br>RL<15:0> | —     |        | BDSTA  | TE<3:0> |         | START   | ACTIVE |            |

|                             |                  | 31:16         | _                           |         |       |       |          | _     |        |        |               |       |        |        |         |         |         | _      | 0000       |

| 5014                        | CEINTSRC         | 15:0          |                             | _       | _     | _     |          |       |        | _      | _             |       | _      | _      | AREIF   | PKTIF   |         | PENDIF |            |

|                             |                  | 31:16         |                             |         |       |       | _        |       |        |        |               |       |        |        |         |         |         | FENDIF | 0000       |

| 5018                        | CEINTEN          | 15:0          |                             |         |       |       |          |       |        | _      |               |       | _      |        | AREIE   | PKTIE   | CBDIE   | PENDIE |            |

|                             |                  | 31:16         |                             | _       | _     | _     | _        |       |        |        | _             |       |        | _      |         | _       | _       |        | 0000       |

| 501C                        | CEPOLLCON        | 15:0          |                             |         |       |       |          |       |        | BDPPLO | CON<15:0      |       | l l    |        |         |         |         |        | 0000       |

|                             |                  | 31:16         |                             |         |       |       |          |       |        |        |               |       | 0000   |        |         |         |         |        |            |

| 5020                        | CEHDLEN          | 15:0          | 0 — — — — — — — HDRLEN<7:0> |         |       |       |          |       |        |        |               |       | 0000   |        |         |         |         |        |            |

|                             |                  | 31:16         | 16                          |         |       |       |          |       |        |        |               |       | 0000   |        |         |         |         |        |            |

| 5024                        | CETRLLEN         | 15:0          | _                           | _       | _     | _     | _        | _     | _      | _      |               |       |        | TRLRL  | EN<7:0> |         |         |        | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | 29/21/13/5 28/20/12/4 2     |             | Bit Bit<br>7/19/11/3 26/18/10/2 |       | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-----------------------------|-------------|---------------------------------|-------|------------------|--|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0 R/W-0 R/W-0 R/W-0 R/V |             |                                 |       |                  |  |  |  |  |  |

| 31.24        | FLTEN15           | MSEL1             | 5<1:0>            |                             | FSEL15<4:0> |                                 |       |                  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0                       | R/W-0       | R/W-0                           | R/W-0 | R/W-0            |  |  |  |  |  |

| 23.10        | FLTEN14           | MSEL1             | 4<1:0>            | FSEL14<4:0>                 |             |                                 |       |                  |  |  |  |  |  |

| 15:8         | R/W-0             | R/W-0 R/W-0       |                   | R/W-0                       | R/W-0       | R/W-0                           | R/W-0 | R/W-0            |  |  |  |  |  |

| 10.0         | FLTEN13           | MSEL1             | 3<1:0>            |                             | F           | SEL13<4:0>                      |       |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0                       | R/W-0       | R/W-0                           | R/W-0 | R/W-0            |  |  |  |  |  |

| 7:0          | FLTEN12           | MSEL1             | 2<1:0>            |                             | F           | SEL12<4:0>                      |       |                  |  |  |  |  |  |

### REGISTER 29-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN15: Filter 15 Enable bit                                                                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                                                          |

| bit 30-29 | MSEL15<1:0>: Filter 15 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected                                                                                          |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                       |

| bit 28-24 | FSEL15<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN14: Filter 14 Enable bit                                                                                            |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                   |

| bit 22-21 | MSEL14<1:0>: Filter 14 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected                                                                                          |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                       |

| bit 20-16 | FSEL14<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                               |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                               |

|           |                                                                                                                          |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## 32.1 Comparator Voltage Reference Control Registers

## TABLE 32-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| ess                         |                                 | æ         | Bits  |       |       |       |       |       |      |      |      |       |      |       |      |      | s    |      |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|------|------|------|------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 0500                        | CVRCON                          | 31:16     | _     | —     | _     | —     | —     | -     | —    | —    | —    | —     | —    | —     | —    | —    | —    | _    | 0000      |

| 0200                        | CVRCON                          | 15:0      | ON    | —     | _     | _     | —     | —     | _    | —    | —    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The register in this table has corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

## REGISTER 34-9: CFGEBIC: EXTERNAL BUS INTERFACE CONTROL PIN CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

|              |                   | EBI<br>RDYINV3    | EBI<br>RDYINV2    | EBI<br>RDYINV1    | _                 | EBI<br>RDYEN3     | EBI<br>RDYEN2    | EBI<br>RDYEN1    |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

|              |                   | -                 | _                 | -                 | _                 | —                 | EBIRDYLVL        | EBIRPEN          |

| 45-0         | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | EBIWEEN           | EBIOEEN           | —                 | _                 | EBIBSEN1         | EBIBSEN0         |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

|              | EBICSEN3          | EBICSEN2          | EBICSEN1          | EBICSEN0          | _                 | _                 | EBIDEN1          | EBIDEN0          |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 31    | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 30    | EBIRDYINV3: EBIRDY3 Inversion Control bit                                                            |

|           | 1 = Invert EBIRDY3 pin before use                                                                    |

|           | 0 = Do not invert EBIRDY3 pin before use                                                             |

| bit 29    | EBIRDYINV2: EBIRDY2 Inversion Control bit                                                            |

|           | 1 = Invert EBIRDY2 pin before use                                                                    |

|           | 0 = Do not invert EBIRDY2 pin before use                                                             |

| bit 28    | EBIRDYINV1: EBIRDY1 Inversion Control bit                                                            |

|           | <ul><li>1 = Invert EBIRDY1 pin before use</li><li>0 = Do not invert EBIRDY1 pin before use</li></ul> |

| bit 27    |                                                                                                      |

|           | Unimplemented: Read as '0'                                                                           |

| bit 26    | EBIRDYEN3: EBIRDY3 Pin Enable bit                                                                    |

|           | 1 = EBIRDY3 pin is enabled for use by the EBI module                                                 |

|           | 0 = EBIRDY3 pin is available for general use                                                         |

| bit 25    | EBIRDYEN2: EBIRDY2 Pin Enable bit                                                                    |

|           | 1 = EBIRDY2 pin is enabled for use by the EBI module                                                 |

|           | 0 = EBIRDY2 pin is available for general use                                                         |

| bit 24    | EBIRDYEN1: EBIRDY1 Pin Enable bit                                                                    |

|           | 1 = EBIRDY1 pin is enabled for use by the EBI module                                                 |

|           | 0 = EBIRDY1 pin is available for general use                                                         |

| bit 23-18 | Unimplemented: Read as '0'                                                                           |

| bit 17    | EBIRDYLVL: EBIRDYx Pin Sensitivity Control bit                                                       |

|           | 1 = Use level detect for EBIRDYx pins                                                                |

|           | 0 = Use edge detect for EBIRDYx pins                                                                 |

| bit 16    | EBIRPEN: EBIRP Pin Sensitivity Control bit                                                           |

|           | $1 = \overline{EBIRP}$ pin is enabled for use by the EBI module                                      |

|           | 0 = EBIRP pin is available for general use                                                           |

bit 15-14 **Unimplemented:** Read as '0'

Note: When EBIMD = 1, the bits in this register are ignored and the pins are available for general use.

| DC CHARACTERISTICS |       |                                                                              | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                     |        |            |             |  |

|--------------------|-------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------|------------|-------------|--|

| Param.<br>No.      | Sym.  | Characteristics                                                              | Min.                                                                                                                                            | Typ. <sup>(1)</sup> | Max.   | Units      | Conditions  |  |

| D130a              | Ер    | Cell Endurance                                                               | 10,000                                                                                                                                          | _                   | _      | E/W        | Without ECC |  |