Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG                         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-QFN (9x9)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048ecg064t-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                          |             |                |                                |  |  |  |  |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|--------------------------------|--|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                    |  |  |  |  |

| ERXD0    | 61                     | 41              | B32             | 81                       | Ι           | ST             | Ethernet Receive Data 0        |  |  |  |  |

| ERXD1    | 58                     | 42              | B26             | 66                       | I           | ST             | Ethernet Receive Data 1        |  |  |  |  |

| ERXD2    | 57                     | 43              | A31             | 67                       | I           | ST             | Ethernet Receive Data 2        |  |  |  |  |

| ERXD3    | 56                     | 44              | A40             | 82                       |             | ST             | Ethernet Receive Data 3        |  |  |  |  |

| ERXERR   | 64                     | 35              | A30             | 65                       | -           | ST             | Ethernet Receive Error Input   |  |  |  |  |

| ERXDV    | 62                     | 12              | B40             | 101                      | I           | ST             | Ethernet Receive Data Valid    |  |  |  |  |

| ERXCLK   | 63                     | 16              | B12             | 27                       | I           | ST             | Ethernet Receive Clock         |  |  |  |  |

| ETXD0    | 2                      | 86              | A5              | 7                        | 0           | —              | Ethernet Transmit Data 0       |  |  |  |  |

| ETXD1    | 3                      | 85              | B4              | 8                        | 0           | —              | Ethernet Transmit Data 1       |  |  |  |  |

| ETXD2    | 43                     | 79              | B17             | 43                       | 0           | —              | Ethernet Transmit Data 2       |  |  |  |  |

| ETXD3    | 46                     | 80              | A22             | 44                       | 0           | —              | Ethernet Transmit Data 3       |  |  |  |  |

| ETXERR   | 50                     | 87              | B44             | 114                      | 0           | —              | Ethernet Transmit Error        |  |  |  |  |

| ETXEN    | 1                      | 77              | A57             | 120                      | 0           | —              | Ethernet Transmit Enable       |  |  |  |  |

| ETXCLK   | 51                     | 78              | B47             | 121                      | I           | ST             | Ethernet Transmit Clock        |  |  |  |  |

| ECOL     | 44                     | 10              | B33             | 83                       | Ι           | ST             | Ethernet Collision Detect      |  |  |  |  |

| ECRS     | 45                     | 11              | A47             | 100                      |             | ST             | Ethernet Carrier Sense         |  |  |  |  |

| EMDC     | 30                     | 70              | B39             | 99                       | 0           | —              | Ethernet Management Data Clock |  |  |  |  |

| EMDIO    | 49                     | 71              | A55             | 115                      | I/O         | —              | Ethernet Management Data       |  |  |  |  |

| Legend:  | CMOS = C               | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power         |  |  |  |  |

#### TABLE 1-16: ETHERNET MII I/O DESCRIPTIONS

Legend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output

PPS = Peripheral Pin Select

I = Input

#### TABLE 1-17: ETHERNET RMII PINOUT I/O DESCRIPTIONS

|          |                        | Pin Nu          | mber            |                          |             |                |                                   |  |  |  |  |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|--|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                       |  |  |  |  |

|          |                        |                 |                 | E                        | thernet I   | VII Interfac   | e                                 |  |  |  |  |

| ERXD0    | 61                     | 41              | B32             | 81                       | I           | ST             | Ethernet Receive Data 0           |  |  |  |  |

| ERXD1    | 58                     | 42              | B26             | 66                       | I           | ST             | Ethernet Receive Data 1           |  |  |  |  |

| ERXERR   | 64                     | 35              | A30             | 65                       | I           | ST             | Ethernet Receive Error Input      |  |  |  |  |

| ETXD0    | 2                      | 86              | A5              | 7                        | 0           | —              | Ethernet Transmit Data 0          |  |  |  |  |

| ETXD1    | 3                      | 85              | B4              | 8                        | 0           | —              | Ethernet Transmit Data 1          |  |  |  |  |

| ETXEN    | 1                      | 77              | A57             | 120                      | 0           | —              | Ethernet Transmit Enable          |  |  |  |  |

| EMDC     | 30                     | 70              | B39             | 99                       | 0           | —              | Ethernet Management Data Clock    |  |  |  |  |

| EMDIO    | 49                     | 71              | A55             | 115                      | I/O         | —              | Ethernet Management Data          |  |  |  |  |

| EREFCLK  | 63                     | 16              | B12             | 27                       | I           | ST             | Ethernet Reference Clock          |  |  |  |  |

| ECRSDV   | 62                     | 12              | B40             | 101                      | I           | ST             | Ethernet Carrier Sense Data Valid |  |  |  |  |

| Legend:  | CMOS = CI              | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power            |  |  |  |  |

Legend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog inputP = Power<math>O = OutputI = InputPPS = Peripheral Pin Select

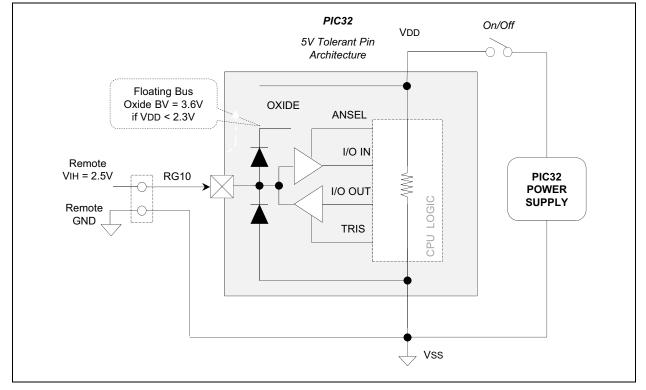

#### 2.10.2 5V TOLERANT INPUT PINS

The internal high side diode on 5V tolerant pins are bussed to an internal floating node, rather than being connected to VDD, as shown in Figure 2-7. Voltages on these pins, if VDD < 2.3V, should not exceed roughly 3.2V relative to Vss of the PIC32 device. Voltage of 3.6V or higher will violate the absolute maximum specification, and will stress the oxide layer separating the high side floating node, which impacts device reliability. If a remotely powered "digital-only" signal can be guaranteed to always be  $\leq$  3.2V relative to Vss on the PIC32 device side, a 5V tolerant pin could be used without the need for a digital isolator. This is assuming there is not a ground loop issue, logic ground of the two circuits not at the same absolute level, and a remote logic low input is not less than Vss - 0.3V.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3    | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0                  | U-0                  | U-0                  | U-0                  |

| 31.24        | —                 | —                 | _                 | —                    | _                    | _                    |                      | —                    |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0                  | U-0                  | U-0                  | U-0                  |

| 23:16        | —                 | —                 | _                 | —                    | _                    | _                    | _                    | _                    |

| 45.0         | R/W-1             | U-0               | U-0               | R/W-1                | R/W-1                | R/W-1                | R/W-1                | R/W-1                |

| 15:8         | LBWPULOCK         | —                 | _                 | LBWP4 <sup>(1)</sup> | LBWP3 <sup>(1)</sup> | LBWP2 <sup>(1)</sup> | LBWP1 <sup>(1)</sup> | LBWP0 <sup>(1)</sup> |

| 7.0          | R/W-1             | r-1               | U-0               | R/W-1                | R/W-1                | R/W-1                | R/W-1                | R/W-1                |

| 7:0          | UBWPULOCK         |                   | _                 | UBWP4 <sup>(1)</sup> | UBWP3 <sup>(1)</sup> | UBWP2 <sup>(1)</sup> | UBWP1 <sup>(1)</sup> | UBWP0 <sup>(1)</sup> |

#### REGISTER 5-7: NVMBWP: FLASH BOOT (PAGE) WRITE-PROTECT REGISTER

| Legend:           |                  | r = Reserved         |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| bit 15    | LBWPULOCK: Lower Boot Alias Write-protect Unlock bit                                                                                                                                                            |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1 = LBWPx bits are not locked and can be modified                                                                                                                                                               |

|           | 0 = LBWPx bits are locked and cannot be modified                                                                                                                                                                |

|           | This bit is only clearable and cannot be set except by any reset.                                                                                                                                               |

| bit 14-13 | Unimplemented: Read as '0'                                                                                                                                                                                      |

| bit 12    | LBWP4: Lower Boot Alias Page 4 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|           | <ul> <li>1 = Write protection for physical address 0x01FC10000 through 0x1FC13FFF enabled</li> <li>0 = Write protection for physical address 0x01FC10000 through 0x1FC13FFF disabled</li> </ul>                 |

| bit 11    | LBWP3: Lower Boot Alias Page 3 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|           | <ul> <li>1 = Write protection for physical address 0x01FC0C000 through 0x1FC0FFFF enabled</li> <li>0 = Write protection for physical address 0x01FC0C000 through 0x1FC0FFFF disabled</li> </ul>                 |

| bit 10    | LBWP2: Lower Boot Alias Page 2 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|           | <ul> <li>1 = Write protection for physical address 0x01FC08000 through 0x1FC0BFFF enabled</li> <li>0 = Write protection for physical address 0x01FC08000 through 0x1FC0BFFF disabled</li> </ul>                 |

| bit 9     | LBWP1: Lower Boot Alias Page 1 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|           | <ul> <li>1 = Write protection for physical address 0x01FC04000 through 0x1FC07FFF enabled</li> <li>0 = Write protection for physical address 0x01FC04000 through 0x1FC07FFF disabled</li> </ul>                 |

| bit 8     | LBWP0: Lower Boot Alias Page 0 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|           | <ul> <li>1 = Write protection for physical address 0x01FC00000 through 0x1FC03FFF enabled</li> <li>0 = Write protection for physical address 0x01FC00000 through 0x1FC03FFF disabled</li> </ul>                 |

| bit 7     | UBWPULOCK: Upper Boot Alias Write-protect Unlock bit                                                                                                                                                            |

|           | <ul> <li>1 = UBWPx bits are not locked and can be modified</li> <li>0 = UBWPx bits are locked and cannot be modified</li> <li>This bit is only user-clearable and cannot be set except by any reset.</li> </ul> |

| bit 6     | Reserved: This bit is reserved for use by development tools                                                                                                                                                     |

| bit 5     | Unimplemented: Read as '0'                                                                                                                                                                                      |

| Note 1:   | These bits are only available when the NVMKEY unlock sequence is performed and the associated Lock bit (LBWPULOCK or UBWPULOCK) is set.                                                                         |

Note: The bits in this register are only writable when the NVMKEY unlock sequence is followed.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        |                   | _                 | _                 |                   | IP3<2:0>          |                   | IS3<             | :1:0>            |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | —                 | —                 | —                 |                   | IP2<2:0>          |                   | IS2<             | :1:0>            |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0 R/W-0       |                  | R/W-0            |

| 15.0         | _                 | —                 |                   |                   | IP1<2:0>          |                   | IS1<             | 1:0>             |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   | _                 |                   |                   | IP0<2:0>          |                   | IS0<             | :1:0>            |

#### REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP3<2:0>: Interrupt Priority bits                            |

|-----------|--------------------------------------------------------------|

|           | 111 = Interrupt priority is 7                                |

|           | •                                                            |

|           | •                                                            |

|           | •                                                            |

|           | 010 = Interrupt priority is 2                                |

|           | 001 = Interrupt priority is 1<br>000 = Interrupt is disabled |

|           | 1                                                            |

| bit 25-24 | IS3<1:0>: Interrupt Subpriority bits                         |

|           | 11 = Interrupt subpriority is 3                              |

|           | 10 = Interrupt subpriority is 2                              |

|           | 01 = Interrupt subpriority is 1                              |

|           | 00 = Interrupt subpriority is 0                              |

|           | Unimplemented: Read as '0'                                   |

| bit 20-18 | IP2<2:0>: Interrupt Priority bits                            |

|           | 111 = Interrupt priority is 7                                |

|           | •                                                            |

|           | •                                                            |

|           | 010 = Interrupt priority is 2                                |

|           | 001 = Interrupt priority is 1                                |

|           | 000 = Interrupt is disabled                                  |

| bit 17-16 | IS2<1:0>: Interrupt Subpriority bits                         |

|           | 11 = Interrupt subpriority is 3                              |

|           | 10 = Interrupt subpriority is 2                              |

|           | 01 = Interrupt subpriority is 1                              |

|           | 00 = Interrupt subpriority is 0                              |

| bit 15-13 | Unimplemented: Read as '0'                                   |

|           | -                                                            |

| Note:     | This register represents a generic defin                     |

|           |                                                              |

Note: This register represents a generic definition of the IPCx register. Refer to Table 7-2 for the exact bit definitions.

#### 8.2 Oscillator Control Registers

#### **TABLE 8-2: OSCILLATOR CONFIGURATION REGISTER MAP** Virtual Address (BF80\_#) Bits Bit Range Register Name 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 FRCDIV<2:0> DRMEN SOSCRDY 31:16 OSCCON 1200 15:0 COSC<2:0> NOSC<2:0> CLKLOCK ULOCK \_ |

|      |                  |                   |    |               |      |    |            |   |             |        |           |      |                     | -      | -          |                |        |   |      |

|------|------------------|-------------------|----|---------------|------|----|------------|---|-------------|--------|-----------|------|---------------------|--------|------------|----------------|--------|---|------|

| 1210 | OSCTUN           | 31:16             | —  | —             | —    | —  | —          | - | —           | —      | —         | —    | —                   |        | -          | —              | _      | — | 0000 |

| 1210 | OSCION           | 15:0              | —  | —             | —    | —  | —          |   | —           | —      | —         | —    |                     |        |            | <b> </b> <5:0> |        |   | 0000 |

| 1220 | SPLLCON          | 31:16             | _  | —             | —    | —  | —          |   | PLLODIV<2:( |        | —         |      |                     | PL     | LMULT<6:   |                |        |   | 01xx |

|      |                  | 15:0              | _  | —             | _    | —  | —          |   | PLLIDIV<2:0 |        | PLLICLK   | —    | — — — PLLRANGE<2:0> |        |            |                |        |   | 0x0x |

| 1280 | REF01CON         | 31:16             | —  |               |      |    |            |   |             |        | DIV<14:0> |      |                     |        |            |                |        |   | 0000 |

| .200 |                  | 15:0              | ON | —             | SIDL | OE | RSLP       | — | DIVSWEN     | ACTIVE | —         | —    | —                   |        |            | ROSE           | L<3:0> |   | 0000 |

| 1290 | REF01TRIM        | 31:16 ROTRIM<8:0> |    |               |      |    |            |   |             |        | —         | 0000 |                     |        |            |                |        |   |      |

|      |                  | 15:0              | —  | —             | —    | —  | —          | — | —           | —      | —         | —    | —                   | —      | —          | —              | —      | — | 0000 |

| 12A0 | REF02CON         | 31:16             |    |               |      |    |            |   |             |        |           |      |                     |        | 0000       |                |        |   |      |

| -    |                  | 15:0              |    |               |      |    |            |   |             |        |           |      |                     | L<3:0> | 1          | 0000           |        |   |      |

| 12B0 | <b>REFO2TRIM</b> | 31:16             |    | •             | •    |    | OTRIM<8:0> |   | -           |        |           | —    | —                   | —      | —          | —              | —      | — | 0000 |

| -    | -                | 15:0              | —  | —             | —    | —  | —          | — | —           | —      | —         | _    | —                   | —      | -          | —              | —      | — | 0000 |

| 12C0 | <b>REFO3CON</b>  | 31:16             |    |               |      |    |            |   |             |        |           |      |                     | 0000   |            |                |        |   |      |

|      |                  | 15:0              | ON | —             | SIDL | OE | RSLP       | _ | DIVSWEN     | ACTIVE | -         | _    | _                   | _      |            | ROSE           | L<3:0> | 1 | 0000 |

| 12D0 | <b>REFO3TRIM</b> | 31:16             |    | <b>-</b>      | r    |    | OTRIM<8:0> |   |             |        |           |      | _                   | _      | _          | _              | _      | — | 0000 |

|      |                  | 15:0              | _  | —             | —    | —  | -          | _ | —           | -      |           | _    | —                   | _      | —          | —              | —      | — | 0000 |

| 12E0 | REFO4CON         | 31:16             | _  |               |      |    |            |   |             |        | DIV<14:0> |      |                     |        |            |                |        |   | 0000 |

|      |                  | 15:0              | ON | —             | SIDL | OE | RSLP       | _ | DIVSWEN     | ACTIVE | -         | _    | _                   | _      |            |                | L<3:0> | 1 | 0000 |

| 12F0 | <b>REFO4TRIM</b> | 31:16             |    |               |      |    | OTRIM<8:0> |   | 1           |        |           | —    | —                   | —      | —          | _              | —      | — | 0000 |

|      |                  | 15:0              | _  | -             | -    | _  | _          | — | -           | -      |           |      | -                   | _      | _          | _              | _      |   | 0000 |

| 1300 | PB1DIV           | 31:16             | _  | -             | _    | —  |            | — | -           | _      | _         | _    | _                   |        | -          | —              |        | — | 0000 |

|      |                  | 15:0              |    |               | _    | _  | PBDIVRDY   | _ |             |        | _         |      |                     | F      | BDIV<6:0   | 1              |        |   | 8801 |

| 1310 | PB2DIV           | 31:16             | -  |               | -    | _  |            | _ | -           | _      |           |      | —                   |        | -          | -              |        | _ | 0000 |

|      |                  | 15:0              | ON | _             | _    | _  | PBDIVRDY   | _ |             |        |           |      |                     |        | BDIV<6:0   |                |        |   | 8801 |

| 1320 | PB3DIV           | 31:16<br>15:0     | ON | _             | -    | _  |            |   | -           | _      |           | —    | —                   |        | BDIV<6:0>  | —              | _      | — | 0000 |

|      |                  |                   |    | -             | -    | _  |            |   | -           | -      | _         | _    |                     | - F    |            | <u> </u>       |        |   | 8801 |

| 1330 | PB4DIV           | 31:16<br>15:0     | ON | -             | -    | -  |            | _ |             | -      | _         |      | _                   |        | BDIV<6:0>  |                |        | _ | 0000 |

|      |                  |                   |    | -             | -    | -  | PBDIVRDY   |   |             | _      |           |      |                     | - F    | BDIV<6:05  |                |        | _ | 8801 |

| 1340 | PB5DIV           | 31:16<br>15:0     | ON | -             | -    | _  |            |   | -           | -      | _         | —    |                     |        |            | -              | _      | _ | 0000 |

|      |                  |                   | ON | _             | -    | -  | PBDIVRDY   | _ |             | _      |           |      |                     | F      | BDIV<6:0   | >              |        |   | 8801 |

| 1360 | PB7DIV           | 31:16<br>15:0     | ON | _             | _    | _  |            | _ |             | _      | _         | _    | _                   |        | BDIV<6:0>  | —              |        |   | 0000 |

|      |                  |                   | -  | -             | -    | _  | FBUIVRDY   | — |             | _      |           |      |                     |        | ט> עועם:0  | -              |        |   | 8800 |

| 1370 | PB8DIV           | 31:16<br>15:0     | ON | _             |      | _  |            |   | -           | _      | _         |      | —                   |        |            | —              | _      | — | 0000 |

| egen |                  |                   | -  | eset; — = uni | —    | —  |            |   | -           | —      | _         |      |                     | F      | PBDIV<6:0> | >              |        |   | 8801 |

21/5

SLOCK

20/4

SLPEN

19/3

CF

18/2

|

17/1

SOSCEN

1: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

Note

All Resets<sup>(1)</sup>

0000

xx0x

16/0

OSWEN

#### TABLE 11-1: USB REGISTER MAP (CONTINUED)

|                    |                  |               |       |                                             |       | (00111 |       |         |              |               | Bits                      |           |              |        |           |              |             |            |            |

|--------------------|------------------|---------------|-------|---------------------------------------------|-------|--------|-------|---------|--------------|---------------|---------------------------|-----------|--------------|--------|-----------|--------------|-------------|------------|------------|

| Virtual<br>Address | Register<br>Name | Bit Range     | 31/15 | 30/14                                       | 29/13 | 28/12  | 27/11 | 26/10   | 25/9         | 24/8          | 23/7                      | 22/6      | 21/5         | 20/4   | 19/3      | 18/2         | 17/1        | 16/0       | All Resets |

| 3170               | USB<br>E7CSR0    | 31:16<br>15:0 |       | L                                           |       | L      | L     | L       | Inde         | exed by the s | same bits in U            | SBIE7CSR0 | L            | l      | •         |              |             |            | 0000       |

| 3174               | USB<br>E7CSR1    | 31:16<br>15:0 |       | Indexed by the same bits in USBIE7CSR1 0000 |       |        |       |         |              |               |                           |           |              |        |           |              |             |            |            |

| 3178               | USB<br>E7CSR2    | 31:16<br>15:0 |       | Indexed by the same bits in USBIE7CSR2 0000 |       |        |       |         |              |               |                           |           |              |        |           |              |             |            |            |

| 317C               | USB<br>E7CSR3    | 31:16<br>15:0 |       | Indexed by the same bits in USBIE7CSR3      |       |        |       |         |              |               |                           |           |              |        |           |              |             |            |            |

| 3200               | USB              | 31:16         | _     | —                                           | —     | —      | —     | —       | —            | —             | -                         | _         | —            | —      | _         | _            | _           | _          | 000        |

|                    | DMAINT           | 15:0          | _     | _                                           | —     | _      | —     | _       |              | —             | DMA8IF                    | DMA7IF    | DMA6IF       | DMA5IF | DMA4IF    | DMA3IF       | DMA2IF      | DMA1IF     | _          |

| 3204               | USB<br>DMA1C     | 31:16<br>15:0 |       | _                                           | _     | _      | _     |         | <br>STM<1:0> | —<br>DMAERR   | —                         |           | —<br>EP<3:0> | _      | <br>DMAIE | —<br>DMAMODE | —<br>DMADIR | —<br>DMAEN | 000        |

| 3208               | USB<br>DMA1A     | 31:16<br>15:0 |       |                                             |       |        |       | DWADIN  | 5110((1.0))  | DMA           | ADDR<31:16                | >         | 1 <0.02      |        | DWAL      | DIMANIODE    | DNIADIR     | DWALN      | 000        |

| 320C               | USB<br>DMA1N     | 31:16         |       |                                             |       |        |       |         |              | DMAG          | ADDR<15:0:<br>COUNT<31:10 | i>        |              |        |           |              |             |            | 000        |

|                    |                  | 15:0<br>31:16 | _     |                                             |       |        |       |         |              | DMA           | COUNT<15:0                | >         |              |        | 1         |              | 1           | _          | 000        |

| 3214               | USB<br>DMA2C     | 15:0          | _     |                                             |       |        |       | DMABR:  | <br>STM<1:0> | <br>DMAERR    |                           |           | <br>EP<3:0>  | _      | DMAIE     | <br>DMAMODE  | <br>DMADIR  | DMAEN      | _          |

| 3218               | USB<br>DMA2A     | 31:16<br>15:0 |       |                                             |       |        |       | 0101011 |              | DMA           | ADDR<31:16                | >         |              |        | 010002    | 5            | 5111,011    | Blister    | 000        |

|                    | USB              | 31:16         |       |                                             |       |        |       |         |              |               | COUNT<31:10               |           |              |        |           |              |             |            | 000        |

| 321C               | DMA2N            | 15:0          |       |                                             |       |        |       |         |              | DMA           | COUNT<15:0                | >         |              |        |           |              |             |            | 000        |

| 3224               | USB              | 31:16         |       | —                                           | —     |        |       |         |              | _             | _                         | _         | _            |        | —         | -            | —           | -          | 000        |

| 0224               | DMA3C            | 15:0          | —     | —                                           | —     | —      |       | DMABR   | STM<1:0>     | DMAERR        |                           |           | EP<3:0>      |        | DMAIE     | DMAMODE      | DMADIR      | DMAEN      | _          |

| 3228               | USB<br>DMA3A     | 31:16<br>15:0 |       |                                             |       |        |       |         |              |               | ADDR<31:16                |           |              |        |           |              |             |            | 000        |

|                    |                  | 31:16         |       |                                             |       |        |       |         |              |               | ADDR<15:0:<br>COUNT<31:10 |           |              |        |           |              |             |            | 000        |

| 322C               | USB<br>DMA3N     | 15:0          |       |                                             |       |        |       |         |              |               | COUNT<15:0                |           |              |        |           |              |             |            | 000        |

| 3234               | USB<br>DMA4C     | 31:16         | _     | -                                           | —     | —      | _     | —       | —            | —             |                           | —         | -            |        | -         | -            | -           | —          | 000        |

|                    |                  | 15:0          | _     | —                                           |       |        | —     | DMABR   | STM<1:0>     | DMAERR        | ADDR<31:16                |           | EP<3:0>      |        | DMAIE     | DMAMODE      | DMADIR      | DMAEN      |            |

| 3238               | USB<br>DMA4A     | 31:16<br>15:0 |       |                                             |       |        |       |         |              |               | ADDR<31:16<br>ADDR<15:0:  |           |              |        |           |              |             |            | 000        |

|                    | USB              | 31:16         |       |                                             |       |        |       |         |              |               | COUNT<31:10               |           |              |        |           |              |             |            | 0000       |

| 323C               | DMA4N            | 15:0          |       |                                             |       |        |       |         |              |               | COUNT<15:0                |           |              |        |           |              |             |            | 000        |

| 2244               | USB              | 31:16         | _     |                                             |       | —      | —     | —       | _            | _             | _                         | —         | _            | —      | —         | —            | —           | _          | 000        |

| 3244               | DMA5C            | 15:0          | _     | —                                           | —     | —      | —     | DMABR   | STM<1:0>     | DMAERR        |                           | DMA       | EP<3:0>      | ·      | DMAIE     | DMAMODE      | DMADIR      | DMAEN      | 1 0000     |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Note

Device mode. 1: 2: Host mode.

3:

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7). 4:

#### REGISTER 11-3: USBCSR2: USB CONTROL STATUS REGISTER 2 (CONTINUED)

- bit 19 **SOFIF:** Start of Frame Interrupt bit

- 1 = A new frame has started

- 0 = No start of frame detected

- bit 18 **RESETIF:** Reset/Babble Interrupt bit

- 1 = In *Host mode*, indicates babble is detected. In *Device mode*, indicates reset signaling is detected on the bus.

- 0 = No reset/babble detected

- bit 17 **RESUMEIF:** Resume Interrupt bit

- 1 = Resume signaling is detected on the bus while USB module is in Suspend mode

- 0 = No Resume signaling detected

- bit 16 SUSPIF: Suspend Interrupt bit

- 1 = Suspend signaling is detected on the bus (Device mode)

- 0 = No suspend signaling detected

- bit 15-8 Unimplemented: Read as '0'

- bit 7-1 EP7RXIE: Endpoint 'n' Receive Interrupt Enable bit

- 1 = Receive interrupt is enabled for this endpoint

- 0 = Receive interrupt is not enabled

- bit 0 Unimplemented: Read as '0'

## REGISTER 11-10: USBIENCSR2: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 2 (ENDPOINT 1-7)

|              |                   |                   | ,                 |                   |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | TXINTERV<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        | SPEE              | D<1:0>            | PROTOCO           | OL<1:0>           |                   | TEP<              | 3:0>             |                  |  |  |  |

| 15:8         | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15.6         | —                 | —                 |                   |                   | RXCNT             | <13:8>            |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | RXC               | NT<7:0>           |                   |                  |                  |  |  |  |

| Legend:           | HC = Hardware Clearable HS = Hardware Settable      |                      |                    |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 31-24 TXINTERV<7:0>: Endpoint TX Polling Interval/NAK Limit bits (Host mode)

For Interrupt and Isochronous transfers, this field defines the polling interval for the endpoint. For Bulk endpoints, this field sets the number of frames/microframes after which the endpoint should time out on receiving a stream of NAK responses.

The following table describes the valid values and interpretation for these bits:

| Transfer Type | Speed        | Valid Values (m) | Interpretation                                                                                                |

|---------------|--------------|------------------|---------------------------------------------------------------------------------------------------------------|

| Interrupt     | Low/Full     | 0x01 to 0xFF     | Polling interval is 'm' frames.                                                                               |

|               | High         | 0x01 to 0x10     | Polling interval is 2 <sup>(m-1)</sup> frames.                                                                |

| Isochronous   | Full or High | 0x01 to 0x10     | Polling interval is 2 <sup>(m-1)</sup> frames/microframes.                                                    |

| Bulk          | Full or High | 0x02 to 0x10     | NAK limit is 2 <sup>(m-1)</sup> frames/microframes. A value of '0' or '1' disables the NAK time-out function. |

bit 23-22 SPEED<1:0>: TX Endpoint Operating Speed Control bits (Host mode)

- 11 = Low-Speed

- 10 = Full-Speed

- 01 = Hi-Speed

- 00 = Reserved

bit 21-20 PROTOCOL<1:0>: TX Endpoint Protocol Control bits

- 11 = Interrupt

- 10 = Bulk

- 01 = Isochronous

- 00 = Control

- bit 19-16 TEP<3:0>: TX Target Endpoint Number bits

This value is the endpoint number contained in the TX endpoint descriptor returned to the USB module during device enumeration.

- bit 15-14 Unimplemented: Read as '0'

- bit 13-0 RXCNT<13:0>: Receive Count bits

The number of received data bytes in the endpoint RX FIFO. The value returned changes as the contents of the FIFO change and is only valid while RXPKTRDY is set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | _                 | _                 | —                 | —                 | -                 | —                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | _                 |                   | —                 | —                 | -                 | —                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | POLLCON<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | POLLCON<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 20-18: SQI1BDPOLLCON: SQI BUFFER DESCRIPTOR POLL CONTROL REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **POLLCON<15:0>:** Buffer Descriptor Processor Poll Status bits These bits indicate the number of cycles the BDP block would wait before refetching the descriptor control word if the previous descriptor fetched was disabled.

## REGISTER 20-19: SQI1BDTXDSTAT: SQI BUFFER DESCRIPTOR DMA TRANSMIT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | U-0              |  |

| 31:24        |                   | _                 | _                 |                   | TXSTATE<3:0>      |                   |                  |                  |  |

| 23:16        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

|              | —                 | _                 | _                 | TXBUFCNT<4:0>     |                   |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | —                 | _                 | _                 | _                 | —                 | —                 | —                | —                |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

| 7:0          | TXCURBUFLEN<7:0>  |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-29 Unimplemented: Read as '0'

bit 28-25 **TXSTATE<3:0>:** Current DMA Transmit State Status bits These bits provide information on the current DMA receive states.

bit 24-21 Unimplemented: Read as '0'

bit 20-16 **TXBUFCNT<4:0>:** DMA Buffer Byte Count Status bits

These bits provide information on the internal FIFO space.

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **TXCURBUFLEN<7:0>:** Current DMA Transmit Buffer Length Status bits These bits provide the length of the current DMA transmit buffer.

#### REGISTER 20-20: SQI1BDRXDSTAT: SQI BUFFER DESCRIPTOR DMA RECEIVE STATUS REGISTER

|              | 1                 | LOISTEN           |                   |                   |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 04.04        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | U-0              |  |

| 31:24        | —                 | _                 | _                 |                   | —                 |                   |                  |                  |  |

| 00.40        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

| 23:16        | —                 | —                 | _                 | RXBUFCNT<4:0>     |                   |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | _                 | _                 | _                 | _                 | —                 | —                 | —                | —                |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

| 7:0          |                   |                   |                   | RXCURBUF          | LEN<7:0>          |                   |                  |                  |  |

| Le | egend | l: |  |  |  |  |

|----|-------|----|--|--|--|--|

|    |       |    |  |  |  |  |

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-29 Unimplemented: Read as '0'

bit 28-25 **RXSTATE<3:0>:** Current DMA Receive State Status bits These bits provide information on the current DMA receive states.

bit 24-21 Unimplemented: Read as '0'

bit 20-16 **RXBUFCNT<4:0>:** DMA Buffer Byte Count Status bits These bits provide information on the internal FIFO space.

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **RXCURBUFLEN<7:0>:** Current DMA Receive Buffer Length Status bits These bits provide the length of the current DMA receive buffer.

| REGIST   | ER 25-1: RTCCON: REAL-TIME CLOCK AND CALENDAR CONTROL REGISTER                                                                                                                                                                 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10-9 | RTCCLKSEL<1:0>: RTCC Clock Select bits                                                                                                                                                                                         |

|          | When a new value is written to these bits, the Seconds Value register should also be written to properly reset the clock prescalers in the RTCC.<br>11 = Reserved                                                              |

|          |                                                                                                                                                                                                                                |

|          | <ul><li>01 = RTCC uses the external 32.768 kHz Secondary Oscillator (SOSC)</li><li>00 = RTCC uses the internal 32 kHz oscillator (LPRC)</li></ul>                                                                              |

| bit 8-7  | RTCOUTSEL<1:0>: RTCC Output Data Select bits <sup>(2)</sup>                                                                                                                                                                    |

|          | 11 = Reserved                                                                                                                                                                                                                  |

|          | 10 = RTCC Clock is presented on the RTCC pin                                                                                                                                                                                   |

|          | 01 = Seconds Clock is presented on the RTCC pin                                                                                                                                                                                |

| 1.11.0   | 00 = Alarm Pulse is presented on the RTCC pin when the alarm interrupt is triggered                                                                                                                                            |

| bit 6    | RTCCLKON: RTCC Clock Enable Status bit <sup>(5)</sup>                                                                                                                                                                          |

|          | <ul> <li>1 = RTCC Clock is actively running</li> <li>0 = RTCC Clock is not running</li> </ul>                                                                                                                                  |

| bit 5-4  | Unimplemented: Read as '0'                                                                                                                                                                                                     |

| bit 3    | RTCWREN: Real-Time Clock Value Registers Write Enable bit <sup>(3)</sup>                                                                                                                                                       |

|          | <ul> <li>1 = Real-Time Clock Value registers can be written to by the user</li> <li>0 = Real-Time Clock Value registers are locked out from being written to by the user</li> </ul>                                            |

| bit 2    | RTCSYNC: Real-Time Clock Value Registers Read Synchronization bit                                                                                                                                                              |

|          | 1 = Real-time clock value registers can change while reading (due to a rollover ripple that results in an invalid data read). If the register is read twice and results in the same data, the data can be assumed to be valid. |

|          | 0 = Real-time clock value registers can be read without concern about a rollover ripple                                                                                                                                        |

| bit 1    | HALFSEC: Half-Second Status bit <sup>(4)</sup>                                                                                                                                                                                 |

|          | 1 = Second half period of a second                                                                                                                                                                                             |

|          | 0 = First half period of a second                                                                                                                                                                                              |

| bit 0    | RTCOE: RTCC Output Enable bit                                                                                                                                                                                                  |

|          | 1 = RTCC output is enabled                                                                                                                                                                                                     |

- 0 = RTCC output is not enabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- **2:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 3: The RTCWREN bit can be set only when the write sequence is enabled.

- 4: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

- **5:** This bit is undefined when RTCCLKSEL<1:0> = 00 (LPRC is the clock source).

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3         | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|--------------------------|----------------------|--------------------|-------------------|---------------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0                      | U-0                  | U-0                | U-0               | U-0                       | U-0               | U-0              | U-0              |  |

| 31.24        | —                        | —                    | —                  | —                 | —                         | —                 | —                | —                |  |

| 00.40        | U-0                      | U-0                  | U-0                | U-0               | U-0                       | U-0               | U-0              | U-0              |  |

| 23:16        | —                        | _                    | —                  | —                 | —                         | —                 | —                | —                |  |

| 45.0         | R/W-0                    | R/W-0                | R/W-0              | R-0               | R/W-0                     | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | ALRMEN <sup>(1,2)</sup>  | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC          | AMASK<3:0> <sup>(2)</sup> |                   |                  |                  |  |

| 7.0          | R/W-0                    | R/W-0                | R/W-0              | R/W-0             | R/W-0                     | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | ARPT<7:0> <sup>(2)</sup> |                      |                    |                   |                           |                   |                  |                  |  |

#### REGISTER 25-2: RTCALRM: REAL-TIME CLOCK ALARM CONTROL REGISTER

#### Legend:

| Logonal           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

- bit 14 CHIME: Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

#### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

#### bit 12 ALRMSYNC: Alarm Sync bit

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing.

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is more than 32 real-time clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

- 0000 = Every half-second

- 0001 = Every second

- 0010 = Every 10 seconds

- 0011 = Every minute

- 0100 = Every 10 minutes

- 0101 = Every hour

- 0110 = Once a day

- 0111 = Once a week

- 1000 = Once a month

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1010 = Reserved

- 1011 = Reserved

- 11xx = Reserved

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

**Note:** This register is reset only on a Power-on Reset (POR).

| Bit Range | Bit<br>31/23/15/7            | Bit<br>30/22/14/6 | Bit<br>29/21/13/5            | Bit<br>28/20/12/4 | Bit<br>27/19/11/3            | Bit<br>26/18/10/2 | Bit<br>25/17/9/1             | Bit<br>24/16/8/0       |

|-----------|------------------------------|-------------------|------------------------------|-------------------|------------------------------|-------------------|------------------------------|------------------------|

| 24.24     | U-0                          | U-0               | U-0                          | U-0               | U-0                          | U-0               | R/W-0                        | R/W-0                  |

| 31:24     | —                            | _                 | —                            | —                 | —                            | _                 | SH4ALT                       | <1:0> <sup>(1,2)</sup> |

| 00.40     | R/W-0                        | R/W-0             | R/W-0                        | R/W-0             | R/W-0                        | R/W-0             | R/W-0                        | R/W-0                  |

| 23:16     | SH3ALT<1:0> <sup>(1,2)</sup> |                   | SH2ALT<1:0> <sup>(1,2)</sup> |                   | SH1ALT<1:0> <sup>(1,2)</sup> |                   | SH0ALT<1:0> <sup>(1,2)</sup> |                        |

| 15.0      | U-0                          | U-0               | U-0                          | U-0               | R/W-0                        | R/W-0             | R/W-0                        | R/W-0                  |

| 15:8      | —                            | _                 | —                            | _                 | SH5MC                        | )D<1:0>           | SH4MC                        | )D<1:0>                |

| 7:0       | R/W-0                        | R/W-0             | R/W-0                        | R/W-0             | R/W-0                        | R/W-0             | R/W-0                        | R/W-0                  |

|           | SH3M0                        | )D<1:0>           | SH2MOD<1:0>                  |                   | SH1MOD<1:0>                  |                   | SH0MOD<1:0>                  |                        |

#### REGISTER 28-4: AD1IMOD: ADC1 INPUT MODE CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-26 Unimplemented: Read as '0'

#### bit 25-24 SH4ALT<1:0>: Analog Input to Dedicated S&H 4 (SH4) Select bits<sup>(1,2)</sup>

- 11 = Reserved

- 10 = Reserved

- 01 = Alternate input AN49

- 00 = Default Class 1 input AN4

#### bit 23-22 SH3ALT<1:0>: Analog Input to Dedicated S&H 3 (SH3) Select bits<sup>(1,2)</sup>

- 11 = Reserved

- 10 = Reserved

- 01 = Alternate input AN48

- 00 = Default Class 1 input AN3

#### bit 21-20 SH2ALT<1:0>: Analog Input to Dedicated S&H 2 (SH2) Select bits<sup>(1,2)</sup>

- 11 = Reserved

- 10 = Reserved

- 01 = Alternate input AN47

- 00 = Default Class 1 input AN2

#### bit 19-18 SH1ALT<1:0>: Analog Input to Dedicated S&H 1 (SH1) Select bits<sup>(1,2)</sup>

- 11 = Reserved

- 10 = Reserved

- 01 = Alternate input AN46

- 00 = Default Class 1 input AN1

#### bit 17-16 SH0ALT<1:0>: Analog Input to Dedicated S&H 0 (SH0) Select bits<sup>(1,2)</sup>

- 11 = Reserved

- 10 = Reserved

- 01 = Alternate input AN45

- 00 = Default Class 1 input AN0

- bit 15-12 Unimplemented: Read as '0'

- **Note 1:** Alternate inputs are only available for Class 1 Inputs.

- 2: When an alternate input is selected (SHxALT<1:0> ≠ 0), the data, status, and control registers for the default Class 1 input are still used. Selecting an alternate input changes the physical input source only.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        | FLTEN27           | MSEL2             | 27<1:0>           | FSEL27<4:0>       |                   |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN26           | MSEL2             | :6<1:0>           | FSEL26<4:0>       |                   |                   |                  |                  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | FLTEN25           | MSEL2             | 25<1:0>           |                   |                   | FSEL25<4:0>       |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | FLTEN24           | MSEL2             | 24<1:0>           | FSEL24<4:0>       |                   |                   |                  |                  |  |

#### REGISTER 29-16: CIFLTCON6: CAN FILTER CONTROL REGISTER 6

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | FLTEN27: Filter 27 Enable bit                                                             |

|-----------|-------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled                                                                     |

|           | 0 = Filter is disabled                                                                    |

| bit 30-29 | MSEL27<1:0>: Filter 27 Mask Select bits                                                   |

|           | 11 = Acceptance Mask 3 selected                                                           |

|           | 10 = Acceptance Mask 2 selected                                                           |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                        |

| bit 28-24 | FSEL27<4:0>: FIFO Selection bits                                                          |

| 511 20 24 | 11111 = Message matching filter is stored in FIFO buffer 31                               |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                               |

|           | •                                                                                         |

|           | •                                                                                         |

|           | •                                                                                         |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                |

| bit 23    | FLTEN26: Filter 26 Enable bit                                                             |

|           | 1 = Filter is enabled                                                                     |

|           | 0 = Filter is disabled                                                                    |

| bit 22-21 | MSEL26<1:0>: Filter 26 Mask Select bits                                                   |

|           | <ul><li>11 = Acceptance Mask 3 selected</li><li>10 = Acceptance Mask 2 selected</li></ul> |

|           | 01 = Acceptance Mask 2 selected                                                           |

|           | 00 = Acceptance Mask 0 selected                                                           |

| bit 20-16 | FSEL26<4:0>: FIFO Selection bits                                                          |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                               |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                               |

|           | •                                                                                         |

|           | •                                                                                         |

|           | •                                                                                         |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                |

| Note:     | The bits in this register can only be modified if the corresponding fil                   |

|           |                                                                                           |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### REGISTER 30-24: EMAC1CFG2: ETHERNET CONTROLLER MAC CONFIGURATION 2 REGISTER VLANPAD: VLAN Pad Enable bit<sup>(1,2)</sup> bit 6 1 = The MAC will pad all short frames to 64 bytes and append a valid CRC 0 = The MAC does not perform padding of short frames PADENABLE: Pad/CRC Enable bit<sup>(1,3)</sup> bit 5 1 = The MAC will pad all short frames 0 = The frames presented to the MAC have a valid length bit 4 CRCENABLE: CRC Enable1 bit 1 = The MAC will append a CRC to every frame whether padding was required or not. Must be set if the PADENABLE bit is set. 0 = The frames presented to the MAC have a valid CRC bit 3 DELAYCRC: Delayed CRC bit This bit determines the number of bytes, if any, of proprietary header information that exist on the front of the IEEE 802.3 frames. 1 = Four bytes of header (ignored by the CRC function) 0 = No proprietary header bit 2 HUGEFRM: Huge Frame enable bit 1 = Frames of any length are transmitted and received 0 = Huge frames are not allowed for receive or transmit bit 1 LENGTHCK: Frame Length checking bit 1 = Both transmit and receive frame lengths are compared to the Length/Type field. If the Length/Type field represents a length then the check is performed. Mismatches are reported on the transmit/receive statistics vector. 0 = Length/Type field check is not performed bit 0 FULLDPLX: Full-Duplex Operation bit

- 1 = The MAC operates in Full-Duplex mode

- 0 = The MAC operates in Half-Duplex mode

- Note 1: Table 30-6 provides a description of the pad function based on the configuration of this register.

- **2:** This bit is ignored if the PADENABLE bit is cleared.

- 3: This bit is used in conjunction with the AUTOPAD and VLANPAD bits.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware

#### TABLE 30-6: PAD OPERATION

| Туре | AUTOPAD | VLANPAD | PADENABLE | Action                                                                                  |

|------|---------|---------|-----------|-----------------------------------------------------------------------------------------|

| Any  | х       | x       | 0         | No pad, check CRC                                                                       |

| Any  | 0       | 0       | 1         | Pad to 60 Bytes, append CRC                                                             |