Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048ecg100-i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 50. "CPU MIPS32<sup>®</sup> for Devices with microAptiv<sup>™</sup> and M-Class Cores" (DS60001192), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32). MIPS32<sup>®</sup> microAptiv™ Microprocessor

MIPS32<sup>®</sup> microAptiv<sup>™</sup> Microprocessor Core resources are available at: www.imgtec.com.

The MIPS32<sup>®</sup> microAptiv<sup>™</sup> Microprocessor Core is the heart of the PIC32MZ EC family device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

#### 3.1 Features

PIC32MZ EC family processor core key features:

- 5-stage pipeline

- 32-bit address and data paths

- MIPS32<sup>®</sup> Enhanced Architecture (Release 2):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- Virtual memory support

- microMIPS<sup>™</sup> compatible instruction set:

- Improves code size density over MIPS32, while maintaining MIPS32 performance.

- Supports all MIPS32 instructions (except branchlikely instructions)

- Fifteen additional 32-bit instructions and 39 16-bit instructions corresponding to commonly-used MIPS32 instructions

- Stack pointer implicit in instruction

- MIPS32 assembly and ABI compatible

- MMU with Translation Lookaside Buffer (TLB) mechanism:

- 16 dual-entry fully associative Joint TLB

- 4-entry fully associative Instruction TLB

- 4-entry fully associative Data TLB

- 4 KB pages

- Separate L1 data and instruction caches:

- 16 KB 4-way Instruction Cache (I-Cache)

- 4 KB 4-way Data Cache (D-Cache)

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x32 multiply per clock

- Early-in iterative divide. Minimum 12 and maximum 38 clock latency (dividend (*rs*) sign extension-dependent)

- Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value breakpoints

- Hardware breakpoint supports both address match and address range triggering.

- Eight instruction and four data complex breakpoints

- iFlowtrace<sup>®</sup> version 2.0 support:

- Real-time instruction program counter

- Special events trace capability

- Two performance counters with 34 userselectable countable events

- Disabled if the processor enters Debug mode

- Four Watch registers:

- Instruction, Data Read, Data Write options

- Address match masking options

- DSP ASE Extension:

- Native fractional format data type operations

- Register Single Instruction Multiple Data (SIMD) operations (add, subtract, multiply, shift)

- GPR-based shift

- Bit manipulation

- Compare-Pick

- DSP Control Access

- Indexed-Load

- Branch

- Multiplication of complex operands

- Variable bit insertion and extraction

- Virtual circular buffers

- Arithmetic saturation and overflow handling

- Zero-cycle overhead saturation and rounding operations

#### TABLE 4-9: SYSTEM BUS TARGET 1 REGISTER MAP (CONTINUED)

| SS                          |                  |           | 1     |       |       |          |       |       |      | ,    | Bits     |      |          |      |        |        |        |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|-------|-------|------|------|----------|------|----------|------|--------|--------|--------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11 | 26/10 | 25/9 | 24/8 | 23/7     | 22/6 | 21/5     | 20/4 | 19/3   | 18/2   | 17/1   | 16/0   | All<br>Resets |

| 84E0                        | SBT1REG5         | 31:16     |       |       |       |          |       |       |      | BA   | SE<21:6> |      |          |      |        |        |        |        | xxxx          |

| 0460                        | OBTINEOS         | 15:0      |       |       | BA    | SE<5:0>  |       |       | PRI  | -    |          |      | SIZE<4:0 | >    |        | —      | —      | —      | xxxx          |

| 84F0                        | SBT1RD5          | 31:16     | —     | —     | —     | —        | —     | —     |      | _    | —        |      | —        | —    | —      | —      |        | —      | xxxx          |

| 0+1 0                       | 0011100          | 15:0      | —     | —     | —     | —        | —     | —     |      | _    | —        |      | —        | —    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 84F8                        | SBT1WR5          | 31:16     | —     | —     | —     | —        | —     | —     |      | _    | —        |      | —        | —    | —      | —      |        |        | xxxx          |

| 0+10                        | OBTIMIts         | 15:0      | —     | —     | —     | —        | —     | —     | —    | —    | —        | —    | —        | —    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 8500                        | SBT1REG6         | 31:16     |       |       |       |          |       |       |      | BA   | SE<21:6> |      |          |      |        |        |        |        | xxxx          |

|                             | 02111200         | 15:0      |       | -     | BA    | SE<5:0>  |       |       | PRI  | —    |          |      | SIZE<4:0 | >    |        | —      | —      | —      | xxxx          |

| 8510                        | SBT1RD6          | 31:16     | —     | -     | —     | —        | —     | —     | -    | -    | —        | _    | —        | —    |        | —      | —      | —      | xxxx          |

| 00.0                        | 0211120          | 15:0      | —     |       | —     | —        | —     | —     | _    | —    | —        | —    | —        | —    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 8518                        | SBT1WR6          | 31:16     | —     |       | —     | —        | —     | —     | _    | _    | _        | _    | —        | —    | -      | —      | —      | —      | xxxx          |

|                             |                  | 15:0      | —     | —     | —     | —        | —     | —     | —    | —    | —        | —    | —        | —    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 8520                        | SBT1REG7         | 31:16     |       |       |       |          |       |       |      | r    | SE<21:6> |      |          |      |        |        |        | 1      | xxxx          |

|                             |                  | 15:0      |       |       |       | SE<5:0>  |       |       | PRI  | _    |          |      | SIZE<4:0 |      |        | _      | —      | —      | XXXX          |

| 8530                        | SBT1RD7          | 31:16     |       |       | _     | —        | —     | —     | _    | -    | —        | —    | —        | —    | -      | —      | —      |        | xxxx          |

|                             |                  | 15:0      | —     |       | _     | _        | —     | _     | _    | _    | —        | _    | _        | —    | GROUP3 | GROUP2 | GROUP1 | GROUP0 |               |

| 8538                        | SBT1WR7          | 31:16     |       |       | _     | —        | —     | —     | _    | -    | _        | —    | —        | —    | -      | —      | —      | —      | XXXX          |

|                             |                  | 15:0      | —     | —     | _     | —        | —     | _     | _    | -    | —        | —    | _        | —    | GROUP3 | GROUP2 | GROUP1 | GROUP0 |               |

| 8540                        | SBT1REG8         | 31:16     |       |       |       | 05 5 0   |       |       |      |      | SE<21:6> |      | 0.75 4 6 |      |        |        |        |        | XXXX          |

|                             |                  | 15:0      |       |       |       | \SE<5:0> |       |       | PRI  | _    |          |      | SIZE<4:0 |      |        | -      |        |        | XXXX          |

| 8550                        | SBT1RD8          | 31:16     |       |       |       |          |       | _     |      | _    | _        | _    |          | —    |        | -      |        | -      | XXXX          |

|                             |                  | 15:0      | —     |       |       |          |       |       |      | _    | _        |      | _        |      | GROUP3 | GROUP2 |        | GROUP0 |               |

| 8558                        | SBT1WR8          | 31:16     |       |       | _     | _        | —     | _     | _    | _    |          |      |          |      |        |        |        |        | XXXX          |

|                             |                  | 15:0      | —     |       |       |          |       | _     |      |      | —        | —    | —        | —    | GROUP3 | GROUP2 | GROUP1 | GROUPU | XXXX          |

PIC32MZ Embedded Connectivity (EC) Family

DS60001191G-page 76

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note:** For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

#### TABLE 7-2: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

| In (annual Causes (1)           |                     | IRQ | Maatan #     |          | Interru  | upt Bit Location |              | Persistent |

|---------------------------------|---------------------|-----|--------------|----------|----------|------------------|--------------|------------|

| Interrupt Source <sup>(1)</sup> | XC32 Vector Name    | #   | Vector #     | Flag     | Enable   | Priority         | Sub-priority | Interrupt  |

| ADC1 Digital Comparator 3       | _ADC1_DC3_VECTOR    | 48  | OFF048<17:1> | IFS1<16> | IEC1<16> | IPC12<4:2>       | IPC12<1:0>   | Yes        |

| ADC1 Digital Comparator 4       | _ADC1_DC4_VECTOR    | 49  | OFF049<17:1> | IFS1<17> | IEC1<17> | IPC12<12:10>     | IPC12<9:8>   | Yes        |

| ADC1 Digital Comparator 5       | _ADC1_DC5_VECTOR    | 50  | OFF050<17:1> | IFS1<18> | IEC1<18> | IPC12<20:18>     | IPC12<17:16> | Yes        |

| ADC1 Digital Comparator 6       | _ADC1_DC6_VECTOR    | 51  | OFF051<17:1> | IFS1<19> | IEC1<19> | IPC12<28:26>     | IPC12<25:24> | Yes        |

| ADC1 Digital Filter 1           | _ADC1_DF1_VECTOR    | 52  | OFF052<17:1> | IFS1<20> | IEC1<20> | IPC13<4:2>       | IPC13<1:0>   | Yes        |

| ADC1 Digital Filter 2           | _ADC1_DF2_VECTOR    | 53  | OFF053<17:1> | IFS1<21> | IEC1<21> | IPC13<12:10>     | IPC13<9:8>   | Yes        |

| ADC1 Digital Filter 3           | _ADC1_DF3_VECTOR    | 54  | OFF054<17:1> | IFS1<22> | IEC1<22> | IPC13<20:18>     | IPC13<17:16> | Yes        |

| ADC1 Digital Filter 4           | _ADC1_DF4_VECTOR    | 55  | OFF055<17:1> | IFS1<23> | IEC1<23> | IPC13<28:26>     | IPC13<25:24> | Yes        |

| ADC1 Digital Filter 5           | _ADC1_DF5_VECTOR    | 56  | OFF056<17:1> | IFS1<24> | IEC1<24> | IPC14<4:2>       | IPC14<1:0>   | Yes        |

| ADC1 Digital Filter 6           | _ADC1_DF6_VECTOR    | 57  | OFF057<17:1> | IFS1<25> | IEC1<25> | IPC14<12:10>     | IPC14<9:8>   | Yes        |

| Reserved                        | —                   | 58  | —            | —        | —        | —                | —            | _          |

| ADC1 Data 0                     | _ADC1_DATA0_VECTOR  | 59  | OFF059<17:1> | IFS1<27> | IEC1<27> | IPC14<28:26>     | IPC14<25:24> | Yes        |

| ADC1 Data 1                     | _ADC1_DATA1_VECTOR  | 60  | OFF060<17:1> | IFS1<28> | IEC1<28> | IPC15<4:2>       | IPC15<1:0>   | Yes        |

| ADC1 Data 2                     | _ADC1_DATA2_VECTOR  | 61  | OFF061<17:1> | IFS1<29> | IEC1<29> | IPC15<12:10>     | IPC15<9:8>   | Yes        |

| ADC1 Data 3                     | _ADC1_DATA3_VECTOR  | 62  | OFF062<17:1> | IFS1<30> | IEC1<30> | IPC15<20:18>     | IPC15<17:16> | Yes        |

| ADC1 Data 4                     | _ADC1_DATA4_VECTOR  | 63  | OFF063<17:1> | IFS1<31> | IEC1<31> | IPC15<28:26>     | IPC15<25:24> | Yes        |

| ADC1 Data 5                     | _ADC1_DATA5_VECTOR  | 64  | OFF064<17:1> | IFS2<0>  | IEC2<0>  | IPC16<4:2>       | IPC16<1:0>   | Yes        |

| ADC1 Data 6                     | _ADC1_DATA6_VECTOR  | 65  | OFF065<17:1> | IFS2<1>  | IEC2<1>  | IPC16<12:10>     | IPC16<9:8>   | Yes        |

| ADC1 Data 7                     | _ADC1_DATA7_VECTOR  | 66  | OFF066<17:1> | IFS2<2>  | IEC2<2>  | IPC16<20:18>     | IPC16<17:16> | Yes        |

| ADC1 Data 8                     | _ADC1_DATA8_VECTOR  | 67  | OFF067<17:1> | IFS2<3>  | IEC2<3>  | IPC16<28:26>     | IPC16<25:24> | Yes        |

| ADC1 Data 9                     | _ADC1_DATA9_VECTOR  | 68  | OFF068<17:1> | IFS2<4>  | IEC2<4>  | IPC17<4:2>       | IPC17<1:0>   | Yes        |

| ADC1 Data 10                    | _ADC1_DATA10_VECTOR | 69  | OFF069<17:1> | IFS2<5>  | IEC2<5>  | IPC17<12:10>     | IPC17<9:8>   | Yes        |

| ADC1 Data 11                    | _ADC1_DATA11_VECTOR | 70  | OFF070<17:1> | IFS2<6>  | IEC2<6>  | IPC17<20:18>     | IPC17<17:16> | Yes        |

| ADC1 Data 12                    | _ADC1_DATA12_VECTOR | 71  | OFF071<17:1> | IFS2<7>  | IEC2<7>  | IPC17<28:26>     | IPC17<25:24> | Yes        |

| ADC1 Data 13                    | _ADC1_DATA13_VECTOR | 72  | OFF072<17:1> | IFS2<8>  | IEC2<8>  | IPC18<4:2>       | IPC18<1:0>   | Yes        |

| ADC1 Data 14                    | _ADC1_DATA14_VECTOR | 73  | OFF073<17:1> | IFS2<9>  | IEC2<9>  | IPC18<12:10>     | IPC18<9:8>   | Yes        |

| ADC1 Data 15                    | _ADC1_DATA15_VECTOR | 74  | OFF074<17:1> | IFS2<10> | IEC2<10> | IPC18<20:18>     | IPC18<17:16> | Yes        |

ADC1 Data 14

\_ADC1\_DATA14\_VECTOR

73

OFF073<17:1>

IFS2<9>

IEC2<9>

IPC18<12:10>

IP

ADC1 Data 15

\_ADC1\_DATA15\_VECTOR

74

OFF074<17:1>

IFS2<10>

IEC2<10>

IPC18<20:18>

IP

Note 1:

Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MZ EC Family Features" for the list of available peripherals.

2:

This interrupt source is not available on 64-pin devices.

3:

This interrupt source is not available on 100-pin devices.

3:

This interrupt source is not available on 100-pin devices.

**4:** This interrupt source is not available on 124-pin devices.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | U-0              | U-0              |

| 51.24     |                   | _                 | —                 | —                 | —                 | PFMSECEN          | -                | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 25.10     |                   | _                 | _                 | —                 | —                 |                   |                  | _                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0      |                   | _                 | _                 | —                 | —                 |                   |                  | _                |

| 7:0       | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1             | R/W-1            | R/W-1            |

| 7.0       |                   |                   | PREFEN            | N<1:0>            | _                 | PF                | MWS<2:0>(*       | 1)               |

#### REGISTER 9-1: PRECON: PREFETCH MODULE CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-27 Unimplemented: Read as '0'

- bit 26 **PFMSECEN:** Flash SEC Interrupt Enable bit

- 1 = Generate an interrupt when the PFMSEC bit (PRESTAT<26>) is set

- 0 = Do not generate an interrupt when the PFMSEC bit is set

- bit 25-6 **Unimplemented:** Read as '0'

- bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

- 11 = Enable predictive prefetch for any address

- 10 = Enable predictive prefetch for CPU instructions and CPU data

- 01 = Enable predictive prefetch for CPU instructions only

- 00 = Disable predictive prefetch

#### bit 3 Unimplemented: Read as '0'

#### bit 2-0 **PFMWS<2:0>:** PFM Access Time Defined in Terms of SYSCLK Wait States bits<sup>(1)</sup>

- 111 = Seven Wait states

- •

- •

- •

- 010 = Two Wait states

- 001 = One Wait state

- 000 = Zero Wait states

- Note 1: For the Wait states to SYSCLK relationship, refer to Table 37-13 in Section37.0 "Electrical Characteristics".

| SS                          |                                 |               |        |       |          |       |          |       |      | Bit    | s      |        |        |        |        |        |        |         |            |

|-----------------------------|---------------------------------|---------------|--------|-------|----------|-------|----------|-------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13    | 28/12 | 27/11    | 26/10 | 25/9 | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0    | All Resets |

| 1280                        | DCH2CPTR                        | 31:16         | _      | —     | —        |       | —        |       | _    | —      |        |        | _      | —      | _      | _      | _      | _       | 0000       |

| .200                        | 2011201 111                     | 15:0          |        |       | , ,      |       |          |       |      | CHCPTR | <15:0> |        |        |        |        |        |        | •       | 000        |

| 1290                        | DCH2DAT                         | 31:16         | —      | _     | —        |       | —        |       | —    | —      | —      | —      | —      | —      | —      | —      | —      | —       | 000        |

|                             |                                 | 15:0          |        |       |          |       |          |       |      | CHPDAT | <15:0> |        |        |        |        |        |        |         | 000        |

| 12A0                        | DCH3CON                         | 31:16         |        |       |          |       | N<7:0>   |       |      |        | —      | —      | _      | —      | _      | —      | —      | —       | 000        |

| ,                           | 201100011                       | 15:0          | CHBUSY | _     | CHPIGNEN | _     | CHPATLEN | _     | —    | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  | —      | CHEDET | CHPR   | RI<1:0> | 0000       |

| 12B0                        | DCH3ECON                        | 31:16         | —      | _     | —        | _     | —        |       |      | —      |        |        |        | CHAIR  | r      |        |        | -       | 00F1       |

|                             |                                 | 15:0          |        |       |          | CHSIR | Q<7:0>   |       |      | 1      | CFORCE |        | PATEN  |        | AIRQEN | -      | -      |         | FFOO       |

| 12C0                        | <b>DCH3INT</b>                  | 31:16         | _      |       | —        | _     | —        | _     |      | _      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE  | 0000       |

|                             |                                 | 15:0<br>31:16 | _      | _     | —        | _     |          | _     | _    | _      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF  | 0000       |

| 12D0                        | DCH3SSA                         | 15:0          |        |       |          |       |          |       |      | CHSSA- | <31:0> |        |        |        |        |        |        |         | 0000       |

| 12E0                        | DCH3DSA                         | 31:16<br>15:0 |        |       |          |       |          |       |      | CHDSA  | <31:0> |        |        |        |        |        |        |         | 0000       |

| 1050                        | DCH3SSIZ                        | 31:16         | _      | _     | —        | —     | —        | —     | —    | —      | —      | —      | _      | _      | —      | —      | —      | —       | 0000       |

| 12FU                        | DCH355IZ                        | 15:0          |        |       |          |       |          |       |      | CHSSIZ | <15:0> |        |        |        |        |        |        |         | 0000       |

| 1300                        | DCH3DSIZ                        | 31:16         | —      | _     | —        | _     | —        | _     | —    | —      | —      | —      | _      | —      | _      | —      | —      | —       | 0000       |

| 1000                        |                                 | 15:0          |        |       |          |       |          |       |      | CHDSIZ | <15:0> |        |        |        |        |        |        |         | 0000       |

| 1310                        | DCH3SPTR                        | 31:16         | —      |       | —        | —     | —        | _     |      | —      |        | —      | —      |        | —      | —      | —      | —       | 0000       |

|                             |                                 | 15:0          |        |       |          |       |          |       |      | CHSPTR | <15:0> |        |        |        |        |        |        | -       | 0000       |

| 1320                        | DCH3DPTR                        | 31:16         | —      |       | —        |       |          |       | _    |        | —      | _      | _      | _      | _      |        |        | —       | 0000       |

|                             |                                 | 15:0          | _      |       |          |       |          |       |      | CHDPTR | <15:0> |        |        |        |        |        |        |         | 0000       |

| 1330                        | DCH3CSIZ                        | 31:16<br>15:0 | —      | _     |          |       | _        |       |      | CHCSIZ | <15:0> |        |        | _      |        |        |        | _       | 0000       |

|                             |                                 | 31:16         | _      | _     | _        | _     |          | _     | _    |        | <10.02 | _      | _      | _      | _      | _      | _      | _       | 0000       |

| 1340                        | DCH3CPTR                        | 15:0          |        |       |          |       |          |       |      | CHCPTR | <15:0> |        |        |        |        |        |        |         | 0000       |

| 1350                        | DCH3DAT                         | 31:16         |        |       |          |       |          |       |      | _      | —      | _      |        |        | _      |        |        | _       | 0000       |

| 1350                        | DUISDAI                         | 15:0          |        |       |          |       |          |       |      | CHPDAT | <15:0> |        |        |        |        |        |        |         | 0000       |

| 1360                        | DCH4CON                         | 31:16         |        |       |          | CHPIG | N<7:0>   |       |      |        | —      | —      | _      | —      | _      | —      | _      | —       | 0000       |

| .000                        | DOI1400N                        | 15:0          | CHBUSY | —     | CHPIGNEN | _     | CHPATLEN | —     | —    | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  |        | CHEDET | CHPR   | RI<1:0> | 0000       |

| 1370                        | DCH4ECON                        | 31:16         | —      | —     | —        |       | —        |       | —    | —      |        | 1      |        | CHAIR  | r      |        |        |         | 00FF       |

|                             |                                 | 15:0          |        |       |          | CHSIR | Q<7:0>   |       |      |        | CFORCE |        | PATEN  | SIRQEN | AIRQEN | —      | —      | —       | FFOC       |

| 1380                        | DCH4INT                         | 31:16         | —      | —     | —        | _     | —        | _     | —    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE  | _          |

|                             |                                 | 15:0          |        |       | —        | _     |          | _     | —    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF  | 0000       |

PIC32MZ Embedded Connectivity (EC) Family

TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |

| 31.24        | _                 | —                 |                   | —                 | —                    | —                 | —                | —                |

| 22.46        | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |

| 23:16        |                   |                   |                   | CHAIRQ<           | <7:0> <sup>(1)</sup> |                   |                  |                  |

| 15.0         | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |

| 15:8         |                   |                   |                   | CHSIRQ<           | <7:0> <sup>(1)</sup> |                   |                  |                  |

| 7:0          | S-0               | S-0               | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |

| 7.0          | CFORCE            | CABORT            | PATEN             | SIRQEN            | AIRQEN               | —                 |                  | —                |

#### **REGISTER 10-8:** DCHxECON: DMA CHANNEL x EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31

| bit 31-24 | Unimplemented: Read as '0'                                                                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                                                              |

| 511 20 10 | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                                                                                         |

|           | •                                                                                                                                                                        |

|           | •                                                                                                                                                                        |

|           | •                                                                                                                                                                        |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag<br>00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag         |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                                                              |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                                                                    |

|           | •                                                                                                                                                                        |

|           | •                                                                                                                                                                        |

|           |                                                                                                                                                                          |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer                                                               |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                                                                                          |

|           | <ul> <li>1 = A DMA transfer is forced to begin when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                       |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                                                                                           |

|           | <ul> <li>1 = A DMA transfer is aborted when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                               |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                                                                                            |

|           | <ul> <li>1 = Abort transfer and clear CHEN on pattern match</li> <li>0 = Pattern match is disabled</li> </ul>                                                            |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                                                                     |

|           | <ul> <li>1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs</li> <li>0 = Interrupt number CHSIRQ is ignored and does not start a transfer</li> </ul> |

| bit 3     | AIRQEN: Channel Abort IRQ Enable bit                                                                                                                                     |

|           |                                                                                                                                                                          |

- 1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

- 0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

- bit 2-0 Unimplemented: Read as '0'

- Note 1: See Table 7-2: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24     |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16     |                   |                   |                   | CHSSA<            | 23:16>            |                   |                  |                  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8      |                   |                   |                   | CHSSA             | <15:8>            |                   |                  |                  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0       | CHSSA<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 10-10: DCHxSSA: DMA CHANNEL x SOURCE START ADDRESS REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-0 CHSSA<31:0> Channel Source Start Address bits Channel source start address. Note: This must be the physical address of the source.

#### REGISTER 10-11: DCHxDSA: DMA CHANNEL x DESTINATION START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        |                   |                   |                   | CHDSA<            | 23:16>            |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         |                   |                   |                   | CHDSA             | <15:8>            |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | CHDSA<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 CHDSA<31:0>: Channel Destination Start Address bits Channel destination start address.

Note: This must be the physical address of the destination.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | —                 | _                 | -                 | _                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 |                   |                   | -                 |                   |                  | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHPDAT            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | <7:0>             |                   |                  |                  |

#### REGISTER 10-18: DCHxDAT: DMA CHANNEL x PATTERN DATA REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | mplemented bit, read as '0' |  |

|-------------------|------------------|------------------------|-----------------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown          |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **CHPDAT<15:0>:** Channel Data Register bits <u>Pattern Terminate mode:</u> Data to be matched must be stored in this register to allow terminate on match.

> All other modes: Unused.

### 11.0 HI-SPEED USB WITH ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 51. "Hi-Speed USB with On-The-Go (OTG)" (DS60001232), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 embedded host, device, or OTG implementation with a minimum of external components.

The module supports Hi-Speed, Full-Speed, or Low-Speed in any of the operating modes. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the RAM controller, packet encode/decode, UTM synchronization, end-point control, a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

Note: To avoid cache coherency problems on devices with L1 cache, USB buffers must only be allocated or accessed from the KSEG1 segment.

The USB module includes the following features:

- USB Hi-Speed, Full-Speed, and Low-Speed support for host and device

- USB OTG support with one or more Hi-Speed, Full-Speed, or Low-Speed device

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- Transaction handshaking performed by hardware

- Integrated 8-channel DMA to access system RAM and Flash

- Seven transmit endpoints and seven receive endpoints, in addition to Endpoint 0

- Session Request Protocol (SRP) and Host Negotiation Protocol (HNP) support

- Suspend and resume signaling support

- Dynamic FIFO sizing

- Integrated RAM for the FIFOs, eliminating the need for system RAM for the FIFOs

- Link power management support

- Note 1: The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

- 2: If the USB module is used, the Primary Oscillator (Posc) is limited to either 12 MHz or 24 MHz.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | _                 | _                 | _                 | - RXDPB RXFIFOSZ<3:0> |                   |                   |                  |                  |  |

| 00.40        | U-0               | U-0               | U-0               | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | _                 | _                 | _                 | TXDPB                 | TXFIFOSZ<3:0>     |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0               | R/W-0            | R/W-0            |  |

| 15:8         | _                 | —                 | —                 | _                     | —                 | —                 | TXEDMA           | RXEDMA           |  |

| 7.0          | R-1               | R-0               | R-0               | R-0                   | R-0               | R-0               | R/W-0, HC        | R/W-0            |  |

| 7:0          | BDEV              | FSDEV             | LSDEV             | VBUS                  | 5<1:0>            | HOSTMODE          | HOSTREQ          | SESSION          |  |

#### REGISTER 11-13: USBOTG: USB OTG CONTROL/STATUS REGISTER

#### Legend:

| 3                 |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-29 Unimplemented: Read as '0'

- bit 28 RXDPB: RX Endpoint Double-packet Buffering Control bit

- 1 = Double-packet buffer is supported. This doubles the size set in RXFIFOSZ.

- 0 = Double-packet buffer is not supported

#### bit 27-24 RXFIFOSZ<3:0>: RX Endpoint FIFO Packet Size bits

The maximum packet size to allowed for (before any splitting within the FIFO of Bulk/High-Bandwidth packets prior to transmission)

- 1111 = Reserved

- •

- •

- •

- 1010 = Reserved

- 1001 = 4096 bytes

- 1000 = 2048 bytes

- 0111 = 1024 bytes

- 0110 = 512 bytes

- 0101 = 256 bytes

- 0100 = 128 bytes

- 0011 = 64 bytes

- 0010 = 32 bytes 0001 = 16 bytes

- 0000 = 8 bytes

- bit 23-21 Unimplemented: Read as '0'

- bit 20 TXDPB: TX Endpoint Double-packet Buffering Control bit

- 1 = Double-packet buffer is supported. This doubles the size set in TXFIFOSZ.

- 0 = Double-packet buffer is not supported

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | NRSTX            | NRST             |  |  |  |  |

| 23:16        | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-0             | R/W-1            | R/W-0            |  |  |  |  |

| 23.10        | LSEOF<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15:8         | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 10.0         | FSEOF<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-1             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R.W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | HSEO              | F<7:0>            |                   |                  |                  |  |  |  |  |

#### REGISTER 11-17: USBEOFRST: USB END-OF-FRAME/SOFT RESET CONTROL REGISTER

#### Legend:

| Logonan           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-26 Unimplemented: Read as '0'

- bit 25 NRSTX: Reset of XCLK Domain bit

- 1 = Reset the XCLK domain, which is clock recovered from the received data by the PHY

- 0 = Normal operation

- bit 24 NRST: Reset of CLK Domain bit

- $\ensuremath{\mathtt{1}}$  = Reset the CLK domain, which is clock recovered from the peripheral bus

- 0 = Normal operation

- bit 23-16 LSEOF<7:0>: Low-Speed EOF bits These bits set the Low-Speed transaction in units of 1.067 μs (default setting is 121.6 μs) prior to the EOF to stop new transactions from beginning.

## bit 15-8 **FSEOF<7:0>:** Full-Speed EOF bits These bits set the Full-Speed transaction in units of 533.3 μs (default setting is 63.46 μs) prior to the EOF to stop new transactions from beginning.

#### bit 7-0 **HSEOF<7:0>:** Hi-Speed EOF bits These bits set the Hi-Speed transaction in units of 133.3 μs (default setting is 17.07 μs) prior to the EOF to stop new transactions from beginning.

# PIC32MZ Embedded Connectivity (EC) Family

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24     | PSINTV<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16     | PSINTV<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45-0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8      | PSINTV<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0       | R-0               | R-0               | R-0               | R-0               | R-0               | R-y               | R-y              | R-y              |  |  |  |

| 7:0       |                   |                   |                   | PSINTV            | <7:0>             |                   |                  |                  |  |  |  |

#### REGISTER 15-7: DMTPSINTV: POST STATUS CONFIGURE DMT INTERVAL STATUS REGISTER

| Legend:           | y = Value set from Configuration bits on PO |                      |                                  |  |  |  |

|-------------------|---------------------------------------------|----------------------|----------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit                            | U = Unimplemented I  | = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set                            | '0' = Bit is cleared | x = Bit is unknown               |  |  |  |

bit 31-8 **PSINTV<31:0>:** DMT Window Interval Configuration Status bits

This is always the value of the DMTINTV<2:0> bits in the DEVCFG1 Configuration register.

#### **SQI Control Registers** 20.1

#### TABLE 20-1: SERIAL QUADRATURE INTERFACE (SQI) REGISTER MAP

| sse                         |                  |           |                               |                                                                                                                                             |             |                  |             |               |              | Bits          | 5              |               |             |              |               |             |              |               |            |

|-----------------------------|------------------|-----------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------|-------------|---------------|--------------|---------------|----------------|---------------|-------------|--------------|---------------|-------------|--------------|---------------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range | 31/15                         | 30/14                                                                                                                                       | 29/13       | 28/12            | 27/11       | 26/10         | 25/9         | 24/8          | 23/7           | 22/6          | 21/5        | 20/4         | 19/3          | 18/2        | 17/1         | 16/0          | All Resets |

| 2000                        | SQI1             | 31:16     |                               | —                                                                                                                                           | _           | —                | —           | —             | —            | —             | DUN            | MYBYTES<      | :2:0>       | AD           | DRBYTES       | <2:0>       | READOPC      | ODE<7:6>      | 0000       |

| 2000                        | XCON1            | 15:0      |                               |                                                                                                                                             | READOPCO    | DDE<5:0>         |             |               | TYPED        | ATA<1:0>      | TYPEDU         | MMY<1:0>      | TYPEMO      | DE<1:0>      | TYPEAD        | DR<1:0>     | TYPEC        | /ID<1:0>      | 0000       |

| 2004                        | SQI1             | 31:16     | -                             |                                                                                                                                             |             |                  |             |               |              |               | 0000           |               |             |              |               |             |              |               |            |

| 2004                        | XCON2            | 15:0      | —                             | -         -         DEVSEL<1:0>         MODEBYTES<1:0>         MODECODE<7:0>         00                                                     |             |                  |             |               |              |               | 0000           |               |             |              |               |             |              |               |            |

| 2008                        | SQI1CFG          | 31:16     | SQIEN                         | DIEN         -         -         -         CSEN<1:0>         -         -         DATAEN<1:0>         -         -         RESET         0000 |             |                  |             |               |              |               |                |               |             |              |               |             |              |               |            |

| 2000                        | SQLICIG          | 15:0      | —                             | _                                                                                                                                           |             | BURSTEN          | —           | HOLD          | WP           | SERMODE       | RXLATCH        | —             | LSBF        | CPOL         | CPHA          |             | MODE<2:0>    |               | 0000       |

| 200C                        | SQI1CON          | 31:16     | —                             | —                                                                                                                                           | —           | —                | —           | —             | —            | —             | —              | DASSERT       | DEVSE       | L<1:0>       | LANEMO        | DE<1:0>     | CMDIN        | IT<1:0>       | 0000       |

| 2000                        | ognoon           | 15:0      |                               | TXRXCOUNT<15:0> 0000                                                                                                                        |             |                  |             |               |              |               |                |               |             |              |               |             |              |               |            |

| 2010                        | SQI1             | 31:16     | —                             | —                                                                                                                                           | —           | —                | —           | _             | _            | —             | _              | —             | _           | _            | _             | —           | —            | —             | 0000       |

|                             | CLKCON           | 15:0      |                               |                                                                                                                                             |             | CLKDIV<7:        | 0>          |               |              |               | _              | —             | —           | -            | —             | —           | STABLE       | EN            | 0000       |

| 2014                        | SQI1             | 31:16     | _                             | _                                                                                                                                           |             | —                | —           |               |              | —             | _              | _             | _           | —            | —             | —           | _            | _             | 0000       |

|                             | CMDTHR           | 15:0      | —                             | -                                                                                                                                           | _           |                  | TXCM        | 1DTHR<4:(     | )>           |               | _              | —             | —           |              | F             | RXCMDTHR    | <4:0>        |               | 0000       |

| 2018                        | SQI1             | 31:16     | —                             | —                                                                                                                                           | -           | —                | —           | —             | —            | —             | -              | —             | —           | —            | —             | —           | —            | —             | 0000       |

| 2010                        | INTTHR           | 15:0      | D TXINTTHR<4:0> RXINTTHR<4:0> |                                                                                                                                             |             |                  |             |               |              | 0000          |                |               |             |              |               |             |              |               |            |

|                             | SQI1             | 31:16     | —                             | —                                                                                                                                           | —           | —                | —           | —             | —            | —             | —              | —             | —           | —            | —             | —           | —            | —             | 0000       |

| 201C                        | INTEN            | 15:0      | —                             | —                                                                                                                                           | —           | —                | —           | PKT<br>COMPIE | BD<br>DONEIE | CON<br>THRIE  | CON<br>EMPTYIE | CON<br>FULLIE | RX<br>THRIE | RX<br>FULLIE | RX<br>EMPTYIE | TX<br>THRIE | TX<br>FULLIE | TX<br>EMPTYIE | 0000       |

|                             | SQI1             | 31:16     | _                             | _                                                                                                                                           | —           |                  | _           |               | _            |               |                | _             | _           | -            | _             | _           | _            |               | 0000       |

| 2020                        | INTSTAT          | 15:0      | -                             | —                                                                                                                                           | —           | —                | —           | PKT<br>COMPIF | BD<br>DONEIF | CON<br>THRIF  | CON<br>EMPTYIF | CON<br>FULLIF | RX<br>THRIF | RX<br>FULLIF | RX<br>EMPTYIF | TX<br>THRIF | TX<br>FULLIF | TX<br>EMPTYIF | 0000       |

| 2024                        | SQI1             | 31:16     |                               |                                                                                                                                             |             |                  |             |               |              | TXDATA<       | 31:16>         |               |             |              |               |             |              |               | 0000       |

| 2024                        | TXDATA           | 15:0      |                               |                                                                                                                                             |             |                  |             |               |              | TXDATA<       | :15:0>         |               |             |              |               |             |              |               | 0000       |

| 0000                        | SQI1             | 31:16     |                               |                                                                                                                                             |             |                  |             |               |              | RXDATA<       | 31:16>         |               |             |              |               |             |              |               | 0000       |

| 2028                        | RXDATA           | 15:0      |                               |                                                                                                                                             |             |                  |             |               |              | RXDATA-       | <15:0>         |               |             |              |               |             |              |               | 0000       |

| 2020                        | SQI1             | 31:16     | —                             | -                                                                                                                                           | _           | —                | _           |               | _            | _             |                |               |             | TXFIFC       | )FREE<7:0>    |             |              |               | 0000       |

| 202C                        | STAT1            | 15:0      | _                             | -                                                                                                                                           | —           | —                | _           | _             | _            |               |                |               |             | RXFIF        | OCNT<7:0>     |             |              |               | 0000       |

| 2030                        | SQI1             | 31:16     |                               | _                                                                                                                                           | —           | _                | _           |               | -            | _             | _              | _             | _           | -            | _             | _           | _            | _             | 0000       |

| 2030                        | STAT2            | 15:0      | —                             | —                                                                                                                                           | —           | —                | —           | _             | —            | _             | _              | SQID3         | SQID2       | SQID1        | SQID0         | _           | RXUN         | TXOV          | 00x0       |

| 2024                        | SQI1             | 31:16     |                               | _                                                                                                                                           | —           | _                | _           |               | -            | _             | _              | _             | _           | -            | _             | _           | _            | _             | 0000       |

| 2034                        | BDCON            | 15:0      |                               | —                                                                                                                                           | —           |                  | —           | —             | —            | —             | —              | —             |             | _            | —             | START       | POLLEN       | DMAEN         | 0000       |

| 2038                        | SQI1BD           | 31:16     |                               |                                                                                                                                             |             |                  |             |               | BI           | DCURRADE      | )R<31:16>      |               |             |              |               |             |              |               | 0000       |

| 2038                        | CURADD           | 15:0      |                               |                                                                                                                                             |             |                  |             |               | В            | DCURRAD       | DR<15:0>       |               |             |              |               |             |              |               | 0000       |

| 2040                        | SQI1BD           | 31:16     |                               |                                                                                                                                             |             |                  |             |               |              | BDADDR<       | :31:16>        |               |             |              |               |             |              |               | 0000       |

| 2040                        | BASEADD          | 15:0      |                               |                                                                                                                                             |             |                  |             |               |              | <b>BDADDR</b> | <15:0>         |               |             |              |               |             |              |               | 0000       |

| 2044                        | SQI1BD           | 31:16     | _                             | _                                                                                                                                           | _           | —                | —           | —             | —            | —             | —              | —             |             | BDSTA        | ATE<3:0>      |             | DMASTART     | DMAACTV       | 0000       |

| 2044                        | STAT             | 15:0      |                               | BDCON<15:0> 0000                                                                                                                            |             |                  |             |               |              |               |                |               |             |              |               |             |              |               |            |

| Legen                       | d: x =           | unknov    | vn value on                   | Reset; — = un                                                                                                                               | implemented | , read as '0'. R | eset values | are shown     | in hexaded   | imal.         |                |               |             |              |               |             |              |               |            |

PIC32MZ Embedded **Connectivity (EC) Family**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | —                 | —                    | -                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | -                    | -                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CLKDIV<           | :7:0> <sup>(1)</sup> |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0               | R-0              | R/W-0            |

| 7:0          |                   |                   |                   |                   | _                    |                   | STABLE           | EN               |

#### REGISTER 20-5: SQI1CLKCON: SQI CLOCK CONTROL REGISTER

#### Legend:

| 0                 |                  |                        |                    |   |

|-------------------|------------------|------------------------|--------------------|---|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        | 1 |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown | 1 |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-8 CLKDIV<7:0>: SQI Clock TSQI Frequency Select bit<sup>(1)</sup>

10000000 = Base clock TBC is divided by 512 01000000 = Base clock TBC is divided by 256 00100000 = Base clock TBC is divided by 128 00010000 = Base clock TBC is divided by 64 00001000 = Base clock TBC is divided by 32 00000100 = Base clock TBC is divided by 16 00000010 = Base clock TBC is divided by 8 00000001 = Base clock TBC is divided by 4 00000000 = Base clock TBC is divided by 2

Setting these bits to '0000000' specifies the highest frequency of the SQI clock.

- bit 7-2 Unimplemented: Read as '0'

- bit 1 STABLE: TSQI Clock Stable Select bit

This bit is set to '1' when the SQI clock, TsQI, is stable after writing a '1' to the EN bit.

- 1 = Tsqi clock is stable

- 0 = TSQI clock is not stable

#### bit 0 EN: TSQI Clock Enable Select bit

When clock oscillation is stable, the SQI module will set the STABLE bit to '1'.

1 = Enable the SQI clock (TsQI) (when clock oscillation is stable, the SQI module sets the STABLE bit to '1')

Disable the SQI clock (TsQI) (the SQI module should stop its clock to enter a low power state); SFRs can still be accessed, as they use PBCLK5

## **Note 1:** Refer to Table in **Section 37.0 "Electrical Characteristics**" for the maximum clock frequency specifications.

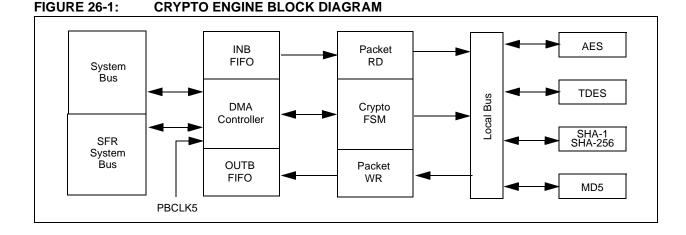

#### 26.0 CRYPTO ENGINE

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 49. "Crypto Engine (CE) and Random Number Generator (RNG)" (DS60001246), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).