Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 120                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

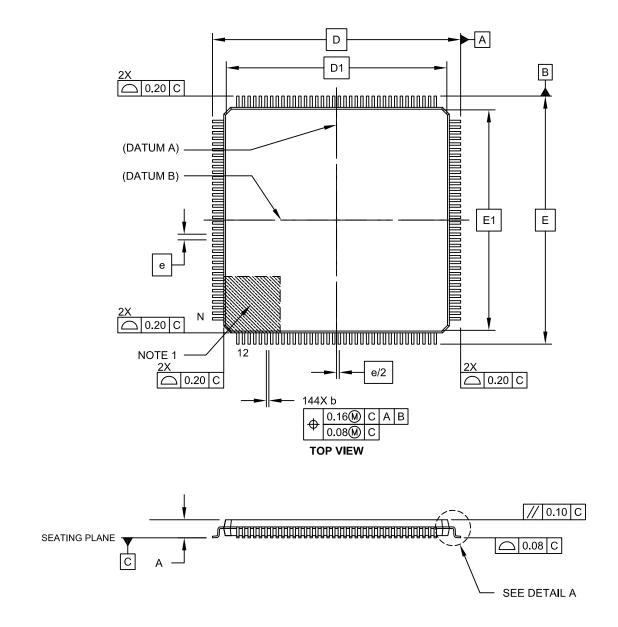

| Package / Case             | 144-LQFP                                                                          |

| Supplier Device Package    | 144-LQFP (20x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048ecg144t-i-pl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The MIPS architecture defines that the result of a multiply or divide operation be placed in one of four pairs of HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

The MDU also implements various shift instructions operating on the HI/LO register and multiply instructions as defined in the DSP ASE. The MDU supports all of the data types required for this purpose and includes three extra HI/LO registers as defined by the ASE.

Table 3-2 lists the latencies and repeat rates for the DSP multiply and dot-product operations. The approximate latencies and repeat rates are listed in terms of pipeline clocks.

| TABLE 3-2: | DSP-RELATED LATENCIES |

|------------|-----------------------|

|            | AND REPEAT RATES      |

| Op code                                                        | Latency | Repeat<br>Rate |

|----------------------------------------------------------------|---------|----------------|

| Multiply and dot-product without saturation after accumulation | 5       | 1              |

| Multiply and dot-product with saturation after accumulation    | 5       | 1              |

| Multiply without accumulation                                  | 5       | 1              |

## 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation and cache protocols, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as cache size and set associativity, and the presence of options like microMIPS, is also available by accessing the CP0 registers, listed in Table 3-3.

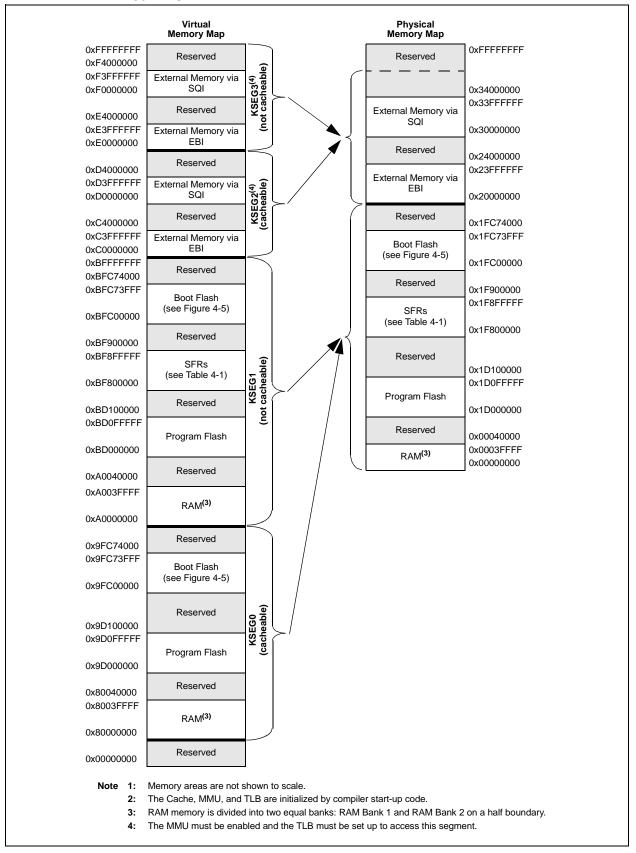

## FIGURE 4-2: MEMORY MAP FOR DEVICES WITH 1024 KB OF PROGRAM MEMORY AND 256 KB OF RAM<sup>(1,2)</sup>

## TABLE 4-16: SYSTEM BUS TARGET 8 REGISTER MAP

| ess                         |                  |                                  |              |       |       |         |       |       |       |         | Bits     |      |          |      |        |        |        |        |               |

|-----------------------------|------------------|----------------------------------|--------------|-------|-------|---------|-------|-------|-------|---------|----------|------|----------|------|--------|--------|--------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range                        | 31/15        | 30/14 | 29/13 | 28/12   | 27/11 | 26/10 | 25/9  | 24/8    | 23/7     | 22/6 | 21/5     | 20/4 | 19/3   | 18/2   | 17/1   | 16/0   | All<br>Resets |

| A020                        | SBT8ELOG1        | 31:16                            | MULTI        | —     |       | _       |       | CODE  | <3:0> |         | _        |      | —        |      | _      | _      | _      |        | 0000          |

| A020                        | SBIELOGI         | 15:0 INITID<7:0> REGION<3:0> —   |              |       |       |         |       |       | C     | MD<2:0> |          | 0000 |          |      |        |        |        |        |               |

| A024                        | SBT8ELOG2        | 31:16                            |              | -     |       | -       | _     |       | _     | _       |          |      | _        |      |        | -      | _      |        | 0000          |

| A024                        | 3BT0EL0G2        | 15:0                             |              | -     |       | -       | _     |       | _     | _       |          |      | _        |      |        | -      | GROU   | P<1:0> | 0000          |

| A028                        | SBT8ECON         | 31:16                            |              | -     |       | -       | _     |       | _     | ERRP    |          |      | _        |      |        | -      | _      |        | 0000          |

| A020                        | SBISECON         | 15:0                             |              | -     |       | -       | _     |       | _     | _       |          |      | _        |      |        | -      | _      |        | 0000          |

| A030                        | SBT8ECLRS        | 31:16                            | _            | —     | -     | —       | —     | _     | —     | _       | _        | _    | —        | _    | —      | _      | —      | -      | 0000          |

| A030                        | SBIOLCERS        | 15:0                             | _            | —     | -     | —       | —     | _     | —     | _       | _        | _    | —        | _    | —      | _      | —      | CLEAR  | 0000          |

| A038                        | SBT8ECLRM        | 31:16                            |              | _     | _     | —       | —     | _     | —     | —       | —        | _    | —        | _    | —      | _      |        | _      | 0000          |

| A030                        | SBIBLCERM        | 15:0                             | _            | —     | -     | —       | —     | _     | —     | _       | _        | _    | —        | _    | —      | _      | —      | CLEAR  | 0000          |

| A040                        | SBT8REG0         | 31:16                            |              |       |       |         |       |       |       | BAS     | SE<21:6> |      |          |      |        |        |        |        | xxxx          |

| A040                        | SBIOKEGO         | 15:0                             |              |       | BA    | SE<5:0> |       |       | PRI   | —       |          |      | SIZE<4:0 | >    |        | _      |        | _      | xxxx          |

| A050                        | SBT8RD0          | 31:16                            |              | —     | _     | —       | —     | _     | —     | —       | —        | _    | —        | _    | —      | —      |        | _      | xxxx          |

| 7030                        | SETUKED          | 15:0                             | —            | —     | _     | _       | —     | _     | _     | —       | —        | _    | _        | _    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| A058                        | SBT8WR0          | 31:16                            | —            | —     | _     | _       | —     | _     | _     | —       | —        | _    | _        | _    | _      | _      | _      | _      | xxxx          |

| 7030                        | 30100000         | 15:0                             | —            | —     | _     | —       | —     | _     | —     | —       | —        | _    | —        | _    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| A060                        | SBT8REG1         | 31:16                            | 6 BASE<21:6> |       |       |         |       |       |       |         |          |      |          | xxxx |        |        |        |        |               |

| 7000                        | SETUREOT         | 15:0 BASE<5:0> PRI — SIZE<4:0> — |              |       |       |         |       |       | —     |         | _        | xxxx |          |      |        |        |        |        |               |

| A070                        | SBT8RD1          | 31:16                            |              | —     | _     | —       | —     | _     | —     | —       | —        | _    | —        | _    | —      | —      |        | _      | xxxx          |

| 7010                        | 0010101          | 15:0                             | —            | —     | _     | _       | _     | _     | _     | —       | —        | _    | _        | _    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| A078                        | SBT8WR1          | 31:16                            | —            | —     | _     | _       | _     | _     | _     | —       | —        | _    | _        | _    | _      | _      | -      | —      | xxxx          |

| 1.070                       | <b>GB10WI</b> (1 | 15:0                             | —            | —     | _     | —       | —     | _     | _     | _       | _        | —    | _        | _    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

© 2013-2016 Microchip Technology Inc.

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |  |

| 31:24        | NVMKEY<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 22.16        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |  |

| 23:16        | NVMKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |  |

| 15:8         | NVMKEY<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7.0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |  |

| 7:0          | NVMKEY<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

### REGISTER 5-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

## Legend:

| 8                 |                  |                      |                    |  |

|-------------------|------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

bit 31-0 **NVMKEY<31:0>:** Unlock Register bits These bits are write-only, and read as '0' on any read

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

## REGISTER 5-3: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7             | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 04.04        | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31:24        | NVMADDR<31:24> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 00.40        | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 23:16        | NVMADDR<23:16> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 45-0         | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15:8         | NVMADDR<15:8> <sup>(1)</sup>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7.0          | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 7:0          | NVMADDR<7:0> <sup>(1)</sup>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 NVMADDR<31:0>: Flash Address bits<sup>(1)</sup>

| NVMOP<3:0><br>Selection                                                                                                                                          | Flash Address Bits (NVMADDR<31:0>)                                                     |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| Page Erase                                                                                                                                                       | Address identifies the page to erase (NVMADDR<13:0> are ignored).                      |  |  |  |  |

| Row Program                                                                                                                                                      | Address identifies the row to program (NVMADDR<11:0> are ignored).                     |  |  |  |  |

| Word Program                                                                                                                                                     | Address identifies the word to program (NVMADDR<1:0> are ignored).                     |  |  |  |  |

| Quad Word Program                                                                                                                                                | Address identifies the quad word (128-bit) to program (NVMADDR<3:0> bits are ignored). |  |  |  |  |

| <b>Note 1:</b> For all other NVMOP<3:0> bit settings, the Flash address is ignored. See the NV register (Register 5-1) for additional information on these bits. |                                                                                        |  |  |  |  |

**Note:** The bits in this register are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

|                             | BLE 7-3:                        | II            | NIERR |       | EGISTE |       | (CONTI | NUED) |                |                |          |      |      |      |      |      |        |       |            |

|-----------------------------|---------------------------------|---------------|-------|-------|--------|-------|--------|-------|----------------|----------------|----------|------|------|------|------|------|--------|-------|------------|

| ess                         | _                               | æ             |       |       |        |       |        |       |                | В              | its      |      |      |      |      |      |        |       | s          |

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13  | 28/12 | 27/11  | 26/10 | 25/9           | 24/8           | 23/7     | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0  | All Resets |

| 0660                        | OFF072                          | 31:16         | _     | _     | —      | —     | _      | —     | _              | —              |          |      | —    | —    | _    |      | VOFF<1 | 7:16> | 0000       |

| 0000                        | 011072                          | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0664                        | OFF073                          | 31:16         | _     | _     | —      | —     | _      |       | —              | —              | _        | _    | —    | —    | —    | _    | VOFF<1 |       | 0000       |

|                             |                                 | 15:0          |       |       | 1      |       |        |       |                | VOFF<15:1      |          |      |      |      |      |      |        |       | 0000       |

| 0668                        | OFF074                          | 31:16         | —     | —     | _      | —     | _      | —     | —              | -              | _        | _    | _    | —    |      | _    | VOFF<1 | 7:16> | 0000       |

|                             |                                 | 15:0          |       |       | 1      | 1     |        | i     |                | VOFF<15:1      | >        | i    | i    | i    | i    |      | VOFF<1 |       | 0000       |

| 066C                        | OFF075                          | 31:16<br>15:0 | —     |       | _      | _     |        | —     | —              |                |          |      | _    | _    |      | _    | VUFF<1 | 7:16> | 0000       |

|                             |                                 | 31:16         | _     |       |        |       |        | _     | _              | VUFF<15.1      | <u> </u> |      |      |      |      | _    | VOFF<1 | 7:16> | 0000       |

| 0670                        | OFF076                          | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      |          |      |      |      |      |      | VOITS  |       | 0000       |

|                             | (1)                             | 31:16         | _     | _     | _      |       | _      | _     | _              | _              | _        | _    | _    | _    | _    |      | VOFF<1 |       | 0000       |

| 0674                        | OFF077 <sup>(2)</sup>           | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | -     | 0000       |

|                             | . (2)                           | 31:16         | _     | _     | _      | _     | _      | _     | _              | _              | _        | _    | _    | _    | _    | _    | VOFF<1 | 7:16> | 0000       |

| 0678                        | OFF078 <sup>(2)</sup>           | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0670                        | OFF079 <sup>(2)</sup>           | 31:16         | _     | _     | —      | _     | —      | —     | —              | _              | _        | _    | —    | —    | _    | _    | VOFF<1 | 7:16> | 0000       |

| 067C                        | OFF0/9 /                        | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0680                        | OFF080 <sup>(2)</sup>           | 31:16         | _     | _     | —      | —     | _      | —     | —              | —              | _        | —    | —    | —    | —    | _    | VOFF<1 | 7:16> | 0000       |

| 0000                        | 011000                          | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0684                        | OFF081 <sup>(2)</sup>           | 31:16         | —     | —     | —      | —     | —      | —     | —              | —              | _        | —    | —    | —    | —    | —    | VOFF<1 | 7:16> | 0000       |

|                             | 0.1.001                         | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0688                        | OFF082 <sup>(2)</sup>           | 31:16         | —     | —     | —      | —     | —      | —     | _              | —              |          | —    | _    | —    | _    |      | VOFF<1 | 7:16> | 0000       |

|                             |                                 | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      |          |      |      |      |      |      |        | _     | 0000       |

| 068C                        | OFF083 <sup>(2)</sup>           | 31:16         | —     | —     | —      | —     | —      | —     | _              |                | _        | _    | —    | —    | —    |      | VOFF<1 |       | 0000       |

|                             |                                 | 15:0<br>31:16 | _     | _     | _      |       |        |       |                | VOFF<15:1      |          |      | _    | _    | _    |      | VOFF<1 |       | 0000       |

| 0690                        | OFF084 <sup>(2)</sup>           | 15:0          | _     |       | _      | —     | _      | —     | —              | —<br>VOFF<15:1 | _        | _    |      |      |      |      | V0FF<1 |       | 0000       |

|                             |                                 | 31:16         |       |       |        |       | _      | _     | _              | VUFF<15.1      | <u> </u> |      |      |      |      |      | VOFF<1 |       | 0000       |

| 0694                        | OFF085 <sup>(2)</sup>           | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      |          |      |      | 1    |      |      | 0.10   |       | 0000       |

|                             |                                 | 31:16         | _     | _     | _      | —     | _      | _     | _              | _              |          |      | _    | —    | —    | _    | VOFF<1 | 7:16> | 0000       |

| 0698                        | OFF086 <sup>(2)</sup>           | 15:0          |       |       |        |       |        | 1     |                | VOFF<15:1      |          | 1    |      | 1    | 1    |      |        | _     | 0000       |

|                             | l                               |               |       |       |        |       |        |       | in have de sin |                |          |      |      |      |      |      |        |       |            |

#### TARIE 7-3. INTEDDUDT DECISTED MAD (CONTINUED)

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV **Registers**" for more information.

2:

This bit or register is not available on 64-pin devices. This bit or register is not available on devices without a CAN module. 3:

This bit or register is not available on 100-pin devices. 4:

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

This bit or register is not available on devices without a Crypto module. 7:

This bit or register is not available on 124-pin devices. 8:

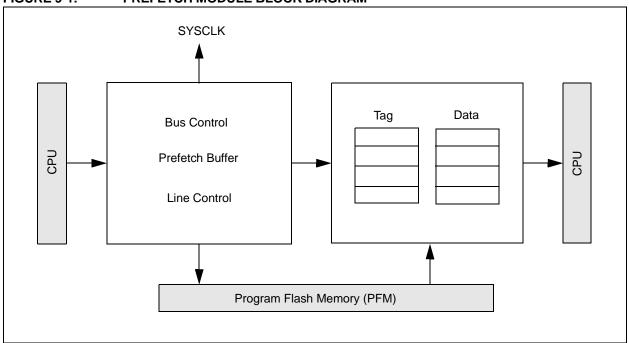

## 9.0 PREFETCH MODULE

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 41. "Prefetch Module for Devices with L1 CPU Cache" (DS60001183), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Prefetch module is a performance enhancing module that is included in PIC32MZ EC family devices. When running at high-clock rates, Wait states must be inserted into Program Flash Memory (PFM) read transactions to meet the access time of the PFM. Wait states can be hidden to the core by prefetching and storing instructions in a temporary holding area that the CPU can access quickly. Although the data path to the CPU is 32 bits wide, the data path to the PFM is 128 bits wide. This wide data path provides the same bandwidth to the CPU as a 32-bit path running at four times the frequency.

The Prefetch module holds a subset of PFM in temporary holding spaces known as lines. Each line contains a tag and data field. Normally, the lines hold a copy of what is currently in memory to make instructions or data available to the CPU without Flash Wait states.

## 9.1 Features

- 4x16 byte fully-associative lines

- One line for CPU instructions

- One line for CPU data

- Two lines for peripheral data

- 16-byte parallel memory fetch

- Configurable predictive prefetch

- Error detection and correction

A simplified block diagram of the Prefetch module is shown in Figure 9-1.

## FIGURE 9-1: PREFETCH MODULE BLOCK DIAGRAM

| ő                         |                                 |               |        |       |           |       |          |       |      | 2      |         |        |        |        |        |        |   |

|---------------------------|---------------------------------|---------------|--------|-------|-----------|-------|----------|-------|------|--------|---------|--------|--------|--------|--------|--------|---|

| Virtual Addre<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13     | 28/12 | 27/11    | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   |   |

|                           | DOLIDOON                        | 31:16         |        |       |           | CHPIG | N<7:0>   |       |      |        | _       | _      | _      | _      | _      | _      |   |

| 1060                      | DCH0CON                         | 15:0          | CHBUSY | _     | CHPIGNEN  | _     | CHPATLEN | _     | —    | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | _      | CHEDET |   |

| 4070                      |                                 | 31:16         | —      |       | —         | _     | —        | —     |      | —      |         |        |        | CHAIR  | Q<7:0> |        |   |

| 1070                      | DCH0ECON                        | 15:0          |        |       |           | CHSIR | Q<7:0>   |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN | _      |   |

| 1080                      | DCH0INT                         | 31:16         | —      | —     | —         | _     | —        | _     | —    | —      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | С |

| 1060                      | DCHUINT                         | 15:0          | —      | -     | —         | _     | —        | _     |      | _      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | С |

| 1090                      | DCH0SSA                         | 31:16<br>15:0 |        |       |           |       |          |       |      | CHSSA  | <31:0>  |        |        |        |        |        |   |

| 10A0                      | DCH0DSA                         | 31:16<br>15:0 |        |       |           |       |          |       |      | CHDSA  | <31:0>  |        |        |        |        |        |   |

| 4000                      | DOLIGOOIZ                       | 31:16         | —      | _     | —         | _     | —        | _     | _    | —      | _       | _      | —      | _      | _      | _      |   |

| 1080                      | DCH0SSIZ                        | 15:0          |        |       |           |       |          |       |      | CHSSIZ | <15:0>  |        |        |        |        |        |   |

| 1000                      | DCH0DSIZ                        | 31:16         | —      | —     | —         | —     | —        | _     | —    | —      | —       | —      | —      | —      | —      | —      |   |

| 1000                      | DCHUDSIZ                        | 15:0          |        |       |           |       |          |       |      | CHDSIZ | <15:0>  |        |        |        |        |        |   |

| 1000                      | DCH0SPTR                        | 31:16         | _      |       | _         | _     | —        | _     |      | —      | _       |        | _      | _      | _      | _      |   |

| 1000                      | DCH03FTK                        | 15:0          |        |       |           |       |          |       |      | CHSPTR | R<15:0> |        |        |        |        |        |   |

| 10E0                      | DCH0DPTR                        | 31:16         | —      | _     | —         | _     | —        | _     | —    | —      | —       | —      | —      | —      | —      | —      |   |

| IULU                      |                                 | 15:0          |        |       |           |       |          |       |      | CHDPTR | R<15:0> |        |        |        |        |        |   |

| 10F0                      | DCH0CSIZ                        | 31:16         | —      | —     | —         | —     | —        | —     | —    | —      | —       | —      | —      | —      | —      | —      |   |

| 101.0                     | DONOCOL                         | 15:0          |        |       | · · · · · |       |          |       |      | CHCSIZ | <15:0>  |        |        |        |        |        | _ |

| 1100                      | DCH0CPTR                        | 31:16         | —      | _     | —         | _     | —        | _     | _    | —      | —       | —      | _      | _      | _      | _      |   |

|                           | - 5                             | 15:0          | ,      |       |           |       |          |       |      | CHCPTR | <15:0>  |        |        |        |        |        | _ |

| 1110                      | DCH0DAT                         | 31:16         | —      | —     | —         | _     | —        | —     | —    | —      | —       | —      | —      | —      | —      | —      |   |

|                           |                                 | 15.0          |        |       |           |       |          |       |      | CHPDAT | -15.0   |        |        |        |        |        |   |

Bits

## TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

CHPIGNEN

\_

\_

\_

CHPIGN<7:0>

CHSIRQ<7:0>

CHPATLEN

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

CHPDAT<15:0>

CHSSA<31:0>

CHDSA<31:0>

CHEN

CHSDIE

CHSDIF

CHAED

CHSHIE

CHSHIF

CFORCE CABORT

CHCHN

PATEN

CHDDIE

CHDDIF

CHAEN

SIRQEN

CHDHIE

CHDHIF

CHAIRQ<7:0>

\_

AIRQEN

CHBCIE

CHBCIF

CHEDET

\_

CHCCIE

CHCCIF

CHCHNS

\_

\_

\_

SS

15:0

31:16

15:0

31:16

15:0

31:16

15:0

31:16

15:0

31:16

15:0

CHBUSY

\_\_\_\_

\_

\_

\_

\_

\_

\_

1120 DCH1CON

1130 DCH1ECON

1150 DCH1SSA

1160 DCH1DSA

DCH1INT

1140

All Resets

0000

0000

OOFF

FF00

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

OOFF

FF00

0000

0000

0000

0000

0000

16/0

\_

CHERIF

\_

\_

\_

\_

\_

\_

\_

CHERIE

CHERIF

CHPRI<1:0>

17/1

—

\_

CHTAIE

CHTAIF

\_

\_

—

\_

\_

\_

—

CHTAIE

CHTAIF

CHPRI<1:0>

| REGISTE | R 10-9: DCHxINT: DMA CHANNEL x INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | CHDDIF: Channel Destination Done Interrupt Flag bit                                                                                                                                        |

|         | <ul> <li>1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ)</li> <li>0 = No interrupt is pending</li> </ul>                                                  |

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul> <li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li> <li>0 = No interrupt is pending</li> </ul>                                                       |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected<br/>Either the source or the destination address is invalid.</li> <li>0 = No interrupt is pending</li> </ul>                        |

# REGISTER 11-5: USBIE0CSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 0)

|              | 1-                |                   | /                 |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|              | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0, HC         | R/W-0            | R/W-0, HC        |

| 31:24        |                   |                   |                   |                   |                   |                   |                  | FLSHFIFO         |

|              |                   | _                 | _                 | _                 | DISPING           | DTWREN            | DATATGGL         | FLOHFIFU         |

|              | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/C-0, HS         | R/W-0, HS         | R-0, HS           | R-0              | R-0              |

| 23:16        | SVCSETEND         | SVCRPR            | SENDSTALL         | SETUPEND          | DATAEND           | SENTSTALL         | TXPKTRDY         | RXPKTRDY         |

|              | NAKTMOUT          | STATPKT           | REQPKT            | ERROR             | SETUPPKT          | RXSTALL           |                  | NAFNINDI         |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | —                 | —                 | —                 | —                 |                   | —                 | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7.0          |                   | _                 |                   | _                 |                   | _                 | _                | _                |

| Legend:           | HC = Hardware Cleared | HS = Hardware Set         |                    |

|-------------------|-----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-28 Unimplemented: Read as '0'

- bit 27 **DISPING:** Disable Ping tokens control bit (*Host mode*)

- 1 = USB Module will not issue PING tokens in data and status phases of a Hi-Speed Control transfer

0 = Ping tokens are issued

- bit 26 DTWREN: Data Toggle Write Enable bit (*Host mode*)

1 = Enable the current state of the Endpoint 0 data toggle to be written. Automatically cleared.

0 = Disable data toggle write

- bit 25 **DATATGGL:** Data Toggle bit (*Host mode*) When read, this bit indicates the current state of the Endpoint 0 data toggle. If DTWREN = 1, this bit is writable with the desired setting.

- If DTWREN = 0, this bit is read-only.

- bit 24 FLSHFIFO: Flush FIFO Control bit

- 1 = Flush the next packet to be transmitted/read from the Endpoint 0 FIFO. The FIFO pointer is reset and the TXPKTRDY/RXPKTRDY bit is cleared. Automatically cleared when the operation completes. Should only be used when TXPKTRDY/RXPKTRDY = 1.

- 0 = No Flush operation

### bit 23 SVCSETEND: Clear SETUPEND Control bit (Device mode)

- 1 = Clear the SETUPEND bit in this register. This bit is automatically cleared.

- 0 = Do not clear

### NAKTMOUT: NAK Time-out Control bit (Host mode)

- 1 = Endpoint 0 is halted following the receipt of NAK responses for longer than the time set by the NAKLIM<4:0> bits (USBICSR<28:24>)

- 0 = Allow the endpoint to continue

- bit 22 **SVCRPR:** Serviced RXPKTRDY Clear Control bit (*Device mode*)

- 1 = Clear the RXPKTRDY bit in this register. This bit is automatically cleared.

- 0 = Do not clear

### STATPKT: Status Stage Transaction Control bit (Host mode)

- 1 = When set at the same time as the TXPKTRDY or REQPKT bit is set, performs a status stage transaction

- 0 = Do not perform a status stage transaction

## REGISTER 11-6: USBIE0CSR2: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 2 (ENDPOINT 0)

|              |                   |                   | /                 |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | —                 | _                 |                   |                   | 1                 | NAKLIM<4:0>       |                  |                  |

| 22.16        | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | SPEED<1:0>        |                   | _                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 |                   |                   |                   | RXCNT<6:0>        |                   |                  |                  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 NAKLIM<4:0>: Endpoint 0 NAK Limit bits

The number of frames/microframes (Hi-Speed transfers) after which Endpoint 0 should time-out on receiving a stream of NAK responses.

- bit 23-22 SPEED<1:0>: Operating Speed Control bits

- 11 = Low-Speed

- 10 = Full-Speed

- 01 = Hi-Speed

- 00 = Reserved

- bit 21-7 Unimplemented: Read as '0'

- bit 6-0 **RXCNT<6:0>:** Receive Count bits

The number of received data bytes in the Endpoint 0 FIFO. The value returned changes as the contents of the FIFO change and is only valid while RXPKTRDY is set.

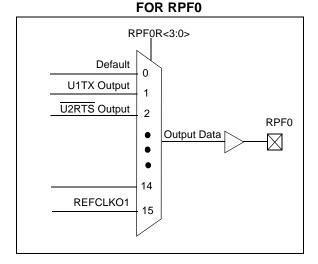

## 12.3.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 12-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 12-2 and Figure 12-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

## FIGURE 12-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT

### 12.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32MZ EC devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

## 12.3.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 42. "Oscillators** with Enhanced PLL" (DS60001250) in the *"PIC32 Family Reference Manual"* for details.

## 12.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and reenable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | _                 |                   | _                 | _                 |                   | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   |                   | _                 |                   |                  | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 |                   |                  | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

#### **REGISTER 12-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (x = A - G)

#### Legend:

- R = Readable bit

- W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

- ON: Change Notice (CN) Control ON bit bit 15

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Control bit

- 1 = CPU Idle mode halts CN operation

- 0 = CPU Idle mode does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 |                   | _                 |                   | —                | —                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 |                   |                   | _                 |                   | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | _                 | _                 | —                 | —                | —                |

| 7.0          | U-0               | R/W-0, HC         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | SWRST             | SWAPEN            | _                 | _                 | BDPCHST           | BDPPLEN          | DMAEN            |

## REGISTER 26-2: CECON: CRYPTO ENGINE CONTROL REGISTER

| Legend:           |                  | HC = Hardware Cleare  | d                  |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

### bit 31-7 Unimplemented: Read as '0'

- bit 6 SWRST: Software Reset bit

- 1 = Initiate a software reset of the Crypto Engine

- 0 = Normal operation

- bit 5 SWAPEN: I/O Swap Enable bit

- 1 = Input data is byte swapped when read by dedicated DMA

- 0 = Input data is not byte swapped when read by dedicated DMA

- bit 4-3 Unimplemented: Read as '0'

#### bit 2 BDPCHST: Buffer Descriptor Processor (BDP) Fetch Enable bit

This bit should be enabled only after all DMA descriptor programming is completed.

- 1 = BDP descriptor fetch is enabled

- 0 = BDP descriptor fetch is disabled

#### bit 1 **BDPPLEN:** Buffer Descriptor Processor Poll Enable bit

This bit should be enabled only after all DMA descriptor programming is completed.

- 1 = Poll for descriptor until valid bit is set

- 0 = Do not poll

## bit 0 DMAEN: DMA Enable bit

- 1 = Crypto Engine DMA is enabled

- 0 = Crypto Engine DMA is disabled

| Bit Range | Bit<br>31/23/15/7            | Bit<br>30/22/14/6 | Bit<br>29/21/13/5            | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2      | Bit<br>25/17/9/1             | Bit<br>24/16/8/0       |

|-----------|------------------------------|-------------------|------------------------------|-------------------|-------------------|------------------------|------------------------------|------------------------|

| 24.24     | U-0                          | U-0               | U-0                          | U-0               | U-0               | U-0                    | R/W-0                        | R/W-0                  |

| 31:24     | —                            | _                 | —                            | —                 | —                 | _                      | SH4ALT                       | <1:0> <sup>(1,2)</sup> |

| 00.40     | R/W-0                        | R/W-0             | R/W-0                        | R/W-0             | R/W-0             | R/W-0                  | R/W-0                        | R/W-0                  |

| 23:16     | SH3ALT<1:0> <sup>(1,2)</sup> |                   | SH2ALT<1:0> <sup>(1,2)</sup> |                   | SH1ALT            | <1:0> <sup>(1,2)</sup> | SH0ALT<1:0> <sup>(1,2)</sup> |                        |

| 15.0      | U-0                          | U-0               | U-0                          | U-0               | R/W-0             | R/W-0                  | R/W-0                        | R/W-0                  |

| 15:8      | —                            | _                 | —                            | _                 | SH5MC             | )D<1:0>                | SH4MC                        | )D<1:0>                |

| 7.0       | R/W-0                        | R/W-0             | R/W-0                        | R/W-0             | R/W-0             | R/W-0                  | R/W-0                        | R/W-0                  |

| 7:0       | SH3M0                        | )D<1:0>           | SH2MC                        | )D<1:0>           | SH1MC             | )D<1:0>                | SHOMO                        | )D<1:0>                |

## REGISTER 28-4: AD1IMOD: ADC1 INPUT MODE CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-26 Unimplemented: Read as '0'

## bit 25-24 SH4ALT<1:0>: Analog Input to Dedicated S&H 4 (SH4) Select bits<sup>(1,2)</sup>

- 11 = Reserved

- 10 = Reserved

- 01 = Alternate input AN49

- 00 = Default Class 1 input AN4

#### bit 23-22 SH3ALT<1:0>: Analog Input to Dedicated S&H 3 (SH3) Select bits<sup>(1,2)</sup>

- 11 = Reserved

- 10 = Reserved

- 01 = Alternate input AN48

- 00 = Default Class 1 input AN3

## bit 21-20 SH2ALT<1:0>: Analog Input to Dedicated S&H 2 (SH2) Select bits<sup>(1,2)</sup>

- 11 = Reserved

- 10 = Reserved

- 01 = Alternate input AN47

- 00 = Default Class 1 input AN2

## bit 19-18 SH1ALT<1:0>: Analog Input to Dedicated S&H 1 (SH1) Select bits<sup>(1,2)</sup>

- 11 = Reserved

- 10 = Reserved

- 01 = Alternate input AN46

- 00 = Default Class 1 input AN1

## bit 17-16 SH0ALT<1:0>: Analog Input to Dedicated S&H 0 (SH0) Select bits<sup>(1,2)</sup>

- 11 = Reserved

- 10 = Reserved

- 01 = Alternate input AN45

- 00 = Default Class 1 input AN0

- bit 15-12 Unimplemented: Read as '0'

- **Note 1:** Alternate inputs are only available for Class 1 Inputs.

- 2: When an alternate input is selected (SHxALT<1:0> ≠ 0), the data, status, and control registers for the default Class 1 input are still used. Selecting an alternate input changes the physical input source only.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN27           | MSEL2             | :7<1:0>           |                   |                   | FSEL27<4:0>       |                  |                  |

| 22:46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN26           | MSEL26<1:0>       |                   | FSEL26<4:0>       |                   |                   |                  |                  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | FLTEN25           | MSEL2             | 5<1:0>            |                   |                   | FSEL25<4:0>       |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN24           | MSEL2             | 4<1:0>            |                   |                   | FSEL24<4:0>       |                  |                  |

### REGISTER 29-16: CIFLTCON6: CAN FILTER CONTROL REGISTER 6

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | FLTEN27: Filter 27 Enable bit                                                             |

|-----------|-------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled                                                                     |

|           | 0 = Filter is disabled                                                                    |

| bit 30-29 | MSEL27<1:0>: Filter 27 Mask Select bits                                                   |

|           | 11 = Acceptance Mask 3 selected                                                           |

|           | 10 = Acceptance Mask 2 selected                                                           |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                        |

| bit 28-24 | FSEL27<4:0>: FIFO Selection bits                                                          |

| 511 20 24 | 11111 = Message matching filter is stored in FIFO buffer 31                               |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                               |

|           | •                                                                                         |

|           | •                                                                                         |

|           | •                                                                                         |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                |

| bit 23    | FLTEN26: Filter 26 Enable bit                                                             |

|           | 1 = Filter is enabled                                                                     |

|           | 0 = Filter is disabled                                                                    |

| bit 22-21 | MSEL26<1:0>: Filter 26 Mask Select bits                                                   |

|           | <ul><li>11 = Acceptance Mask 3 selected</li><li>10 = Acceptance Mask 2 selected</li></ul> |

|           | 01 = Acceptance Mask 2 selected                                                           |

|           | 00 = Acceptance Mask 0 selected                                                           |

| bit 20-16 | FSEL26<4:0>: FIFO Selection bits                                                          |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                               |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                               |

|           | •                                                                                         |

|           | •                                                                                         |

|           | •                                                                                         |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                |

| Note:     | The bits in this register can only be modified if the corresponding fil                   |

|           |                                                                                           |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## TABLE 30-5: ETHERNET CONTROLLER REGISTER SUMMARY (CONTINUED)

| ess                         | Register<br>Name <sup>(1)</sup> |               | Bits                                      |               |               |         |               |               |               |               |                |         |               |               |            |         |           |          |     |

|-----------------------------|---------------------------------|---------------|-------------------------------------------|---------------|---------------|---------|---------------|---------------|---------------|---------------|----------------|---------|---------------|---------------|------------|---------|-----------|----------|-----|

| VIRTUAI Address<br>(BF88_#) |                                 | Bit Range     | 31/15                                     | 30/14         | 29/13         | 28/12   | 27/11         | 26/10         | 25/9          | 24/8          | 23/7           | 22/6    | 21/5          | 20/4          | 19/3       | 18/2    | 17/1      | 16/0     |     |

| 2110                        | ETH<br>FRMTXOK                  | 31:16<br>15:0 | —                                         | _             | _             | -       | -             | —             | -             |               | —<br>CNT<15:0> | —       | —             | —             | —          | —       | —         | -        | 00  |

| etth                        |                                 | 31:16         | _                                         | _             | _             | _       | _             | _             | _             | -             |                | _       | —             | _             | _          | _       | _         | _        | 00  |

|                             | SCOLFRM                         | 15:0          |                                           |               |               |         |               |               |               | SCOLFRM       | CNT<15:0>      |         |               |               |            |         |           |          | 00  |

|                             | ETH                             | 31:16         | _                                         | _             | —             | —       | _             | —             | -             | _             | —              | —       | —             | —             | _          | _       | —         | _        | 0   |

| .150                        | MCOLFRM                         | 15:0          |                                           |               |               |         |               |               |               | MCOLFRM       | ICNT<15:0>     |         |               |               |            |         |           |          | 0   |

| 140                         | ETH                             | 31:16         | _                                         | _             | _             | —       | _             | _             | -             | —             | —              | —       | —             | —             | —          | —       | —         | —        | 0   |

| F                           | FRMRXOK                         | 15:0          |                                           |               |               |         |               |               | r             | FRMRXOK       | CNT<15:0>      |         |               |               |            |         |           |          | 0   |

| 2150                        | ETH<br>FCSERR                   | 31:16         | —                                         | _             | _             | —       | _             |               | -             | -             |                | _       |               | _             |            | _       |           |          | 0   |

|                             |                                 | 15:0          |                                           |               |               |         |               |               |               | FCSERRO       | CNT<15:0>      |         |               |               |            |         |           |          | 0   |

| 2160                        | ETH<br>ALGNERR                  | 31:16<br>15:0 | _                                         |               |               | —       | _             |               | _             |               | <br>CNT<15:0>  |         |               |               |            | —       |           |          | 0   |

| -                           |                                 | 31:16         |                                           | _             |               | _       |               |               | _             | _             |                | _       | _             | _             | _          |         |           |          | 0   |

| 200                         | EMAC1<br>CFG1                   | 15:0          | SOFT<br>RESET                             | SIM<br>RESET  | -             | _       | RESET<br>RMCS | RESET<br>RFUN | RESET<br>TMCS | RESET<br>TFUN | _              | _       | _             | LOOPBACK      | TXPAUSE    | RXPAUSE | PASSALL   | RXENABLE |     |

| 2210                        | EMAC1<br>CFG2                   | 31:16         | _                                         | _             |               |         | _             |               | _             | _             | _              | _       | _             |               |            |         |           |          | 0   |

|                             |                                 | 15:0          | _                                         | EXCESS<br>DFR | BP<br>NOBKOFF | NOBKOFF | _             | _             | LONGPRE       | PUREPRE       | AUTOPAD        | VLANPAD | PAD<br>ENABLE | CRC<br>ENABLE | DELAYCRC   | HUGEFRM | LENGTHCK  | FULLDPLX | < 4 |

| 220                         | EMAC1                           | 31:16         | _                                         | -             | —             | —       | —             | _             | -             | _             | -              | _       | -             | _             | _          | _       | -         | -        | 0   |

| 220                         | IPGT                            | 15:0          | _                                         |               | _             | —       | _             | —             | _             | —             | _              |         |               | Bź            | 2BIPKTGP<6 | :0>     |           |          | 0   |

| 230                         | EMAC1                           | 31:16         | _                                         | _             | _             | —       | _             |               | -             | _             | _              | —       |               | —             | _          | _       |           |          | 0   |

| 200                         | IPGR                            | 15:0          | NB2BIPKTGP1<6:0>         NB2BIPKTGP2<6:0> |               |               |         |               |               |               |               | C              |         |               |               |            |         |           |          |     |

| 240                         | EMAC1                           | 31:16         | _                                         |               |               | —       | _             | _             | -             | —             | _              | —       | _             | —             | —          | —       | —         | —        | 0   |

| -                           | CLRT                            | 15:0          | _                                         | _             |               |         | CWINDO        | DW<5:0>       | r             |               | _              | —       | —             | —             |            | RET)    | <<3:0>    |          | 3   |

| 250                         | EMAC1<br>MAXF                   | 31:16         |                                           | _             |               | —       | _             |               | _             | —             |                | _       |               | _             |            | —       |           |          | 0   |

|                             | MAAI                            | 15:0          |                                           |               |               |         |               |               |               | MACMA         | XF<15:0>       |         |               |               |            |         |           |          | 0   |

| 260                         | EMAC1<br>SUPP                   | 31:16<br>15:0 | _                                         | _             | _             | _       | RESET<br>RMII |               |               | SPEED<br>RMII | _              | _       | _             | _             | _          | _       |           |          | 0   |

|                             | EMAC1<br>TEST                   | 31:16         | _                                         |               | _             | _       | _             | _             | _             |               | _              | _       | _             | _             | _          | _       | _         | _        | 0   |

| 270                         |                                 | 15:0          | _                                         | _             | _             | _       | _             | _             | _             | _             | _              | _       | _             | _             | _          | TESTBP  | TESTPAUSE | SHRTQNTA | _   |

|                             |                                 | 31:16         | _                                         | _             | _             | _       | _             | _             | _             | _             | _              | _       | _             | _             | _          | _       | _         | _        | 0   |

| 280                         | EMAC1<br>MCFG                   | 15:0          | RESET<br>MGMT                             | _             | _             | _       | _             | _             | -             | _             | _              | _       |               | CLKSE         | L<3:0>     |         | NOPRE     | SCANINC  |     |

| 290                         | EMAC1                           | 31:16         |                                           |               | —             | _       |               |               | —             |               | _              |         |               |               |            | _       | _         |          | 0   |

| 2290                        | MCMD                            | 15:0          | _                                         | _             | -             | —       | _             | —             | -             | —             | —              | _       | —             | _             | —          | —       | SCAN      | READ     | 0   |

|                             | EMAC1                           | 31:16         |                                           | _             | _             | _       | _             |               | _             |               | -              |         |               | _             |            |         |           | _        | 0   |

x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexad

Note 1: All registers in this table (with the exception of ETHSTAT) have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: Reset values default to the factory programmed value.

#### REGISTER 30-9: ETHPMCS: ETHERNET CONTROLLER PATTERN MATCH CHECKSUM REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |