Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048ech064-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

# **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# TABLE 4-21: SYSTEM BUS TARGET 13 REGISTER MAP

| ess                         |                  |           |       |       |       |          |             |       |       |             | Bits     |      |           |      |         |        |        |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|-------------|-------|-------|-------------|----------|------|-----------|------|---------|--------|--------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11       | 26/10 | 25/9  | 24/8        | 23/7     | 22/6 | 21/5      | 20/4 | 19/3    | 18/2   | 17/1   | 16/0   | All<br>Resets |

|                             |                  | 31:16     | MULTI | —     | —     | —        |             | CODE  | <3:0> |             | _        | —    | -         |      | —       |        | —      |        | 0000          |

| B420                        | SBT13ELOG1       | 15:0      |       |       |       | INI      | INITID<7:0> |       |       | REGION<3:0> |          |      | _         | С    | MD<2:0> |        | 0000   |        |               |

| B424                        | SBT13ELOG2       | 31:16     | _     | _     | —     | —        | _           | _     | _     | _           | —        | _    | —         | _    | _       | _      | _      | _      | 0000          |

| D424                        | SB113ELUG2       | 15:0      | —     | _     | _     | _        | _           | _     | _     | _           |          | _    | _         | _    | _       | _      | GROU   | P<1:0> | 0000          |

| B428                        | 3 SBT13ECON      | 31:16     | —     | _     | _     | _        | _           | _     | _     | ERRP        |          | _    | _         | _    | _       | _      | _      | _      | 0000          |

|                             |                  | 15:0      |       | -     | _     | _        | —           | _     |       | -           | _        | _    |           |      | —       | _      | —      | _      | 0000          |

| P420                        | SBT13ECLRS       | 31:16     |       | -     | _     | _        | —           | _     |       | -           | _        | _    |           |      | —       | _      | —      | _      | 0000          |

| D430                        | SBI ISECLKS      | 15:0      |       |       | _     | —        | —           |       |       |             | _        | _    |           |      | _       |        | _      | CLEAR  | 0000          |

| D120                        | SBT13ECLRM       | 31:16     |       |       | _     | —        | —           |       |       |             | _        | _    |           |      | _       |        | _      |        | 0000          |

| D430                        | SBITSECLKI       | 15:0      |       |       | _     | —        | —           |       |       |             | _        | _    |           |      | _       |        | _      | CLEAR  | 0000          |

| B440                        | SBT13REG0        | 31:16     |       |       |       |          |             |       |       | BA          | SE<21:6> |      |           |      |         |        |        |        | xxxx          |

| D440                        | SBITSREGU        | 15:0      |       |       | BA    | ASE<5:0> |             |       | PRI   |             |          |      | SIZE<4:0: | >    |         |        | _      |        | xxxx          |

| B450                        | SBT13RD0         | 31:16     |       |       | _     | —        | _           |       |       |             | _        | —    |           |      |         |        | _      |        | xxxx          |

| 5450                        | 3BT I3RD0        | 15:0      |       | -     | —     | —        | _           |       |       |             | _        | _    |           |      | GROUP3  | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| B458                        | SBT13WR0         | 31:16     |       | -     | —     | —        | _           |       |       |             | _        | _    |           |      | —       |        | _      |        | xxxx          |

| 5400                        | GBTTSWRU         | 15:0      |       |       | _     | _        | —           |       |       |             | _        | —    |           |      | GROUP3  | GROUP2 | GROUP1 | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-1             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | PWPULOCK          | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        |                   |                   |                   | PWP<2             | 3:16>             |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         |                   |                   |                   | PWP<              | 15:8>             |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | PWP<7:0>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |

# REGISTER 5-6: NVMPWP: PROGRAM FLASH WRITE-PROTECT REGISTER

#### Legend:

| Legena.           |                  |                                          |

|-------------------|------------------|------------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'       |

| -n = Value at POR | '1' = Bit is set | 0' = Bit is cleared $x = Bit is unknown$ |

bit 31 **PWPULOCK:** Program Flash Memory Page Write-protect Unlock bit

1 = Register is not locked and can be modified

0 = Register is locked and cannot be modified

This bit is only clearable and cannot be set except by any reset.

bit 30-24 Unimplemented: Read as '0'

bit 23-0 PWP<23:0>: Flash Program Write-protect (Page) Address bits

Physical memory below address 0x1Dxxxxxx is write protected, where 'xxxxx' is specified by PWP<23:0>. When PWP<23:0> has a value of '0', write protection is disabled for the entire program Flash. If the specified address falls within the page, the entire page and all pages below the current page will be protected.

**Note:** The bits in this register are only writable when the NVMKEY unlock sequence is followed.

# 7.2 Interrupts

The PIC32MZ EC family uses variable offsets for vector spacing. This allows the interrupt vector spacing to be configured according to application needs. A unique interrupt vector offset can be set for each vector using its associated OFFx register.

# TABLE 7-2: INTERRUPT IRQ, VECTOR AND BIT LOCATION

For details on the Variable Offset feature, refer to **8.5.2 "Variable Offset"** in **Section 8. "Interrupt Controller"** (DS60001108) of the *"PIC32 Family Reference Manual"*.

IC32MZ

Π

mbedded

onnectivity

Π

Family

Table 7-2 provides the Interrupt IRQ, vector and bit location information.

| (1)                             |                               | IRQ    |                |          | Interru  | upt Bit Location |              | Persistent |

|---------------------------------|-------------------------------|--------|----------------|----------|----------|------------------|--------------|------------|

| Interrupt Source <sup>(1)</sup> | XC32 Vector Name              | #      | Vector #       | Flag     | Enable   | Priority         | Sub-priority | Interrupt  |

|                                 | Highest N                     | latura | Order Priority |          |          |                  |              |            |

| Core Timer Interrupt            | _CORE_TIMER_VECTOR            | 0      | OFF000<17:1>   | IFS0<0>  | IEC0<0>  | IPC0<4:2>        | IPC0<1:0>    | No         |

| Core Software Interrupt 0       | _CORE_SOFTWARE_0_VECTOR       | 1      | OFF001<17:1>   | IFS0<1>  | IEC0<1>  | IPC0<12:10>      | IPC0<9:8>    | No         |

| Core Software Interrupt 1       | _CORE_SOFTWARE_1_VECTOR       | 2      | OFF002<17:1>   | IFS0<2>  | IEC0<2>  | IPC0<20:18>      | IPC0<17:16>  | No         |

| External Interrupt              | _EXTERNAL_0_VECTOR            | 3      | OFF003<17:1>   | IFS0<3>  | IEC0<3>  | IPC0<28:26>      | IPC0<25:24>  | No         |

| Timer1                          | _TIMER_1_VECTOR               | 4      | OFF004<17:1>   | IFS0<4>  | IEC0<4>  | IPC1<4:2>        | IPC1<1:0>    | No         |

| Input Capture 1 Error           | _INPUT_CAPTURE_1_ERROR_VECTOR | 5      | OFF005<17:1>   | IFS0<5>  | IEC0<5>  | IPC1<12:10>      | IPC1<9:8>    | Yes        |

| Input Capture 1                 | _INPUT_CAPTURE_1_VECTOR       | 6      | OFF006<17:1>   | IFS0<6>  | IEC0<6>  | IPC1<20:18>      | IPC1<17:16>  | Yes        |

| Output Compare 1                | _OUTPUT_COMPARE_1_VECTOR      | 7      | OFF007<17:1>   | IFS0<7>  | IEC0<7>  | IPC1<28:26>      | IPC1<25:24>  | No         |

| External Interrupt 1            | _EXTERNAL_1_VECTOR            | 8      | OFF008<17:1>   | IFS0<8>  | IEC0<8>  | IPC2<4:2>        | IPC2<1:0>    | No         |

| Timer2                          | _TIMER_2_VECTOR               | 9      | OFF009<17:1>   | IFS0<9>  | IEC0<9>  | IPC2<12:10>      | IPC2<9:8>    | No         |

| Input Capture 2 Error           | _INPUT_CAPTURE_2_ERROR_VECTOR | 10     | OFF010<17:1>   | IFS0<10> | IEC0<10> | IPC2<20:18>      | IPC2<17:16>  | Yes        |

| Input Capture 2                 | _INPUT_CAPTURE_2_VECTOR       | 11     | OFF011<17:1>   | IFS0<11> | IEC0<11> | IPC2<28:26>      | IPC2<25:24>  | Yes        |

| Output Compare 2                | _OUTPUT_COMPARE_2_VECTOR      | 12     | OFF012<17:1>   | IFS0<12> | IEC0<12> | IPC3<4:2>        | IPC3<1:0>    | No         |

| External Interrupt 2            | _EXTERNAL_2_VECTOR            | 13     | OFF013<17:1>   | IFS0<13> | IEC0<13> | IPC3<12:10>      | IPC3<9:8>    | No         |

| Timer3                          | _TIMER_3_VECTOR               | 14     | OFF014<17:1>   | IFS0<14> | IEC0<14> | IPC3<20:18>      | IPC3<17:16>  | No         |

| Input Capture 3 Error           | _INPUT_CAPTURE_3_ERROR_VECTOR | 15     | OFF015<17:1>   | IFS0<15> | IEC0<15> | IPC3<28:26>      | IPC3<25:24>  | Yes        |

| Input Capture 3                 | _INPUT_CAPTURE_3_VECTOR       | 16     | OFF016<17:1>   | IFS0<16> | IEC0<16> | IPC4<4:2>        | IPC4<1:0>    | Yes        |

| Output Compare 3                | _OUTPUT_COMPARE_3_VECTOR      | 17     | OFF017<17:1>   | IFS0<17> | IEC0<17> | IPC4<12:10>      | IPC4<9:8>    | No         |

| External Interrupt 3            | _EXTERNAL_3_VECTOR            | 18     | OFF018<17:1>   | IFS0<18> | IEC0<18> | IPC4<20:18>      | IPC4<17:16>  | No         |

| Timer4                          | _TIMER_4_VECTOR               | 19     | OFF019<17:1>   | IFS0<19> | IEC0<19> | IPC4<28:26>      | IPC4<25:24>  | No         |

| Input Capture 4 Error           | _INPUT_CAPTURE_4_ERROR_VECTOR | 20     | OFF020<17:1>   | IFS0<20> | IEC0<20> | IPC5<4:2>        | IPC5<1:0>    | Yes        |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MZ EC Family Features" for the list of available peripherals.

**2:** This interrupt source is not available on 64-pin devices.

3: This interrupt source is not available on 100-pin devices.

4: This interrupt source is not available on 124-pin devices.

# REGISTER 11-28: USBLPMR1: USB LINK POWER MANAGEMENT CONTROL REGISTER 1 (CONTINUED)

# bit 16 LPMXMT: LPM Transition to the L1 State bit

# When in Device mode:

- 1 = USB module will transition to the L1 state upon the receipt of the next LPM transaction. LPMEN must be set to `0b11. Both LPMXMT and LPMEN must be set in the same cycle.

- 0 = Maintain current state

When LPMXMT and LPMEN are set, the USB module can respond in the following ways:

- If no data is pending (all TX FIFOs are empty), the USB module will respond with an ACK. The bit will self clear and a software interrupt will be generated.

- If data is pending (data resides in at least one TX FIFO), the USB module will respond with a NYET. In this case, the bit will not self clear however a software interrupt will be generated.

# When in Host mode:

- 1 = USB module will transmit an LPM transaction. This bit is self clearing, and will be immediately cleared upon receipt of any Token or three time-outs have occurred.

- 0 = Maintain current state

# bit 15-12 ENDPOINT<3:0>: LPM Token Packet Endpoint bits

This is the endpoint in the token packet of the LPM transaction.

# bit 11-9 Unimplemented: Read as '0'

bit 8 **RMTWAK:** Remote Wake-up Enable bit

This bit is applied on a temporary basis only and is only applied to the current suspend state.

- 1 = Remote wake-up is enabled

- 0 = Remote wake-up is disabled

# bit 7-4 HIRD<3:0>: Host Initiated Resume Duration bits

The minimum time the host will drive resume on the bus. The value in this register corresponds to an actual resume time of:

Resume Time = 50  $\mu$ s + HIRD \* 75  $\mu$ s. The resulting range is 50  $\mu$ s to 1200  $\mu$ s.

# bit 3-0 LNKSTATE<3:0>: Link State bits

This value is provided by the host to the peripheral to indicate what state the peripheral must transition to after the receipt and acceptance of a LPM transaction. The only valid value for this register is '1' for Sleep State (L1). All other values are reserved.

| Peripheral Pin               | [pin name]R SFR      | [pin name]R bits          | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection          |

|------------------------------|----------------------|---------------------------|-------------------------------------------------------------|

| INT3                         | INT3R                | INT3R<3:0>                | 0000 = RPD2                                                 |

| T2CK                         | T2CKR                | T2CKR<3:0>                | 0001 = RPG8                                                 |

| T6CK                         | T6CKR                | T6CKR<3:0>                | 0010 = RPF4                                                 |

| IC3                          | IC3R                 | IC3R<3:0>                 | 0011 = RPD10                                                |

| IC7                          | IC7R                 | IC7R<3:0>                 |                                                             |

| U1RX                         | U1RXR                | U1RXR<3:0>                | 0101 = RPB9<br>0110 = RPB10                                 |

| U2CTS                        | U2CTSR               | U2CTSR<3:0>               | 0111 = RPC14                                                |

| U5RX                         | U5RXR                | U5RXR<3:0>                | 1000 = RPB5                                                 |

| U6CTS                        | U6CTSR               | U6CTSR<3:0>               | 1001 = Reserved                                             |

| SDI1                         | SDI1R                | SDI1R<3:0>                | $1010 = \text{RPC1}^{(1)}$                                  |

| SDI3                         | SDI3R                | SDI3R<3:0>                | $-1011 = \text{RPD14}^{(1)}$                                |

| SDI5 <sup>(1)</sup>          | SDI5R <sup>(1)</sup> | SDI5R<3:0> <sup>(1)</sup> | 1100 = RPG1 <sup>(1)</sup><br>1101 = RPA14 <sup>(1)</sup>   |

| <u>SS6</u> (1)               | SS6R <sup>(1)</sup>  | SS6R<3:0> <sup>(1)</sup>  | $11101 = RPD6^{(2)}$                                        |

| REFCLKI1                     | REFCLKI1R            | REFCLKI1R<3:0>            | 1111 = Reserved                                             |

| INT4                         | INT4R                | INT4R<3:0>                | 0000 = RPD3                                                 |

| T5CK                         | T5CKR                | T5CKR<3:0>                | 0001 = RPG7                                                 |

| T7CK                         | T7CKR                | T7CKR<3:0>                | 0010 = RPF5<br>0011 = RPD11                                 |

| IC4                          | IC4R                 | IC4R<3:0>                 | 0100 = RPF0                                                 |

| IC8                          | IC8R                 | IC8R<3:0>                 |                                                             |

| U3RX                         | U3RXR                | U3RXR<3:0>                | 0111 = RPC13                                                |

|                              | U4CTSR               | U4CTSR<3:0>               | 1000 = RPB3<br>1001 = Reserved                              |

| SDI2                         | SDI2R                | SDI2R<3:0>                | 1010 = RPC4 <sup>(1)</sup>                                  |

| SDI4                         | SDI4R                | SDI4R<3:0>                | $- 1011 = \text{RPD15}^{(1)}$<br>1100 = RPG0 <sup>(1)</sup> |

| C1RX <sup>(3)</sup>          | C1RXR <sup>(3)</sup> | C1RXR<3:0> <sup>(3)</sup> | 1101 = RPA15 <sup>(1)</sup>                                 |

| REFCLKI4                     | REFCLKI4R            | REFCLKI4R<3:0>            |                                                             |

| INT2                         | INT2R                | INT2R<3:0>                | 0000 = RPD9                                                 |

| T3CK                         | T3CKR                | T3CKR<3:0>                | 0001 = RPG6                                                 |

| T8CK                         | TBCKR                | T8CKR<3:0>                | 0010 = RPB8                                                 |

| IC2                          | IC2R                 | IC2R<3:0>                 | 0011 = RPB15                                                |

| IC5                          | IC5R                 | IC5R<3:0>                 |                                                             |

| IC9                          | IC9R                 | IC9R<3:0>                 | 0101 = RPB0                                                 |

| UICTS                        | U1CTSR               | U1CTSR<3:0>               | 0110 = RPE3<br>0111 = RPB7                                  |

| U2RX                         | U2RXR                | U2RXR<3:0>                | 1000 = Reserved                                             |

| USCTS                        | USCTSR               |                           | 1001 = RPF12 <sup>(1)</sup>                                 |

| <u>SS1</u>                   |                      | U5CTSR<3:0>               | 1010 = RPD12 <sup>(1)</sup>                                 |

| <u> </u>                     | SS1R                 | SS1R<3:0>                 |                                                             |

|                              | SS3R                 | SS3R<3:0>                 | 1100 = RPC3 <sup>(1)</sup>                                  |

| <u>SS4</u><br><u>SS5</u> (1) | SS4R                 | SS4R<3:0>                 | 1101 = RPE9 <sup>(1)</sup>                                  |

| 222.1                        | SS5R <sup>(1)</sup>  | SS5R<3:0> <sup>(1)</sup>  | 1110 = Reserved                                             |

# TABLE 12-1: INPUT PIN SELECTION

**Note 1:** This selection is not available on 64-pin devices.

**2:** This selection is not available on 64-pin or 100-pin devices.

3: This selection is not available on devices without a CAN module.

# TABLE 12-6: PORTC REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |           |           |           |           |       |       |      | Bits |      |      |      |      |      |      |      |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|------|------|------|------|------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All<br>Resets |

| 0210                        | TRISC                           | 31:16     |           |           | _         | —         | _     | _     |      | -    | —    |      | -    | -    | —    | —    | —    | —    | 0000          |

| 0210                        | INIOC                           | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | _     | _     | —    | _    |      | —    | _    | _    | —    | —    |      | —    | F000          |

| 0220                        | PORTC                           | 31:16     | —         | —         | —         | —         |       | —     | _    | _    |      | —    | _    |      | —    | —    |      | —    | 0000          |

| 0220                        |                                 | 15:0      | RC15      | RC14      | RC13      | RC12      | _     | _     | _    | _    | _    | —    | _    | _    | —    | —    | —    | —    | xxxx          |

| 0230                        | LATC                            | 31:16     |           | —         | —         | —         | —     | —     | —    | _    | —    | —    | -    | —    | —    | —    | —    | —    | 0000          |

| 0200                        | LATO                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | —     | _     | _    | —    | —    | —    | —    | _    | —    | —    | —    | —    | xxxx          |

| 0240                        | ODCC                            | 31:16     |           | —         | _         | —         | —     | _     | _    | -    | —    | —    | -    | —    | —    | —    | —    | —    | 0000          |

| 0210                        | ODCC                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | —     | _     | _    | —    | —    | —    | —    | _    | —    | —    | —    | —    | xxxx          |

| 0250                        | CNPUC                           | 31:16     | —         | —         | —         | —         | —     | _     | _    | —    | —    | —    | —    | _    | —    | —    | —    | —    | 0000          |

| 0200                        | 011 00                          | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | —     | _     | _    | —    | —    | —    | —    | _    | —    | —    | —    | —    | 0000          |

| 0260                        | CNPDC                           | 31:16     | —         | —         | —         | —         | —     | _     | _    | —    | —    | —    | —    | _    | —    | —    | —    | —    | 0000          |

| 0200                        |                                 | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | _     | _     | _    |      | —    | —    |      |      | —    | —    | —    | —    | 0000          |

| 0270                        | CNCONC                          | 31:16     |           | —         | _         | —         | _     | _     | _    |      | —    | —    |      |      | —    | —    | —    | —    | 0000          |

| 0210                        | onconc                          | 15:0      | ON        | —         | SIDL      | —         | —     | _     | —    | _    | —    | —    | _    | _    | —    | —    | —    | —    | 0000          |

| 0280                        | CNENC                           | 31:16     |           | _         |           | _         | _     | _     | _    | _    | —    | —    | _    |      | —    | —    | —    | —    | 0000          |

| 0200                        | ONENO                           | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | —     | —     | —    | -    | —    | —    | -    | _    | —    | —    | —    | —    | 0000          |

| 0200                        | CNSTATC                         | 31:16     | _         | _         | _         | —         | —     |       | —    |      | _    | _    |      |      | —    | —    | _    | _    | 0000          |

| 0290                        | CHOIRIC                         | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | —     | —     | —    | _    | -    | _    | _    | _    | _    | _    | _    |      | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

#### **TABLE 18-2: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 9 REGISTER MAP (CONTINUED)** Virtual Address (BF84\_#) Bits Bit Range Register Name<sup>(1)</sup> 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 31:16 \_ — \_ — \_ — — \_ — — \_ \_ \_ 4A00 OC6CON 15:0 ON \_ SIDL \_ \_ \_ \_ \_ \_ \_ OC32 OCFLT OCTSEL OCM<2:0> 31:16 OC6R OC6R<31:0> 4A10 15:0 31:16 4A20 OC6RS OC6RS<31:0> 15:0

| 4000 | OC7CON | 31:16                    | _            | — | —    | — | — | - | _ | _     | —       | _    | —    | —     | —      |      | —        | _ | 0000 |

|------|--------|--------------------------|--------------|---|------|---|---|---|---|-------|---------|------|------|-------|--------|------|----------|---|------|

| 4000 |        | 15:0                     | ON           | — | SIDL | — | — | - | _ | _     | —       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |   | 0000 |

| 4C10 | OC7R   | 31:16                    |              |   |      |   |   |   |   | OC7R- | ~21.0>  |      |      |       |        |      |          |   | xxxx |

| 4010 | 0078   | 15:0                     |              |   |      |   |   |   |   | 00714 | <31.0>  |      |      |       |        |      |          |   | xxxx |

| 4020 | OC7RS  | 31:16                    |              |   |      |   |   |   |   | OC7RS | -21.0   |      |      |       |        |      |          |   | xxxx |

| 4020 | 00783  | 15:0                     |              |   |      |   |   |   |   |       |         |      |      |       | xxxx   |      |          |   |      |

| 4500 | OC8CON | 31:16                    | _            | _ | —    | _ | _ | - | — | —     | _       | _    | —    | _     | _      | -    | —        | _ | 0000 |

| 4E00 |        | 15:0                     | ON           | — | SIDL | _ | _ |   | _ | —     | _       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |   | 0000 |

| 4E10 | OC8R   | 31:16                    | 16OC8R<31:0> |   |      |   |   |   |   |       |         |      |      |       |        |      | xxxx     |   |      |

| 4110 | OCOR   | 15:0                     | 000R<31.0>   |   |      |   |   |   |   |       |         |      |      |       |        | xxxx |          |   |      |

| 4520 | OC8RS  | 31:16                    |              |   |      |   |   |   |   | OC8RS | -31.0~  |      |      |       |        |      |          |   | xxxx |

| 4620 | 000100 | 15:0                     |              |   |      |   |   |   |   | OCONC | 0<01.02 |      |      |       |        |      |          |   | xxxx |

| 5000 | OC9CON | 31:16                    | _            | _ | _    | _ | — | - | — | —     | _       | _    | —    | _     | _      | -    | —        | - | 0000 |

| 3000 | OCSCON | 15:0                     | ON           | _ | SIDL |   | _ |   | _ | _     |         | -    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |   | 0000 |

| 5010 | OC9R   | 31:16         OC9R<31:0> |              |   |      |   |   |   |   |       |         |      | xxxx |       |        |      |          |   |      |

| 3010 | OCar   |                          |              |   |      |   |   |   |   |       |         | xxxx |      |       |        |      |          |   |      |

| 5020 | OC9RS  | 31:16                    |              |   |      |   |   |   |   | OC9RS | S<31:0> |      |      |       |        |      |          |   | xxxx |

|      |        | 15:0                     |              |   |      |   |   |   |   |       |         |      |      |       |        |      |          |   |      |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

All Resets

0000

0000

xxxx

xxxx

xxxx

xxxx

16/0

\_

# REGISTER 20-1: SQI1XCON1: SQI XIP CONTROL REGISTER 1 (CONTINUED)

# bit 5-4 TYPEMODE<1:0>: SQI Type Mode Enable bits

- The boot controller will send the mode in Single Lane, Dual Lane, or Quad Lane.

- 11 = Reserved

- 10 = Quad Lane mode is enabled

- 01 = Dual Lane mode is enabled

- 00 = Single Lane mode is enabled

- bit 3-2 **TYPEADDR<1:0>:** SQI Type Address Enable bits

The boot controller will send the address in Single Lane, Dual Lane, or Quad Lane.

- 11 = Reserved

- 10 = Quad Lane mode address is enabled

- 01 = Dual Lane mode address is enabled

- 00 = Single Lane mode address is enabled

# bit 1-0 TYPECMD<1:0>: SQI Type Command Enable bits

The boot controller will send the command in Single Lane, Dual Lane, or Quad Lane.

- 11 = Reserved

- 10 =Quad Lane mode command is enabled

- 01 = Dual Lane mode command is enabled

- 00 = Single Lane mode command is enabled

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 45-0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | PTEN<             | :15:14>           |                   |                   | PTEN-             | <13:8>            |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | PTEN              | <7:0>             |                   |                  |                  |

# REGISTER 23-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

# Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

# bit 31-15 Unimplemented: Read as '0'

- bit 15-14 PTEN<15:14>: PMCS1 Strobe Enable bits

- 1 = PMA15 and PMA14 function as either PMA<15:14> or PMCS1 and PMCS2<sup>(1)</sup>

- 0 = PMA15 and PMA14 function as port I/O

- bit 13-2 **PTEN<13:2>:** PMP Address Port Enable bits

- 1 = PMA<13:2> function as PMP address lines

- 0 = PMA<13:2> function as port I/O

- bit 1-0 **PTEN<1:0>:** PMALH/PMALL Strobe Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- **Note 1:** The use of these pins as PMA15 and PMA14 or CS1 and CS2 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 | -                 | _                | —                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 |                   |                   | -                 |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   | —                 |                   | _                 | AREIF             | PKTIF             | CBDIF            | PENDIF           |

# REGISTER 26-6: CEINTSRC: CRYPTO ENGINE INTERRUPT SOURCE REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

# bit 31-4 Unimplemented: Read as '0'

- bit 3 AREIF: Access Response Error Interrupt bit

- 1 = Error occurred trying to access memory outside the Crypto Engine

- 0 = No error has occurred

- bit 2 **PKTIF:** DMA Packet Completion Interrupt Status bit

- 1 = DMA packet was completed

- 0 = DMA packet was not completed

- bit 1 CBDIF: BD Transmit Status bit

- 1 = Last BD transmit was processed

- 0 = Last BD transmit has not been processed

- bit 0 **PENDIF:** Crypto Engine Interrupt Pending Status bit

- 1 = Crypto Engine interrupt is pending (this value is the result of an OR of all interrupts in the Crypto Engine)

- 0 = Crypto Engine interrupt is not pending

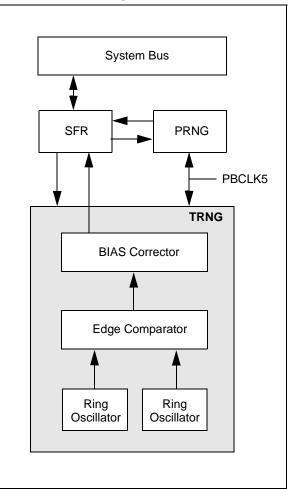

# 27.0 RANDOM NUMBER GENERATOR (RNG)

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 49. "Crypto Engine (CE) and Random Number Generator (RNG)" (DS60001246), which is available from the Documentation > Reference Manual section of the PIC32 Microchip web site (www.microchip.com/pic32).

The Random Number Generator (RNG) core implements a thermal noise-based, True Random Number Generator (TRNG) and a cryptographically secure Pseudo-Random Number Generator (PRNG).

The TRNG uses multiple ring oscillators and the inherent thermal noise of integrated circuits to generate true random numbers that can initialize the PRNG.

The PRNG is a flexible LSFR, which is capable of manifesting a maximal length LFSR of up to 64-bits.

The following are some of the key features of the Random Number Generator:

- TRNG:

- Up to 25 Mbps of random bits

- Multi-Ring Oscillator based design

- Built-in Bias Corrector

- PRNG:

- LSFR-based

- Up to 64-bit polynomial length

- Programmable polynomial

- TRNG can be seed value

# TABLE 27-1: RANDOM NUMBER GENERATOR BLOCK DIAGRAM

|              | (')               | k' = 1 OR 2)      |                   |                   |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 04-04        | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 31:24        | POLY<31:24>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22:16        | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 23:16        | POLY<23:16>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | POLY<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | POLY<             | :7:0>             |                   |                  |                  |  |  |  |

# REGISTER 27-3: RNGPOLYx: RANDOM NUMBER GENERATOR POLYNOMIAL REGISTER 'x'

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 POLY<31:0>: PRNG LFSR Polynomial MSb/LSb bits (RNGPOLY1 = LSb, RNGPOLY2 = MSb)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 31:24        | RNG<31:24>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22.46        | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 23:16        | RNG<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 15:8         | RNG<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 7:0          |                   | RNG<7:0>          |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 RNG<31:0>: Current PRNG MSb/LSb Value bits (RNGNUMGEN1 = LSb, RNGNUMGEN2 = MSb)

| Bit Range | Bit Bit Bit 31/23/15/7 30/22/14/ |         | Bit Bit<br>29/21/13/5 28/20/12/4 |         | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|----------------------------------|---------|----------------------------------|---------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | U-0                              | U-0     | U-0                              | U-0     | U-0               | U-0               | U-0              | U-0              |  |

| 31.24     | _                                | -       | _                                |         |                   | _                 |                  | _                |  |

| 23:16     | U-0                              | U-0     | U-0                              | U-0     | U-0               | U-0               | U-0              | U-0              |  |

| 23.10     | _                                | -       | _                                |         |                   | _                 |                  | _                |  |

| 15:8      | U-0                              | U-0     | U-0                              | R/W-0   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 10.0      | _                                | -       | _                                | AGIEN44 | AGIEN43           | AGIEN42           | AGIEN41          | AGIEN40          |  |

| 7:0       | R/W-0                            | R/W-0   | R/W-0                            | R/W-0   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0       | AGIEN39                          | AGIEN38 | AGIEN37                          | AGIEN36 | AGIEN35           | AGIEN34           | AGIEN33          | AGIEN32          |  |

# REGISTER 28-6: AD1GIRQEN2: ADC1 GLOBAL INTERRUPT ENABLE REGISTER 2

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

# bit 31-13 Unimplemented: Read as '0'

bit 12-0 **AGIENx:** Global ADC Interrupt Enable bits ('x' = 32-44)

1 = A data ready event (transition from 0 to 1 of the ARDYx bit) will generate a Global ADC interrupt

0 = No global interrupt is generated on a data ready event

**Note 1:** The enable bits do not affect assertion of the individual interrupt output. Interrupts generated for individual ARDYx events are enabled in the IECx register.

2: AGIENx = ANx, where 'x' = 32-42, AGIEN43 = IVREF, and AGIEN44 = IVTEMP.

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14 |       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|--------------------------------|-------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0                          | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        | FLTEN15                        | MSEL1 | 5<1:0>            |                   | F                 | SEL15<4:0>        | EL15<4:0>        |                  |  |  |

| 00.40        | R/W-0                          | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | FLTEN14                        | MSEL1 | 4<1:0>            | FSEL14<4:0>       |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0                          | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | FLTEN13                        | MSEL1 | 3<1:0>            | FSEL13<4:0>       |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0                          | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | FLTEN12 MSEL12<1:0>            |       |                   | FSEL12<4:0>       |                   |                   |                  |                  |  |  |

# REGISTER 29-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN15: Filter 15 Enable bit                                                                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                                                          |

| bit 30-29 | MSEL15<1:0>: Filter 15 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected                                                                                          |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                       |

| bit 28-24 | FSEL15<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN14: Filter 14 Enable bit                                                                                            |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                   |

| bit 22-21 | MSEL14<1:0>: Filter 14 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected                                                                                          |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                       |

| bit 20-16 | FSEL14<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                               |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                               |

|           |                                                                                                                          |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# 34.2 Registers

# TABLE 34-1: DEVCFG: DEVICE CONFIGURATION WORD SUMMARY

| ess<br>)                    |                  | c)            |        |          |          |               |           |          |        | Bit     | S        |         |            |           |        |                   |            |      | s          |

|-----------------------------|------------------|---------------|--------|----------|----------|---------------|-----------|----------|--------|---------|----------|---------|------------|-----------|--------|-------------------|------------|------|------------|

| Virtual Address<br>(BFC0_#) | Register<br>Name | Bit Range     | 31/15  | 30/14    | 29/13    | 28/12         | 27/11     | 26/10    | 25/9   | 24/8    | 23/7     | 22/6    | 21/5       | 20/4      | 19/3   | 18/2              | 17/1       | 16/0 | All Resets |

| FFC0                        | DEVCFG3          | 31:16         |        | FUSBIDIO | IOL1WAY  | PMDL1WAY      | PGL1WAY   | _        | FETHIO | FMIIEN  | _        | _       | _          |           | _      | —                 |            | _    | xxxx       |

| 1100                        | DE VOI 00        | 15:0          |        |          |          |               |           |          |        | USERID  | <15:0>   |         |            |           |        |                   |            |      | xxxx       |

| FFC4                        | DEVCFG2          | 31:16         | —      | UPLLFSEL | —        | —             | —         | —        | —      | —       | —        | —       | —          | —         | —      |                   | PLLODIV<2: | -    | xxxx       |

| 1104                        | DE VOI 02        | 15:0          | —      |          |          |               | LMULT<6:0 | >        |        |         | FPLLICLK |         | PLLRNG<2:0 | >         | —      |                   | PLLIDIV<2: | )>   | xxxx       |

| FFC8                        | DEVCFG1          |               | FDMTEN |          |          | DMTCNT<4:0:   |           |          | FWDTWI |         | FWDTEN   | WINDIS  | WDTSPGM    |           |        | WDTPS<4:0         |            |      | xxxx       |

| 11 00                       | DEVOIOT          | 15:0          | FCKS   | SM<1:0>  | —        | —             | _         | OSCIOFNC | POSCM  | OD<1:0> | IESO     | FSOSCEN | DM         | TINTV<2:0 | >      | F                 | NOSC<2:0   | >    | xxxx       |

| FFCC                        | DEVCFG0          | 31:16         | _      | EJTAGBEN | _        | —             | _         |          | _      | —       | —        | _       | _          | _         | —      | —                 | _          | —    | xxxx       |

|                             | 5210.00          | 15:0          | _      | C        | BGPER<2: | )>            | _         | FSLEEP   | FECCCO | ON<1:0> | -        | BOOTISA | TRCEN      | ICESE     | L<1:0> | JTAGEN DEBUG<1:0> |            | xxxx |            |

| FFD0                        | DEVCP3           | 31:16         | —      | _        | —        | —             | _         | —        | —      |         |          | _       | —          | _         | _      | —                 | _          | —    | xxxx       |

|                             |                  | 15:0          | —      | _        | —        | —             | _         | —        | —      |         |          | _       | —          | _         | _      | —                 | _          | —    | xxxx       |

| FFD4                        | DEVCP2           | 31:16         | —      | _        | —        | —             | _         | —        | —      |         |          | _       | —          | _         | _      | —                 | _          | —    | xxxx       |

|                             |                  | 15:0          | _      | _        | _        | -             | _         | -        | _      | _       |          | _       | _          | _         | —      | -                 | _          | _    | xxxx       |

| FFD8                        | DEVCP1           | 31:16         | _      | _        | _        | -             | _         | -        | _      | _       |          | _       | _          | _         | —      | -                 | _          | _    | xxxx       |

|                             |                  | 15:0          | _      | _        | _        | -             | _         | -        | _      | _       |          | _       | _          | _         | —      | -                 | _          | _    | xxxx       |

| FFDC                        | DEVCP0           | 31:16         | _      | _        | _        | CP            |           | _        | _      |         |          |         | _          | _         |        | _                 |            |      | XXXX       |

|                             |                  | 15:0          |        |          |          | _             |           |          | _      |         |          |         | _          |           | _      | _                 |            |      | xxxx       |

| FFE0                        | DEVSIGN3         | 31:16         | _      | _        |          | _             |           | _        | _      |         |          |         | _          | _         | _      | _                 |            |      | xxxx       |

|                             |                  | 15:0          | —      | _        | _        | _             | _         | _        | _      | _       | _        |         | _          | _         | _      | _                 | _          | —    | XXXX       |

| FFE4                        | DEVSIGN2         | 31:16         | _      | —        | _        | _             | _         | _        | —      | _       |          |         | _          | _         | _      | _                 |            |      | XXXX       |

| $\vdash$                    |                  | 15:0<br>31:16 |        |          | —        | _             | _         |          |        | —       |          |         | _          |           | —      |                   |            | _    | XXXX       |

| FFE8                        | DEVSIGN1         | 31:16<br>15:0 |        |          | —        | _             |           |          |        | —       |          |         |            |           |        |                   |            |      | XXXX       |

|                             |                  |               | 0      |          | _        | _             |           |          |        | _       |          |         |            |           | _      | -                 |            | _    | XXXX       |

| FFEC                        | DEVSIGN0         | 31:16<br>15:0 | -      |          | _        | _             |           |          |        | _       |          |         |            |           |        | -                 |            | _    | xxxx       |

| Legen                       |                  | 1             |        |          |          | las '1' Reset | . —       | —        |        | —       | —        | _       |            | _         | _      | —                 | —          | _    | XXXX       |

Legend: x = unknown value on Reset; - = Reserved, read as '1'. Reset values are shown in hexadecimal

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0       |  |

|--------------|----------------------------------|-----|-----------------------|------------------------|-----------------------|-------------------|-----------------------|------------------------|--|

| 04-04        | U-0                              | U-0 | U-0                   | U-0                    | U-0                   | U-0               | R/W-0                 | R/W-0                  |  |

| 31:24        | —                                | _   | —                     | —                      | _                     | —                 | DMAPRI <sup>(1)</sup> | CPUPRI <sup>(1)</sup>  |  |

| 00.40        | U-0                              | U-0 | U-0                   | U-0                    | U-0                   | U-0               | R/W-0                 | R/W-0                  |  |

| 23:16        | —                                | _   |                       |                        |                       |                   | ICACLK <sup>(1)</sup> | OCACLK <sup>(1)</sup>  |  |

| 45.0         | U-0                              | U-0 | R/W-0                 | R/W-0                  | R/W-0                 | U-0               | U-0                   | R/W-0                  |  |

| 15:8         | —                                | _   | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> | PGLOCK <sup>(1)</sup> | —                 | _                     | USBSSEN <sup>(1)</sup> |  |

| 7.0          | U-0                              | U-0 | R/W-1                 | R/W-1                  | R/W-1                 | R/W-0             | U-0                   | R/W-1                  |  |

| 7:0          |                                  |     | ECCC                  | ON<1:0>                | JTAGEN                | TROEN             | _                     | TDOEN                  |  |

# REGISTER 34-7: CFGCON: CONFIGURATION CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

# bit 31-26 Unimplemented: Read as '0'

| bit 31-26 | Unimplemented: Read as '0'                                                                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 25    | DMAPRI: DMA Read and DMA Write Arbitration Priority to SRAM bit <sup>(1)</sup>                                                                                                                   |

|           | 1 = DMA gets High Priority access to SRAM                                                                                                                                                        |

|           | 0 = DMA uses Least Recently Serviced Arbitration (same as other initiators)                                                                                                                      |

| bit 24    | <b>CPUPRI:</b> CPU Arbitration Priority to SRAM When Servicing an Interrupt bit <sup>(1)</sup>                                                                                                   |

|           | 1 = CPU gets High Priority access to SRAM                                                                                                                                                        |

| 1 1 00 40 | 0 = CPU uses Least Recently Serviced Arbitration (same as other initiators)                                                                                                                      |

|           | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 17    | ICACLK: Input Capture Alternate Clock Selection bit <sup>(1)</sup>                                                                                                                               |

|           | <ul> <li>1 = Input Capture modules use an alternative Timer pair as their timebase clock</li> <li>0 = All Input Capture modules use Timer2/3 as their timebase clock</li> </ul>                  |

| bit 16    | OCACLK: Output Compare Alternate Clock Selection bit <sup>(1)</sup>                                                                                                                              |

|           | <ul> <li>1 = Output Compare modules use an alternative Timer pair as their timebase clock</li> <li>0 = All Output Compare modules use Timer2/3 as their timebase clock</li> </ul>                |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 13    | IOLOCK: Peripheral Pin Select Lock bit <sup>(1)</sup>                                                                                                                                            |

|           | <ul> <li>1 = Peripheral Pin Select is locked. Writes to PPS registers are not allowed</li> <li>0 = Peripheral Pin Select is not locked. Writes to PPS registers are allowed</li> </ul>           |

| bit 12    | PMDLOCK: Peripheral Module Disable bit <sup>(1)</sup>                                                                                                                                            |

|           | <ul> <li>1 = Peripheral module is locked. Writes to PMD registers are not allowed</li> <li>0 = Peripheral module is not locked. Writes to PMD registers are allowed</li> </ul>                   |

| bit 11    | PGLOCK: Permission Group Lock bit <sup>(1)</sup>                                                                                                                                                 |

|           | <ul> <li>1 = Permission Group registers are locked. Writes to PG registers are not allowed</li> <li>0 = Permission Group registers are not locked. Writes to PG registers are allowed</li> </ul> |

| bit 10-9  | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 8     | USBSSEN: USB Suspend Sleep Enable bit <sup>(1)</sup>                                                                                                                                             |

|           | Enables features for USB PHY clock shutdown in Sleep mode.                                                                                                                                       |

|           | 1 = USB PHY clock is shut down when Sleep mode is active                                                                                                                                         |

| 1 1 7 0   | 0 = USB PHY clock continues to run when Sleep is active                                                                                                                                          |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                                                                       |

| Note 1:   | To change this bit, the unlock sequence must be performed. Refer to <b>Section 42. "Oscillators with Enhanced PLL"</b> (DS60001250) in the <i>"PIC32 Family Reference Manual"</i> for details.   |

# REGISTER 34-8: CFGEBIA: EXTERNAL BUS INTERFACE ADDRESS PIN CONFIGURATION REGISTER

|              | =                 |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | EBIPINEN          | _                 | _                 | _                 | —                 | —                 | -                | _                |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | EBIA23EN          | EBIA22EN          | EBIA21EN          | EBIA20EN          | EBIA19EN          | EBIA18EN          | EBIA17EN         | EBIA16EN         |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | EBIA15EN          | EBIA14EN          | EBIA13EN          | EBIA12EN          | EBIA11EN          | EBIA10EN          | EBIA9EN          | EBIA8EN          |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | EBIA7EN           | EBIA6EN           | EBIA5EN           | EBIA4EN           | EBIA3EN           | EBIA2EN           | EBIA1EN          | EBIA0EN          |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

# bit 31 EBIPINEN: EBI Pin Enable bit

1 = EBI controls access of pins shared with PMP

0 = Pins shared with EBI are available for general use

- bit 30-24 Unimplemented: Read as '0'

- bit 23-0 EBIA23EN:EBIA0EN: EBI Address Pin Enable bits

- 1 = EBIAx pin is enabled for use by EBI

- 0 = EBIAx pin has is available for general use

Note: When EBIMD = 1, the bits in this register are ignored and the pins are available for general use.

# 36.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

# 36.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for highperformance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules