Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

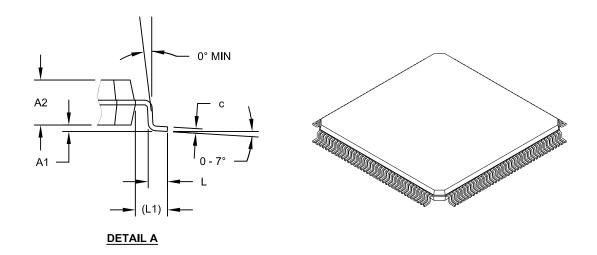

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048ech064t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Fr40       AP2DEVCFG3       310         Fr43       AP2DEVCFG3       310         Fr43       AP2DEVCFG3       310         Fr44       AP2DEVCFG3       310         Fr56       AP2DEVCFG3       310         Fr56       AP2DEVCFG3       310         Fr56       AP2DEVCF3       310         Fr56       AP2DEVCF3       310         Fr56       AP2DEVCF3       310         Fr56       AP2DEVSIGN1       310         Fr56       AP2DEVSIGN2       310         Fr56       AP2DEVSIGN3       310         Fr57       AP2DEVSIGN1       310         Fr57       AP2DEVSIGN1       310         Fr57       AP2DEVSIGN2       310         Fr57       AP2DEVSIGN3       310         Fr57       AP2DEVSIGN3       310         Fr58       AP2DEVSIGN3       310         Fr59       AP2DEVSIGN3       310         Fr59       AP2DEVSIGN3       310         Fr50       AP2DEVSIGN3       310         Fr50       AP2DEVSIGN3       310         Fr50       BP2DEVCFG3       310         Fr50       BP2DEVSIGN3       310 <tr< th=""><th>SSS</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th>В</th><th>ts</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SSS                         |                  |           |       |       |       |       |       |       |          | В          | ts           |                |       |      |      |      |      |      |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|----------|------------|--------------|----------------|-------|------|------|------|------|------|----|

| Fr40       AP2DEVCFG3       310         Fr43       AP2DEVCFG3       310         Fr43       AP2DEVCFG3       310         Fr44       AP2DEVCFG3       310         Fr56       AP2DEVCFG3       310         Fr56       AP2DEVCFG3       310         Fr56       AP2DEVCF3       310         Fr56       AP2DEVCF3       310         Fr56       AP2DEVCF3       310         Fr56       AP2DEVSIGN1       310         Fr56       AP2DEVSIGN2       310         Fr56       AP2DEVSIGN3       310         Fr57       AP2DEVSIGN1       310         Fr57       AP2DEVSIGN1       310         Fr57       AP2DEVSIGN2       310         Fr57       AP2DEVSIGN3       310         Fr57       AP2DEVSIGN3       310         Fr58       AP2DEVSIGN3       310         Fr59       AP2DEVSIGN3       310         Fr59       AP2DEVSIGN3       310         Fr50       AP2DEVSIGN3       310         Fr50       AP2DEVSIGN3       310         Fr50       BP2DEVCFG3       310         Fr50       BP2DEVSIGN3       310 <tr< th=""><th>Virtual Address<br/>(BFC6_#)</th><th>Register<br/>Name</th><th>Bit Range</th><th>31/15</th><th>30/14</th><th>29/13</th><th>28/12</th><th>27/11</th><th>26/10</th><th>25/9</th><th>24/8</th><th>23/7</th><th>22/6</th><th>21/5</th><th>20/4</th><th>19/3</th><th>18/2</th><th>17/1</th><th>16/0</th><th></th></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Virtual Address<br>(BFC6_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8       | 23/7         | 22/6           | 21/5  | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 |    |

| Free AP20EVCPG 31:0           Note: See Table 34-2 for the bit descriptions.           Free AP20EVCPB 31:0           Free AP20EVCPD 31:0           Note: See Table 34-2 for the bit descriptions.           Free AP20EVCPB 31:0           Free AP20EVCVPD 31:0           Free AP20EVSIGND 31:0           Free B20EV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FF40                        | ABF2DEVCFG3      | 31:0      |       | 1     | 1     |       |       | I     |          |            |              | I              |       |      |      |      |      | 1    | xx |

| FRG AP272EVCF60 310           FRG AP272EVCF8 310           FRG AP272EVCF8 310           FRG AP272EVCF8 310           FRG AP272EVCF9 310           FRG AP272EVCF9 310           FRG AP272EVC780310           FRG AP272EVC780310           FRG AP272EVC780310           FRG AP272EVC780310           FRG AP272EVC780310           FRG AP272EVC780310           TREC AP272EVC78040           10         -         -           FRG AP272EVC78040         310           FRG AP272EVC80         310           FRG AP272EVC800         310           FRG AP272EVC800         310           FRG AP272EVC800         310           FRG AP272EVC80         310           FRG AP272EVC80         310           FRG AP272EVC80         310           FRG AP272EVC760         310           FRG AP272EVC760         310           FRG AP272EVC760         310                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FF44                        | ABF2DEVCFG2      | 31:0      |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FF48                        | ABF2DEVCFG1      | 31:0      |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| See Table 34-2 for the bit descriptions.           Note: See Table 34-2 for the bit descriptions.           FFEG         APE7DEVCPE         310           FFEG         APE7DEVSIGN3         3116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FF4C                        | ABF2DEVCFG0      | 31:0      |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| Note: See Table 34-2 for the bit descriptions.           Note: See Table 34-2 for the bit descriptions.           Note: See Table 34-2 for the bit descriptions.           FF66         ABF2DEVSIGN1         31:0           FF66         ABF2DEVSIGN3         31:0           FF76         ABF2DEVSIGN3         31:0           FF76         ABF2DEVSIGN3         31:0           FF76         ABF2DEVSIGN3         31:0           FF76         ABF2DEVSIGN4         31:0           FF76         ABF2DEVSIGN4         31:0           FF76         ABF2DEVSIGN4         31:0           THEO         CSEQ         31:16         —         —         —           ABF2DEVSIGN4         31:0         —         CSEQ         SSEQ         31:0           FF76         ABF2DEVSIGN2         31:0           TSEQ         SSEQ         SSEQ         SSEQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FF50                        | ABF2DEVCP3       | 31:0      |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| H188 Add/DEVCP1       310         FFEO       AB72DEVSIGN2       310         FFEO       AB72EVCFG       310         FFEO       AB72EVCFG       310         FFEO       AB72EVCFG       310         FFEO       B72DEVCFG       310 <t< td=""><td>FF54</td><td>ABF2DEVCP2</td><td>31:0</td><td></td><td></td><td></td><td></td><td></td><td></td><td>Notes Se</td><td>o Toblo 24</td><td>2 for the h</td><td>it doporinti</td><td></td><td></td><td></td><td></td><td></td><td></td><td>x</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FF54                        | ABF2DEVCP2       | 31:0      |       |       |       |       |       |       | Notes Se | o Toblo 24 | 2 for the h  | it doporinti   |       |      |      |      |      |      | x  |

| FF60       AB72DEVSIGN3       31.0         FF64       AB72DEVSIGN4       31.0         FF64       AB72DEVSIGN5       31.0         FF76       AB72DEVSIGN5       31.0         FF77       AB72DEVSIGN5       31.0         FF77       AB72DEVSIGN5       31.0         FF77       AB72EC       31.16       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | FF58                        | ABF2DEVCP1       | 31:0      |       |       |       |       |       |       | Note. Se | e Table 34 |              | it description | JII5. |      |      |      |      |      | x  |

| FF64       AB720EVSIGN0       310         FF76       AB72SEQ3       31:6       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FF5C                        | ABF2DEVCP0       | 31:0      |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| FF66         AB720E VSIGN1 31:0           FF76         AB720E VSIGN0 31:0           FF76         B720E VCF63 31:0           TECE B720E VCF63 31:0           FF76         B720E VCF63 31:0           FF70         B720E VCF63 31:0           FF70         B720E VCF63 31:0           FF70         B720E VCF63 31:0           FF70         B720E VS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FF60                        | ABF2DEVSIGN3     | 31:0      |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| FFEG       ABF2DEVSIGN0       31:0         FF70       ABF2DEQ3       31:16       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FF64                        | ABF2DEVSIGN2     | 31:0      |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | х  |

| ABF2SEQ3       31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FF68                        | ABF2DEVSIGN1     | 31:0      |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | х  |

| PF/0       AB22EQ3       16.0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FF6C                        | ABF2DEVSIGN0     | 31:0      |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | х  |

| Image: Second  | EE70                        |                  | 31:16     | —     | -     | _     |       |       | _     | _        | -          | -            | _              |       | -    | -    | -    | -    | -    | х  |

| FF74       ABF2SEQ2       15.0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FF70                        | ADF23EQ3         | 15:0      | _     | —     | —     |       |       | _     | —        | -          | _            | —              | _     |      |      | _    | —    | —    | x  |

| Image: state in the s |                             |                  | 31:16     | _     | _     | _     |       |       | _     |          |            | _            |                |       |      |      |      | _    | _    | x  |

| HF78       ABPSED1       150       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <t< td=""><td>FF74</td><td>ABF2SEQ2</td><td>15:0</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>x</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | FF74                        | ABF2SEQ2         | 15:0      | _     | _     | _     | _     | _     | _     | _        | _          | _            | _              | _     | _    | _    | _    | _    | _    | x  |

| HF78       ABPSED1       150       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <t< td=""><td></td><td></td><td>31:16</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td></td><td></td><td>_</td><td></td><td>_</td><td>_</td><td></td><td></td><td>_</td><td>_</td><td>_</td><td>x</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             |                  | 31:16     | _     | _     | _     | _     | _     |       |          | _          |              | _              | _     |      |      | _    | _    | _    | x  |

| Strice       31:16       CSEQ<15:0>         TFC0       BF2DEVCFG3       31:0         FFC4       BF2DEVCFG1       31:0         FFC6       BF2DEVCFG1       31:0         FFC6       BF2DEVCFG1       31:0         FFC6       BF2DEVCFG1       31:0         FFC8       BF2DEVCF3       31:0         FFD0       BF2DEVCF3       31:0         FFD0       BF2DEVCP3       31:0         FFD0       BF2DEVCP4       31:0         FFD0       BF2DEVCP3       31:0         FFE0       BF2DEVCP4       31:0         FFE0       BF2DEVCP4       31:0         FFE4       BF2DEVCP4       31:0         FFE4       BF2DEVSIGN1       31:0         FFE4       BF2DEVSIGN1       31:0         FFE4       BF2DEVSIGN0       31:0         FFF4       BF2SEQ2       31:16       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <t< td=""><td>FF78</td><td>ABF2SEQ1</td><td></td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>_</td><td>x</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FF78                        | ABF2SEQ1         |           | _     | _     | _     | _     | _     | _     | _        | _          | _            | _              | _     | _    | _    | _    | _    | _    | x  |

| TFC0       RAP2SEQ0       TSEQ<15:0>         TFC0       BF2DEVCFG3       31:0         FFC4       BF2DEVCFG1       31:0         FFC6       BF2DEVCFG0       31:0         FFC0       BF2DEVCF0       31:0         FFD4       BF2DEVCP1       31:0         FFD4       BF2DEVCP2       31:0         FFD4       BF2DEVCP2       31:0         FFD6       BF2DEVSIGN3       31:0         FFE4       BF2DEVSIGN0       31:0         FFE4       BF2DEVSIGN0       31:0         FFF4       BF2DEVSIGN0       31:0         FFF4       BF2DEVSIGN0       31:0         FFF6       BF2SEQ2       31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             |                  | 31:16     |       |       |       |       |       |       |          | CSEQ       | <15:0>       |                |       |      |      |      |      |      | x  |

| FFC0       BF2DEVCFG3       31:0         FFC4       BF2DEVCFG2       31:0         FFD6       BF2DEVCFG3       31:0         FFD6       BF2DEVCFG3       31:0         FFD6       BF2DEVCP3       31:0         FFD7       BF2DEVCP3       31:0         FFD8       BF2DEVCP1       31:0         FFD8       BF2DEVCP1       31:0         FFD8       BF2DEVCP1       31:0         FFE6       BF2DEVSIGN3       31:0         FFE7       BF2SEQ3       11:16              FFF6       BF2SEQ2       11:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FF7C                        | ABF2SEQ0         |           |       |       |       |       |       |       |          | TSEQ       | <15:0>       |                |       |      |      |      |      |      | x  |

| FFC4       BF2DEVCFG2       31:0         FFC8       BF2DEVCFG1       31:0         FFC0       BF2DEVCF3       31:0         FFD0       BF2DEVCP3       31:0         FFD4       BF2DEVCP1       31:0         FFD6       BF2DEVCP3       31:0         FFD7       BF2DEVCP1       31:0         FFD8       BF2DEVCP3       31:0         FFE0       BF2DEVCP3       31:0         FFE0       BF2DEVSIGN2       31:0         FFE6       BF2DEVSIGN3       31:0         FFE6       BF2DEVSIGN3       31:0         FFE6       BF2DEVSIGN3       31:0         FFE6       BF2DEVSIGN3       31:0         FFE7       BF2DEVSIGN3       31:0         FFE7       BF2DEVSIGN3       31:0         FFF6       BF2SEQ3       31:16       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FFC0                        | BF2DEVCFG3       | 31:0      |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| FFC8       BF2DEVCFG1       31:0         FFC0       BF2DEVCF3       31:0         FFD4       BF2DEVCP1       31:0         FFD8       BF2DEVCP1       31:0         FFD6       BF2DEVCP1       31:0         FFD6       BF2DEVCP1       31:0         FFD6       BF2DEVCP0       31:0         FFD7       BF2DEVSIGN3       31:0         FFE8       BF2DEVSIGN3       31:0         FFE8       BF2DEVSIGN3       31:0         FFF6       BF2DEVSIGN3       31:0         FFF6       BF2DEVSIGN4       31:0         FFF6       BF2DEVSIGN4       31:0         FFF7       BF2SEQ3       31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                             |                  |           |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| FFCC BF2DEVCPG0 31:0         FFD0 BF2DEVCP3 31:0         FFD4 BF2DEVCP3 31:0         FFD5 BF2DEVCP1 31:0         FFD6 BF2DEVCP0 31:0         FFD6 BF2DEVCP0 31:0         FFE4 BF2DEVSIGN3 31:0         FFE4 BF2DEVSIGN3 31:0         FFE4 BF2DEVSIGN0 31:0         FFE6 BF2DEVSIGN0 31:0         FFE7 BF2DEVSIGN0 31:0         FFE7 BF2DEVSIGN0 31:0         FFF6 BF2DEVSIGN0 31:0         FFF6 BF2DEVSIGN0 31:0         FFF6 BF2DEVSIGN0 31:0         FFF7 BF2DEVSIGN0 31:0         FFF8 BF2DEVSIGN0 31:0         FFF9 BF2SEQ2       31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |                  |           |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| FFD0 BF2DEVCP3 31:0         FFD4 BF2DEVCP3 31:0         FFD6 BF2DEVCP1 31:0         FFD6 BF2DEVCP0 31:0         FFE0 BF2DEVSIGN3 31:0         FFE4 BF2DEVSIGN2 31:0         FFE6 BF2DEVSIGN3 31:0         FFE6 BF2DEVSIGN0 31:0         FFE6 BF2DEVSIGN0 31:0         FFE6 BF2DEVSIGN0 31:0         FFF6 BF2DEQ2         31:16       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td>FFCC</td> <td></td> <td>x</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FFCC                        |                  |           |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| FFD4       BF2DEVCP2       31:0         FFD8       BF2DEVCP1       31:0         FFD0       BF2DEVCP0       31:0         FFE0       BF2DEVSIGN2       31:0         FFE4       BF2DEVSIGN2       31:0         FFE6       BF2DEVSIGN2       31:0         FFF6       BF2DEVSIGN3       31:0         FFF7       BF2SEQ2       31:16       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td></td> <td>x</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             |                  |           |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| Note: See Table 34-1 for the bit descriptions.           FFD8         BF2DEVCP0         31:0           FFC0         BF2DEVSIGN3         31:0           FFE4         BF2DEVSIGN2         31:0           FFE6         BF2DEVSIGN3         31:0           FFE6         BF2DEVSIGN3         31:0           FFE6         BF2DEVSIGN3         31:0           FFE6         BF2DEVSIGN1         31:0           FFE6         BF2DEVSIGN0         31:0           FFF6         BF2SEQ3         31:16         -           15:0         -         -         -         -         -         -           FFF6         BF2SEQ2         31:16         -         -         -         -         -         -         -           FFF7         BF2SEQ2         31:16         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                             |                  |           |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| FFDC       BF2DEVCP0       31:0         FFE0       BF2DEVSIGN3       31:0         FFE4       BF2DEVSIGN2       31:0         FFE8       BF2DEVSIGN0       31:0         FFE0       BF2DEVSIGN0       31:0         FFE0       BF2DEVSIGN0       31:0         FFF0       BF2DEVSIGN0       31:0         FFF0       BF2SEQ3       31:16                                                                                  -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FFD8                        |                  |           |       |       |       |       |       |       | Note: Se | e Table 34 | -1 for the b | it description | ons.  |      |      |      |      |      | x  |

| FFE0       BF2DEVSIGN3       31:0         FFE4       BF2DEVSIGN2       31:0         FFE8       BF2DEVSIGN0       31:0         FFE0       BF2DEVSIGN0       31:0         FFF0       BF2SEQ3       31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             |                  |           |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| FFE4       BF2DEVSIGN2       31:0         FFE8       BF2DEVSIGN1       31:0         FFE0       BF2DEVSIGN0       31:0         FFF0       BF2SEQ3       31:16                                                                                                     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                             |                  | 31:0      |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| FFE8       BF2DEVSIGN1       31:0         FFE0       BF2DEVSIGN0       31:0         FFF0       BF2SEQ3 <sup>31:16</sup> / <sub>15:0</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             |                  |           |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| FFEC       BF2DEVSIGNO       31:0         FFFO       BF2SEQ3       31:16       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             |                  |           |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      | x  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             |                  |           |       |       |       |       |       |       |          |            |              |                |       |      |      |      |      |      |    |

| FFF0       BF2SEQ3       15:0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             |                  |           | _     | _     | _     | —     | —     | —     | _        | _          | _            | _              | _     | _    | _    | _    | _    | _    | x  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FFF0                        | BF2SEQ3          |           |       |       |       |       | _     |       |          |            | _            |                | _     |      | _    | _    |      | _    | _  |