Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048ech100-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 5: PIN NAMES FOR 144-PIN DEVICES (CONTINUED)

# 144-PIN LQFP AND TQFP (TOP VIEW)

## PIC32MZ0512EC(E/F/K)144 PIC32MZ1024EC(G/H/M)144 PIC32MZ1024EC(E/F/K)144 PIC32MZ2048EC(G/H/M)144

144

| PhineFull Pin NamePhin73VeusRPD1/SCK1/RD174VUSBNV3FD1/SCK1/RD175VSSFD1/SCK1/RD176D-FD1/SCK1/RD177D-FD1/SCK1/RD1/SRD378RPF3USBID/RF3FD1/SCK1/RD1/SRD379SDA3/RPF2/RF2FD180SCL3/RPF3/RF8FD1/SCK1/RD181ERXD0/RH8FD1/SCK1/RD182ERXD3/RH9FD183ECOLRH10FD1/SCK1/RD484EBIN2Y/RD4/RA3FD185SCL2/RA2FD186EBIROY1/SDA2/RA3FD187EBIA3/RPF4/SDA5/PMA9/RF4FD188Vo0FD189VSSFD1/SCK1/RM14/RA490EBIA3/RPF4/SDA5/PMA9/RF4FD191EBIA3/RPF5/SCL5/PMA3/RF4FD192EBIA3/RPF5/SCL5/PMA3/RF4FD1/SCK1/RA693EBIA3/RK4FD1/SCK1/RA694FD1/SCK4/RD195RP11/SCK4/RD196RP11/SCK1/RA1597EBIA3/RK498RP10/SCK4/RD199EMOC/RPD1/RD199EMOC/RPD1/RD191EBIA3/RC1391EBICSS/RJ492EBIA3/RC1393RD10/SCK1/RD194EBIO/RPD1/RD195EBIO/RPD1/RD196RP11/SCC1/RD197EBIA3/RC1398RP10/SCK1/RD199EBIA3/RC13910EBIA3/RC13911EBIA3/RC                                                                                                                                                                                                                                                                                                                                                                                                                   |     |                             |     | 1                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------|-----|-------------------------|

| 74       VUSB3V3         74       VUSB3V3         75       VSS         76       D-         77       D+         78       RPF3/USBID/RF3         81       ERVD0/RF8         81       ERXD0/RF8         82       ECOL/RH10         83       ECOL/RH10         84       EBIRDY2/RH11         85       SCL2/RA2         86       EBIRDY1/SDA2/RA3         87       EBIA3/RPF4/RSA         88       VoD         89       VSS         80       CL2/RA2         81       ENXD/RM4         82       ECOL/RH10         84       EBIRDY1/SDA2/RA3         85       SCL2/RA2         86       VoD         87       EBIA3/RPF4/SDA5/PMA9/RF4         90       EBIA3/RPF4/SDA5/PMA9/RF4         91       EBIA3/RPF4/SDA5/PMA9/RF5         92       EBIA14/PMCS1/PMA14/RA4         93       EBIA14/RM4         94       EBIA2/RK4         95       RPA14/SCL1/RA14         96       RPA14/SCL1/RA14         97       EBIA15/RPD6/PMCS2/PMA15/RD9         98       RPD10/                                                                                                                                                                                                                                 |     | Full Pin Name               |     | Full Pin Name           |

| 75       Vss         76       D-         77       D+         78       RPF3/USBID/RF3         79       SDA3/RPF2/RF2         80       SCL2/RPF3/RF8         81       ERXD0/RH8         82       ERXD3/RH9         83       ECOL/RH10         84       EBIRDY/2/RH11         85       SCL2/RA2         86       EBIRDY1/SDA2/RA3         87       EBIA14/PMCS1/PMA1/RA4         88       VoD         90       EBIA2/RK4         91       EBIA2/RK4         92       EBIA19/RK4         93       EBIA20/RK6         94       EBIA20/RK6         95       RPA14/SCL1/RA14         96       RPA14/SCL1/RA14         97       EBIA20/RK6         98       RPD10/SCK4/RD10         99       EBIC3/RL         91       EBIC3/RL         92       RH14         103       EBIC3/RL         104       RPD0/RCRD1/RD1         105       SOSCU/RPC13/RC13         106       SOSCO/RPC13/RC14         107       VoD           10                                                                                                                                                                                                                                                                        | 73  | VBUS                        | 109 | RPD1/SCK1/RD1           |

| 76       D-         77       D+         78       RPF3UUSBID/RF3         79       SDA3/RPF2/RF2         80       SCL3/RPF3/RF8         81       ERXD0/RH8         82       ERXD3/RH9         83       ECOL/RH10         84       EBIRDY2/RPL3/RD4         85       SCL3/RPF2/RH1         86       EBIRDY2/RH11         87       EBIA14/PMCS1/PMA14/RA4         88       Vb0         87       EBIA14/PMCS1/PMA14/RA4         88       Vb0         89       Vss         90       EBIA9/RPF4/SDA5/PMA9/RF4         91       EBIA9/RPF4/SDA5/PMA9/RF4         92       EBIA14/PMCS1/PMA14/RA4         93       EBIA19/RK5         94       EBIA20/RK6         93       EBIA14/RK15         94       EBIA20/RK6         95       RP10/SCK4/RD10         96       RPA14/SCD1/RA15         97       EBIA13/RPD9/PMCS2/PMA15/RD9         98       RPD10/SCK4/RD10         99       EMDC/RPD11/RD11         104       RPD0/RTCC/INT0/RD0         105       SOSCURPC13/RC13         106       SOSCO/RPC                                                                                                                                                                                              | 74  | VUSB3V3                     | 110 | EBID14/RPD2/PMD14/RD2   |

| 77       D+         78       RPF3/USBID/RF3         79       SDA3/RP52/RF2         80       SCL3/RPF8/RF8         81       ERXD0/RH8         82       ERXD3/RH9         83       ECOL/RH10         84       EBIRDY/SDA2/RA3         85       SCL2/RA2         86       EBIRDY/SDA2/RA3         87       EBIA14/PMCS1/PMA14/RA4         88       Vop         89       Vss         81       EBIA9/RPF4/SDA2/RA3         81       EBIA9/RPF4/SDA2/RA3         82       EBIA19/RK5         84       EBIA19/RF5/SCL5/PMA9/RF4         90       EBIA9/RPF4/SDA5/PMA9/RF4         91       EBIA9/RF4/SDA5/PMA9/RF4         92       EBIA19/RK5         93       EBIA19/RK5         94       EBIA2/RK4         95       RPA14/SCL1/RA14         96       RPA14/SCL1/RA14         97       EBIA19/RK6         98       RPD10/SCK4/RD10         98       RPD10/SCK4/RD10         99       EBID2/PMD1/RD11         100       ECS/R/H12         111       EBICS2/RJ6         113       EBICS2/RJ6                                                                                                                                                                                                     | 75  | Vss                         | 111 | EBID15/RPD3/PMD15/RD3   |

| 78         RPF3/USBID/RF3           79         SDA3/RPF2/RF2           80         SCL3/RPF8/RF8           81         ERXD0/RH8           82         ERXD3/RH9           83         ECOL/RH0           84         EBIRDY2/RH1           85         SCL2/RA2           86         EBIRDY2/RH11           87         EBIRDY2/RH11           88         Vob           89         Vss           89         Vss           81         EBIA9/2/RL3           81         EBIA9/2/RL3           82         ERXD3/RH4           84         EBIRDY2/RH1           85         SCL2/RA2           86         Vob           87         EBIA14/PMCS1/PMA9/RF4           88         Vob           90         EBIA9/RPF4/SDA5/PMA9/RF4           91         EBIA9/RPF4/SDA5/PMA9/RF4           92         EBIA19/RK4           93         EBIA19/RK4           94         EBIA20/RK6           97         EBIA19/RK4           98         RPD10/SCK4/RD10           99         EMDC/RPD1/RD11           133         EBICS7/RJ6                                                                                                                                                                              | 76  | D-                          | 112 | EBID12/RPD12/PMD12/RD12 |

| 79         SDA3/RPF2/RF2           81         SCL3/RPF3/RF8           81         ERXD0/RH8           82         ERXD3/RH9           83         ECOL/RH10           84         EBIRDY2/RH1           85         SCL2/RA2           86         EBIRDY1/SDA2/RA3           87         EBIA14/PMCS1/PMA14/RA4           90         EBIA9/RF4/SDA5/PMA9/RF4           91         EBIA9/RF5/SCL5/PMA9/RF4           92         EBIA18/RK4           93         EBIA20/RK6           94         EBIA20/RK6           94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA15/SDA1/RA15           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           98         RPD10/SCK4/RD10           99         EMIC/RPD11/RD11           100         ECRS/RH12           1010         ECRS/RH12           102         RH4           103         EBICS/RA7           104         RPD0/RTCC/INT0/RD0           105         SOSC//RPC13/RC13           106         SOSC//RPC13/RC13           107         Vod                                                                                                                                 | 77  | D+                          | 113 | EBID13/PMD13/RD13       |

| 80         SCL3/RPF8/RF8           81         ERXD0/RH8           82         ERXD3/RH9           83         ECOURH10           84         EBIRDY2/RH1           85         SCL3/RP5/RD5           84         EBIRDY1/SDA2/RA3           87         EBIA14/PMCS1/PMA14/RA4           88         Vob           87         EBIA14/PMCS1/PMA14/RA4           120         ETXELX/RPD7/RD7           88         Vob           90         EBIA9/RF5/SCL5/PMA9/RF4           91         EBIA9/RF5/SCL5/PMA8/RF5           92         EBIA19/RK5           93         EBIA19/RK6           94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA15/SDA1/RA15           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           99         EMDC/RPD1/RD11           136         VSS           100         ECRS/RH2           112         EBICS/R/A           133         EBICS/R/A           134         EBICS/R/A           135         EBID0/PMD0/RE0           136         VSS           10                                                                                                                                          | 78  | RPF3/USBID/RF3              | 114 | ETXERR/RJ0              |

| 81         ERXD0/RH8           82         ERXD3/RH9           83         ECOL/RH10           84         EBIRDY2/RH11           85         SCL2/RA2           86         EBIRDY1/SDA2/RA3           87         EDIA14/PMCS1/PMA14/RA4           88         VoD           89         Vss           80         EBIA3/RPF4/SDA5/PMA9/RF4           90         EBIA3/RPF5/SCL5/PMA8/RF5           91         EBIA3/RPF5/SCL5/PMA8/RF5           92         EBIA19/RK5           93         EBIA3/RPF5/SCL5/PMA8/RF5           94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA14/SCL1/RA14           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           99         EMC/RPD11/RD11           100         ECRS3/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA23/RH15           104         RPD0//SCC/INT0/RD0           105         SOSC//RPC13/RC13           106         SOSCO/RPC14/T1CK/RC14           107         VoD           106         SOSCO                                                                                                                | 79  | SDA3/RPF2/RF2               | 115 | EMDIO/RJ1               |

| 82         ERXD3/RH9           83         ECOL/RH10           84         EBIRDY/2/RH11           85         SCL2/RA2           86         EBIRDY/1/SDA2/RA3           87         EBIRDY1/SDA2/RA3           88         Vod           87         EBIRDY1/SDA2/RA3           88         Vod           87         EBIRDY1/SDA2/RA3           88         Vod           89         Vss           80         EBIA9//RP4/SDA5/PMA9/RF4           90         EBIA9/RP5/SCL5/PMA8/RF5           91         EBIA3/RP5/SCL5/PMA8/RF5           92         EBIA19/RK4           93         EBIA19/RK4           94         EBIA20/RK6           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           90         ERXDV/ECRSDV/RH13           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA23/RH15           104         RPD0/RCC/INT0/RD0           105         SOSC//RPC13/RC13           106         SOSC//RPC13/RC13           107         Vod                                                                                                                                          | 80  | SCL3/RPF8/RF8               | 116 | EBIRDY3/RJ2             |

| 83         ECOL/RH10           84         EBIRDY2/RH10           85         SCL2/RA2           86         EBIRDY1/SDA2/RA3           87         EBIA14/PMCS1/PMA14/RA4           88         VoD           89         Vss           80         EBIA14/PMCS1/PMA14/RA4           90         EBIA14/PMCS1/PMA9/RF4           91         EBIA8/RPF4/SDA5/PMA9/RF4           92         EBIA18/RK4           93         EBIA19/RK5           94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA14/SCL1/RA15           97         EBIA15/RPD0/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           100         ECRS/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA23/RH15           104         RPD0/RTCC/INT0/RD0           105         SOSCO/RPC13/RC13           106         SOSCO/RPC14/T1CK/RC14           107         VoD                                                                                                                                                                                                                             | 81  | ERXD0/RH8                   | 117 | EBIA22/RJ3              |

| 84         EBIRDY2/RH11           85         SCL2/RA2           86         EBIRDY1/SDA2/RA3           87         EBIA14/PMCS1/PMA14/RA4           88         Vob           88         Vob           90         EBIA9/RPF4/SDA5/PMA9/RF4           91         EBIA9/RPF4/SDA5/PMA9/RF4           92         EBIA19/RK4           93         EBIA9/RPF5/SCL5/PMA8/RF5           94         EBIA20/RK6           93         EBIA19/RK4           94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA14/SCL1/RA14           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           100         ECGS/RH12           101         ERICS3/RJ4           102         RH14           103         EBIA23/RH15           104         RPD0/FCC/INT0/RD0           105         SOSCI/RPC13/RC13           106         SOSCO/RPC14/T1CK/RC14           107         Vob                                                                                                                                                                                                                               | 82  | ERXD3/RH9                   | 118 | SQICS0/RPD4/RD4         |

| 85         SCL2/RA2           86         EBIRDY1/SDA2/RA3           87         EBIA14/PMCS1/PMA14/RA4           88         Vob           88         Vob           89         Vss           90         EBIA9/RPF4/SDA5/PMA9/RF4           91         EBIA8/RPF5/SCL5/PMA9/RF4           92         EBIA14/PMCS1/PMA9/RF4           93         EBIA9/RPF5/SCL5/PMA9/RF5           92         EBIA18/RK4           93         EBIA9/RP5/SCL5/PMA9/RF5           94         EBIA9/RK5           95         RPA14/SCL1/RA14           96         RPA14/SCL1/RA14           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           100         ECRS/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA2/RH15           104         RPD0/RTCC/INT0/RD0           105         SOSCI/RPC13/RC13           106         SOSCO/RPC14/T1CK/RC14           107         Vob           108         EBID2/PMD3/RE2           109         RD2/SQID0/RG13           106                                                                                                                  | 83  | ECOL/RH10                   | 119 | SQICS1/RPD5/RD5         |

| 86         EBIRDY1/SDA2/RA3           87         EBIA14/PMCS1/PMA14/RA4           88         Vob           88         Vob           89         Vss           90         EBIA9/RPF4/SDA5/PMA9/RF4           91         EBIA8/RPF5/SCL5/PMA8/RF5           92         EBIA16/RK4           93         EBIA19/RK5           94         EBIA20/RK6           94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA15/SDA1/RA15           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           99         EBICS7/RJ3           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA2/RH12           104         RPD0//SCK4/RD10           105         SOSCI/RPC13/RC13           106         SOSC/RPC13/RC13           107         Vob           108         SSEO/RPC13/RC13           109         RDD0/RPC1/RD1/RD1           114         TRD0/SQLD0/RG14           1142         EBID2/PMD2/RE2           1107         Vob                                                                                                                                                                      | 84  | EBIRDY2/RH11                | 120 | ETXEN/RPD6/RD6          |

| 87         EBIA14/PMCS1/PMA14/RA4         123         Vss           88         Vod         124         EBID11/RPF0/PMD11/RF0           89         Vss         125         EBID10/RPF1/PMD10/RF1           90         EBIA9/RPF4/SDA5/PMA9/RF4         126         EBIA21/RK7           91         EBIA8/RPF5/SCL5/PMA8/RF5         127         EBID9/RPG1/PMD9/RG1           92         EBIA18/RK4         128         EBID9/RPG1/PMD9/RG1           93         EBIA20/RK6         129         TRCLK/SQICLK/RA6           94         EBIA20/RK6         130         TRD3/SQID3/RA7           95         RPA14/SCL1/RA14         131         EBICS0/RJ4           96         RPA15/SDA1/RA15         132         EBICS1/RJ5           97         EBIA15/RPD9/PMCS2/PMA15/RD9         133         EBICS2/RJ6           98         RPD10/SCK4/RD10         134         EBICS3/RJ7           99         EMDC/RPD11/RD11         135         EBID0/PMD0/RE0           100         ECRS/RH12         136         Vss           101         ERXDV/ECRSDV/RH13         137         Vod           102         RH14         138         EBID1/PMD1/RE1           103         EBIA3/RH15         139 | 85  | SCL2/RA2                    | 121 | ETXCLK/RPD7/RD7         |

| 88         VDD           89         Vss           90         EBIA9/RPF4/SDA5/PMA9/RF4           91         EBIA9/RPF4/SDA5/PMA9/RF4           91         EBIA8/RPF5/SCL5/PMA8/RF5           92         EBIA18/RK4           93         EBIA20/RK6           94         EBIA20/RK6           94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA15/SDA1/RA15           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           100         ECRS/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA2/RH15           104         RPD0/FTCC/INT0/RD0           105         SOSC/RPC13/RC13           106         SOSCO/RPC14/T1CK/RC14           107         VD                                                                                                                                                                                                                                                                                                                                                                            | 86  | EBIRDY1/SDA2/RA3            | 122 | VDD                     |

| 89         Vss           90         EBIA9/RPF4/SDA5/PMA9/RF4           91         EBIA8/RPF5/SCL5/PMA8/RF5           92         EBIA18/RK4           93         EBIA19/RK5           94         EBIA20/RK6           94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA15/SDA1/RA15           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           100         ECRS/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA23/RH15           104         RPD0/RTCC/INT0/RD0           105         SOSC//RPC14/T1CK/RC14           106         SOSCO/RPC14/T1CK/RC14           107         Vod                                                                                                                                                                                                                                                                                                                                                                                                                                           | 87  | EBIA14/PMCS1/PMA14/RA4      | 123 | Vss                     |

| 90         EBIA9/RPF4/SDA5/PMA9/RF4           91         EBIA8/RPF5/SCL5/PMA8/RF5           92         EBIA18/RK4           93         EBIA19/RK5           94         EBIA20/RK6           94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA15/SDA1/RA15           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           100         ECRS/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA2/RC13           104         RPD0/RTCC/INT0/RD0           105         SOSCO/RPC14/T1CK/RC14           106         SOSCO/RPC14/T1CK/RC14           107         Vod                                                                                                                                                                                                                                                                                                                                                                                                                                | 88  | Vdd                         | 124 | EBID11/RPF0/PMD11/RF0   |

| 91         EBIA8/RPF5/SCL5/PMA8/RF5           92         EBIA18/RK4           93         EBIA19/RK5           94         EBIA20/RK6           94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA15/SDA1/RA15           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           100         ECRS/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA23/RH15           104         RPD0/RTCC/INT0/RD0           105         SOSCI/RPC13/RC13           106         SOSCO/RPC14/T1CK/RC14           107         VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 89  | Vss                         | 125 | EBID10/RPF1/PMD10/RF1   |

| 92         EBIA18/RK4           93         EBIA19/RK5           94         EBIA20/RK6           94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA15/SDA1/RA15           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           100         ECRS/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA23/RH15           104         RPD0/RTCC/INT0/RD0           105         SOSCO/RPC13/RC13           106         SOSCO/RPC14/T1CK/RC14           107         Vod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90  | EBIA9/RPF4/SDA5/PMA9/RF4    | 126 | EBIA21/RK7              |

| 93         EBIA19/RK5           94         EBIA20/RK6           94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA15/SDA1/RA15           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           100         ECRS/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA23/RH15           104         RPD0/RTCC/INT0/RD0           105         SOSCO/RPC14/T1CK/RC14           106         SOSCO/RPC14/T1CK/RC14           107         VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 91  | EBIA8/RPF5/SCL5/PMA8/RF5    | 127 | EBID9/RPG1/PMD9/RG1     |

| 94         EBIA20/RK6           95         RPA14/SCL1/RA14           96         RPA15/SDA1/RA15           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           100         ECRS/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA23/RH15           104         RPD0/RTCC/INT0/RD0           105         SOSC//RPC13/RC13           106         SOSCO/RPC14/T1CK/RC14           107         Vod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 92  | EBIA18/RK4                  | 128 | EBID8/RPG0/PMD8/RG0     |

| 95         RPA14/SCL1/RA14         131         EBICS0/RJ4           96         RPA15/SDA1/RA15         132         EBICS1/RJ5           97         EBIA15/RPD9/PMCS2/PMA15/RD9         133         EBICS2/RJ6           98         RPD10/SCK4/RD10         134         EBICS3/RJ7           99         EMDC/RPD11/RD11         135         EBID0/PMD0/RE0           100         ECRS/RH12         136         Vss           101         ERXDV/ECRSDV/RH13         137         VDD           102         RH14         138         EBID1/PMD1/RE1           103         EBIA23/RH15         139         TRD2/SQID2/RG14           104         RPD0/RTCC/INT0/RD0         140         TRD1/SQID1/RG12           105         SOSCO/RPC14/T1CK/RC14         142         EBID2/PMD2/RE2           107         VDD         143         EBID3/RPE3/PMD3/RE3                                                                                                                                                                                                                                                                                                                                       | 93  | EBIA19/RK5                  | 129 | TRCLK/SQICLK/RA6        |

| 96         RPA15/SDA1/RA15           97         EBIA15/RPD9/PMCS2/PMA15/RD9           98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           100         ECRS/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA23/RH15           104         RPD0/RTCC/INT0/RD0           105         SOSCO/RPC14/T1CK/RC14           106         SOSCO/RPC14/T1CK/RC14           107         Vod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 94  | EBIA20/RK6                  | 130 | TRD3/SQID3/RA7          |

| 97         EBIA15/RPD9/PMCS2/PMA15/RD9         133         EBICS2/RJ6           98         RPD10/SCK4/RD10         134         EBICS3/RJ7           99         EMDC/RPD11/RD11         135         EBID0/PMD0/RE0           100         ECRS/RH12         136         Vss           101         ERXDV/ECRSDV/RH13         137         VDD           102         RH14         138         EBID1/PMD1/RE1           103         EBIA23/RH15         139         TRD2/SQID2/RG14           104         RPD0/RTCC/INT0/RD0         140         TRD1/SQID1/RG12           105         SOSCO/RPC13/RC13         141         TRD0/SQID0/RG13           106         SOSCO/RPC14/T1CK/RC14         142         EBID2/PMD2/RE2           107         VDD         143         EBID3/RPE3/PMD3/RE3                                                                                                                                                                                                                                                                                                                                                                                                    | 95  | RPA14/SCL1/RA14             | 131 | EBICS0/RJ4              |

| 98         RPD10/SCK4/RD10           99         EMDC/RPD11/RD11           100         ECRS/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA23/RH15           104         RPD0/RTCC/INT0/RD0           105         SOSCO/RPC13/RC13           106         SOSCO/RPC14/T1CK/RC14           107         VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 96  | RPA15/SDA1/RA15             | 132 | EBICS1/RJ5              |

| 99         EMDC/RPD11/RD11         135         EBID0/PMD0/RE0           100         ECRS/RH12         136         Vss           101         ERXDV/ECRSDV/RH13         137         VDD           102         RH14         138         EBID1/PMD1/RE1           103         EBIA23/RH15         139         TRD2/SQID2/RG14           104         RPD0/RTCC/INT0/RD0         140         TRD1/SQID1/RG12           105         SOSCO/RPC13/RC13         141         TRD0/SQID0/RG13           106         SOSCO/RPC14/T1CK/RC14         142         EBID2/PMD2/RE2           107         VDD         143         EBID3/RPE3/PMD3/RE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97  | EBIA15/RPD9/PMCS2/PMA15/RD9 | 133 | EBICS2/RJ6              |

| 100         ECRS/RH12           101         ERXDV/ECRSDV/RH13           102         RH14           103         EBIA23/RH15           104         RPD0/RTCC/INT0/RD0           105         SOSCO/RPC13/RC13           106         SOSCO/RPC14/T1CK/RC14           107         VDD           108         EBID2/PMD2/RE2           107         VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 98  | RPD10/SCK4/RD10             | 134 | EBICS3/RJ7              |

| 101         ERXDV/ECRSDV/RH13         137         VDD           102         RH14         138         EBID1/PMD1/RE1           103         EBIA23/RH15         139         TRD2/SQID2/RG14           104         RPD0/RTCC/INT0/RD0         140         TRD1/SQID1/RG12           105         SOSCO/RPC13/RC13         141         TRD0/SQID0/RG13           106         SOSCO/RPC14/T1CK/RC14         142         EBID2/PMD2/RE2           107         VDD         143         EBID3/RPE3/PMD3/RE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 99  | EMDC/RPD11/RD11             | 135 | EBID0/PMD0/RE0          |

| 102         RH14         138         EBID1/PMD1/RE1           103         EBIA23/RH15         139         TRD2/SQID2/RG14           104         RPD0/RTCC/INT0/RD0         140         TRD1/SQID1/RG12           105         SOSCI/RPC13/RC13         141         TRD0/SQID0/RG13           106         SOSCO/RPC14/T1CK/RC14         142         EBID2/PMD2/RE2           107         VDD         143         EBID3/RPE3/PMD3/RE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100 | ECRS/RH12                   | 136 | Vss                     |

| 103         EBIA23/RH15         139         TRD2/SQID2/RG14           104         RPD0/RTCC/INT0/RD0         140         TRD1/SQID1/RG12           105         SOSCI/RPC13/RC13         141         TRD0/SQID0/RG13           106         SOSCO/RPC14/T1CK/RC14         142         EBID2/PMD2/RE2           107         VDD         143         EBID3/RPE3/PMD3/RE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 101 | ERXDV/ECRSDV/RH13           | 137 | VDD                     |

| 104         RPD0/RTCC/INT0/RD0         140         TRD1/SQID1/RG12           105         SOSCI/RPC13/RC13         141         TRD0/SQID0/RG13           106         SOSCO/RPC14/T1CK/RC14         142         EBID2/PMD2/RE2           107         VDD         143         EBID3/RPE3/PMD3/RE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 102 | RH14                        | 138 | EBID1/PMD1/RE1          |

| 105         SOSCI/RPC13/RC13         141         TRD0/SQID0/RG13           106         SOSCO/RPC14/T1CK/RC14         142         EBID2/PMD2/RE2           107         VDD         143         EBID3/RPE3/PMD3/RE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 103 | EBIA23/RH15                 | 139 | TRD2/SQID2/RG14         |

| 106         SOSCO/RPC14/T1CK/RC14         142         EBID2/PMD2/RE2           107         VDD         143         EBID3/RPE3/PMD3/RE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 104 | RPD0/RTCC/INT0/RD0          | 140 | TRD1/SQID1/RG12         |

| 107 VDD 143 EBID3/RPE3/PMD3/RE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 105 | SOSCI/RPC13/RC13            | 141 | TRD0/SQID0/RG13         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 106 | SOSCO/RPC14/T1CK/RC14       | 142 | EBID2/PMD2/RE2          |

| 108 Vss 144 EBID4/AN18/PMD4/RE4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 107 | Vdd                         | 143 | EBID3/RPE3/PMD3/RE3     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 108 | Vss                         | 144 | EBID4/AN18/PMD4/RE4     |

Note

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select (PPS)" for restrictions.

2: Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See Section 12.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

|          |                        | Pin Nu          | mber            |                          |             |                |                                                                                                                                                                                               |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                   |

| CLKI     | 31                     | 49              | B28             | 71                       | Ι           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                        |

| CLKO     | 32                     | 50              | A33             | 72                       | 0           | _              | Oscillator crystal output. Connects to crystal or reso-<br>nator in Crystal Oscillator mode. Optionally functions<br>as CLKO in RC and EC modes. Always associated<br>with OSC2 pin function. |

| OSC1     | 31                     | 49              | B28             | 71                       | Ι           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                               |

| OSC2     | 32                     | 50              | A33             | 72                       | 0           | _              | Oscillator crystal output. Connects to crystal or reso-<br>nator in Crystal Oscillator mode. Optionally functions<br>as CLKO in RC and EC modes.                                              |

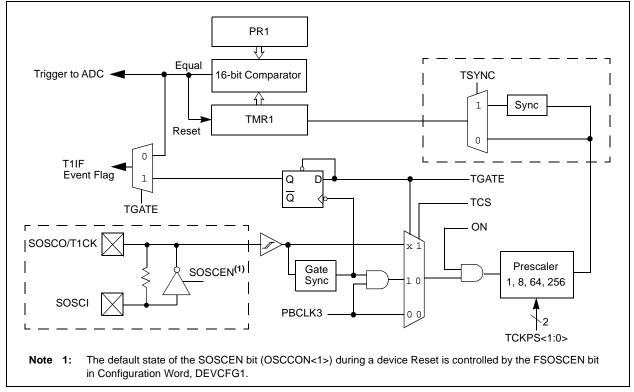

| SOSCI    | 47                     | 72              | B41             | 105                      | Ι           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                |

| SOSCO    | 48                     | 73              | A49             | 106                      | 0           | —              | 32.768 low-power oscillator crystal output.                                                                                                                                                   |

| REFCLKI1 | PPS                    | PPS             | PPS             | PPS                      | Ι           | _              | Reference Clock Generator Inputs 1-4                                                                                                                                                          |

| REFCLKI3 | PPS                    | PPS             | PPS             | PPS                      | Ι           | —              |                                                                                                                                                                                               |

| REFCLKI4 | PPS                    | PPS             | PPS             | PPS                      | Ι           | —              |                                                                                                                                                                                               |

| REFCLKO1 | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | Reference Clock Generator Outputs 1-4                                                                                                                                                         |

| REFCLKO3 | PPS                    | PPS             | PPS             | PPS                      | 0           | —              |                                                                                                                                                                                               |

| REFCLKO4 | PPS                    | PPS             | PPS             | PPS                      | 0           | _              |                                                                                                                                                                                               |

#### **TABLE 1-2: OSCILLATOR PINOUT I/O DESCRIPTIONS**

**Legend:** CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output PPS = Peripheral Pin Select

P = Power I = Input

#### **IC1 THROUGH IC9 PINOUT I/O DESCRIPTIONS TABLE 1-3**:

|               |                        | Pin Nu          | mber            |                          |             |                      |                                        |  |  |  |  |  |

|---------------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------------|----------------------------------------|--|--|--|--|--|

| Pin Name      | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type       | Description                            |  |  |  |  |  |

| Input Capture |                        |                 |                 |                          |             |                      |                                        |  |  |  |  |  |

| IC1           | PPS                    | PPS             | PPS             | PPS                      | I           | ST                   | Input Capture Inputs 1-9               |  |  |  |  |  |

| IC2           | PPS                    | PPS             | PPS             | PPS                      | I           | ST                   | 1                                      |  |  |  |  |  |

| IC3           | PPS                    | PPS             | PPS             | PPS                      | I           | ST                   |                                        |  |  |  |  |  |

| IC4           | PPS                    | PPS             | PPS             | PPS                      | I           | ST                   |                                        |  |  |  |  |  |

| IC5           | PPS                    | PPS             | PPS             | PPS                      | I           | ST                   |                                        |  |  |  |  |  |

| IC6           | PPS                    | PPS             | PPS             | PPS                      | I           | ST                   |                                        |  |  |  |  |  |

| IC7           | PPS                    | PPS             | PPS             | PPS                      | I           | ST                   |                                        |  |  |  |  |  |

| IC8           | PPS                    | PPS             | PPS             | PPS                      | I           | ST                   | 1                                      |  |  |  |  |  |

| IC9           | PPS                    | PPS             | PPS             | PPS                      | I           | ST                   | 1                                      |  |  |  |  |  |

| Legend:       | CMOS = Cl<br>ST = Schm | •               | •               |                          | s           | Analog =<br>O = Outp | Analog input P = Power<br>ut I = Input |  |  |  |  |  |

Schmitt Trigger input with CIVIOS levels TTL = Transistor-transistor Logic input buffer

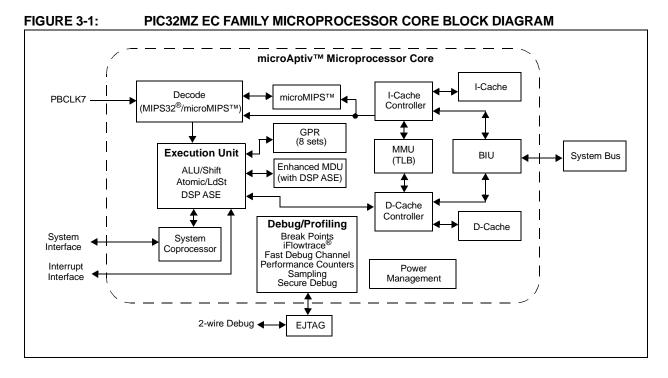

Output PPS = Peripheral Pin Select A block diagram of the PIC32MZ EC family processor core is shown in Figure 3-1.

# TABLE 4-21: SYSTEM BUS TARGET 13 REGISTER MAP

| IAD                         |                  |           |       |       |       |          |          |       |       |      |          |       |           |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|----------|-------|-------|------|----------|-------|-----------|------|--------|--------|---------|--------|---------------|

| ess                         |                  |           |       |       |       |          |          |       |       |      | Bits     |       |           |      |        |        |         |        |               |

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6  | 21/5      | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

|                             |                  | 31:16     | MULTI | —     | —     | —        |          | CODE  | <3:0> |      | _        | —     | -         |      | —      |        | —       |        | 0000          |

| B420                        | SBT13ELOG1       | 15:0      |       |       |       | INI      | ΓID<7:0> |       |       |      | •        | REGIO | N<3:0>    |      | _      | С      | MD<2:0> |        | 0000          |

| D404                        | SBT13ELOG2       | 31:16     | _     | _     | —     | —        | _        | _     | _     | _    | —        | _     | —         | _    | _      | _      | _       | _      | 0000          |

| B424                        | SB113ELUG2       | 15:0      | —     | _     | _     | _        | _        | _     | _     | _    |          | _     | _         | _    | _      | _      | GROU    | P<1:0> | 0000          |

| D 400                       |                  | 31:16     | —     | _     | _     | _        | _        | _     | _     | ERRP |          | _     | _         | _    | _      | _      | _       | _      | 0000          |

| B428                        | SBT13ECON 1      | 15:0      |       | -     | _     | _        | —        | _     |       | _    | _        | _     |           |      | —      | _      | —       | _      | 0000          |

| P420                        | SBT13ECLRS       | 31:16     |       | -     | _     | _        | —        | _     |       | _    | _        | _     |           |      | —      | _      | —       | _      | 0000          |

| D430                        | SBI ISECLKS      | 15:0      |       |       | _     | —        | —        |       |       |      | _        | _     |           |      | _      |        | _       | CLEAR  | 0000          |

| D120                        | SBT13ECLRM       | 31:16     |       |       | _     | —        | —        |       |       |      | _        | _     |           |      | _      |        | _       |        | 0000          |

| D430                        | SBITSECLKI       | 15:0      |       |       | _     | —        | —        |       |       |      | _        | _     |           |      | _      |        | _       | CLEAR  | 0000          |

| B440                        | SBT13REG0        | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6> |       |           |      |        |        |         |        | xxxx          |

| D440                        | SBITSREGU        | 15:0      |       |       | BA    | ASE<5:0> |          |       | PRI   |      |          |       | SIZE<4:0: | >    |        |        | _       |        | xxxx          |

| B450                        | SBT13RD0         | 31:16     |       |       | _     | —        | _        |       |       |      | _        | —     |           |      |        |        | -       |        | xxxx          |

| 5450                        | 3BT I3RD0        | 15:0      |       | -     | —     | —        | _        |       |       |      | _        | _     |           |      | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| B458                        | SBT13WR0         | 31:16     |       | -     | —     | —        | _        |       |       |      | _        | _     |           |      | —      |        | _       |        | xxxx          |

| 5400                        | GBTTSWRU         | 15:0      |       |       | _     | _        | —        |       |       |      | _        | —     |           |      | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

| REGISTE  | ER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER                                                                                 |

|----------|-----------------------------------------------------------------------------------------------------------------------------|

| bit 10-8 | NOSC<2:0>: New Oscillator Selection bits                                                                                    |

|          | 111 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)                                                |

|          | 110 = Reserved                                                                                                              |

|          | 101 = Internal Low-Power RC (LPRC) Oscillator                                                                               |

|          | 100 = Secondary Oscillator (Sosc)<br>011 = Reserved                                                                         |

|          | 010 = Primary Oscillator (Posc) (HS or EC)                                                                                  |

|          | 001 = System PLL (SPLL)                                                                                                     |

|          | 000 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)                                                |

|          | On Reset, these bits are set to the value of the FNOSC<2:0> Configuration bits (DEVCFG1<2:0>).                              |

| bit 7    | CLKLOCK: Clock Selection Lock Enable bit                                                                                    |

|          | 1 = Clock and PLL selections are locked                                                                                     |

|          | 0 = Clock and PLL selections are not locked and may be modified                                                             |

| bit 6    | ULOCK: USB PLL Lock Status bit                                                                                              |

|          | 1 = Indicates that the USB PLL module is in lock or USB PLL module start-up timer is satisfied                              |

|          | 0 = Indicates that the USB PLL module is out of lock or USB PLL module start-up timer is in progress or USB PLL is disabled |

| bit 5    | SLOCK: System PLL Lock Status bit                                                                                           |

|          | 1 = System PLL module is in lock or module start-up timer is satisfied                                                      |

|          | 0 = System PLL module is out of lock, start-up timer is running or system PLL is disabled                                   |

| bit 4    | SLPEN: Sleep Mode Enable bit                                                                                                |

|          | 1 = Device will enter Sleep mode when a WAIT instruction is executed                                                        |

| 1.11.0   | 0 = Device will enter Idle mode when a WAIT instruction is executed                                                         |

| bit 3    | CF: Clock Fail Detect bit                                                                                                   |

|          | <ul> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> </ul>                   |

| bit 2    | Unimplemented: Read as '0'                                                                                                  |

| bit 1    | SOSCEN: Secondary Oscillator (Sosc) Enable bit                                                                              |

| DICT     | 1 = Enable Secondary Oscillator                                                                                             |

|          | 0 = Disable Secondary Oscillator                                                                                            |

| bit 0    | <b>OSWEN:</b> Oscillator Switch Enable bit <sup>(1)</sup>                                                                   |

|          | 1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits                                                  |

|          | 0 = Oscillator switch is complete                                                                                           |

| Note 1:  | The reset value for this bit depends on the setting of the IESO (DEVCFG1<7>) bit. When IESO = 1, the                        |

|          | reset value is '1'. When IESO = 0, the reset value is '0'.                                                                  |

# Note: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

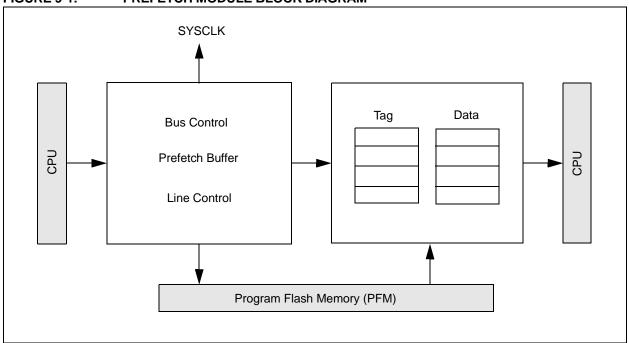

# 9.0 PREFETCH MODULE

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 41. "Prefetch Module for Devices with L1 CPU Cache" (DS60001183), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Prefetch module is a performance enhancing module that is included in PIC32MZ EC family devices. When running at high-clock rates, Wait states must be inserted into Program Flash Memory (PFM) read transactions to meet the access time of the PFM. Wait states can be hidden to the core by prefetching and storing instructions in a temporary holding area that the CPU can access quickly. Although the data path to the CPU is 32 bits wide, the data path to the PFM is 128 bits wide. This wide data path provides the same bandwidth to the CPU as a 32-bit path running at four times the frequency.

The Prefetch module holds a subset of PFM in temporary holding spaces known as lines. Each line contains a tag and data field. Normally, the lines hold a copy of what is currently in memory to make instructions or data available to the CPU without Flash Wait states.

# 9.1 Features

- 4x16 byte fully-associative lines

- One line for CPU instructions

- One line for CPU data

- Two lines for peripheral data

- 16-byte parallel memory fetch

- Configurable predictive prefetch

- Error detection and correction

A simplified block diagram of the Prefetch module is shown in Figure 9-1.

# FIGURE 9-1: PREFETCH MODULE BLOCK DIAGRAM

| Bit<br>Range   | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                   | Bit<br>24/16/8/0 |

|----------------|-------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------------------------|------------------|

| 21.24          | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0                                | U-0              |

| 31:24<br>23:16 | _                 | —                 |                   | —                 | —                    | —                 | —                                  | —                |

| 22.16          | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1                              | R/W-1            |

| 23.10          |                   |                   |                   | CHAIRQ<           | <7:0> <sup>(1)</sup> |                   | U-0                                |                  |

| 15.0           | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1                              | R/W-1            |

| 15:8           |                   |                   |                   | CHSIRQ<           | <7:0> <sup>(1)</sup> |                   | 25/17/9/1<br>U-0<br>R/W-1<br>R/W-1 |                  |

| 7:0            | S-0               | S-0               | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0                                | U-0              |

| 7.0            | CFORCE            | CABORT            | PATEN             | SIRQEN            | AIRQEN               | —                 |                                    | —                |

#### **REGISTER 10-8:** DCHxECON: DMA CHANNEL x EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# bit 31

| bit 31-24 | Unimplemented: Read as '0'                                                                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                                                              |

| 511 20 10 | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                                                                                         |

|           | •                                                                                                                                                                        |

|           | •                                                                                                                                                                        |

|           | •                                                                                                                                                                        |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag<br>00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag         |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                                                              |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                                                                    |

|           | •                                                                                                                                                                        |

|           | •                                                                                                                                                                        |

|           |                                                                                                                                                                          |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer                                                               |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                                                                                          |

|           | <ul> <li>1 = A DMA transfer is forced to begin when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                       |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                                                                                           |

|           | <ul> <li>1 = A DMA transfer is aborted when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                               |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                                                                                            |

|           | <ul> <li>1 = Abort transfer and clear CHEN on pattern match</li> <li>0 = Pattern match is disabled</li> </ul>                                                            |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                                                                     |

|           | <ul> <li>1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs</li> <li>0 = Interrupt number CHSIRQ is ignored and does not start a transfer</li> </ul> |

| bit 3     | AIRQEN: Channel Abort IRQ Enable bit                                                                                                                                     |

|           |                                                                                                                                                                          |

- 1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

- 0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

- bit 2-0 Unimplemented: Read as '0'

- Note 1: See Table 7-2: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

# PIC32MZ Embedded Connectivity (EC) Family

# REGISTER 11-7: USBIE0CSR3: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 3 (ENDPOINT 0)

|              |                   | (==               | /                 |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 21.24        | R-x               | R-x               | R-0               | R-x               | R-x               | R-x               | R-1              | R-0              |