Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 78                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

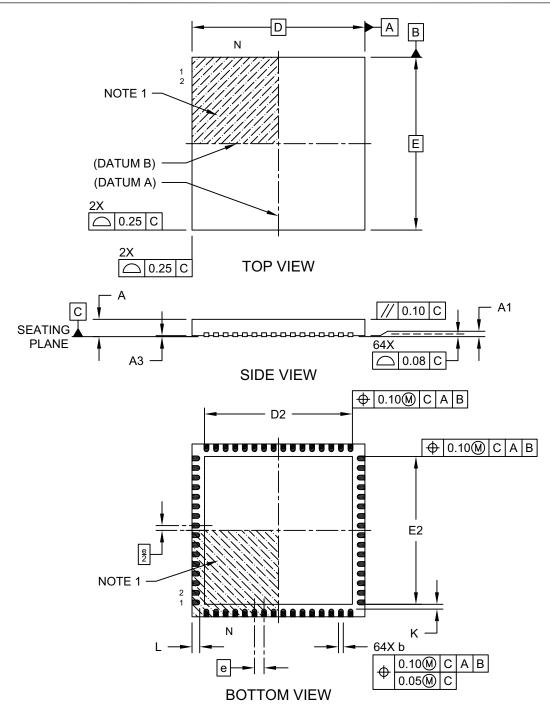

| Mounting Type              | Surface Mount                                                                     |

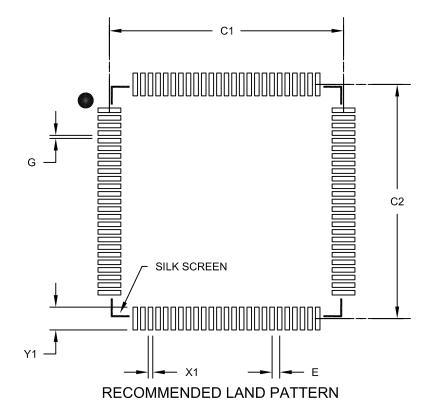

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048ech100t-i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 5: **PIN NAMES FOR 144-PIN DEVICES**

#### 144-PIN LQFP AND TQFP (TOP VIEW)

# PIC32MZ0512EC(E/F/K)144 PIC32MZ1024EC(G/H/M)144 PIC32MZ1024EC(E/F/K)144 PIC32MZ2048EC(G/H/M)144

144

| Pin<br>umber | Full Pin Name                  | Pin<br>Number | Full Pin Name              |

|--------------|--------------------------------|---------------|----------------------------|

| 1            | AN23/RG15                      | 37            | PGEC2/AN46/RPB6/RB6        |

| 2            | EBIA5/AN34/PMA5/RA5            | 38            | PGED2/AN47/RPB7/RB7        |

| 3            | EBID5/AN17/RPE5/PMD5/RE5       | 39            | VREF-/CVREF-/AN27/RA9      |

| 4            | EBID6/AN16/PMD6/RE6            | 40            | VREF+/CVREF+/AN28/RA10     |

| 5            | EBID7/AN15/PMD7/RE7            | 41            | AVDD                       |

| 6            | EBIA6/AN22/RPC1/PMA6/RC1       | 42            | AVss                       |

| 7            | AN35/ETXD0/RJ8                 | 43            | AN38/ETXD2/RH0             |

| 8            | AN36/ETXD1/RJ9                 | 44            | AN39/ETXD3/RH1             |

| 9            | EBIBS0/RJ12                    | 45            | EBIRP/RH2                  |

| 10           | EBIBS1/RJ10                    | 46            | RH3                        |

| 11           | EBIA12/AN21/RPC2/PMA12/RC2     | 47            | EBIA10/AN48/RPB8/PMA10/RB8 |

| 12           | EBIWE/AN20/RPC3/PMWR/RC3       | 48            | EBIA7/AN49/RPB9/PMA7/RB9   |

| 13           | EBIOE/AN19/RPC4/PMRD/RC4       | 49            | CVREFOUT/AN5/RPB10/RB10    |

| 14           | AN14/C1IND/RPG6/SCK2/RG6       | 50            | AN6/RB11                   |

| 15           | AN13/C1INC/RPG7/SDA4/RG7       | 51            | EBIA1/PMA1/RK1             |

| 16           | AN12/C2IND/RPG8/SCL4/RG8       | 52            | EBIA3/PMA3/RK2             |

| 17           | Vss                            | 53            | EBIA17/RK3                 |

| 18           | VDD                            | 54            | Vss                        |

| 19           | EBIA16/RK0                     | 55            | VDD                        |

| 20           | MCLR                           | 56            | TCK/AN29/RA1               |

| 21           | EBIA2/AN11/C2INC/RPG9/PMA2/RG9 | 57            | TDI/AN30/RPF13/SCK5/RF13   |

| 22           | TMS/AN24/RA0                   | 58            | TDO/AN31/RPF12/RF12        |

| 23           | AN25/RPE8/RE8                  | 59            | AN7/RB12                   |

| 24           | AN26/RPE9/RE9                  | 60            | AN8/RB13                   |

| 25           | AN45/C1INA/RPB5/RB5            | 61            | AN9/RPB14/SCK3/RB14        |

| 26           | AN4/C1INB/RB4                  | 62            | AN10/RPB15/OCFB/RB15       |

| 27           | AN37/ERXCLK/EREFCLK/RJ11       | 63            | Vss                        |

| 28           | EBIA13/PMA13/RJ13              | 64            | VDD                        |

| 29           | EBIA11/PMA11/RJ14              | 65            | AN40/ERXERR/RH4            |

| 30           | EBIA0/PMA0/RJ15                | 66            | AN41/ERXD1/RH5             |

| 31           | AN3/C2INA/RPB3/RB3             | 67            | AN42/ERXD2/RH6             |

| 32           | Vss                            | 68            | EBIA4/PMA4/RH7             |

| 33           | Vdd                            | 69            | AN32/RPD14/RD14            |

| 34           | AN2/C2INB/RPB2/RB2             | 70            | AN33/RPD15/SCK6/RD15       |

| 35           | PGEC1/AN1/RPB1/RB1             | 71            | OSC1/CLKI/RC12             |

| 36           | PGED1/AN0/RPB0/RB0             | 72            | OSC2/CLKO/RC15             |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select (PPS)" for restrictions.

Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See Section 12.0 "I/O Ports" for more 2: information.

3: Shaded pins are 5V tolerant.

|                                                                                                        |                        | Pin Nu          | mber            |                          |             |                |                                      |

|--------------------------------------------------------------------------------------------------------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|--------------------------------------|

| Pin Name                                                                                               | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                          |

|                                                                                                        |                        |                 |                 | Ti                       | imer1 thr   | ough Timer     | 9                                    |

| T1CK                                                                                                   | 48                     | 73              | A49             | 106                      | I           | ST             | Timer1 External Clock Input          |

| T2CK                                                                                                   | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer2 External Clock Input          |

| T3CK                                                                                                   | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer3 External Clock Input          |

| T4CK                                                                                                   | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer4 External Clock Input          |

| T5CK                                                                                                   | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer5 External Clock Input          |

| T6CK                                                                                                   | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer6 External Clock Input          |

| T7CK                                                                                                   | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer7 External Clock Input          |

| T8CK                                                                                                   | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer8 External Clock Input          |

| T9CK                                                                                                   | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer9 External Clock Input          |

|                                                                                                        | •                      | •               | •               | Real-                    | Time Clo    | ck and Cale    | endar                                |

| RTCC                                                                                                   | 46                     | 71              | A48             | 104                      | 0           | —              | Real-Time Clock Alarm/Seconds Output |

| Legend:         CMOS = CMOS-compatible input or output         Analog = Analog input         P = Power |                        |                 |                 |                          |             |                |                                      |

#### **TABLE 1-7:** TIMER1 THROUGH TIMER9 AND RTCC PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levelsO = OutputTTL = Transistor-transistor Logic input bufferPPS = Peripl

Analog = Analog input

PPS = Peripheral Pin Select

I = Input

DS60001191G-page 24

|              |                        | Pin Nu          | mber            |                          |             |                |                        |

|--------------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|------------------------|

| Pin Name     | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description            |

|              |                        |                 | Unive           | ersal Asyn               | chronou     | IS Receive     | r Transmitter 1        |

| U1RX         | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART1 Receive          |

| U1TX         | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART1 Transmit         |

| U1CTS        | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | UART1 Clear to Send    |

| U1RTS        | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART1 Ready to Send    |

| Universal As |                        |                 |                 | rsal Asyn                | chronou     | s Receive      | r Transmitter 2        |

| U2RX         | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART2 Receive          |

| U2TX         | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART2 Transmit         |

| U2CTS        | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | UART2 Clear To Send    |

| U2RTS        | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART2 Ready To Send    |

| Universal As |                        |                 |                 | ersal Asyn               | chronou     | Is Receive     | r Transmitter 3        |

| U3RX         | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART3 Receive          |

| U3TX         | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART3 Transmit         |

| U3CTS        | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | UART3 Clear to Send    |

| U3RTS        | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART3 Ready to Send    |

|              |                        |                 | Unive           | ersal Asyn               | chronou     | Is Receive     | r Transmitter 4        |

| U4RX         | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART4 Receive          |

| U4TX         | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART4 Transmit         |

| U4CTS        | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | UART4 Clear to Send    |

| U4RTS        | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART4 Ready to Send    |

|              |                        |                 | Unive           | ersal Asyn               | chronou     | Is Receive     | r Transmitter 5        |

| U5RX         | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART5 Receive          |

| U5TX         | PPS                    | PPS             | PPS             | PPS                      | 0           |                | UART5 Transmit         |

| U5CTS        | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART5 Clear to Send    |

| U5RTS        | PPS                    | PPS             | PPS             | PPS                      | 0           | —              | UART5 Ready to Send    |

|              |                        | •               | Unive           | ersal Asyn               | chronou     | s Receive      | r Transmitter 6        |

| U6RX         | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART6 Receive          |

| U6TX         | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART6 Transmit         |

| U6CTS        | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART6 Clear to Send    |

| U6RTS        | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART6 Ready to Send    |

| Legend: (    | CMOS = CI              | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power |

#### **TABLE 1-8: UART1 THROUGH UART6 PINOUT I/O DESCRIPTIONS**

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select

I = Input

© 2013-2016 Microchip Technology Inc.

| IAB                         | LE 7-3:                         | 11                                                                                                       | NIERR          |       | EGISTE | R MAP | (CONTI | NUED) |      |                |        |      |      |      |      |      |       |        |            |

|-----------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------|----------------|-------|--------|-------|--------|-------|------|----------------|--------|------|------|------|------|------|-------|--------|------------|

| ess.                        |                                 | ۵                                                                                                        |                |       |        |       |        |       |      | В              | its    |      |      |      |      |      |       |        | s          |

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                                                                                | 31/15          | 30/14 | 29/13  | 28/12 | 27/11  | 26/10 | 25/9 | 24/8           | 23/7   | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

| 05E0                        | OFF040                          | 31:16                                                                                                    | _              | —     | —      | —     | _      | —     |      | —              | —      | _    | _    | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0020                        | 011040                          | 15:0                                                                                                     |                |       |        | •     |        |       |      | VOFF<15:1      | >      |      |      |      |      |      |       | —      | 0000       |

| 05E4                        | OFF041                          | 31:16                                                                                                    | —              | —     | —      | —     | —      | —     | —    | —              | —      | —    | —    | —    | —    | —    | VOFF< | 1      | 0000       |

|                             |                                 | 15:0                                                                                                     |                |       | 1      |       |        |       |      | VOFF<15:1      | >      |      |      |      |      |      |       |        | 0000       |

| 05E8                        | OFF042                          | 31:16                                                                                                    |                |       | —      | —     | —      | —     | _    | —              | _      |      | _    | —    |      | _    | VOFF< |        | 0000       |

|                             |                                 | 15:0 VOFF<15:1>                                                                                          |                |       |        |       |        |       |      |                |        | 0000 |      |      |      |      |       |        |            |

| 05EC                        | OFF043                          | 31:16     -     -     -     -     -     -     VOFF     0000       15:0     VOFF     15:1>     -     0000 |                |       |        |       |        |       |      |                |        |      |      |      |      |      |       |        |            |

|                             |                                 | 31:16                                                                                                    |                |       |        |       |        | _     |      | VUFF<15.1      | >      | _    |      |      |      |      | VOFF< | 17:16  | 0000       |

| 05F0                        | OFF044                          | 15:0                                                                                                     |                |       |        |       |        |       |      | VOFF<15:1      | 、<br>、 |      |      |      |      |      | VOITS |        | 0000       |

|                             |                                 | 31:16                                                                                                    | _              |       |        | _     | _      |       |      | _              |        | _    | _    | _    | _    | _    | VOFF< |        | 0000       |

| 05F8                        | OFF046                          | 15:0                                                                                                     |                |       |        |       |        |       |      | VOFF<15:1      | >      |      |      |      |      |      |       | _      | 0000       |

|                             |                                 | 31:16                                                                                                    | _              | _     | _      | _     | _      | _     | _    | _              | _      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 05FC                        | OFF047                          | 15:0                                                                                                     |                |       |        |       |        |       |      | VOFF<15:1      | >      |      |      |      |      |      |       | —      | 0000       |

| 0600                        | OFF048                          | 31:16                                                                                                    | _              | _     | _      | —     | —      | _     | —    | _              | _      | _    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0600                        | OFF046                          | 15:0                                                                                                     |                |       |        |       |        |       |      | VOFF<15:1      | >      |      |      |      |      |      |       | _      | 0000       |

| 0604                        | OFF049                          | 31:16                                                                                                    | _              | —     | _      | —     | _      | —     | _    | —              | _      | —    | _    | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0004                        | 011043                          | 15:0                                                                                                     |                |       |        |       |        |       |      | VOFF<15:1      | >      |      |      |      |      |      |       | —      | 0000       |

| 0608                        | OFF050                          | 31:16                                                                                                    | —              | —     | -      | —     | —      | —     | —    | —              | —      | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

|                             | 011000                          | 15:0                                                                                                     |                |       | 1      |       |        |       |      | VOFF<15:1      | >      |      |      |      |      |      | 1     | —      | 0000       |

| 060C                        | OFF051                          | 31:16                                                                                                    |                |       | _      | —     | _      | _     | —    | —              | —      | —    | _    | —    | —    | —    | VOFF< |        | 0000       |

|                             |                                 | 15:0                                                                                                     |                |       |        |       |        |       |      | VOFF<15:1      | >      |      |      |      |      |      |       | —      | 0000       |

| 0610                        | OFF052                          | 31:16                                                                                                    | —              |       | _      | —     | —      | —     | _    | —              | —      | —    | _    | _    | —    | —    | VOFF< |        | 0000       |

|                             |                                 | 15:0<br>31:16                                                                                            |                | _     | _      | _     | _      | _     | _    | VOFF<15:1      | >      |      |      | _    |      |      | VOFF< | -      | 0000       |

| 0614                        | OFF053                          | 15:0                                                                                                     | _              |       |        |       |        |       |      | —<br>VOFF<15:1 |        |      | _    |      | _    | _    | VUFF< | -      | 0000       |

|                             |                                 | 31:16                                                                                                    |                |       |        | _     | _      | _     | _    | VUFF<15.1      |        |      |      |      |      |      | VOFF< |        | 0000       |

| 0618                        | OFF054                          | 15:0                                                                                                     |                |       |        |       |        |       |      |                | >      |      |      |      |      |      |       |        | 0000       |

|                             |                                 | 31:16                                                                                                    |                |       |        |       |        | _     |      | _              |        |      | _    |      |      |      | VOFF< | 17:16> | 0000       |

| 061C                        | OFF055                          | 15:0                                                                                                     |                |       |        |       |        |       |      | VOFF<15:1      | >      |      |      |      |      |      |       | _      | 0000       |

|                             |                                 |                                                                                                          | VOFF<15:1>0000 |       |        |       |        |       |      |                |        |      |      |      |      |      |       |        |            |

#### TARIE 7-3. INTEDDUDT DECISTED MAD (CONTINUED)

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Note 1: **Registers**" for more information.

2:

This bit or register is not available on 64-pin devices. This bit or register is not available on devices without a CAN module. 3:

This bit or register is not available on 100-pin devices. 4:

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

This bit or register is not available on devices without a Crypto module. 7:

8: This bit or register is not available on 124-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | 31:24 DATA<31:24> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23.10        | DATA<23:16>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15.6         | DATA<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   | DATA<7:0>         |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 11-12: USBFIFOX: USB FIFO DATA REGISTER 'x' ('x' = 0-7)

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 DATA<31:0>: USB Transmit/Receive FIFO Data bits

Writes to this register loads data into the TxFIFO for the corresponding endpoint. Reading from this register unloads data from the RxFIFO for the corresponding endpoint.

Transfers may be 8-bit, 16-bit or 32-bit as required, and any combination of access is allowed provided the data accessed is contiguous. However, all transfers associated with one packet must be of the same width so that data is consistently byte-, word- or double-word aligned. The last transfer may contain fewer bytes than the previous transfers in order to complete an odd-byte or odd-word transfer.

#### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 2

TSYNC: Timer External Clock Input Synchronization Selection bit

When TCS = 1:

1 = External clock input is synchronized

0 = External clock input is not synchronized

When TCS = 0:

When TCS = 0:

This bit is ignored.

bit 1

TCS: Timer Clock Source Select bit

- 1 = External clock from T1CKI pin 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                |  |  |  |

| 00.40        | U-0               |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | _                 | DASSERT           | DEVSE             | :L<1:0>           | LANEMO            | DDE<1:0>          | CMDINIT<1:0>     |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | TXRXCOUNT<15:8>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | TXRXCOU           | NT<7:0>           |                   |                  |                  |  |  |  |

#### REGISTER 20-4: SQI1CON: SQI CONTROL REGISTER

#### Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-23 Unimplemented: Read as '0'

#### bit 22 DASSERT: Chip Select Assert bit

1 = Chip Select is deasserted after transmission or reception of the specified number of bytes

0 = Chip Select is not deasserted after transmission or reception of the specified number of bytes

#### bit 21-20 DEVSEL<1:0>: SQI Device Select bits

- 11 = Reserved

- 10 = Reserved

- 01 = Select Device 1

- 00 = Select Device 0

#### bit 19-18 LANEMODE<1:0>: SQI Lane Mode Select bits

- 11 = Reserved

- 10 = Quad Lane mode

- 01 = Dual Lane mode

- 00 = Single Lane mode

#### bit 17-16 CMDINIT<1:0>: Command Initiation Mode Select bits

If it is Transmit, commands are initiated based on a write to the transmit register or the contents of TX FIFO. If CMDINIT is Receive, commands are initiated based on reads to the read register or RX FIFO availability.

- 11 = Reserved

- 10 = Receive

- 01 = Transmit

- 00 = Idle

#### bit 15-0 TXRXCOUNT<15:0>: Transmit/Receive Count bits

These bits specify the total number of bytes to transmit or received (based on CMDINIT)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | TXDATA<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | TXDATA<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | TXDATA<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | TXDATA            | <7:0>             |                   |                  |                  |  |  |  |

#### REGISTER 20-10: SQI1TXDATA: SQI TRANSMIT DATA BUFFER REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 TXDATA<31:0>: Transmit Command Data bits

Data is loaded into this register before being transmitted. Just prior to the beginning of a data transfer, the data in TXDATA is loaded into the shift register (SFDR).

Multiple writes to TXDATA can occur even while a transfer is already in progress. There can be a maximum of eight commands that can be queued.

#### REGISTER 20-11: SQI1RXDATA: SQI RECEIVE DATA BUFFER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24        | RXDATA<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22:46        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        | RXDATA<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         | RXDATA<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   |                   |                   | RXDATA            | <7:0>             |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 RXDATA<31:0>: Receive Data Buffer bits

At the end of a data transfer, the data in the shift register is loaded into the RXDATA register. This register works like a FIFO. The depth of the receive buffer is eight words. These bits indicate the starting write block address for an erase operation.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | —                 | —                 | —                 | —                 | —                | —                |

|              | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | -                 |                   | —                 | —                 | PKT<br>DONEISE    | BD<br>DONEISE    | CON<br>THRISE    |

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CON               | CON               | RX                | RX                | RX                | TX                | TX               | TX               |

|              | EMPTYISE          | FULLISE           | THRISE            | FULLISE           | EMPTYISE          | THRISE            | FULLISE          | EMPTYISE         |

#### REGISTER 20-22: SQI1INTSEN: SQI INTERRUPT SIGNAL ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bi

| R = Read  | able bit                                                                              | vv = vvritable bit            | U = Unimplemented    |

|-----------|---------------------------------------------------------------------------------------|-------------------------------|----------------------|

| -n = Valu | e at POR                                                                              | '1' = Bit is set              | '0' = Bit is cleared |

|           |                                                                                       |                               |                      |

| bit 31-11 | Unimplemented: Read a                                                                 | <b>s</b> '0'                  |                      |

| bit 10    | PKTDONEISE: Receive E                                                                 | Error Interrupt Signal Enab   | le bit               |

|           | 1 = Interrupt signal is ena                                                           |                               |                      |

|           | 0 = Interrupt signal is disa                                                          |                               |                      |

| bit 9     |                                                                                       | rror Interrupt Signal Enable  | e bit                |

|           | 1 = Interrupt signal is ena                                                           |                               |                      |

|           | 0 = Interrupt signal is disa                                                          |                               |                      |

| bit 8     |                                                                                       | ffer Threshold Interrupt Sig  | nal Enable bit       |

|           | 1 = Interrupt signal is ena                                                           |                               |                      |

|           | 0 = Interrupt signal is disa                                                          |                               |                      |

| bit 7     |                                                                                       | Buffer Empty Interrupt Sig    | nal Enable bit       |

|           | 1 = Interrupt signal is ena                                                           |                               |                      |

| bit 6     | 0 = Interrupt signal is disa                                                          |                               | nabla bit            |

| DILO      |                                                                                       | uffer Full Interrupt Signal E |                      |

|           | <ul> <li>1 = Interrupt signal is ena</li> <li>0 = Interrupt signal is disa</li> </ul> |                               |                      |

| bit 5     |                                                                                       | er Threshold Interrupt Sigr   | nal Enable bit       |

| bit 0     | 1 = Interrupt signal is ena                                                           |                               |                      |

|           | 0 = Interrupt signal is disa                                                          |                               |                      |

| bit 4     |                                                                                       | ffer Full Interrupt Signal Er | nable bit            |

|           | 1 = Interrupt signal is ena                                                           |                               |                      |

|           | 0 = Interrupt signal is disa                                                          |                               |                      |

| bit 3     | RXEMPTYISE: Receive E                                                                 | Buffer Empty Interrupt Sign   | al Enable bit        |

|           | 1 = Interrupt signal is ena                                                           | abled                         |                      |

|           | 0 = Interrupt signal is disa                                                          | abled                         |                      |

| bit 2     | TXTHRISE: Transmit Buff                                                               | er Threshold Interrupt Sig    | nal Enable bit       |

|           | 1 = Interrupt signal is ena                                                           |                               |                      |

|           | 0 = Interrupt signal is disa                                                          | abled                         |                      |

| bit 1     |                                                                                       | ffer Full Interrupt Signal E  | nable bit            |

|           | 1 = Interrupt signal is ena                                                           |                               |                      |

|           | 0 = Interrupt signal is disa                                                          |                               |                      |

| bit 0     |                                                                                       | Buffer Empty Interrupt Sigr   | nal Enable bit       |

|           | 1 = Interrupt signal is ena                                                           |                               |                      |

|           | 0 = Interrupt signal is disa                                                          | adied                         |                      |

|           |                                                                                       |                               |                      |

|           |                                                                                       |                               |                      |

|            | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1        | Bit<br>24/16/8/0 |

|------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------------|------------------|

| 04-04      | R/W-0                      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                   | R/W-0            |

| 31:24      |                            | FI                | LTRDLY<4:0        | >                 |                   | S                 | TRGSRC<4:               | 2>               |

| 00.46      | R/W-0                      | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0                   | R/W-0            |

| 23:16      | STRGSF                     | RC<1:0>           | —                 | —                 | —                 |                   | EIE<2:0> <sup>(1)</sup> |                  |

| 15:8       | R/W-0                      | U-0               | R/W-0             | U-0               | R/W-0             | U-0               | U-0                     | U-0              |

| 10.0       | ADCEN <sup>(2,4)</sup>     | —                 | ADSIDL            | —                 | FRACT             |                   | —                       | _                |

| 7:0        | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0              |

| 7.0        |                            |                   | _                 | —                 | —                 |                   | _                       | -                |

| Legend:    |                            |                   |                   |                   |                   |                   |                         |                  |

| R = Readal | ole bit                    | W = Writable      | bit               | U = Unimple       | mented bit, r     | ead as '0'        |                         |                  |

| -n = Value |                            | '1' = Bit is se   |                   | '0' = Bit is clo  |                   | x = Bit is unk    | nown                    |                  |

|            |                            |                   | 1.5 TAD           |                   |                   |                   |                         |                  |

|            | 00001 = Sar<br>00000 = Sar | -                 | .5 Tad            |                   |                   |                   |                         |                  |

00101 = TMR1 match 00100 = INTO 00011 = Reserved 00010 = Reserved 00001 = Global software trigger (GSWTRG) 00000 = No trigger

- The early interrupt feature should not be used if polling any of the ARDY bits to determine if the Note 1: conversion is complete. Early interrupts should be used only when all results from the ADC module are retrieved using an individual interrupt routine to fetch ADC results.

- The ADCEN bit should be set only after the ADC module has been configured. Changing ADC Configura-2: tion bits when ADCEN = 1, will result in unpredictable behavior. When ADCEN = 0, the ADC clocks are disabled, the internal control logic is reset, and all status flags used by the module are cleared. However, the SFRs are available for reading and writing.

- The rising edge of the module output signal triggers an ADC conversion. See Figure 18-1 in Section 18.0 3: "Output Compare" and Figure 31-1 in Section 31.0 "Comparator" for more information.

- See 28.1 "ADC Configuration Requirements" for detailed ADC calibration information. 4:

Note: The ADC module is not available for normal operations until the ADCRDY bit (AD1CON2<31>) is set.

#### REGISTER 28-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 21-19 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 18-16 | <b>EIE&lt;2:0&gt;:</b> Early Interrupt Enable bits <sup>(1)</sup><br>These bits select the number of clocks prior to the actual arrival of valid data when the associated<br>ARDYx bit is set. Since the ARDYx bit triggers an interrupt, these bits allow for early interrupt generation.<br>111 = The data ready bit, ARDYx, is set 7 TAD clocks prior to when the data is ready<br>100 = The data ready bit, ARDYx, is set 6 TAD clocks prior to when the data is ready<br>101 = The data ready bit, ARDYx, is set 5 TAD clocks prior to when the data is ready<br>100 = The data ready bit, ARDYx, is set 4 TAD clocks prior to when the data is ready<br>111 = The data ready bit, ARDYx, is set 3 TAD clocks prior to when the data is ready<br>112 = The data ready bit, ARDYx, is set 3 TAD clocks prior to when the data is ready<br>113 = The data ready bit, ARDYx, is set 2 TAD clocks prior to when the data is ready<br>114 = The data ready bit, ARDYx, is set 1 TAD clocks prior to when the data is ready<br>115 = The data ready bit, ARDYx, is set 1 TAD clock prior to when the data is ready<br>116 = The data ready bit, ARDYx, when the data is ready |

| bit 15    | ADCEN: ADC Operating Mode bit <sup>(2,4)</sup><br>1 = ADC module is enabled<br>0 = ADC module is off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 13    | ADSIDL: Stop in Idle Mode bit<br>1 = Discontinue module operation when device enters Idle mode<br>0 = Continue module operation in Idle mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| bit 12    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 11    | FRACT: Fractional Data Output Format bit<br>1 = Fractional<br>0 = Integer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 10-0  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Note 1:   | The early interrupt feature should not be used if polling any of the ARDY bits to determine if the conversion is complete. Early interrupts should be used only when all results from the ADC module are retrieved using an individual interrupt routine to fetch ADC results.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2:        | The ADCEN bit should be set only after the ADC module has been configured. Changing ADC Configura-<br>tion bits when $ADCEN = 1$ , will result in unpredictable behavior. When $ADCEN = 0$ , the ADC clocks are<br>disabled, the internal control logic is reset, and all status flags used by the module are cleared. However,<br>the SFRs are available for reading and writing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3:        | The rising edge of the module output signal triggers an ADC conversion. See Figure 18-1 in <b>Section 18.0</b><br>"Output Compare" and Figure 31-1 in <b>Section 31.0</b> "Comparator" for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4:        | See 28.1 "ADC Configuration Requirements" for detailed ADC calibration information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Note: The ADC module is not available for normal operations until the ADCRDY bit (AD1CON2<31>) is set.

#### REGISTER 28-4: AD1IMOD: ADC1 INPUT MODE CONTROL REGISTER (CONTINUED)

| bit 11-10 | <b>SH5MOD&lt;1:0&gt;:</b> Input Configuration for S&H 5 (SH5) Select bits<br>11 = Differential inputs, two's complement (signed) data output<br>10 = Differential inputs, unipolar encoded (unsigned) data output<br>01 = Single ended inputs, two's complement (signed) data output<br>00 = Single ended inputs, unipolar encoded (unsigned) data output |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 9-8   | <b>SH4MOD&lt;1:0&gt;:</b> Input Configuration for S&H 4 (SH4) Select bits<br>11 = Differential inputs, two's complement (signed) data output<br>10 = Differential inputs, unipolar encoded (unsigned) data output<br>01 = Single ended inputs, two's complement (signed) data output<br>00 = Single ended inputs, unipolar encoded (unsigned) data output |

| bit 7-6   | <b>SH3MOD&lt;1:0&gt;:</b> Input Configuration for S&H 3 (SH3) Select bits<br>11 = Differential inputs, two's complement (signed) data output<br>10 = Differential inputs, unipolar encoded (unsigned) data output<br>01 = Single ended inputs, two's complement (signed) data output<br>00 = Single ended inputs, unipolar encoded (unsigned) data output |

| bit 5-4   | <b>SH2MOD&lt;1:0&gt;:</b> Input Configuration for S&H 2 (SH2) Select bits<br>11 = Differential inputs, two's complement (signed) data output<br>10 = Differential inputs, unipolar encoded (unsigned) data output<br>01 = Single ended inputs, two's complement (signed) data output<br>00 = Single ended inputs, unipolar encoded (unsigned) data output |

| bit 3-2   | <b>SH1MOD&lt;1:0&gt;:</b> Input Configuration for S&H 1 (SH1) Select bits<br>11 = Differential inputs, two's complement (signed) data output<br>10 = Differential inputs, unipolar encoded (unsigned) data output<br>01 = Single ended inputs, two's complement (signed) data output<br>00 = Single ended inputs, unipolar encoded (unsigned) data output |

| bit 1-0   | <b>SHOMOD&lt;1:0&gt;:</b> Input Configuration for S&H 0 (SH0) Select bits<br>11 = Differential inputs, two's complement (signed) data output<br>10 = Differential inputs, unipolar encoded (unsigned) data output<br>01 = Single ended inputs, two's complement (signed) data output<br>00 = Single ended inputs, unipolar encoded (unsigned) data output |

- **Note 1:** Alternate inputs are only available for Class 1 Inputs.

- 2: When an alternate input is selected (SHxALT<1:0> ≠ 0), the data, status, and control registers for the default Class 1 input are still used. Selecting an alternate input changes the physical input source only.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31.24     | DATA<31:24>       |                   |                   |                   |                   |                   |                  |                  |

| 23:16     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23.10     | DATA<23:16>       |                   |                   |                   |                   |                   |                  |                  |

| 15:8      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.0      | DATA<15:8>        |                   |                   |                   |                   |                   |                  |                  |

| 7:0       | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0       |                   |                   |                   | DATA              | <7:0>             |                   |                  |                  |

#### **REGISTER 28-18:** AD1DATAn: ADC1 DATA OUTPUT REGISTER ('n' = 0 through 44)

| I | Legend:          |                  |                          |                    |

|---|------------------|------------------|--------------------------|--------------------|

| F | R = Readable bit | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| - | n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 **DATA<31:0>:** Data Output Value bits (formatted as specified by the SHxMOD<1:0> bits for the associated S&H circuits and the FRACT bit)

Note: AD1DATAn = ANx, where 'x' and 'n' =0-42, AD1DATA 43 = IVREF, and AD1DATA44 = IVTEMP.

# 34.3 On-Chip Voltage Regulator

The core and digital logic for all PIC32MZ EC devices is designed to operate at a nominal 1.8V. To simplify system designs, devices in the PIC32MZ EC family incorporate an on-chip regulator providing the required core logic voltage from VDD.

#### 34.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

#### 34.3.2 ON-CHIP REGULATOR AND BOR

PIC32MZ EC devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 37.1** "**DC Characteristics**".

#### 34.4 On-chip Temperature Sensor

PIC32MZ EC devices include a temperature sensor that provides accurate measurement of a device's junction temperature (see Section 37.2 "AC Characteristics and Timing Parameters" for more information).

The temperature sensor is connected to the ADC module and can be measured using the shared S&H circuit (see Section 28.0 "Pipelined Analog-to-Digital Converter (ADC)" for more information).

# 34.5 Programming and Diagnostics

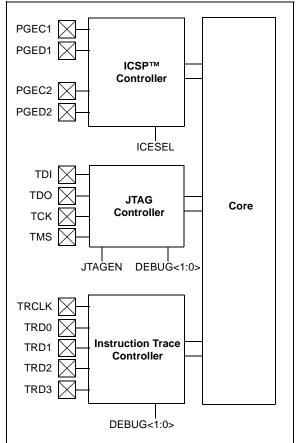

PIC32MZ EC devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

#### FIGURE 34-1:

#### BLOCK DIAGRAM OF PROGRAMMING, DEBUGGING AND TRACE PORTS

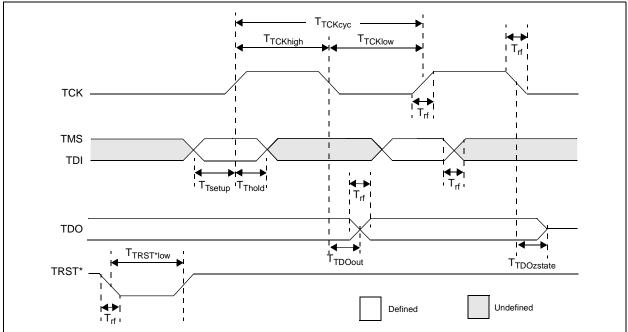

#### FIGURE 37-30: EJTAG TIMING CHARACTERISTICS

#### TABLE 37-48: EJTAG TIMING REQUIREMENTS

| АС СНА        | AC CHARACTERISTICS |                                                  |      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industria |       |            |  |

|---------------|--------------------|--------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|--|

| Param.<br>No. | Symbol             | Description <sup>(1)</sup>                       | Min. | Max.                                                                                                                                             | Units | Conditions |  |