Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 78                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048ech100t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.7 microAptiv<sup>™</sup> Core Configuration

Register 3-1 through Register 3-4 show the default configuration of the microAptiv core, which is included on PIC32MZ EC family devices.

| INE OISTE    |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

| 04.04        | r-1               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |  |  |  |  |  |

| 31:24        |                   | —                 | _                 | _                 | —                 |                   | _                | ISP              |  |  |  |  |  |

| 00.40        | R-0               | R-0               | R-1               | R-0               | U-0               | R-1               | R-0              | R-0              |  |  |  |  |  |

| 23:16        | DSP               | UDI               | SB                | MDU               | —                 | MM<               | BM               |                  |  |  |  |  |  |

| 15.0         | R-0 R-0           |                   | R-0               | R-0 R-0           |                   | R-1 R-0           |                  | R-0              |  |  |  |  |  |

| 15:8         | BE                | AT<               | 1:0>              |                   | AR<2:0>           |                   | <2:1>            |                  |  |  |  |  |  |

| 7.0          | R-1               | U-0               | U-0               | U-0 U-0           |                   | R/W-0             | R/W-1            | R/W-0            |  |  |  |  |  |

| 7:0          | MT<0>             | —                 | _                 | _                 | —                 |                   | K0<2:0>          |                  |  |  |  |  |  |

#### REGISTER 3-1: CONFIG: CONFIGURATION REGISTER; CP0 REGISTER 16, SELECT 0

| Legend:           | r = Reserved bit |                           |                    |  |  |  |

|-------------------|------------------|---------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |

Reserved: This bit is hardwired to '1' to indicate the presence of the Config1 register.

| bit 30-25 | Unimplemented: Read as '0'                                                                                                          |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 24    | <b>ISP:</b> Instruction Scratch Pad RAM bit<br>0 = Instruction Scratch Pad RAM is not implemented                                   |

| bit 23    | <b>DSP:</b> Data Scratch Pad RAM bit<br>0 = Data Scratch Pad RAM is not implemented                                                 |

| bit 22    | <b>UDI:</b> User-defined bit<br>0 = CorExtend User-Defined Instructions are not implemented                                         |

| bit 21    | <b>SB:</b> SimpleBE bit<br>1 = Only Simple Byte Enables are allowed on the internal bus interface                                   |

| bit 20    | <b>MDU:</b> Multiply/Divide Unit bit<br>0 = Fast, high-performance MDU                                                              |

| bit 19    | Unimplemented: Read as '0'                                                                                                          |

| bit 18-17 | MM<1:0>: Merge Mode bits<br>10 = Merging is allowed                                                                                 |

| bit 16    | <b>BM:</b> Burst Mode bit<br>0 = Burst order is sequential                                                                          |

| bit 15    | <b>BE:</b> Endian Mode bit<br>0 = Little-endian                                                                                     |

| bit 14-13 | AT<1:0>: Architecture Type bits<br>00 = MIPS32                                                                                      |

| bit 12-10 | AR<2:0>: Architecture Revision Level bits<br>001 = MIPS32 Release 2                                                                 |

| bit 9-7   | MT<2:0>: MMU Type bits<br>001 = microAptiv MPU Microprocessor core uses a TLB-based MMU                                             |

| bit 6-3   | Unimplemented: Read as '0'                                                                                                          |

| bit 2-0   | <b>K0&lt;2:0&gt;:</b> Kseg0 Coherency Algorithm bits<br>011 = Cacheable, non-coherent, write-back, write allocate<br>010 = Uncached |

000 = Cacheable, non-coherent, write-through, no write allocate

All other values are not used and are mapped to other values. Values 100, 101, and 110 are mapped to 010. Value 111 is mapped to 010.

bit 31

## FIGURE 4-4: MEMORY MAP FOR DEVICES WITH 2048 KB OF PROGRAM MEMORY<sup>(1,2)</sup>

|                          | Virtual<br>Memory Map          |                                     | Physical<br>Memory Map     |                          |

|--------------------------|--------------------------------|-------------------------------------|----------------------------|--------------------------|

| 0xFFFFFFF                | Reserved                       |                                     | Reserved                   | 0xFFFFFFF                |

| 0xF4000000               | <b>F</b>                       |                                     |                            |                          |

| 0xF3FFFFFF<br>0xF0000000 | External Memory via<br>SQI     | (not cacheable)                     |                            | 0x34000000               |

| 02F000000                | 50                             |                                     |                            | 0x34000000<br>0x33FFFFFF |

| 0xE4000000               | Reserved                       |                                     | External Memory via        | 0,00111111               |

| 0xE3FFFFF                | External Memory via            | Ê                                   | SQI                        | 0x30000000               |

| 0xE0000000               | EBI                            |                                     |                            |                          |

|                          |                                |                                     | Reserved                   | 0x24000000               |

| 0xD4000000               | Reserved                       |                                     |                            | 0x23FFFFFF               |

| 0xD3FFFFF                | External Memory via            | e e                                 | External Memory via<br>EBI |                          |

| 0xD0000000               | SQI                            | as (                                | LDI                        | 0x20000000               |

|                          | Reserved                       | KSEG2 <sup>(4)</sup><br>(cacheable) | Reserved                   |                          |

| 0xC4000000               |                                | Ϋ́                                  | noconvou                   | 0x1FC74000               |

| 0xC3FFFFF                | External Memory via            |                                     | Boot Flash                 | 0x1FC73FFF               |

| 0xC0000000               | EBI                            |                                     | (see Figure 4-5)           |                          |

| 0xBFFFFFF                | Reserved                       |                                     |                            | 0x1FC00000               |

| 0xBFC74000<br>0xBFC73FFF |                                | 4                                   | Reserved                   | 0x1F900000               |

| UXBFC/3FFF               | Boot Flash                     |                                     |                            | 0x1F8FFFF                |

| 0xBFC00000               | (see Figure 4-5)               |                                     | SFRs                       |                          |

|                          |                                |                                     | (see Table 4-1)            | 0x1F800000               |

| 0xBF900000               | Reserved                       |                                     |                            |                          |

| 0xBF8FFFFF               |                                |                                     | Reserved                   |                          |

|                          | SFRs                           |                                     |                            | 0x1D200000               |

| 0xBF800000               | (see Table 4-1)                | head                                |                            | 0x1D1FFFFF               |

|                          | Deserved                       | KSEG                                | Program Flash              |                          |

| 0xBD200000               | Reserved                       | KSEG<br>(not cacheable)             |                            | 0x1D000000               |

| 0xBD1FFFFF               |                                | 「 E                                 | Reserved                   |                          |

|                          | Program Flash                  |                                     | Reserved                   | 0x00080000               |

| 0xBD000000               |                                |                                     | RAM <sup>(3)</sup>         | 0x0007FFF                |

| 01.0000000               | Reserved                       |                                     |                            | 0x0000000                |

| 0xA0080000               |                                |                                     |                            |                          |

| 0xA007FFFF               | RAM <sup>(3)</sup>             |                                     |                            |                          |

| 0xA000000                |                                |                                     |                            |                          |

| 024000000                |                                | $\leq$                              |                            |                          |

| 0x9FC74000               | Reserved                       |                                     |                            |                          |

| 0x9FC73FFF               |                                | 1   /                               |                            |                          |

|                          | Boot Flash<br>(see Figure 4-5) |                                     |                            |                          |

| 0x9FC00000               | (See Figure 4-5)               |                                     |                            |                          |

|                          |                                |                                     |                            |                          |

|                          | Reserved                       | 0<br>ple)                           |                            |                          |

| 0x9D200000               |                                | KSEG0<br>(cacheable)                |                            |                          |

| 0x9D1FFFF                |                                | act                                 |                            |                          |

|                          | Program Flash                  | 9                                   |                            |                          |

| 0x9D000000               |                                |                                     |                            |                          |

| 0.480080000              | Reserved                       |                                     |                            |                          |

| 0x80080000<br>0x8007FFFF |                                | -                                   |                            |                          |

| 0000071111               | RAM <sup>(3)</sup>             |                                     |                            |                          |

| 0x80000000               | TO UN                          |                                     |                            |                          |

| 0x00000000               | Reserved                       |                                     |                            |                          |

|                          |                                | <b>_</b>                            |                            |                          |

|                          | Memory areas are not s         |                                     |                            |                          |

|                          |                                | TLB are initialized by compil       |                            |                          |

|                          | -                              | d into two equal banks: RAM         |                            | -                        |

| 4:                       | I ne MMU must be ena           | bled and the TLB must be se         | et up to access this segme | ent.                     |

|                          |                                |                                     |                            |                          |

|                          |                                |                                     |                            |                          |

| Bit<br>Range | Bit Bit<br>e 31/23/15/7 30/22/14/6 |       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|------------------------------------|-------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0                                | U-0   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                                  | —     | —                 | —                 |                   | _                 | —                | —                |  |

| 22.46        | U-0                                | U-0   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                                  | —     | —                 | —                 |                   | _                 | —                | —                |  |

| 45.0         | U-0                                | U-0   | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         | —                                  | —     | T13PGV            | T12PGV            | T11PGV            | T10PGV            | T9PGV            | T8PGV            |  |

| 7.0          | R-0                                | R-0   | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | T7PGV                              | T6PGV | T5PGV             | T4PGV             | T3PGV             | T2PGV             | T1PGV            | <b>T0PGV</b>     |  |

#### **REGISTER 4-2:** SBFLAG: SYSTEM BUS STATUS FLAG REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-14 Unimplemented: Read as '0'

bit 13-0 **TxPGV:** Target 'x' Permission Group Violation Status bits ('x' = 0-13)

Refer to Table 4-6 for the list of available targets and their descriptions.

- 1 = Target is reporting a Permission Group (PG) violation

- 0 = Target is not reporting a PG violation

Note: All errors are cleared at the source (i.e., SBTxELOG1, SBTxELOG2, SBTxECLRS, or SBTxECLRM registers).

|              |                   | $(\mathbf{X} = 0 - 13)$ |     |     |                   |                   |                  |                  |

|--------------|-------------------|-------------------------|-----|-----|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       |     |     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0                     | U-0 | U-0 | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                       | _   | —   | —                 | _                 | —                | —                |

| 00.40        | U-0               | U-0                     | U-0 | U-0 | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                       |     | _   | —                 | _                 |                  | —                |

| 45.0         | U-0               | U-0                     | U-0 | U-0 | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                       | _   | _   | —                 | _                 | -                | —                |

| 7.0          | U-0               | U-0                     | U-0 | U-0 | U-0               | U-0 U-0           |                  | R-0              |

| 7:0          |                   | _                       |     |     | _                 | _                 |                  | CLEAR            |

|              |                   |                         |     |     |                   |                   |                  |                  |

## REGISTER 4-6: SBTxECLRS: SYSTEM BUS TARGET 'x' SINGLE ERROR CLEAR REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-1 Unimplemented: Read as '0'

bit 0 CLEAR: Clear Single Error on Read bit A single error as reported via SBTxELOG1 and SBTxELOG2 is cleared by a read of this register.

**Note:** Refer to Table 4-6 for the list of available targets and their descriptions.

#### REGISTER 4-7: SBTxECLRM: SYSTEM BUS TARGET 'x' MULTIPLE ERROR CLEAR REGISTER ('x' = 0-13)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 |                   |                   | _                 | _                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 |                   |                   | _                 |                   | —                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 7:0          |                   |                   |                   |                   |                   |                   |                  | CLEAR            |

#### Legend:

| _ogonan           |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-1 Unimplemented: Read as '0'

bit 0 CLEAR: Clear Multiple Errors on Read bit Multiple errors as reported via SBTxELOG1 and SBTxELOG2 is cleared by a read of this register.

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

© 2013-2016 Microchip Technology Inc.

NOTES:

|                             | BLE 7-3:                        | II            | NIERR |       | EGISTE |       | (CONTI | NUED) |                |                |          |      |      |      |      |      |        |       |            |

|-----------------------------|---------------------------------|---------------|-------|-------|--------|-------|--------|-------|----------------|----------------|----------|------|------|------|------|------|--------|-------|------------|

| ess                         | _                               | æ             |       |       |        |       |        |       |                | В              | its      |      |      |      |      |      |        |       | s          |

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13  | 28/12 | 27/11  | 26/10 | 25/9           | 24/8           | 23/7     | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0  | All Resets |

| 0660                        | OFF072                          | 31:16         | _     | _     | —      | —     | _      | —     | _              | —              |          |      | —    | —    | _    |      | VOFF<1 | 7:16> | 0000       |

| 0000                        | 011072                          | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0664                        | OFF073                          | 31:16         | _     | _     | —      | —     | _      |       | —              | —              | _        | _    | —    | —    | —    | _    | VOFF<1 |       | 0000       |

|                             |                                 | 15:0          |       |       | 1      |       |        |       |                | VOFF<15:1      |          |      |      |      |      |      |        |       | 0000       |

| 0668                        | OFF074                          | 31:16         | —     | —     | _      | —     | _      | —     | —              | -              | _        | _    | _    | —    |      | _    | VOFF<1 | 7:16> | 0000       |

|                             |                                 | 15:0          |       |       | 1      | 1     |        | i     |                | VOFF<15:1      | >        | i    | i    | i    | i    |      | VOFF<1 |       | 0000       |

| 066C                        | OFF075                          | 31:16<br>15:0 | —     |       | _      | _     |        | —     | —              |                |          |      | _    | _    |      | _    | VUFF<1 | 7:16> | 0000       |

|                             |                                 | 31:16         | _     |       |        |       |        | _     | _              | VUFF<15.1      | <u> </u> |      |      |      |      | _    | VOFF<1 | 7:16> | 0000       |

| 0670                        | OFF076                          | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      |          |      |      |      |      |      | VOITS  |       | 0000       |

|                             | (1)                             | 31:16         | _     | _     | _      |       | _      | _     | _              | _              | _        | _    | _    | _    | _    |      | VOFF<1 |       | 0000       |

| 0674                        | OFF077 <sup>(2)</sup>           | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | -     | 0000       |

|                             | . (2)                           | 31:16         | _     | _     | _      | _     | _      | _     | _              | _              | _        | _    | _    | _    | _    | _    | VOFF<1 | 7:16> | 0000       |

| 0678                        | OFF078 <sup>(2)</sup>           | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0670                        | OFF079 <sup>(2)</sup>           | 31:16         | _     | _     | —      | _     | —      | —     | —              | _              | _        | _    | —    | —    | _    | _    | VOFF<1 | 7:16> | 0000       |

| 067C                        | OFF0/9 /                        | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0680                        | OFF080 <sup>(2)</sup>           | 31:16         | _     | _     | —      | —     | _      | —     | —              | —              | _        | —    | —    | —    | —    | _    | VOFF<1 | 7:16> | 0000       |

| 0000                        | 011000                          | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0684                        | OFF081 <sup>(2)</sup>           | 31:16         | —     | —     | —      | —     | —      | —     | —              | —              | _        | —    | —    | —    | —    | —    | VOFF<1 | 7:16> | 0000       |

|                             | 0.1.001                         | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0688                        | OFF082 <sup>(2)</sup>           | 31:16         | —     | —     | —      | —     | —      | —     | _              | —              |          | —    | _    | —    | _    |      | VOFF<1 | 7:16> | 0000       |

|                             |                                 | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      |          |      |      |      |      |      |        | _     | 0000       |

| 068C                        | OFF083 <sup>(2)</sup>           | 31:16         | —     | —     | —      | —     | —      | —     | _              |                | _        | _    | —    | —    | —    |      | VOFF<1 |       | 0000       |

|                             |                                 | 15:0<br>31:16 | _     | _     | _      |       |        |       |                | VOFF<15:1      |          |      | _    | _    | _    |      | VOFF<1 |       | 0000       |

| 0690                        | OFF084 <sup>(2)</sup>           | 15:0          | _     |       | _      | —     | _      | —     | —              | —<br>VOFF<15:1 | _        | _    |      |      |      |      | V0FF<1 |       | 0000       |

|                             |                                 | 31:16         |       |       |        |       | _      | _     | _              | VUFF<15.1      | <u> </u> |      |      |      |      |      | VOFF<1 |       | 0000       |

| 0694                        | OFF085 <sup>(2)</sup>           | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      |          |      |      | 1    |      |      | 0.10   |       | 0000       |

|                             |                                 | 31:16         | _     | —     | _      | —     | _      | _     | _              | _              |          |      | _    | —    | —    | _    | VOFF<1 | 7:16> | 0000       |

| 0698                        | OFF086 <sup>(2)</sup>           | 15:0          |       |       |        |       |        | 1     |                | VOFF<15:1      |          | 1    |      | 1    | 1    |      |        | _     | 0000       |

|                             | l                               |               |       |       |        |       |        |       | in have de sin |                |          |      |      |      |      |      |        |       |            |

#### TARIE 7-3. INTEDDUDT DECISTED MAD (CONTINUED)

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV **Registers**" for more information.

2:

This bit or register is not available on 64-pin devices. This bit or register is not available on devices without a CAN module. 3:

This bit or register is not available on 100-pin devices. 4:

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

This bit or register is not available on devices without a Crypto module. 7:

This bit or register is not available on 124-pin devices. 8:

#### REGISTER 10-7: DCHxCON: DMA CHANNEL x CONTROL REGISTER (CONTINUED)

- bit 4 **CHAEN:** Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete 0 = Channel is disabled on block transfer complete

#### bit 3 Unimplemented: Read as '0'

- bit 2 **CHEDET:** Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | —                 | —                 | —                 | _                 | _                | —                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45-0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | _                 | _                 | —                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

#### REGISTER 10-9: DCHxINT: DMA CHANNEL x INTERRUPT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

| bit 23   | <b>CHSDIE:</b> Channel Source Done Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                       |

|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| bit 22   | <b>CHSHIE:</b> Channel Source Half Empty Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                 |

| bit 21   | <b>CHDDIE:</b> Channel Destination Done Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                  |

| bit 20   | <b>CHDHIE:</b> Channel Destination Half Full Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled             |

| bit 19   | <b>CHBCIE:</b> Channel Block Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

| bit 18   | <b>CHCCIE:</b> Channel Cell Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

| bit 17   | CHTAIE: Channel Transfer Abort Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                           |

| bit 16   | <b>CHERIE:</b> Channel Address Error Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                     |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                             |

| bit 7    | CHSDIF: Channel Source Done Interrupt Flag bit                                                                                         |

|          | <ul> <li>1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)</li> <li>0 = No interrupt is pending</li> </ul>        |

| bit 6    | CHSHIF: Channel Source Half Empty Interrupt Flag bit                                                                                   |

|          | <ul> <li>1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul> |

|          |                                                                                                                                        |

### 12.1 Parallel I/O (PIO) Ports

All port pins have ten registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

#### 12.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

Refer to the pin name tables (Table 2 through Table 5) for the available pins and their functionality.

# 12.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 12.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be an NOP.

#### 12.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MZ EC devices to generate interrupt requests to the processor in response to a change-ofstate on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on change           |

|-------|---------------------------------------------|

|       | notification pins should always be          |

|       | disabled when the port pin is configured as |

|       | a digital output.                           |

An additional control register (CNCONx) is shown in Register 12-3.

#### 12.2 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

#### TABLE 12-11: PORTE REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |       |       |      | E    | Bits         |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0400                        | ANSELE                          | 31:16     | —     | —     | _     | _     | —     |       | —    | —    |              | —            | _            | _            | —            | —            | —            | —            | 0000          |

| 0400                        | ANGELE                          | 15:0      |       | -     |       | -     | _     |       | —    | —    | ANSE7        | ANSE6        | ANSE5        | ANSE4        | —            | —            | —            | —            | 00F0          |

| 0410                        | TRISE                           | 31:16     | -     | -     | _     | -     | —     | _     | _    | _    | _            | —            | -            | -            | _            | _            | _            | _            | 0000          |

| 0410                        | TRISE                           | 15:0      | -     | -     | _     |       | _     |       | _    | _    | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | OOFF          |

| 0420                        | PORTE                           | 31:16     |       |       | _     |       | _     |       | _    | _    |              | _            |              |              | -            | _            | _            | _            | 0000          |

| 0420                        | PORTE                           | 15:0      |       |       | _     | —     | _     | —     | —    | —    | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | xxxx          |

| 0430                        | LATE                            | 31:16     |       |       | _     |       | _     |       | _    | _    |              | _            |              |              | -            | _            | _            | _            | 0000          |

| 0430                        | LAIL                            | 15:0      | -     | -     | _     |       | _     |       | -    | _    | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | xxxx          |

| 0440                        | ODCE                            | 31:16     | -     | -     | _     |       | _     |       | -    | _    | _            | _            |              |              | _            | _            | _            | -            | 0000          |

| 0440                        | ODCL                            | 15:0      | -     | -     | _     |       | _     |       | -    | _    | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | 0000          |

| 0450                        | CNPUE                           | 31:16     | _     | _     | _     |       | —     |       | _    | _    | _            | -            |              |              | —            |              | _            | -            | 0000          |

| 0430                        |                                 | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPUE3       | CNPUE2       | CNPUE1       | CNPUE0       | 0000          |

| 0460                        | CNPDE                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0400                        |                                 | 15:0      | —     | —     | —     | —     | —     | -     | —    | —    | CNPDE7       | CNPDE6       | CNPDE5       | CNPDE4       | CNPDE3       | CNPDE2       | CNPDE1       | CNPDE0       | 0000          |

| 0470                        | CNCONE                          | 31:16     | —     | —     | —     | —     | —     | -     | —    | —    | —            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0470                        | CINCOINE                        | 15:0      | ON    | —     | SIDL  | —     | —     | -     | —    | —    | —            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0480                        | CNENE                           | 31:16     | —     | —     | —     | —     | —     | -     | —    | —    | —            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0400                        | CINEME                          | 15:0      | —     | —     | —     | —     | —     | -     | —    | —    | CNIEE7       | CNIEE6       | CNIEE5       | CNIEE4       | CNIEE3       | CNIEE2       | CNIEE1       | CNIEE0       | 0000          |

|                             |                                 | 31:16     | _     | _     | _     |       | —     |       | —    | —    | —            | -            |              | 1            | —            | —            | —            | —            | 0000          |

| 0490                        | CNSTATE                         | 15:0      | _     | _     | _     | -     | _     | _     | _    | _    | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | 0000          |

Legend: x = Unknown value on Reset; -- = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

The timer source for each Output Compare module depends on the setting of the OCACLK bit in the CFGCON register. The available configurations are shown in Table 18-1.

| TABLE 18-1: | TIMER SOURCE   |

|-------------|----------------|

|             | CONFIGURATIONS |

| Output<br>Compare<br>Module | Timerx                   | Timery       |

|-----------------------------|--------------------------|--------------|

| OCACLK (CFGC                | <b>ON&lt;16&gt;) =</b> 0 |              |

| OC1                         | Timer2                   | Timer3       |

| •                           | •                        | •            |

| •                           | •                        | •            |

| OC9                         | •<br>Timer 2             | •<br>Timer 3 |

| OCACLK (CFGC                | ON<16>) = 1              |              |

| OC1                         | Timer4                   | Timer5       |

| OC2                         | Timer4                   | Timer5       |

| OC3                         | Timer4                   | Timer5       |

| OC4                         | Timer2                   | Timer3       |

| OC5                         | Timer2                   | Timer3       |

| OC6                         | Timer2                   | Timer3       |

| OC7                         | Timer6                   | Timer7       |

| OC8                         | Timer6                   | Timer7       |

| OC9                         | Timer6                   | Timer7       |

#### 25.1 RTCC Control Registers

#### TABLE 25-1: RTCC REGISTER MAP

| ess                         |                                 | 6         |        |       |           |          |       |                   |          |        | Bits     |          |            |         |         |         |            |       | s          |

|-----------------------------|---------------------------------|-----------|--------|-------|-----------|----------|-------|-------------------|----------|--------|----------|----------|------------|---------|---------|---------|------------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13     | 28/12    | 27/11 | 26/10             | 25/9     | 24/8   | 23/7     | 22/6     | 21/5       | 20/4    | 19/3    | 18/2    | 17/1       | 16/0  | All Resets |

| 0C00                        | RTCCON                          | 31:16     | _      | —     | —         | —        |       |                   |          |        |          |          | CAL        | <9:0>   |         |         |            |       | 0000       |

| 0000                        | RICCON                          | 15:0      | ON     |       | SIDL      | —        | —     | RTCCLK            | SEL<1:0> | RTCOUT | SEL<1:0> | RTCCLKON |            | —       | RTCWREN | RTCSYNC | HALFSEC    | RTCOE | 0000       |

| 0010                        | RTCALRM                         | 31:16     | -      | _     | _         | —        | —     | _                 | _        | _      | -        | _        | _          | _       | -       |         | —          | _     | 0000       |

| 0010                        | RICALINI                        | 15:0      | ALRMEN | CHIME | PIV       | ALRMSYNC |       | AMASI             | <<3:0>   |        |          |          |            | ARPT    | <7:0>   |         |            |       | 0000       |

| 0000                        | RTCTIME                         | 31:16     | -      |       | HR1       | 0<1:0>   |       | HR01              | <3:0>    |        | —        | N        | 1IN10<2:0> |         |         | MIN01   | <3:0>      |       | xxxx       |

| 0020                        | RICTIME                         | 15:0      | _      |       | SEC10<2:0 | )>       |       | SEC0 <sup>2</sup> | <3:0>    |        | _        | _        | _          | _       | _       | _       | —          | _     | xx00       |

| 0000                        |                                 | 31:16     |        | YEAR  | 10<3:0>   |          |       | YEAR0             | 1<3:0>   |        | _        | _        | _          | MONTH10 |         | MONTH   | 01<3:0>    |       | xxxx       |

| 0030                        | RTCDATE                         | 15:0      | _      | _     | DAY1      | 0<1:0>   |       | DAY0'             | <3:0>    |        | _        | _        | _          | _       | _       | W       | /DAY01<2:0 | >     | xx00       |

|                             |                                 | 31:16     | _      | _     | HR1       | 0<1:0>   |       | HR01              | <3:0>    |        | _        | N        | 1IN10<2:0> |         |         | MIN01   | <3:0>      |       | xxxx       |

| 0C40                        | ALRMTIME                        | 15:0      | _      |       | SEC10<2:0 | )>       |       | SEC0 <sup>2</sup> | <3:0>    |        | _        | —        | —          |         | _       | _       | _          | _     | xx00       |

| 0050                        |                                 | 31:16     | _      | _     | —         | —        | _     | _                 | _        | _      | _        | _        | _          | MONTH10 |         | MONTH   | 01<3:0>    |       | 00xx       |

| 0050                        | ALRMDATE                        | 15:0      | _      | _     | DAY1      | 0<1:0>   |       | DAY0'             | <3:0>    |        | —        | —        |            | —       | —       | W       | /DAY01<2:0 | >     | xx0x       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | -                 | _                 | -                 | _                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   | -                 |                   | -                 |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   | _                 | _                 | LOAD              | _                 | CONT              | PRNGEN           | TRNGEN           |

| 7.0          | R/W-0             | R/W-1             | R/W-1             | R/W-0             | R/W-0             | R/W-1             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | PLEN<             | :7:0>             |                   |                  |                  |

#### REGISTER 27-2: RNGCON: RANDOM NUMBER GENERATOR CONTROL REGISTER

### Legend:

| Legenu.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-13 **Unimplemented:** Read as '0'

bit 12 LOAD: Device Select bit

This bit is self-clearing and is used to load the seed from the TRNG (i.e., the random value) as a seed to the PRNG.

- bit 11 Unimplemented: Read as '0'

- bit 10 CONT: PRNG Number Shift Enable bit

- 1 = The PRNG random number is shifted every cycle

- 0 = The PRNG random number is shifted when the previous value is removed

- bit 9 PRNGEN: PRNG Operation Enable bit

- 1 = PRNG operation is enabled

- 0 = PRNG operation is not enabled

- bit 8 TRNGEN: TRNG Operation Enable bit

1 = TRNG operation is enabled

- 0 = TRNG operation is not enabled

- bit 7-0 **PLEN<7:0>:** PRNG Polynomial Length bits These bits contain the length of the polynomial used for the PRNG.

#### TABLE 28-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  |               |        |        |        |                |           |           |        | Bits        |        |               |        |        |        |            |        |        |     |

|-----------------------------|------------------|---------------|--------|--------|--------|----------------|-----------|-----------|--------|-------------|--------|---------------|--------|--------|--------|------------|--------|--------|-----|

| Virtual Address<br>(BF84_#) | Register<br>Name |               |        | 27/11  | 26/10  | 25/9           | 24/8      | 23/7      | 22/6   | 21/5        | 20/4   | 19/3          | 18/2   | 17/1   | 16/0   | All Resets |        |        |     |

| D040                        | AD1CMPEN5        | 31:16         | CMPE31 | CMPE30 | CMPE29 | CMPE28         | CMPE27    | CMPE26    | CMPE25 | CMPE24      | CMPE23 | CMPE22        | CMPE21 | CMPE20 | CMPE19 | CMPE18     | CMPE17 | CMPE16 | 000 |

| B048                        | AD1CMPEN5        | 15:0          | CMPE15 | CMPE14 | CMPE13 | CMPE12         | CMPE11    | CMPE10    | CMPE9  | CMPE8       | CMPE7  | CMPE6         | CMPE5  | CMPE4  | CMPE3  | CMPE2      | CMPE1  | CMPE0  | 000 |

| B04C                        | AD1CMP5          | 31:16         |        |        |        |                |           |           |        | ADCMPHI<15: | 0>     |               |        |        |        |            |        |        | 000 |

| D040                        | AD ICIMI 3       | 15:0          |        |        |        |                |           | -         |        | ADCMPLO<15  |        |               |        | -      |        | -          |        |        | 000 |

| B050                        | AD1CMPEN6        | 31:16         |        | CMPE30 | CMPE29 | CMPE28         | CMPE27    | CMPE26    | CMPE25 | CMPE24      | CMPE23 | CMPE22        | CMPE21 | CMPE20 |        | CMPE18     | CMPE17 | CMPE16 | _   |

| 2000                        |                  | 15:0          | CMPE15 | CMPE14 | CMPE13 | CMPE12         | CMPE11    | CMPE10    | CMPE9  | CMPE8       | CMPE7  | CMPE6         | CMPE5  | CMPE4  | CMPE3  | CMPE2      | CMPE1  | CMPE0  | 000 |

| B054                        | AD1CMP6          | 31:16         |        |        |        |                |           |           |        | ADCMPHI<15: |        |               |        |        |        |            |        |        | 000 |

|                             |                  | 15:0          |        |        |        |                |           |           |        | ADCMPLO<15  | 1      |               |        |        |        |            |        |        | 000 |

| B058                        | AD1FLTR1         | 31:16         | AFEN   | _      | _      | (              | OVRSAM<2: | 0>        | AFGIEN | AFRDY       | _      | _             |        |        | CHNLI  | D<5:0>     |        |        | 000 |

|                             |                  | 15:0          |        |        |        |                |           |           |        | LTRDATA<15  | -      |               |        |        |        |            |        |        | 000 |

| B05C                        | AD1FLTR2         | 31:16         | AFEN   | _      | _      | (              | OVRSAM<2: | 0>        | AFGIEN | AFRDY       |        | _             |        |        | CHNLI  | D<5:0>     |        |        | 000 |

|                             |                  | 15:0          |        |        |        |                |           |           |        | LTRDATA<15  | :0>    |               |        |        |        |            |        |        | 000 |

| B060                        | AD1FLTR3         | 31:16         | AFEN   | _      | —      | (              | OVRSAM<2: | 0>        | AFGIEN | AFRDY       |        | —             |        |        | CHNLI  | D<5:0>     |        |        | 000 |

|                             |                  | 15:0          |        |        |        |                |           |           |        | LTRDATA<15  | :0>    |               |        |        |        |            |        |        | 000 |

| B064                        | AD1FLTR4         | 31:16         | AFEN   | _      | —      | (              | OVRSAM<2: | 0>        | AFGIEN | AFRDY       |        | —             |        |        | CHNLI  | D<5:0>     |        |        |     |

|                             |                  | 15:0          |        |        |        | FLTRDATA<15:0> |           |           |        |             |        |               |        | 000    |        |            |        |        |     |

| B068                        | AD1FLTR5         | 31:16         | AFEN   | —      | —      | (              | OVRSAM<2: | 0>        | AFGIEN | AFRDY       | —      | —             |        |        | CHNLI  | D<5:0>     |        |        | 000 |

|                             |                  | 15:0          |        |        |        | 1              |           |           |        | LTRDATA<15  |        |               | 1      |        |        |            |        |        | 000 |

| B06C                        | AD1FLTR6         | 31:16         | AFEN   | —      | —      | (              | OVRSAM<2: | 0>        | AFGIEN | AFRDY       | —      | —             |        |        | CHNLI  | D<5:0>     |        |        | 000 |

|                             |                  | 15:0          |        |        |        |                |           |           |        | FLTRDATA<15 | :0>    |               | -      |        |        |            |        |        | 000 |

| B070                        | AD1TRG1          | 31:16         | —      | _      | _      |                |           | TRGSRC3<  |        |             | —      | _             | —      |        |        | GSRC2<4    |        |        | 000 |

|                             |                  | 15:0          | _      | —      | _      |                |           | TRGSRC1<  |        |             | _      | _             | _      |        |        | GSRC0<4    |        |        | 000 |

| B074                        | AD1TRG2          | 31:16         | —      | -      | -      |                |           | TRGSRC7<  |        |             | -      | _             | _      |        |        | GSRC6<4    |        |        | 000 |

|                             | -                | 15:0          |        |        |        |                |           | TRGSRC5<  |        |             | _      |               |        |        |        | GSRC4<4    |        |        | 000 |

| B078                        | AD1TRG3          | 31:16         | _      | _      | _      | _              |           | TRGSRC11  |        |             | _      | —             | —      |        |        | GSRC10<    |        |        | 000 |

|                             |                  | 15:0<br>31:16 | _      | _      |        |                |           | TRGSRC9<  | 4:0>   |             | _      |               | _      |        |        | GSRC8<4    | :0>    |        | 000 |

| B090                        | AD1CMPCON1       | 15:0          |        |        |        | _              | _         | AINID<4:0 |        |             |        | —<br>DCMPGIEN |        | IEBTWN | IEHIHI | IEHILO     | IELOHI | IELOLO | 000 |

|                             |                  | 31:16         |        |        |        |                | _         | AINID<4.  | J>     | _           |        |               |        |        |        |            |        | IELOLO | 000 |

| B094                        | AD1CMPCON2       | 15:0          |        |        |        |                |           | AINID<4:0 |        |             |        | DCMPGIEN      | DCMPED | IEBTWN | IEHIHI | IEHILO     | IELOHI | IELOLO | 000 |

|                             |                  | 31:16         | _      | _      |        | _              |           |           |        | _           |        |               |        |        |        |            |        |        | 000 |

| B098                        | AD1CMPCON3       | 15:0          | _      | _      | _      |                |           | AINID<4:0 | )>     |             | ENDCMP | DCMPGIEN      | DCMPED | IEBTWN | IEHIHI | IEHILO     | IELOHI | IELOLO | 000 |

|                             |                  | 31:16         | _      | _      | _      |                | _         |           | _      | _           |        |               |        |        | —      |            |        |        | 000 |

| B09C                        | AD1CMPCON4       | 15:0          |        | _      | _      |                |           | AINID<4:0 | 0>     |             | ENDCMP | DCMPGIEN      | DCMPED | IEBTWN | IEHIHI | IEHILO     | IELOHI | IELOLO | 000 |

| -                           |                  | 31:16         | _      | _      | _      |                | _         | _         | _      | _           | _      | _             | _      | _      | _      | -          | _      | _      | 000 |

| B0A0                        | AD1CMPCON5       | 15:0          | _      | _      | _      |                |           |           |        | IELOLO      | 000    |               |        |        |        |            |        |        |     |

| <b>B</b> 4 • •              |                  | 31:16         | _      | _      | _      |                | —         | —         | —      | _           | —      | _             | —      | _      | _      | _          | —      | —      | 000 |

| B0A4                        | AD1CMPCON6       | 15:0          | _      | _      | _      |                |           | AINID<4:0 | )>     |             | ENDCMP | DCMPGIEN      |        | IEBTWN | IEHIHI | IEHILO     | IELOHI | IELOLO | 000 |

PIC32MZ Embedded Connectivity (EC) Family

#### REGISTER 34-4: DEVCFG1/ADEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FNOSC<2:0>: Oscillator Selection bits

- 111 = FRC divided by FRCDIV<2:0> bits (FRCDIV)

- 110 = Reserved

- 101 = LPRC

- 100 **= S**OSC

- 011 = Reserved

- 010 = Posc (HS, EC)

- 001 = SPLL

- 000 = FRC divided by FRCDIV<2:0> bits (FRCDIV)

NOTES:

#### TABLE 37-45: ETHERNET MODULE SPECIFICATIONS

| АС СНА          | RACTERISTICS                        | (unless | d Operatin<br>otherwise<br>g temperati | stated) |       | <b>to 3.6V</b><br>85°C for Industrial |

|-----------------|-------------------------------------|---------|----------------------------------------|---------|-------|---------------------------------------|

| Param.<br>No.   | Characteristic                      | Min.    | Тур.                                   | Max.    | Units | Conditions                            |

| MIIM Tin        | ning Requirements                   |         | •                                      |         | •     |                                       |

| ET1             | MDC Duty Cycle                      | 40      | —                                      | 60      | %     | —                                     |

| ET2             | MDC Period                          | 400     | —                                      | —       | ns    | —                                     |

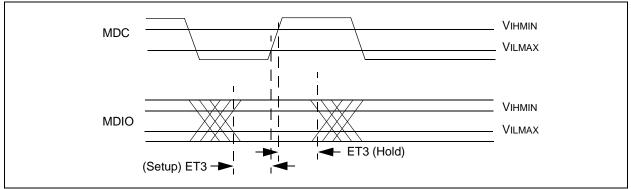

| ET3             | MDIO Output Setup and Hold          | 10      | —                                      | 10      | ns    | See Figure 37-24                      |

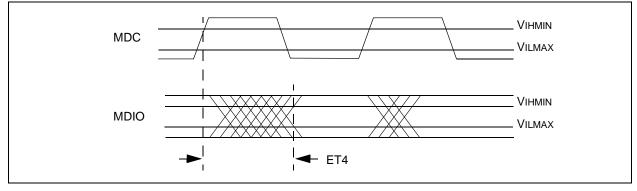

| ET4             | MDIO Input Setup and Hold           | 0       | —                                      | 300     | ns    | See Figure 37-25                      |

| MII Timi        | ng Requirements                     |         |                                        |         |       |                                       |

| ET5             | TX Clock Frequency                  | _       | 25                                     | —       | MHz   | —                                     |

| ET6             | TX Clock Duty Cycle                 | 35      | —                                      | 65      | %     | —                                     |

| ET7             | ETXDx, ETEN, ETXERR Output Delay    | 0       | —                                      | 25      | ns    | See Figure 37-26                      |

| ET8             | RX Clock Frequency                  |         | 25                                     | —       | MHz   | —                                     |

| ET9             | RX Clock Duty Cycle                 | 35      | —                                      | 65      | %     | —                                     |

| ET10            | ERXDx, ERXDV, ERXERR Setup and Hold | 10      | —                                      | 30      | ns    | See Figure 37-27                      |

| <b>RMII</b> Tin | ning Requirements                   |         |                                        |         |       |                                       |

| ET11            | Reference Clock Frequency           | _       | 50                                     | —       | MHz   | _                                     |

| ET12            | Reference Clock Duty Cycle          | 35      | —                                      | 65      | %     | —                                     |

| ET13            | ETXDx, ETEN, Setup and Hold         | 2       | —                                      | 16      | ns    | —                                     |

| ET14            | ERXDx, ERXDV, ERXERR Setup and Hold | 2       | —                                      | 16      | ns    | —                                     |

#### FIGURE 37-24: MDIO SOURCED BY THE PIC32 DEVICE

#### FIGURE 37-25: MDIO SOURCED BY THE PHY

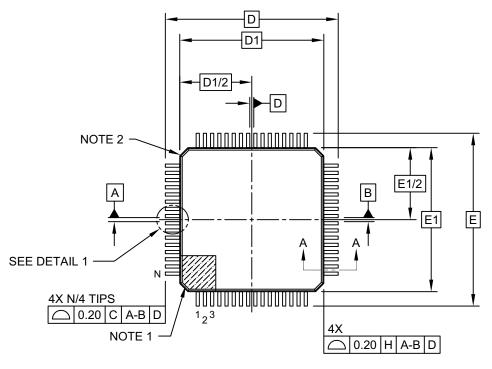

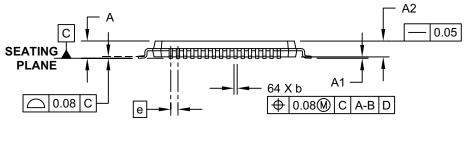

### 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2

#### TABLE A-1: OSCILLATOR CONFIGURATION DIFFERENCES (CONTINUED)

| PIC32MX5XX/6XX/7XX Feature                                                                                                           | PIC32MZ Feature                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fail-Safe Clock Monitor (FSCM)                                                                                                       |                                                                                                                                                                                                                                                |

| On PIC32MX devices, the internal FRC became the clock source on a failure of the clock source.                                       | On PIC32MZ devices, a separate internal Backup FRC (BFRC) becomes the clock source upon a failure at the clock source.                                                                                                                         |

| On PIC32MX devices, a clock failure resulted in the triggering of a specific interrupt when the switchover was complete.             | On PIC32MZ devices, a NMI is triggered instead, and must be handled by the NMI routine.                                                                                                                                                        |

| FSCM generates an interrupt.                                                                                                         | FSCM generates a NMI.                                                                                                                                                                                                                          |

|                                                                                                                                      | The definitions of the FCKSM<1:0> bits has changed on PIC32MZ devices.                                                                                                                                                                         |

| FCKSM<1:0> (DEVCFG1<15:14>)                                                                                                          | FCKSM<1:0> (DEVCFG1<15:14>)                                                                                                                                                                                                                    |