Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 120                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

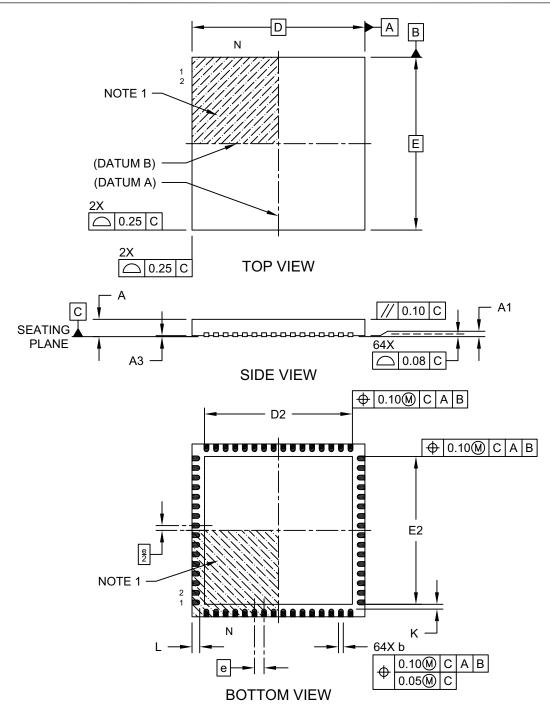

| Package / Case             | 144-LQFP                                                                          |

| Supplier Device Package    | 144-LQFP (20x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048ech144t-i-pl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2 Architecture Overview

The MIPS32 microAptiv Microprocessor core in PIC32MZ EC family devices contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution unit

- General Purpose Register (GPR)

- Multiply/Divide Unit (MDU)

- System control coprocessor (CP0)

- Memory Management Unit (MMU)

- Instruction/Data cache controllers

- Power Management

- Instructions and data caches

- microMIPS support

- Enhanced JTAG (EJTAG) controller

#### 3.2.1 EXECUTION UNIT

The processor core execution unit implements a load/ store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. Seven additional register file shadow sets (containing thirty-two registers) are added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing arithmetic and bitwise logical operations

- · Shifter and store aligner

- DSP ALU and logic block for performing DSP instructions, such as arithmetic/shift/compare operations

#### 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations, and DSP ASE multiply instructions. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x32 booth recoded multiplier, four pairs of result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x32) represents the *rs* operand. The second number ('32' of 32x32) represents the *rt* operand.

The MDU supports execution of one multiply or multiply-accumulate operation every clock cycle.

Divide operations are implemented with a simple 1-bitper-clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation has completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the processor core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| MOLTIFLI/DIVIDE UNIT LATENCIES AND REPEAT RATES |                                                |         |             |  |  |  |  |  |  |

|-------------------------------------------------|------------------------------------------------|---------|-------------|--|--|--|--|--|--|

| Opcode                                          | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |  |  |  |  |  |  |

| MULT/MULTU, MADD/MADDU,                         | 16 bits                                        | 5       | 1           |  |  |  |  |  |  |

| MSUB/MSUBU (HI/LO destination)                  | 32 bits                                        | 5       | 1           |  |  |  |  |  |  |

| MUL (GPR destination)                           | 16 bits                                        | 5       | 1           |  |  |  |  |  |  |

|                                                 | 32 bits                                        | 5       | 1           |  |  |  |  |  |  |

| DIV/DIVU                                        | 8 bits                                         | 12/14   | 12/14       |  |  |  |  |  |  |

|                                                 | 16 bits                                        | 20/22   | 20/22       |  |  |  |  |  |  |

|                                                 | 24 bits                                        | 28/30   | 28/30       |  |  |  |  |  |  |

|                                                 | 32 bits                                        | 36/38   | 36/38       |  |  |  |  |  |  |

## TABLE 3-1: MIPS32 microAptiv MICROPROCESSOR CORE HIGH-PERFORMANCE INTEGER MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | _                 | _                 | _                 | _                 |                   | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 |                   |                  | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 |                   |                  | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 7.0          | _                 | —                 | _                 |                   | _                 | _                 | _                | VREGS            |

#### REGISTER 6-4: PWRCON: POWER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-1 Unimplemented: Read as '0'

bit 0 VREGS: Voltage Regulator Stand-by Enable bit

1 = Voltage regulator will remain active during Sleep

0 = Voltage regulator will go to Stand-by mode during Sleep

| Exception Type<br>(In Order of<br>Priority) | Description                                                                                                                                                                                                                                                                                                                    | Branches to     | Status<br>Bits Set | Debug Bits<br>Set                           | EXCCODE         | XC32 Function Name         |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|---------------------------------------------|-----------------|----------------------------|

| Instruction<br>Validity<br>Exceptions       | An instruction could not be completed because it<br>was not allowed to access the required resources<br>(Coprocessor Unusable) or was illegal (Reserved<br>Instruction). If both exceptions occur on the same<br>instruction, the Coprocessor Unusable Exception<br>takes priority over the Reserved Instruction<br>Exception. | EBASE+0x180     | EXL                |                                             | 0x0A or<br>0x0B | _general_exception_handle  |

| Execute<br>Exception                        | An instruction-based exception occurred: Integer<br>overflow, trap, system call, breakpoint, floating<br>point, or DSP ASE state disabled exception.                                                                                                                                                                           | EBASE+0x180     | EXL                | _                                           | 0x08-0x0C       | _general_exception_handler |

| Tr                                          | Execution of a trap (when trap condition is true).                                                                                                                                                                                                                                                                             | EBASE+0x180     | EXL                | —                                           | 0x0D            | _general_exception_handle  |

| DDBL/DDBS                                   | EJTAG Data Address Break (address only) or<br>EJTAG data value break on store (address +<br>value).                                                                                                                                                                                                                            | 0xBFC0_0480     | _                  | DDBL or<br>DDBS                             | _               | _                          |

| WATCH                                       | A reference to an address that is in one of the Watch registers (data).                                                                                                                                                                                                                                                        | EBASE+0x180     | EXL                | —                                           | 0x17            | _general_exception_handle  |

| AdEL                                        | Load address alignment error. User mode load reference to kernel address.                                                                                                                                                                                                                                                      | EBASE+0x180     | EXL                | —                                           | 0x04            | _general_exception_handle  |

| AdES                                        | Store address alignment error. User mode store to kernel address.                                                                                                                                                                                                                                                              | EBASE+0x180     | EXL                | —                                           | 0x05            | _general_exception_handler |

| TLBL                                        | Load TLB miss or load TLB hit to page with $V = 0$ .                                                                                                                                                                                                                                                                           | EBASE+0x180     | EXL                | —                                           | 0x02            | _general_exception_handle  |

| TLBS                                        | Store TLB miss or store TLB hit to page with $V = 0$ .                                                                                                                                                                                                                                                                         | EBASE+0x180     | EXL                | —                                           | 0x03            | _general_exception_handle  |

| DBE                                         | Load or store bus error.                                                                                                                                                                                                                                                                                                       | EBASE+0x180     | EXL                | —                                           | 0x07            | _general_exception_handle  |

| DDBL                                        | EJTAG data hardware breakpoint matched in load data compare.                                                                                                                                                                                                                                                                   | 0xBFC0_0480     | —                  | DDBL                                        | —               | _                          |

| CBrk                                        | EJTAG complex breakpoint.                                                                                                                                                                                                                                                                                                      | 0xBFC0_0480     | _                  | DIBIMPR,<br>DDBLIMPR,<br>and/or<br>DDBSIMPR | _               | _                          |

|                                             |                                                                                                                                                                                                                                                                                                                                | Lowest Priority |                    |                                             |                 |                            |

PIC32MZ Embedded Connectivity (EC) Family

### TABLE 7-1: MIPS32<sup>®</sup> microAptiv<sup>™</sup> MICROPROCESSOR CORE EXCEPTION TYPES (CONTINUED)

| REGISTE  | ER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER                                                                                 |

|----------|-----------------------------------------------------------------------------------------------------------------------------|

| bit 10-8 | NOSC<2:0>: New Oscillator Selection bits                                                                                    |

|          | 111 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)                                                |

|          | 110 = Reserved                                                                                                              |

|          | 101 = Internal Low-Power RC (LPRC) Oscillator                                                                               |

|          | 100 = Secondary Oscillator (Sosc)<br>011 = Reserved                                                                         |

|          | 010 = Primary Oscillator (Posc) (HS or EC)                                                                                  |

|          | 001 = System PLL (SPLL)                                                                                                     |

|          | 000 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)                                                |

|          | On Reset, these bits are set to the value of the FNOSC<2:0> Configuration bits (DEVCFG1<2:0>).                              |

| bit 7    | CLKLOCK: Clock Selection Lock Enable bit                                                                                    |

|          | 1 = Clock and PLL selections are locked                                                                                     |

|          | 0 = Clock and PLL selections are not locked and may be modified                                                             |

| bit 6    | ULOCK: USB PLL Lock Status bit                                                                                              |

|          | 1 = Indicates that the USB PLL module is in lock or USB PLL module start-up timer is satisfied                              |

|          | 0 = Indicates that the USB PLL module is out of lock or USB PLL module start-up timer is in progress or USB PLL is disabled |

| bit 5    | SLOCK: System PLL Lock Status bit                                                                                           |

|          | 1 = System PLL module is in lock or module start-up timer is satisfied                                                      |

|          | 0 = System PLL module is out of lock, start-up timer is running or system PLL is disabled                                   |

| bit 4    | SLPEN: Sleep Mode Enable bit                                                                                                |

|          | 1 = Device will enter Sleep mode when a WAIT instruction is executed                                                        |

| 1.11.0   | 0 = Device will enter Idle mode when a WAIT instruction is executed                                                         |

| bit 3    | CF: Clock Fail Detect bit                                                                                                   |

|          | <ul> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> </ul>                   |

| bit 2    | Unimplemented: Read as '0'                                                                                                  |

| bit 1    | SOSCEN: Secondary Oscillator (Sosc) Enable bit                                                                              |

| DICT     | 1 = Enable Secondary Oscillator                                                                                             |

|          | 0 = Disable Secondary Oscillator                                                                                            |

| bit 0    | <b>OSWEN:</b> Oscillator Switch Enable bit <sup>(1)</sup>                                                                   |

|          | 1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits                                                  |

|          | 0 = Oscillator switch is complete                                                                                           |

| Note 1:  | The reset value for this bit depends on the setting of the IESO (DEVCFG1<7>) bit. When IESO = 1, the                        |

|          | reset value is '1'. When IESO = 0, the reset value is '0'.                                                                  |

## Note: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

## PIC32MZ Embedded Connectivity (EC) Family

## REGISTER 11-7: USBIE0CSR3: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 3 (ENDPOINT 0)

|              |                   | (, • •)           |                   |                   |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 21.24        | R-x               | R-x               | R-0               | R-x               | R-x               | R-x               | R-1              | R-0              |  |  |  |

| 31:24        | MPRXEN            | MPTXEN            | BIGEND            | HBRXEN            | HBTXEN            | DYNFIFOS          | SOFTCONE         | UTMIDWID         |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | _                 | _                 | _                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | _                 | _                 | _                 | _                 | —                 | —                 | —                | —                |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 |                   | _                |                  |  |  |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 MPRXEN: Automatic Amalgamation Option bit

- 1 = Automatic amalgamation of bulk packets is done

- 0 = No automatic amalgamation

- bit 30 **MPTXEN:** Automatic Splitting Option bit 1 = Automatic splitting of bulk packets is done

- Automatic splitting of bulk packets

- 0 = No automatic splitting

- bit 29 BIGEND: Byte Ordering Option bit

- 1 = Big Endian ordering

- 0 = Little Endian ordering

- bit 28 HBRXEN: High-bandwidth RX ISO Option bit

1 = High-bandwidth RX ISO endpoint support is selected

0 = No High-bandwidth RX ISO support

- bit 27 **HBTXEN:** High-bandwidth TX ISO Option bit 1 = High-bandwidth TX ISO endpoint support is selected 0 = No High-bandwidth TX ISO support

- bit 26 **DYNFIFOS:** Dynamic FIFO Sizing Option bit 1 = Dynamic FIFO sizing is supported 0 = No Dynamic FIFO sizing

- bit 25 SOFTCONE: Soft Connect/Disconnect Option bit 1 = Soft Connect/Disconnect is supported 0 = Soft Connect/Disconnect is not supported

- bit 24 UTMIDWID: UTMI+ Data Width Option bit Always '0', indicating 8-bit UTMI+ data width

- bit 23-0 Unimplemented: Read as '0'

#### TABLE 12-21: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| SS                          |                  |               | Bits  |       |       |       |       |       |      |      |      |      |      |      |      |       |              |      |            |

|-----------------------------|------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1         | 16/0 | All Resets |

|                             | IC4R             | 31:16         | _     | -     | —     | —     | -     | —     | —    | —    | —    | —    | -    | —    | —    | —     | —            | —    | 000        |

| 1444                        | IC4R             | 15:0          |       | -     | —     | —     | -     | —     | —    | —    |      | —    | _    | —    |      | IC4R  | <3:0>        |      | 0000       |

| 1448                        | IC5R             | 31:16         | _     |       | —     | —     |       | —     | —    | _    | _    | _    |      | —    | _    | —     | _            | —    | 0000       |

| 1448                        | ICSK             | 15:0          | _     |       | —     | —     |       | —     | —    | _    | _    | _    |      | —    |      | IC5R  | <3:0>        |      | 0000       |

| 144C                        | IC6R             | 31:16         | -     |       | _     |       |       | —     | —    | —    | —    | —    |      | —    | _    | —     | _            | —    | 0000       |

| 1440                        | ICOK             | 15:0          | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | IC6R  | <3:0>        |      | 0000       |

| 1450                        | IC7R             | 31:16         | _     | _     | —     | _     | _     | —     | —    | _    | _    | —    | _    | —    | —    | —     | —            | _    | 0000       |

| 1400                        | 10/11            | 15:0          | —     | —     | —     | —     | _     | —     | —    | —    | —    | —    | —    | —    |      | IC7R  | <3:0>        | •    | 0000       |

| 1454                        | IC8R             | 31:16         | _     | _     | —     | —     | _     | —     | —    | —    | —    | —    | _    | —    | —    | —     | —            | —    | 0000       |

|                             | 10011            | 15:0          | —     | —     | —     | —     | —     | —     | —    | —    | -    | —    | —    | —    |      | IC8R  | <3:0>        |      | 0000       |

| 1458                        | IC9R             | 31:16         |       | _     | _     | _     | _     | _     | _    | _    | —    | —    | _    | —    |      |       |              | —    | 0000       |

|                             |                  | 15:0          | —     | _     | —     | —     | _     | _     |      | —    | —    | —    | _    | —    |      | IC9R  |              |      |            |

| 1460                        | OCFAR            | 31:16         | —     | _     | _     | —     | _     |       |      | —    | —    | —    | _    | —    |      | —     | —            | _    | 0000       |

|                             |                  | 15:0          | —     | _     | _     | —     | _     |       |      | —    | —    | —    | _    | —    |      | r     | R<3:0>       |      | 0000       |

| 1468                        | U1RXR -          | 31:16         | _     | —     | —     | —     | _     | —     |      | —    | —    | —    | —    | —    | —    | —     | —            | —    | 0000       |

|                             |                  | 15:0          | —     | —     | —     | —     | _     | —     |      | —    | —    | —    | —    | —    |      | U1RX  | R<3:0>       |      | 0000       |

| 146C                        | U1CTSR           | 31:16         | _     | —     | _     | —     | _     | _     |      | _    | -    | _    | —    | _    | —    | —     | —            | —    | 0000       |

|                             |                  | 15:0          |       |       | _     | _     |       | _     |      | _    | _    | _    |      | _    |      | U1CTS | R<3:0>       |      | 0000       |

| 1470                        | U2RXR            | 31:16         |       |       | _     | _     |       | _     |      | _    | _    | _    |      | _    | —    | -     |              | —    | 0000       |

|                             |                  | 15:0          | _     |       | _     |       |       |       | _    | _    | _    | _    |      | _    |      | U2RX  | R<3:0>       | 1    | 0000       |

| 1474                        | U2CTSR           | 31:16<br>15:0 | _     |       | _     |       |       |       |      | —    | _    | _    |      | —    | —    | -     | —<br>R<3:0>  | —    | 0000       |

|                             |                  | 31:16         |       |       |       | _     |       | _     | _    | _    |      |      |      | _    |      | 02018 | K<3:0>       | _    | 0000       |

| 1478                        | <b>U3RXR</b>     | 15:0          |       |       |       |       |       |       |      |      |      |      |      |      |      |       | —<br>R<3:0>  |      | 0000       |

|                             |                  | 31:16         |       |       |       | _     |       | _     |      |      | _    |      |      |      | _    |       |              | _    | 0000       |

| 147C                        | <b>U3CTSR</b>    | 15:0          |       |       |       | _     |       | _     |      |      | _    |      |      | _    |      |       | —<br>SR<3:0> |      | 0000       |

|                             |                  | 31:16         |       |       |       |       |       |       | _    |      |      |      |      | _    | _    |       | —            | _    | 0000       |

| 1480                        | U4RXR            | 15:0          |       |       |       |       |       |       |      |      |      | _    |      |      |      |       | —<br>R<3:0>  |      | 0000       |

|                             |                  | 31:16         |       |       |       |       |       |       | _    |      |      |      |      |      |      | _     |              | _    | 0000       |

| 1484                        | U4CTSR           | 15:0          |       |       |       |       |       |       |      |      |      |      |      |      |      |       |              |      | 0000       |

PIC32MZ Embedded Connectivity (EC) Family

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | _                 |                   | _                 | _                 |                   | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   |                   | _                 |                   |                  | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 |                   |                  | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |

#### **REGISTER 12-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (x = A - G)

#### Legend:

- R = Readable bit

- W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

- ON: Change Notice (CN) Control ON bit bit 15

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Control bit

- 1 = CPU Idle mode halts CN operation

- 0 = CPU Idle mode does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

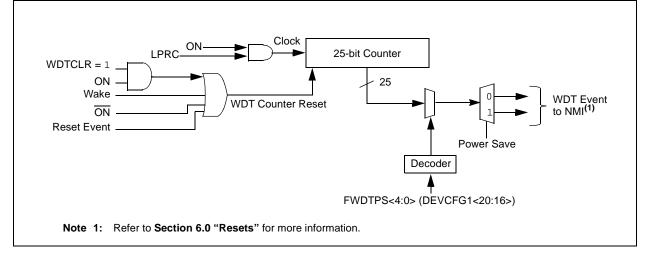

#### 16.0 WATCHDOG TIMER (WDT)

This data sheet summarizes the features Note: of the PIC32MZ Embedded Connectivity (EC) Family family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

When enabled, the Watchdog Timer (WDT) operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

Some of the key features of the WDT module are:

- Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle

#### FIGURE 16-1: WATCHDOG TIMER BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |  |  |

|--------------|------------------------|--------------------|-------------------|-----------------------|-------------------|-------------------|------------------|-----------------------|--|--|

| 24.24        | R/W-0                  | R/W-0              | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN                 | FRMSYPW           | FRMCNT<2:0>       |                  |                       |  |  |

| 00.40        | R/W-0                  | U-0                | U-0               | U-0                   | U-0               | U-0               | R/W-0            | R/W-0                 |  |  |

| 23:16        | MCLKSEL <sup>(1)</sup> | —                  | —                 | _                     | —                 | —                 | SPIFE            | ENHBUF <sup>(1)</sup> |  |  |

| 45.0         | R/W-0                  | U-0                | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 15:8         | ON                     | —                  | SIDL              | DISSDO <sup>(4)</sup> | MODE32            | MODE16            | SMP              | CKE <sup>(2)</sup>    |  |  |

| 7.0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 7:0          | SSEN                   | CKP <sup>(3)</sup> | MSTEN             | DISSDI <sup>(4)</sup> | STXISEL<1:0>      |                   | SRXISEL<1:0>     |                       |  |  |

|              |                        |                    |                   |                       |                   |                   |                  |                       |  |  |

#### REGISTER 19-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31 **FRMEN:** Framed SPI Support bit

- 1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

- 0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on <u>SSx</u> pin bit (Framed SPI mode only)

- 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 FRMPOL: Frame Sync Polarity bit (Framed SPI mode only)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in Framed mode.

- 111 = Reserved

- 110 = Reserved

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

- 000 = Generate a frame sync pulse on every data character

- bit 23 MCLKSEL: Master Clock Enable bit<sup>(1)</sup>

- 1 = REFCLKO1 is used by the Baud Rate Generator

- 0 = PBCLK2 is used by the Baud Rate Generator

- bit 22-18 Unimplemented: Read as '0'

- **Note 1:** This bit can only be written when the ON bit = 0. Refer to **Section 37.0** "**Electrical Characteristics**" for maximum clock frequency requirements.

- 2: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: This bit present for legacy compatibility and is superseded by PPS functionality on these devices (see Section 12.3 "Peripheral Pin Select (PPS)" for more information).

| REGISTE | ER 25-2: RTCALRM: REAL-TIME CLOCK ALARM CONTROL REGISTER (CONTINUED)                                       |

|---------|------------------------------------------------------------------------------------------------------------|

| bit 7-0 | ARPT<7:0>: Alarm Repeat Counter Value bits <sup>(2)</sup>                                                  |

|         | 11111111 = Alarm will trigger 256 times                                                                    |

|         | •                                                                                                          |

|         | •                                                                                                          |

|         | 0000000 = Alarm will trigger one time                                                                      |

|         | The counter decrements on any alarm event. The counter only rolls over from $0x00$ to $0xFF$ if CHIME = 1. |

| Note 1: | Hardware clears the ALRMEN bit anytime the alarm event occurs, when $ARPT < 7:0 > = 0.0$ and $CHIME = 0.$  |

| 2:      | This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.                 |

| Mater   | This assists is asset where a Deves on Devet (DOD)                                                         |

| Note:   | This register is reset only on a Power-on Reset (POR).                                                     |

| Bit<br>Range | Bit<br>31/23/15/7  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0, HC          | R/W-0, HC         | R/W-0, HC         | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | CAL <sup>(2)</sup> | GSWTRG            | RQCNVRT           | —                 | —                 | _                 | —                | —                |

| 23:16        | U-0                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                  | —                 | _                 | —                 | —                 | _                 | —                | —                |

| 15:8         | U-0                | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |

| 15.0         | —                  | —                 | —                 | V                 | REFSEL<2:0>       | 1)                | —                | —                |

| 7:0          | U-0                | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | —                  | —                 |                   |                   | ADINSE            | L<5:0>            |                  |                  |

#### REGISTER 28-3: AD1CON3: ADC1 CONTROL REGISTER 3

| Legend:           |                  | HC = Hardware Cleared  | b                  |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 31 CAL: Calibration bit<sup>(2)</sup>

- 1 = Initiate an ADC calibration cycle

- 0 = Calibration cycle is not in progress

#### bit 30 **GSWTRG:** Global Software Trigger bit

- 1 = Trigger analog-to-digital conversion for ADC inputs that have selected the GSWTRG bit as the trigger signal, either through the associated TRGSRC<4:0> bits in the AD1TRGn registers or through the STRGSRC<4:0> bits in the AD1CON1 register

- 0 = This bit is automatically cleared

- bit 29 RQCNVRT: Individual ADC Input Conversion Request bit

This bit and its associated ADINSEL<5:0> bits enable the user to individually request an analog-to-digital conversion of an analog input without having to reprogram the TRGSRC<4:0> bits or the STRGSRC<4:0> bits. This is very useful during debugging or error handling situations where the user software needs to obtain an immediate ADC result of a specific input.

1 = Trigger the conversion of the selected ADC input as specified by the ADINSEL<5:0> bits

- 0 = This bit is automatically cleared

- bit 28-13 Unimplemented: Read as '0'

- bit 12-10 VREFSEL<2:0>: VREF Input Selection bits<sup>(1)</sup>

| VREFSEL<2:0> | VREFH    | VREFL    |

|--------------|----------|----------|

| 111          | Reserved | Reserved |

| 110          | Reserved | Reserved |

| 101          | Reserved | Reserved |

| 100          | Reserved | Reserved |

| 011          | Vref+    | Vref-    |

| 010          | AVdd     | Vref-    |

| 001          | Vref+    | AVss     |

| 000          | AVdd     | AVss     |

- bit 9-6 **Unimplemented:** Read as '0'

- **Note 1:** These bits should be configured prior to enabling the ADC module by setting the ADCEN bit (AD1CON1<15> = 1).

- 2: See 28.1 "ADC Configuration Requirements" for detailed ADC calibration information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |

| 31:24        | —                 | _                 | _                 |                   | ABAT              | F                 | REQOP<2:0>       | >                |

| 22.16        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 23:16        | OPMOD<2:0>        |                   |                   | CANCAP            | —                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDLE             | -                 | CANBUSY           | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 |                   |                   |                   |                   | DNCNT<4:0>        |                  |                  |

#### REGISTER 29-1: CiCON: CAN MODULE CONTROL REGISTER

| Legend:             | HC = Hardware Clear          | S = Settable bit      |                  |  |

|---------------------|------------------------------|-----------------------|------------------|--|

| R = Readable bit    | W = Writable bit             | P = Programmable bit  | r = Reserved bit |  |

| U = Unimplemented b | it -n = Bit Value at POR: (' | 0', '1', x = Unknown) |                  |  |

#### bit 31-28 Unimplemented: Read as '0'

#### bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

#### bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved Do not use

- 101 = Reserved Do not use

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

#### bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

#### bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 **ON:** CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN19           | MSEL19<1:0>       |                   | FSEL19<4:0>       |                   |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN18           | MSEL18<1:0>       |                   | FSEL18<4:0>       |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6         | FLTEN17           | MSEL17<1:0>       |                   | FSEL17<4:0>       |                   | >                 |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | FLTEN16           | MSEL1             | 6<1:0>            |                   | I                 | SEL16<4:0>        | >                |                  |

#### REGISTER 29-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN19: Filter 19 Enable bit<br>1 = Filter is enabled                                                                   |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

|           | 0 = Filter is disabled                                                                                                   |

| bit 30-29 | MSEL19<1:0>: Filter 19 Mask Select bits                                                                                  |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> </ul>                             |

|           | 01 = Acceptance Mask 2 selected                                                                                          |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 28-24 | FSEL19<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN18: Filter 18 Enable bit                                                                                            |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                   |

| bit 22-21 | MSEL18<1:0>: Filter 18 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected                                                                                          |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                       |

| bit 20-16 | FSEL18<4:0>: FIFO Selection bits                                                                                         |

| 511 20 10 | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                               |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                               |

|           |                                                                                                                          |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------|--|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |

| 31:24     |                   |                   |                   | PTV<              | 15:8>             |                   |                  |                     |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |

| 23:16     | PTV<7:0>          |                   |                   |                   |                   |                   |                  |                     |  |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0               |  |

| 15:8      | ON                | —                 | SIDL              | _                 | _                 | _                 | TXRTS            | RXEN <sup>(1)</sup> |  |

| 7:0       | R/W-0             | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0               |  |

|           | AUTOFC            | —                 | _                 | MANFC             | _                 | _                 | _                | BUFCDEC             |  |

#### REGISTER 30-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

|           | PAUSE Timer Value used for Flow Control.<br>This register should only be written when RXEN (ETHCON1<8>) is not set.                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | These bits are only used for Flow Control operations.                                                                                                                                                                                                                                                     |

| bit 15    | ON: Ethernet ON bit                                                                                                                                                                                                                                                                                       |

|           | <ul><li>1 = Ethernet module is enabled</li><li>0 = Ethernet module is disabled</li></ul>                                                                                                                                                                                                                  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                |

| bit 13    | SIDL: Ethernet Stop in Idle Mode bit                                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = Ethernet module transfers are paused during Idle mode</li> <li>0 = Ethernet module transfers continue during Idle mode</li> </ul>                                                                                                                                                            |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                |

| bit 9     | TXRTS: Transmit Request to Send bit                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Activate the TX logic and send the packet(s) defined in the TX EDT</li> <li>0 = Stop transmit (when cleared by software) or transmit done (when cleared by hardware)</li> </ul>                                                                                                              |

|           | After the bit is written with a '1', it will clear to a '0' whenever the transmit logic has finished transmitting the requested packets in the Ethernet Descriptor Table (EDT). If a '0' is written by the CPU, the transmit logic finishes the current packet's transmission and then stops any further. |

|           | This bit only affects TX operations.                                                                                                                                                                                                                                                                      |

| bit 8     | RXEN: Receive Enable bit <sup>(1)</sup>                                                                                                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                                                                                                           |

- 1 = Enable RX logic, packets are received and stored in the RX buffer as controlled by the filter configuration

- 0 = Disable RX logic, no packets are received in the RX buffer

This bit only affects RX operations.

PTV<15:0>: PAUSE Timer Value bits

bit 31-16

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24     | PMM<31:24>        |                   |                   |                   |                   |                   |                  |                  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10     | PMM<23:16>        |                   |                   |                   |                   |                   |                  |                  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0      | PMM<15:8>         |                   |                   |                   |                   |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0       |                   |                   |                   | PMM               | <7:0>             |                   |                  |                  |

#### REGISTER 30-7: ETHPMM0: ETHERNET CONTROLLER PATTERN MATCH MASK 0 REGISTER

#### Legend:

| 9                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 31-24 | PMM<31:24>: Pattern Match Mask 3 bits |

|-----------|---------------------------------------|

| hit 23-16 | PMM-23-16- Pattern Match Mask 2 hits  |

- bit 23-16 PMM<23:16>: Pattern Match Mask 2 bits

- bit 15-8 **PMM<15:8>:** Pattern Match Mask 1 bits

- bit 7-0 PMM<7:0>: Pattern Match Mask 0 bits

- Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

#### REGISTER 30-8: ETHPMM1: ETHERNET CONTROLLER PATTERN MATCH MASK 1 REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24     |                   | PMM<63:56>        |                   |                   |                   |                   |                  |                  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10     | PMM<55:48>        |                   |                   |                   |                   |                   |                  |                  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 13.8      | PMM<47:40>        |                   |                   |                   |                   |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0       |                   |                   |                   | PMM<              | 39:32>            |                   |                  |                  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|                   |                  |                      |                    |

| bit 31-24 | PMM<63:56>: Pattern Match Mask 7 bits |

|-----------|---------------------------------------|

| bit 23-16 | PMM<55:48>: Pattern Match Mask 6 bits |

| bit 15-8  | PMM<47:40>: Pattern Match Mask 5 bits |

| bit 7-0   | PMM<39:32>: Pattern Match Mask 4 bits |

# Note 1: This register is only used for RX operations. 2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

## REGISTER 30-33: EMAC1MADR: ETHERNET CONTROLLER MAC MII MANAGEMENT ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   | —                 | -                 | —                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   | —                 | _                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-1            |

| 0.61         | —                 | —                 | —                 | PHYADDR<4:0>      |                   |                   |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   | —                 |                   | REGADDR<4:0>      |                   |                   |                  |                  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-13 Unimplemented: Read as '0'

- bit 12-8 **PHYADDR<4:0>:** MII Management PHY Address bits This field represents the 5-bit PHY Address field of Management cycles. Up to 31 PHYs can be addressed (0 is reserved).

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **REGADDR<4:0>:** MII Management Register Address bits This field represents the 5-bit Register Address field of Management cycles. Up to 32 registers can be accessed.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| 24.24        | r-0               | R/P               | r-1               | r-1               | r-1               | r-1                   | r-1              | r-1              |

| 31:24        | —                 | EJTAGBEN          |                   | —                 | —                 | _                     | —                | —                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1                   | r-1              | r-1              |

| 23:16        | —                 | —                 | _                 | —                 | —                 | _                     | —                | —                |

| 45.0         | r-1               | R/P               | R/P               | R/P               | r-1               | R/P                   | R/P              | R/P              |

| 15:8         | —                 | DBGPER<2:0>       |                   | —                 | FSLEEP            | FECCC                 | ON<1:0>          |                  |

| 7.0          | r-1               | R/P               | R/P               | R/P               | R/P               | R/P                   | R/P              | R/P              |

| 7:0          |                   | BOOTISA           | TRCEN             | ICESE             | _<1:0>            | JTAGEN <sup>(1)</sup> | DEBU             | G<1:0>           |

#### REGISTER 34-3: DEVCFG0/ADEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:           | r = Reserved bit | P = Programmable bit |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 Reserved: Write as '0'

- bit 30 EJTAGBEN: EJTAG Boot Enable bit

- 1 = Normal EJTAG functionality

- 0 = Reduced EJTAG functionality

- bit 29-15 Reserved: Write as '1'

- bit 14-12 DBGPER<2:0>: Debug Mode CPU Access Permission bits

- 1xx = Allow CPU access to Permission Group 2 permission regions

- x1x = Allow CPU access to Permission Group 1 permission regions

- xx1 = Allow CPU access to Permission Group 0 permission regions

- 0xx = Deny CPU access to Permission Group 2 permission regions

- ${\rm x0x}$  = Deny CPU access to Permission Group 1 permission regions

- xx0 = Deny CPU access to Permission Group 0 permission regions

When the CPU is in Debug mode and the CPU1PG<1:0> bits (CFGPG<1:0>) are set to a denied permission group as defined by DBGPER<2:0>, the transaction request is assigned Group 3 permissions.

- bit 11 Reserved: Write as '1'

- bit 10 FSLEEP: Flash Sleep Mode bit

- 1 = Flash is powered down when the device is in Sleep mode

- 0 = Flash power down is controlled by the VREGS bit (PWRCON<1>)

- bit 9-8 **FECCCON<1:0>:** Dynamic Flash ECC Configuration bits

Upon a device Reset, the value of these bits is copied to the ECCCON<1:0> bits (CFGCON<5:4>).

- 11 = ECC and dynamic ECC are disabled (ECCCON<1:0> bits are writable)

- 10 = ECC and dynamic ECC are disabled (ECCCON<1:0> bits are locked)

- 01 = Dynamic Flash ECC is enabled (ECCCON<1:0> bits are locked)

- 00 = Flash ECC is enabled (ECCCON<1:0> bits are locked; disables word Flash writes)

- bit 7 Reserved: Write as '1'

- bit 6 BOOTISA: Boot ISA Selection bit

- 1 = Boot code and Exception code is MIPS32<sup>®</sup>