Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048ecm100-i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The System Bus arbitration scheme implements a nonprogrammable, Least Recently Serviced (LRS) priority, which provides Quality Of Service (QOS) for most initiators. However, some initiators can use Fixed High Priority (HIGH) arbitration to guarantee their access to data.

The arbitration scheme for the available initiators is shown in Table 4-5.

| Name             | ID | QOS                   |

|------------------|----|-----------------------|

| CPU              | 1  | LRS <sup>(1)</sup>    |

| CPU              | 2  | HIGH <sup>(1,2)</sup> |

| DMA Read         | 3  | LRS <sup>(1)</sup>    |

| DMA Read         | 4  | HIGH <sup>(1,2)</sup> |

| DMA Write        | 5  | LRS <sup>(1)</sup>    |

| DMA Write        | 6  | HIGH <sup>(1,2)</sup> |

| USB              | 7  | LRS                   |

| Ethernet Read    | 8  | LRS                   |

| Ethernet Write   | 9  | LRS                   |

| CAN1             | 10 | LRS                   |

| CAN2             | 11 | LRS                   |

| SQI1             | 12 | LRS                   |

| Flash Controller | 13 | HIGH <sup>(2)</sup>   |

| Crypto           | 14 | LRS                   |

TABLE 4-5:INITIATOR ID AND QOS

- Note 1: When accessing SRAM, the DMAPRI bit (CFGCON<25>) and the CPUPRI bit (CFGCON<24>) provide arbitration control for the DMA and CPU (when servicing an interrupt (i.e., EXL = 1)), respectively, by selecting the use of LRS or HIGH When using HIGH, the DMA and CPU get arbitration preference over all initiators using LRS.

- 2: Using HIGH arbitration can have serious negative effects on other initiators. Therefore, it is recommended to not enable this type of arbitration for an initiator that uses significant system bandwidth. HIGH arbitration is intended to be used for low bandwidth applications that require low latency, such as LCC graphics applications.

## 4.3 Permission Access and System Bus Registers

The System Bus on PIC32MZ EC family of microcontrollers provides access control capabilities for the transaction initiators on the System Bus.

The System Bus divides the entire memory space into fourteen target regions and permits access to each target by initiators via permission groups. Four Permission Groups (0 through 3) can be assigned to each initiator. Each permission group is independent of the others and can have exclusive or shared access to a region.

Using the CFGPG register (see Register 34-10 in **Section 34.0 "Special Features"**), Boot firmware can assign a permission group to each initiator, which can make requests on the System Bus.

The available targets and their regions, as well as the associated control registers to assign protection, are described and listed in Table 4-6.

Register 4-2 through Register 4-10 are used for setting and controlling access permission groups and regions.

To change these registers, they must be unlocked in hardware. The register lock is controlled by the PGLOCK Configuration bit (CFGCON<11>). Setting PGLOCK prevents writes to the control registers; clearing PGLOCK allows writes.

To set or clear the PGLOCK bit, an unlock sequence must be executed. Refer to **Section 42. "Oscillators with Enhanced PLL"** (DS60001250) in the *"PIC32 Family Reference Manual"* for details.

## REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER (CONTINUED)

- bit 3-0 NVMOP<3:0>: NVM Operation bits

- These bits are only writable when WREN = 0.

- 1111 = Reserved

- •

- •

- 1000 = Reserved

- 0111 = Program erase operation: erase all of program Flash memory (all pages must be unprotected, PWP<23:0> = 0x000000)

- 0110 = Upper program Flash memory erase operation: erases only the upper mapped region of program Flash (all pages in that region must be unprotected)

- 0101 = Lower program Flash memory erase operation: erases only the lower mapped region of program Flash (all pages in that region must be unprotected)

- 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected

- 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected

- 0010 = Quad Word (128-bit) program operation: programs the 128-bit Flash word selected by NVMADDR, if it is not write-protected

- 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<sup>(2)</sup> 0000 = No operation

- Note 1: These bits are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

- 2: This operation results in a "no operation" (NOP) when the Dynamic Flash ECC Configuration bits = 00 (FECCCON<1:0> (DVCFG0<9:8>)), which enables ECC at all times. For all other FECCCON<1:0> bit settings, this command will execute, but will not write the ECC bits for the word and can cause DED errors if dynamic Flash ECC is enabled (FECCCON<1:0> = 01). Refer to Section 52. "Flash Program Memory with Support for Live Update" (DS60001193) for information regarding ECC and Flash programming.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        |                   | DATA<31:24>       |                   |                   |                   |                   |                  |                  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        | DATA<23:16>       |                   |                   |                   |                   |                   |                  |                  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.6         | DATA<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | DATA<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |

## REGISTER 11-12: USBFIFOX: USB FIFO DATA REGISTER 'x' ('x' = 0-7)

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 DATA<31:0>: USB Transmit/Receive FIFO Data bits

Writes to this register loads data into the TxFIFO for the corresponding endpoint. Reading from this register unloads data from the RxFIFO for the corresponding endpoint.

Transfers may be 8-bit, 16-bit or 32-bit as required, and any combination of access is allowed provided the data accessed is contiguous. However, all transfers associated with one packet must be of the same width so that data is consistently byte-, word- or double-word aligned. The last transfer may contain fewer bytes than the previous transfers in order to complete an odd-byte or odd-word transfer.

## REGISTER 11-29: USBLPMR2: USB LINK POWER MANAGEMENT CONTROL REGISTER 2

## bit 0 LPMSTIF: LPM STALL Interrupt Flag bit

#### When in Device mode:

- 1 = A LPM transaction was received and the USB Module responded with a STALL

- 0 = No Stall condition

#### When in Host mode:

- 1 = A LPM transaction was transmitted and the device responded with a STALL

- 0 = No Stall condition

# PIC32MZ Embedded Connectivity (EC) Family

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24     |                   | PSINTV<31:24>     |                   |                   |                   |                   |                  |                  |  |  |

| 00.40     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16     | PSINTV<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45-0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8      | PSINTV<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0       | R-0               | R-0               | R-0               | R-0               | R-0               | R-y               | R-y              | R-y              |  |  |

|           |                   | PSINTV<7:0>       |                   |                   |                   |                   |                  |                  |  |  |

## REGISTER 15-7: DMTPSINTV: POST STATUS CONFIGURE DMT INTERVAL STATUS REGISTER

| Legend:           |                  | y = Value set from Co | onfiguration bits on POR |

|-------------------|------------------|-----------------------|--------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented I   | bit, read as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown       |

bit 31-8 **PSINTV<31:0>:** DMT Window Interval Configuration Status bits

This is always the value of the DMTINTV<2:0> bits in the DEVCFG1 Configuration register.

| Bit<br>Range   | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|----------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |

| 31:24 WDTCLRKE |                   |                   |                   |                   | EY<15:8>          |                   |                  |                  |

| 00.40          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |

| 23:16          | WDTCLRKEY<7:0>    |                   |                   |                   |                   |                   |                  |                  |

| 45.0           | R/W-y             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8           | 0N <sup>(1)</sup> | _                 | _                 | _                 | —                 | _                 | _                | —                |

| 7.0            | U-0               | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | U-0              |

| 7:0            |                   |                   | S                 | WDTWINEN          | —                 |                   |                  |                  |

## REGISTER 16-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                        |                    |  |  |

|-------------------|-----------------------------------------------|------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, | read as '0'        |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared   | x = Bit is unknown |  |  |

bit 31-16 WDTCLRKEY<15:0>: Watchdog Timer Clear Key bits To clear the Watchdog Timer to prevent a time-out, software must write the value 0x5743 to this location

- using a single 16-bit write.

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1)</sup> 1 = The WDT is enabled 0 = The WDT is disabled

- bit 14-7 Unimplemented: Read as '0'

bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> Configuration bits in DEVCFG1.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 Unimplemented: Read as '0'

- **Note 1:** This bit only has control when FWDTEN (DEVCFG1<23>) = 0.

The timer source for each Input Capture module depends on the setting of the ICACLK bit in the CFGCON register. The available configurations are shown in Table 17-1.

| TABLE 17-1: | TIMER SOURCE   |

|-------------|----------------|

|             | CONFIGURATIONS |

| Input Capture<br>Module | Timerx                  | Timery  |  |  |  |  |  |

|-------------------------|-------------------------|---------|--|--|--|--|--|

| ICACLK (CFGCC           | <b>N&lt;17&gt;) =</b> 0 |         |  |  |  |  |  |

| IC1                     | Timer2                  | Timer3  |  |  |  |  |  |

| •                       | •                       | •       |  |  |  |  |  |

| •                       | •                       | •       |  |  |  |  |  |

| •                       | •                       | •       |  |  |  |  |  |

| IC9                     | Timer 2                 | Timer 3 |  |  |  |  |  |

| ICACLK (CFGCC           | ICACLK (CFGCON<17>) = 1 |         |  |  |  |  |  |

| IC1                     | Timer4                  | Timer5  |  |  |  |  |  |

| IC2                     | Timer4                  | Timer5  |  |  |  |  |  |

| IC3                     | Timer4                  | Timer5  |  |  |  |  |  |

| IC4                     | Timer2                  | Timer3  |  |  |  |  |  |

| IC5                     | Timer2                  | Timer3  |  |  |  |  |  |

| IC6                     | Timer2                  | Timer3  |  |  |  |  |  |

| IC7                     | Timer6                  | Timer7  |  |  |  |  |  |

| IC8                     | Timer6                  | Timer7  |  |  |  |  |  |

| IC9                     | Timer6                  | Timer7  |  |  |  |  |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31.24        |                   | ADCAL<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 23:16        | ADCAL<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15:8         | ADCAL<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

|              |                   |                   |                   | ADCAI             | <7:0>             |                   |                  | ADCAL<7:0>       |  |  |  |  |  |  |  |

## **REGISTER 28-19:** AD1CALx: ADC1 CALIBRATION REGISTER 'x' ('x' = 1-5)

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 ADCAL<31:0>: Calibration Data for the ADC Module bits

This data must be copied from the corresponding DEVADCx register. Refer to **Section 34.1** "**Configuration Bits**" for more information.

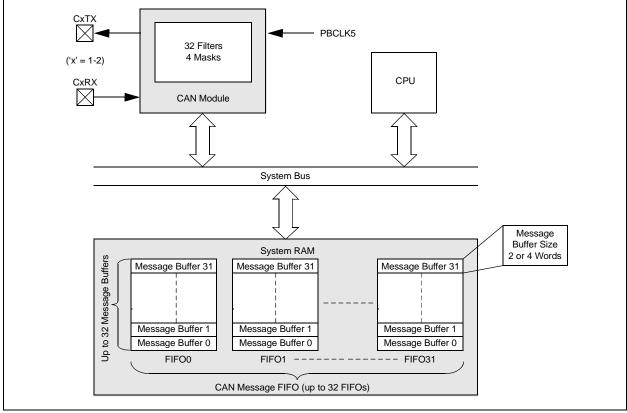

# 29.0 CONTROLLER AREA NETWORK (CAN)

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 34. "Controller Area Network (CAN)" (DS60001154), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Controller Area Network (CAN) module supports the following key features:

- Standards Compliance:

- Full CAN 2.0B compliance

- Programmable bit rate up to 1 Mbps

- Message Reception and Transmission:

- 32 message FIFOs

- Each FIFO can have up to 32 messages for a total of 1024 messages

- FIFO can be a transmit message FIFO or a receive message FIFO

- User-defined priority levels for message FIFOs used for transmission

- 32 acceptance filters for message filtering

- Four acceptance filter mask registers for message filtering

- Automatic response to remote transmit request

DeviceNet<sup>™</sup> addressing support

- Additional Features:

- Loopback, Listen All Messages and Listen Only modes for self-test, system diagnostics and bus monitoring

- Low-power operating modes

- CAN module is a bus master on the PIC32 System Bus

- Use of DMA is not required

- Dedicated time-stamp timer

- Dedicated DMA channels

- Data-only Message Reception mode

Figure 29-1 illustrates the general structure of the CAN module.

Note: To avoid cache coherency problems on devices with L1 cache, CAN buffers must only be allocated or accessed from the KSEG1 segment.

# FIGURE 29-1: PIC32 CAN MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |

| 31:24        | —                 | _                 | _                 |                   | ABAT              | F                 | REQOP<2:0>       | >                |

| 00.40        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 23:16        | OPMOD<2:0>        |                   |                   | CANCAP            | —                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDLE             | -                 | CANBUSY           | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 |                   |                   |                   |                   | DNCNT<4:0>        |                  |                  |

## REGISTER 29-1: CICON: CAN MODULE CONTROL REGISTER

| Legend:               | HC = Hardware Clear        | S = Settable bit     |                  |  |

|-----------------------|----------------------------|----------------------|------------------|--|

| R = Readable bit      | W = Writable bit           | P = Programmable bit | r = Reserved bit |  |

| U = Unimplemented bit | -n = Bit Value at POR: ('0 | ), '1', x = Unknown) |                  |  |

#### bit 31-28 Unimplemented: Read as '0'

#### bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

#### bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved Do not use

- 101 = Reserved Do not use

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

#### bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

#### bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 **ON:** CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

| REGISTE   | R 29-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4 (CONTINUED)                                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

| bit 15    | FLTEN17: Filter 13 Enable bit                                                                                            |

|           | 1 = Filter is enabled                                                                                                    |

|           | 0 = Filter is disabled                                                                                                   |

| bit 14-13 | MSEL17<1:0>: Filter 17 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected                                                       |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 12-8  | FSEL17<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                               |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                               |

| bit 7     | FLTEN16: Filter 16 Enable bit                                                                                            |

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                                                          |

| bit 6-5   | MSEL16<1:0>: Filter 16 Mask Select bits                                                                                  |

| DIL 0-5   | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected                                                                                          |

|           | 01 = Acceptance Mask 1 selected                                                                                          |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 4-0   | FSEL16<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

|           |                                                                                                                          |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                   |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN23           | MSEL23<1:0>       |                   | FSEL23<4:0>       |                   |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN22           | MSEL22<1:0>       |                   | FSEL22<4:0>       |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN21           | MSEL2             | :1<1:0>           |                   | F                 | SEL21<4:0>        |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN20           | MSEL2             | 0<1:0>            | FSEL20<4:0>       |                   |                   |                  |                  |

## **REGISTER 29-15: CIFLTCON5: CAN FILTER CONTROL REGISTER 5**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

|-------------------|------------------|-----------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

| bit 31    | FLTEN23: Filter 23 Enable bit                                                                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                   |

| bit 30-29 | MSEL23<1:0>: Filter 23 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected                                                       |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 28-24 | FSEL23<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           |                                                                                                                          |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN22: Filter 22 Enable bit                                                                                            |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                   |

| bit 22-21 | MSEL22<1:0>: Filter 22 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected                                                       |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 20-16 | FSEL22<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

|           |                                                                                                                          |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN27           | MSEL27<1:0>       |                   | FSEL27<4:0>       |                   |                   |                  |                  |

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN26           | MSEL26<1:0>       |                   | FSEL26<4:0>       |                   |                   |                  |                  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | FLTEN25           | MSEL2             | 5<1:0>            |                   |                   | FSEL25<4:0>       |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN24           | MSEL2             | 4<1:0>            |                   |                   | FSEL24<4:0>       |                  |                  |

## REGISTER 29-16: CIFLTCON6: CAN FILTER CONTROL REGISTER 6

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | FLTEN27: Filter 27 Enable bit                                                             |

|-----------|-------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled                                                                     |

|           | 0 = Filter is disabled                                                                    |

| bit 30-29 | MSEL27<1:0>: Filter 27 Mask Select bits                                                   |

|           | 11 = Acceptance Mask 3 selected                                                           |

|           | 10 = Acceptance Mask 2 selected                                                           |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                        |

| bit 28-24 | FSEL27<4:0>: FIFO Selection bits                                                          |

| 511 20 24 | 11111 = Message matching filter is stored in FIFO buffer 31                               |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                               |

|           | •                                                                                         |

|           | •                                                                                         |

|           | •                                                                                         |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                |

| bit 23    | FLTEN26: Filter 26 Enable bit                                                             |

|           | 1 = Filter is enabled                                                                     |

|           | 0 = Filter is disabled                                                                    |

| bit 22-21 | MSEL26<1:0>: Filter 26 Mask Select bits                                                   |

|           | <ul><li>11 = Acceptance Mask 3 selected</li><li>10 = Acceptance Mask 2 selected</li></ul> |

|           | 01 = Acceptance Mask 2 selected                                                           |

|           | 00 = Acceptance Mask 0 selected                                                           |

| bit 20-16 | FSEL26<4:0>: FIFO Selection bits                                                          |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                               |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                               |

|           | •                                                                                         |

|           | •                                                                                         |

|           | •                                                                                         |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                |

| Note:     | The bits in this register can only be modified if the corresponding fil                   |

|           |                                                                                           |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------|--|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |

| 31:24     | PTV<15:8>         |                   |                   |                   |                   |                   |                  |                     |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |

| 23:16     | PTV<7:0>          |                   |                   |                   |                   |                   |                  |                     |  |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0               |  |

| 15:8      | ON                | —                 | SIDL              | _                 | _                 | _                 | TXRTS            | RXEN <sup>(1)</sup> |  |

| 7:0       | R/W-0             | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0               |  |

|           | AUTOFC            | —                 | _                 | MANFC             | _                 | _                 | _                | BUFCDEC             |  |

## REGISTER 30-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

|           | PAUSE Timer Value used for Flow Control.<br>This register should only be written when RXEN (ETHCON1<8>) is not set.                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | These bits are only used for Flow Control operations.                                                                                                                                                                                                                                                     |

| bit 15    | ON: Ethernet ON bit                                                                                                                                                                                                                                                                                       |

|           | <ul><li>1 = Ethernet module is enabled</li><li>0 = Ethernet module is disabled</li></ul>                                                                                                                                                                                                                  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                |

| bit 13    | SIDL: Ethernet Stop in Idle Mode bit                                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = Ethernet module transfers are paused during Idle mode</li> <li>0 = Ethernet module transfers continue during Idle mode</li> </ul>                                                                                                                                                            |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                |

| bit 9     | TXRTS: Transmit Request to Send bit                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Activate the TX logic and send the packet(s) defined in the TX EDT</li> <li>0 = Stop transmit (when cleared by software) or transmit done (when cleared by hardware)</li> </ul>                                                                                                              |

|           | After the bit is written with a '1', it will clear to a '0' whenever the transmit logic has finished transmitting the requested packets in the Ethernet Descriptor Table (EDT). If a '0' is written by the CPU, the transmit logic finishes the current packet's transmission and then stops any further. |

|           | This bit only affects TX operations.                                                                                                                                                                                                                                                                      |

| bit 8     | RXEN: Receive Enable bit <sup>(1)</sup>                                                                                                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                                                                                                           |

- 1 = Enable RX logic, packets are received and stored in the RX buffer as controlled by the filter configuration

- 0 = Disable RX logic, no packets are received in the RX buffer

This bit only affects RX operations.

PTV<15:0>: PAUSE Timer Value bits

bit 31-16

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

## 36.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 36.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 36.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 36.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 36.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

| DC CHARACTERISTICS: I/O PIN C |      |                                                                                                                                                                                                                                                                                                    |      | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |       |                                                         |  |  |

|-------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------------------|--|--|

| Param.                        | Sym. | Characteristic                                                                                                                                                                                                                                                                                     | Min. | Тур.                                                                                                                                                    | Max. | Units | Conditions <sup>(1)</sup>                               |  |  |

| DO20a                         | Vон1 | Output High Voltage<br>I/O Pins:<br>4x Source Driver Pins -<br>RA3, RA9, RA10, RA14, RA15<br>RB0-7, RB11, RB13<br>RC12-RC15<br>RD0, RD6-RD7, RD11, RD14<br>RE8, RE9<br>RF2, RF3, RF8<br>RG15<br>RH0, RH1, RH4-RH6, RH8-RH13<br>RJ0-RJ2, RJ8, RJ9, RJ11                                             | 1.5  | _                                                                                                                                                       |      | V     | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$   |  |  |

|                               |      |                                                                                                                                                                                                                                                                                                    | 2.0  | —                                                                                                                                                       |      | V     | IOH $\geq$ -12 mA, VDD = 3.3                            |  |  |

|                               |      |                                                                                                                                                                                                                                                                                                    | 3.0  | _                                                                                                                                                       | _    | V     | Iон ≥ -7 mA, Vdd = 3.3V                                 |  |  |

|                               |      | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins -<br>RA0-RA2, RA4, RA5<br>RB8-RB10, RB12, RB14, RB15<br>RC1-RC4<br>RD1-RD5, RD9, RD10, RD12, RD13, RD15<br>RE4-RE7<br>RF0, RF4, RF5, RF12, RF13<br>RG0, RG1, RG6-RG9<br>RH2, RH3, RH7, RH14, RH15<br>RJ3-RJ7, RJ10, RJ12-RJ15<br>RK0-RK7 | 1.5  |                                                                                                                                                         |      | V     | $IOH \ge -22 \text{ mA}, \text{ VDD} = 3.3 \text{ VDD}$ |  |  |

|                               |      |                                                                                                                                                                                                                                                                                                    | 2.0  |                                                                                                                                                         |      | V     | ІОН ≥ -18 mA, VDD = 3.3\                                |  |  |

|                               |      |                                                                                                                                                                                                                                                                                                    | 3.0  |                                                                                                                                                         |      | V     | IOH ≥ -10 mA, VDD = 3.3\                                |  |  |

|                               |      | Output High Voltage<br>I/O Pins:<br>12x Source Driver Pins -<br>RA6, RA7<br>RE0-RE3<br>RF1<br>RG12-RG14                                                                                                                                                                                            | 1.5  | _                                                                                                                                                       | _    | V     | $IOH \ge -32 \text{ mA}, \text{ VDD} = 3.3 \text{ VDD}$ |  |  |

|                               |      |                                                                                                                                                                                                                                                                                                    | 2.0  | —                                                                                                                                                       | —    | V     | $IOH \ge -25 \text{ mA}, \text{ VDD} = 3.3 \text{ VDD}$ |  |  |

|                               |      |                                                                                                                                                                                                                                                                                                    | 3.0  | _                                                                                                                                                       | _    | V     | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{ VDD}$ |  |  |

## TABLE 37-11: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS (CONTINUED)

Note 1: Parameters are characterized, but not tested.

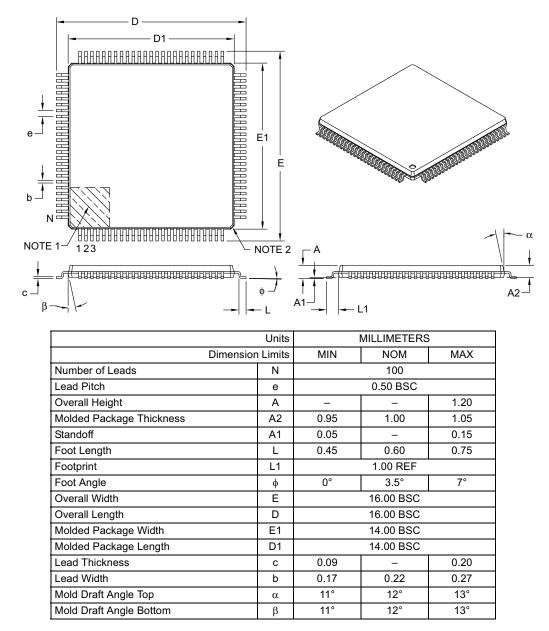

## 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B

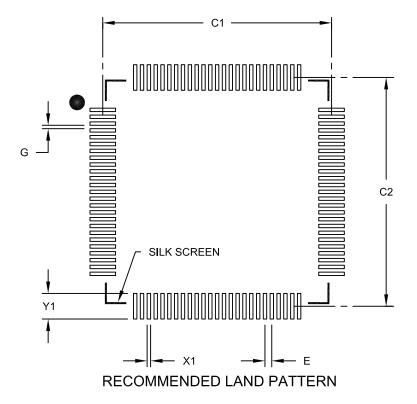

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                     |        | MILLIMETERS |          |      |

|---------------------------|--------|-------------|----------|------|

| Dimension                 | Limits | MIN         | NOM      | MAX  |

| Contact Pitch             | E      |             | 0.40 BSC |      |

| Contact Pad Spacing       | C1     |             | 13.40    |      |

| Contact Pad Spacing       | C2     |             | 13.40    |      |

| Contact Pad Width (X100)  | X1     |             |          | 0.20 |

| Contact Pad Length (X100) | Y1     |             |          | 1.50 |

| Distance Between Pads     | G      | 0.20        |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

| Section Name                                                  | Update Description                                                                                                                                                    |  |  |  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 28.0 "12-bit Pipelined Analog-to-                             | Figure 28-1, Figure 28-2, and Figure 28-3 were updated.                                                                                                               |  |  |  |

| Digital Converter (ADC)"                                      | Register names were updated in the ADC Register Map (see Table 28-1).                                                                                                 |  |  |  |

|                                                               | The OVRSAM<2:0> bit values were updated (see Register 28-14).                                                                                                         |  |  |  |

| 34.0 "Special Features"                                       | The DEVCFG3/ADEVCFG3 register was updated (see Register 34-6).                                                                                                        |  |  |  |

| 37.0 "Electrical Characteristics"                             | Various electrical specifications were updated, including:                                                                                                            |  |  |  |

|                                                               | • The minimum value for parameter DC10 (VDD) in the DC Temperature and Voltage Specifications was updated (see Table 37-4).                                           |  |  |  |

|                                                               | • The minimum and maximum values for parameter BO10 (VBOR) were updated in the BOR Electrical Characteristics (see Table 37-4).                                       |  |  |  |

|                                                               | • Updated the third and fourth bullet list items in Note 2 in DC Characteristics:<br>Operating Current (IDD) (see Table 37-6).                                        |  |  |  |

|                                                               | • Updated the third and fourth bullet list items in Note 1 in DC Characteristics: Idle Current (IIDLE) (see Table 37-7).                                              |  |  |  |

|                                                               | • Updated the third and fourth bullet list items in Note 1in DC Characteristics: Power-Down Current (IPD) (see Table 37-8).                                           |  |  |  |

|                                                               | <ul> <li>Added Note 6 and updated parameters DI20, DI28a, DI28b, DI30, and<br/>DI31 in DC Characteristics: I/O Pin Input Specifications (see Table 37-9).</li> </ul>  |  |  |  |

|                                                               | <ul> <li>Added DC Characteristics: I/O Pin Input Injection Current Specifications<br/>(see Table 37-10).</li> </ul>                                                   |  |  |  |

|                                                               | <ul> <li>Added parameter DO50 to Capacitive Loading Requirements on Output<br/>Pins (see Table 37-15).</li> </ul>                                                     |  |  |  |

|                                                               | • Note 3 was added and the Conditions were updated for parameter OS42 in the External Clock Timing Requirements (see Table 37-16).                                    |  |  |  |

|                                                               | <ul> <li>Updated the Minimum value for parameter OS51 (Fsys) in the System<br/>Timing Requirements (see Table 37-17).</li> </ul>                                      |  |  |  |

|                                                               | <ul> <li>Added parameter OS54a and updated the Maximum value for parameter<br/>OS50 in the PLL Clock Timing Specifications (see Table 37-18).</li> </ul>              |  |  |  |

|                                                               | <ul> <li>The Internal Backup FRC (BFRC) Accuracy specification was added<br/>(see Table 37-21).</li> </ul>                                                            |  |  |  |

|                                                               | <ul> <li>The SQI Input and Output Timing Characteristics diagram were updated<br/>(see Figure 37-14 and Figure 37-15).</li> </ul>                                     |  |  |  |

|                                                               | <ul> <li>The SQI Timing Requirements were updated (see Table 37-33).</li> </ul>                                                                                       |  |  |  |

|                                                               | <ul> <li>Parameter AD13 was removed (see Table 37-37).</li> </ul>                                                                                                     |  |  |  |

|                                                               | • The Min. and Max. values for parameter TS12 and the Conditions for parameter TS13 and TS14 in the Temperature Sensor Specifications were updated (see Table 36-39). |  |  |  |

| 38.0 "AC and DC Characteristics<br>Graphs"                    | Updated Typical Temperature Sensor Voltage (see Figure 38-7).                                                                                                         |  |  |  |

| Appendix A: "Migrating from<br>PIC32MX5XX/6XX/7XX to PIC32MZ" | New appendix for migrating to PIC32MZ devices was added.                                                                                                              |  |  |  |

## TABLE B-1: MAJOR SECTION UPDATES (CONTINUED)

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Pin Count<br>Tape and Reel Flag<br>Temperature Range | (if applicable)                                                                                                                                                                                                                                                                                                                                                                                                      | Example:<br>PIC32MZ2048ECH144-I/PT:<br>Embedded Connectivity PIC32,<br>MIPS32 <sup>®</sup> microAptiv™ MPU core,<br>2048 KB program memory,<br>144-pin, Industrial temperature,<br>TQFP package. |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash Memory Fa                                      | mily                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                  |

| Architecture                                         | MZ = MIPS32 <sup>®</sup> microAptiv <sup>™</sup> MPU Core                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                  |

| Flash Memory Size                                    | 0512 = 512 KB<br>1024 = 1024 KB<br>2048 = 2048 KB                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                  |

| Family                                               | EC = Embedded Connectivity Microcontroller Family                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                  |

| Key Feature                                          | <ul> <li>E = PIC32 EC Family Features (no CAN, no Crypto)</li> <li>F = PIC32 EC Family Features (CAN, no Crypto)</li> <li>G = PIC32 EC Family Features (no CAN, no Crypto)</li> <li>H = PIC32 EC Family Features (CAN, no Crypto)</li> <li>K = PIC32 EC Family Features (Crypto and CAN)</li> <li>M = PIC32 EC Family Features (Crypto and CAN)</li> </ul>                                                           |                                                                                                                                                                                                  |

| Pin Count                                            | 064 = 64-pin<br>100 = 100-pin<br>124 = 124-pin<br>144 = 144-pin                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                  |

| Temperature Range                                    | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                  |

| Package                                              | MR = 64-Lead (9x9x0.9 mm) QFN (Plastic Quad Flatpack)<br>PT = 64-Lead (10x10x1 mm) TQFP (Thin Quad Flatpack)<br>PT = 100-Lead (12x12x1 mm) TQFP (Thin Quad Flatpack)<br>PF = 100-Lead (14x14x1 mm) TQFP (Thin Quad Flatpack)<br>TL = 124-Lead (9x9x0.9 mm) VTLA (Very Thin Leadless Array)<br>PH = 144-Lead (16x16x1 mm) TQFP (Thin Quad Flatpack)<br>PL = 144-Lead (20x20x1.40 mm) LQFP (Low Profile Quad Flatpack) |                                                                                                                                                                                                  |

| Pattern                                              | Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)<br>ES = Engineering Sample                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                  |