Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 78                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

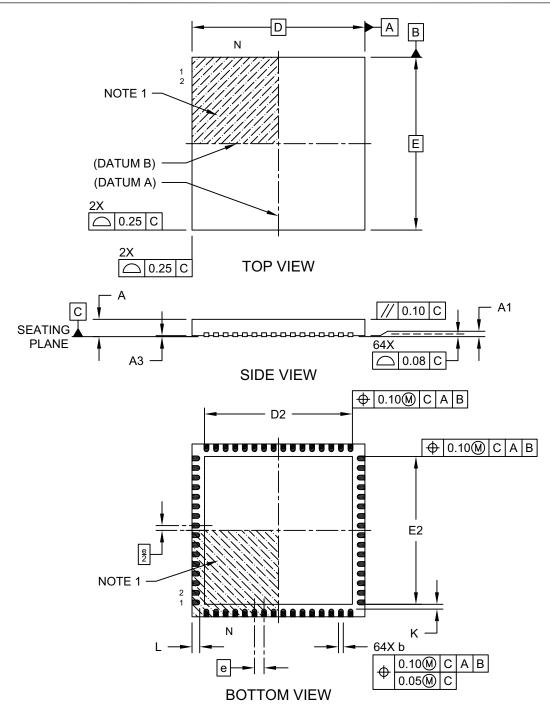

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048ecm100t-i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Referenced Sources**

This device data sheet is based on the following individual sections of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access the following documents, refer |

|-------|------------------------------------------|

|       | to the Documentation > Reference         |

|       | Manuals section of the Microchip PIC32   |

|       | website: http://www.microchip.com/pic32. |

- Section 1. "Introduction" (DS60001127)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 18. "12-bit Pipelined Analog-to-Digital Converter (ADC)" (DS60001194)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 35. "Ethernet Controller" (DS60001155)

- Section 41. "Prefetch Module for Devices with L1 CPU Cache" (DS60001183)

- Section 42. "Oscillators with Enhanced PLL" (DS60001250)

- Section 46. "Serial Quad Interface (SQI)" (DS60001244)

- Section 47. "External Bus Interface (EBI)" (DS60001245)

- Section 48. "Memory Organization and Permissions" (DS60001214)

- Section 49. "Crypto Engine (CE) and Random Number Generator (RNG)" (DS60001246)

- Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192)

- Section 51. "Hi-Speed USB with On-The-Go (OTG)" (DS60001326)

- Section 52. "Flash Program Memory with Support for Live Update" (DS60001193)

### TABLE 4-19: SYSTEM BUS TARGET 11 REGISTER MAP

| sss                         |                  |           |       |       |       |         |          |       |       |      | Bits         |       |          |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|---------|----------|-------|-------|------|--------------|-------|----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11    | 26/10 | 25/9  | 24/8 | 23/7         | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

| AC20                        | SBT11ELOG1       | 31:16     | MULTI | —     | _     |         |          | CODE  | <3:0> |      |              |       |          | —    | -      | _      | _       | 0000   |               |

| 7020                        | SBIIIEE001       | 15:0      |       | -     |       | INI     | TID<7:0> |       | -     |      |              | REGIO | N<3:0>   |      | —      | C      | MD<2:0> | -      | 0000          |

| AC24                        | SBT11ELOG2       | 31:16     | _     | _     | —     | -       | -        | -     | —     | -    | _            | _     | _        | _    | —      | -      | —       | —      | 0000          |

| A024                        | 3BTTTEE002       | 15:0      | _     | _     | —     | -       | -        | -     | —     | -    | _            | _     | _        | _    | —      | -      | GROU    | P<1:0> | 0000          |

| AC28                        | SBT11ECON        | 31:16     | _     | _     | —     | -       | -        | -     | —     | ERRP | _            | _     | _        | _    | —      | -      | —       | —      | 0000          |

| AC20                        | SBITTLEON        | 15:0      | _     | _     | —     | -       | -        | -     | —     | -    | _            | _     | _        | _    | —      | -      | —       | —      | 0000          |

| AC30                        | SBT11ECLRS       | 31:16     | _     | _     | —     | _       | _        | _     | —     | _    | _            | _     | —        | _    | —      | _      |         | —      | 0000          |

| 7030                        | SBITTECERS       | 15:0      | _     | —     | —     | _       | _        | _     | —     | _    | —            | _     | —        | _    | —      | _      |         | CLEAR  | 0000          |

| AC38                        | SBT11ECLRM       | 31:16     | _     | —     | —     | _       | _        | _     | —     | _    | —            | _     | —        | _    | —      | _      |         | —      | 0000          |

| AC30                        | SBITTECERM       | 15:0      | _     | _     |       | —       | —        | _     | —     | —    | _            | _     |          | _    | _      | _      | —       | CLEAR  | 0000          |

| AC40                        | SBT11REG0        | 31:16     |       |       |       |         |          |       | -     | BA   | SE<21:6>     |       |          |      |        |        |         | -      | xxxx          |

| 7040                        | SBITIKEOU        | 15:0      |       | -     | BA    | SE<5:0> |          |       | PRI   | _    |              |       | SIZE<4:0 | >    |        | _      |         | —      | xxxx          |

| AC50                        | SBT11RD0         | 31:16     | _     | —     | —     | _       | _        | _     | —     | _    | —            | _     | —        | _    | —      | _      |         | —      | xxxx          |

| 7000                        | SETTINED         | 15:0      | _     | —     | —     | _       | _        | _     | —     | _    | —            | _     | —        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| AC58                        | SBT11WR0         | 31:16     | _     | —     | —     | _       | _        | _     | —     | _    | —            | _     | —        | _    | —      | _      |         | —      | xxxx          |

| 7000                        | OBTITWING        | 15:0      | _     |       | _     | —       | —        | —     | —     | —    | —            | —     |          | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| AC60                        | SBT11REG1        | 31:16     |       |       |       |         |          |       | -     | BA   | BASE<21:6> x |       |          |      |        |        | xxxx    |        |               |

| 7000                        | SBITIKEOT        | 15:0      |       | -     | BA    | SE<5:0> |          |       | PRI   | _    | SIZE<4:0>    |       |          |      | —      | xxxx   |         |        |               |

| AC70                        | SBT11RD1         | 31:16     | _     | _     | _     | _       | _        | _     | _     | _    | —            | _     | _        | _    | _      | _      |         |        | xxxx          |

| 7010                        |                  | 15:0      | _     | _     | _     | _       | _        | _     | _     | _    | —            | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| AC78                        | SBT11WR1         | 31:16     | _     | _     | _     | _       | _        | _     | _     | _    | —            | _     | _        | _    | _      | _      |         | —      | xxxx          |

| 7010                        | Continued        | 15:0      |       |       | —     |         | -        | -     | —     | -    | _            | _     | —        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

DS60001191G-page 86

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note:** For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

### TABLE 4-20: SYSTEM BUS TARGET 12 REGISTER MAP

| 17 ( )                      |                  |           |       | 000   |       |         |          |       |       |      |          |       |          |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|---------|----------|-------|-------|------|----------|-------|----------|------|--------|--------|---------|--------|---------------|

| ess                         |                  |           |       |       |       | _       |          |       |       |      | Bits     |       |          |      |        |        |         |        |               |

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

|                             |                  | 31:16     | MULTI | —     | -     |         |          | CODE  | <3:0> |      | _        | _     | —        | —    | —      |        | —       |        | 0000          |

| B020                        | SBT12ELOG1       | 15:0      |       |       |       | INI     | ΓID<7:0> |       |       |      |          | REGIO | N<3:0>   |      | _      | С      | MD<2:0> |        | 0000          |

| DO04                        |                  | 31:16     | _     | _     | —     | _       | _        | _     | _     | _    | _        | _     | _        | _    | _      | _      | _       | _      | 0000          |

| B024                        | SBT12ELOG2       | 15:0      | —     | _     | _     | _       | _        | _     | _     | _    | -        | _     | _        | _    | _      | _      | GROU    | P<1:0> | 0000          |

| B028                        | SBT12ECON        | 31:16     | —     | _     | _     | _       | _        | _     | _     | ERRP | -        | _     | _        | _    | _      | _      | _       | _      | 0000          |

| DU20                        | SBITZECON        | 15:0      | —     | _     | _     | _       | _        | _     | _     | _    | -        | _     | _        | _    | _      | _      | _       | _      | 0000          |

| P020                        | SBT12ECLRS       | 31:16     |       | -     | —     | _       | —        | —     |       | -    | _        | —     | _        | —    | —      | _      | _       |        | 0000          |

| Б030                        | SBI IZECLKS      | 15:0      |       | —     | _     |         | —        | —     |       |      | _        | —     | —        | _    | _      |        | —       | CLEAR  | 0000          |

| D020                        | SBT12ECLRM       | 31:16     |       | —     | _     |         | —        | —     |       |      | _        | —     | —        | _    | _      |        | —       |        | 0000          |

| DU30                        | 3BT 12ECLRIVI    | 15:0      |       | —     | _     |         | —        | —     |       |      | _        | —     | —        | _    | _      |        | —       | CLEAR  | 0000          |

| B040                        | SBT12REG0        | 31:16     |       |       |       |         |          |       |       | BA   | SE<21:6> |       |          |      |        |        |         |        | xxxx          |

| D040                        | SBITZREGU        | 15:0      |       |       | BA    | SE<5:0> |          |       | PRI   |      |          |       | SIZE<4:0 | >    |        |        | —       |        | xxxx          |

| B050                        | SBT12RD0         | 31:16     |       | —     | _     |         | —        | —     |       |      | _        | —     | —        | _    | _      |        | —       |        | xxxx          |

| D030                        | SB112KD0         | 15:0      |       | -     | —     |         |          | -     |       |      | _        | —     | —        | -    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| B058                        | SBT12WR0         | 31:16     |       | -     | —     |         |          | -     |       |      | _        | —     | —        | -    |        |        | _       | _      | xxxx          |

| 6056                        | 3BT12WR0         | 15:0      |       |       | _     |         | -        | -     |       |      | _        | _     | _        | -    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

# 5.1 Flash Control Registers

# TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | đ             |           | Bits                                                                                                    |       |        |       |       |      |          |           |      |      | s    |      |      |        |      |            |

|-----------------------------|------------------------|---------------|-----------|---------------------------------------------------------------------------------------------------------|-------|--------|-------|-------|------|----------|-----------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range     | 31/15     | 30/14                                                                                                   | 29/13 | 28/12  | 27/11 | 26/10 | 25/9 | 24/8     | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| 0600                        | NVMCON <sup>(1)</sup>  | 31:16         | —         |                                                                                                         |       |        |       |       |      |          |           |      | 0000 |      |      |      |        |      |            |

| 0000                        | NUMCON                 | 15:0          | WR        | WREN                                                                                                    | WRERR | LVDERR | —     | —     | —    | _        | SWAP      | _    | —    | —    |      | NVMO | P<3:0> |      | 0000       |

| 0610                        | NVMKEY                 | 31:16         |           | NVMKEY<31:0>                                                                                            |       |        |       |       |      |          |           |      |      |      |      |      |        |      |            |

|                             |                        | 15:0          |           | 0000                                                                                                    |       |        |       |       |      |          |           |      |      |      |      |      |        |      |            |

| 0620                        | NVMADDR <sup>(1)</sup> | 31:16         |           |                                                                                                         |       |        |       |       |      | NVMAD    | DR<31:0>  |      |      |      |      |      |        |      | 0000       |

|                             |                        | 15:0          |           |                                                                                                         |       |        |       |       |      |          |           |      |      |      |      |      |        |      | 0000       |

| 0630                        | NVMDATA0               | 31:16<br>15:0 |           |                                                                                                         |       |        |       |       |      | NVMDA    | TA0<31:0> |      |      |      |      |      |        |      | 0000       |

|                             |                        | 31:16         |           |                                                                                                         |       |        |       |       |      |          |           |      |      |      |      |      |        |      | 0000       |

| 0640                        | NVMDATA1               | 15:0          |           |                                                                                                         |       |        |       |       |      | NVMDA    | TA1<31:0> |      |      |      |      |      |        |      | 0000       |

|                             |                        | 31:16         |           |                                                                                                         |       |        |       |       |      |          |           |      |      |      |      |      |        |      | 0000       |

| 0650                        | NVMDATA2               | 15:0          |           |                                                                                                         |       |        |       |       |      | NVMDA    | TA2<31:0> |      |      |      |      |      |        |      | 0000       |

| 0660                        | NVMDATA3               | 31:16         |           |                                                                                                         |       |        |       |       |      |          | TA3<31:0> |      |      |      |      |      |        |      | 0000       |

| 0000                        | NVINDATA3              | 15:0          |           |                                                                                                         |       |        |       |       |      | INVIVIDA | TA3<31.0> |      |      |      |      |      |        |      | 0000       |

| 0670                        | NVMSRC                 | 31:16         |           |                                                                                                         |       |        |       |       |      | NVMSRC   |           |      |      |      |      |      |        |      | 0000       |

| 0070                        | ADDR                   | 15:0          |           | NVMSRCADDR<31:0> 0000                                                                                   |       |        |       |       |      |          |           |      |      |      |      |      |        |      |            |

| 0680                        | NVMPWP <sup>(1)</sup>  | 31:16         | PWPULOCK  |                                                                                                         |       |        |       |       |      |          |           |      |      |      |      |      |        |      |            |

|                             |                        | 15:0          |           | PWP<15:0> 0000                                                                                          |       |        |       |       |      |          |           |      |      |      |      |      |        |      |            |

| 0690                        | NVMBWP <sup>(1)</sup>  | 31:16         |           | —                                                                                                       | —     | —      |       | —     |      |          | —         | _    | —    | —    |      | —    | —      | —    | 0000       |

|                             |                        | 15:0          | LBWPULOCK | - <u>- LBWP4</u> LBWP3 LBWP2 LBWP1 LBWP0 UBWPULOCK <u>-</u> <u>-</u> UBWP4 UBWP3 UBWP2 UBWP1 UBWP0 9FDF |       |        |       |       |      |          |           |      |      |      |      |      |        |      |            |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range        | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04-04               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 31:24 NVMKEY<31:24> |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 23:16               | NVMKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0                | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 15:8                |                   | •                 |                   | NVMK              | EY<15:8>          |                   |                  |                  |  |  |  |

| 7.0                 | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 7:0                 | NVMKEY<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 5-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

## Legend:

| 8                 |                  |                      |                    |  |

|-------------------|------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

bit 31-0 **NVMKEY<31:0>:** Unlock Register bits These bits are write-only, and read as '0' on any read

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

## REGISTER 5-3: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7                  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|------------------------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R/W-0                              | R/W-0             | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | 1:24 NVMADDR<31:24> <sup>(1)</sup> |                   |                   |                   |                         |                   |                  |                  |  |  |

| 00.40        | R/W-0                              | R/W-0             | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | NVMADDR<23:16> <sup>(1)</sup>      |                   |                   |                   |                         |                   |                  |                  |  |  |

| 45-0         | R/W-0                              | R/W-0             | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                                    | •                 |                   | NVMADE            | DR<15:8> <sup>(1)</sup> |                   |                  |                  |  |  |

| 7.0          | R/W-0                              | R/W-0             | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | NVMADDR<7:0>(1)                    |                   |                   |                   |                         |                   |                  |                  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 NVMADDR<31:0>: Flash Address bits<sup>(1)</sup>

| NVMOP<3:0><br>Selection                                                                                                                                              | Flash Address Bits (NVMADDR<31:0>)                                                     |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|

| Page Erase                                                                                                                                                           | Address identifies the page to erase (NVMADDR<13:0> are ignored).                      |  |  |  |  |  |

| Row Program                                                                                                                                                          | Address identifies the row to program (NVMADDR<11:0> are ignored).                     |  |  |  |  |  |

| Word Program                                                                                                                                                         | Address identifies the word to program (NVMADDR<1:0> are ignored).                     |  |  |  |  |  |

| Quad Word Program                                                                                                                                                    | Address identifies the quad word (128-bit) to program (NVMADDR<3:0> bits are ignored). |  |  |  |  |  |

| <b>Note 1:</b> For all other NVMOP<3:0> bit settings, the Flash address is ignored. See the NVMCON register (Register 5-1) for additional information on these bits. |                                                                                        |  |  |  |  |  |

**Note:** The bits in this register are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

NOTES:

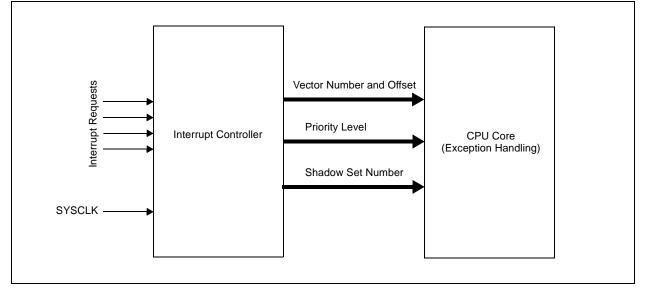

# 7.0 CPU EXCEPTIONS AND INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108) and Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192), which are available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MZ EC devices generate interrupt requests in response to interrupt events from peripheral modules. The Interrupt Controller module exists outside of the CPU and prioritizes the interrupt events before presenting them to the CPU.

The CPU handles interrupt events as part of the exception handling mechanism, which is described in **Section 7.1 "CPU Exceptions"**.

The Interrupt Controller module includes the following features:

- Up to 190 interrupt sources and vectors with dedicated programmable offsets, eliminating the need for redirection

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- Seven shadow register sets that can be used for any priority level, eliminating software context switch and reducing interrupt latency

- Software can generate any interrupt

Figure 7-1 shows the block diagram for the Interrupt Controller and CPU exceptions.

## FIGURE 7-1: CPU EXCEPTIONS AND INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

# PIC32MZ Embedded Connectivity (EC) Family

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | _                 | _                 | _                 | —                 | —                | _                |  |  |  |  |

| 00.40        | R-0, HS           | R-0, HS          | R-0, HS          |  |  |  |  |

| 23:16        | EP7TXIF           | EP6TXIF           | EP5TXIF           | EP4TXIF           | EP3TXIF           | EP2TXIF           | EP1TXIF          | EP0IF            |  |  |  |  |

|              | R/W-0             | R/W-0             | R/W-1             | R-0, HS           | R-0               | R/W-0             | R-0, HC          | R/W-0            |  |  |  |  |

| 15:8         | ISOUPD            | SOFTCONN          | HSEN              | HSMODE            | RESET             | RESUME            | SUSPMODE         | SUSPEN           |  |  |  |  |

|              | _                 | —                 |                   |                   |                   |                   |                  |                  |  |  |  |  |

|              | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   |                   | FUNC<6:0>         |                   |                  |                  |  |  |  |  |

|              | _                 | —                 | _                 | _                 | _                 | —                 | —                | _                |  |  |  |  |

#### REGISTER 11-1: USBCSR0: USB CONTROL STATUS REGISTER 0

| Legend:           | HS = Hardware Settable | HC = Hardware Clearable   |                    |  |  |  |

|-------------------|------------------------|---------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit, re | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |

#### bit 31-24 Unimplemented: Read as '0'

#### bit 23-17 EP7TXIF: Endpoint 'n' TX Interrupt Flag bit

- 1 = Endpoint has a transmit interrupt to be serviced

- 0 = No interrupt event

#### bit 16 **EP0IF:** Endpoint 0 Interrupt bit

- 1 = Endpoint 0 has an interrupt to be serviced

- 0 = No interrupt event

All EPxTX and EP0 bits are cleared when the byte is read. Therefore, these bits must be read independently from the remaining bits in this register to avoid accidental clearing.

#### bit 15 **ISOUPD:** ISO Update bit (*Device mode only; unimplemented in Host mode*)

- 1 = USB module will wait for a SOF token from the time TXPKTRDY is set before sending the packet

- 0 = No change in behavior

This bit only affects endpoints performing isochronous transfers when in *Device mode*. This bit is unimplemented in *Host mode*.

#### bit 14 SOFTCONN: Soft Connect/Disconnect Feature Selection bit

- 1 = The USB D+/D- lines are enabled and active

- 0 = The USB D+/D- lines are disabled and are tri-stated

This bit is only available in Device mode.

#### bit 13 **HSEN:** Hi-Speed Enable bit

- 1 = The USB module will negotiate for Hi-Speed mode when the device is reset by the hub

- 0 = Module only operates in Full-Speed mode

#### bit 12 HSMODE: Hi-Speed Mode Status bit

- 1 = Hi-Speed mode successfully negotiated during USB reset

- 0 = Module is not in Hi-Speed mode

In *Device mode*, this bit becomes valid when a USB reset completes. In *Host mode*, it becomes valid when the RESET bit is cleared.

#### bit 11 **RESET:** Module Reset Status bit

- 1 = Reset signaling is present on the bus

- 0 = Normal module operation

In Device mode, this bit is read-only. In Host mode, this bit is read/write.

#### REGISTER 11-8: USBIENCSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 1-7)

|              |           |                           | ••••              |                  |                  |              |            |           |

|--------------|-----------|---------------------------|-------------------|------------------|------------------|--------------|------------|-----------|

| Bit<br>Range |           |                           | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |              |            |           |

|              | R/W-0     | R/W-0                     | R/W-0             | R/W-0            | R/W-0            | R/W-0        | R/W-0      | R/W-0     |

| 31:24        | AUTOSET   | ISO                       | MODE              |                  |                  | DMAREQMD     | —          | —         |

|              | AUTOSET   | —                         | MODE              | DIMAREQUIN       | FREDATIG         | DIVIAREQIVID | DATAWEN    | DATATGGL  |

|              | R/W-0, HS | R/W-0, HC R/W-0, HS R/W-0 |                   | R/W-0            | R/W-0            | R/W-0, HS    | R/W-0      | R/W-0, HC |

| 23:16        | INCOMPTX  | CLRDT                     | SENTSTALL         | SENDSTALL        | FLUSH            | UNDERRUN     | FIFONE     | TXPKTRDY  |

|              | NAKTMOUT  | GLRDT                     | RXSTALL           | SETUPPKT         | FLUSH            | ERROR        | FIFONE     | INPKIRUT  |

| 45.0         | R/W-0     | R/W-0                     | R/W-0             | R/W-0            | R/W-0            | R/W-0        | R/W-0      | R/W-0     |

| 15:8         |           |                           | MULT<4:0>         |                  |                  | T            | XMAXP<10:8 | >         |

| 7:0          | R/W-0     | R/W-0                     | R/W-0             |                  |                  |              |            |           |

| 7.0          |           |                           |                   |                  |                  |              |            |           |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31 AUTOSET: Auto Set Control bit

- 1 = TXPKTRDY will be automatically set when data of the maximum packet size (value in TXMAXP) is loaded into the TX FIFO. If a packet of less than the maximum packet size is loaded, then TXPKTRDY will have to be set manually.

- 0 = TXPKTRDY must be set manually for all packet sizes

- bit 30 **ISO:** Isochronous TX Endpoint Enable bit (Device mode)

- 1 = Enables the endpoint for Isochronous transfers

- 0 = Disables the endpoint for lsochronous transfers and enables it for Bulk or Interrupt transfers. This bit only has an effect in Device mode. In Host mode, it always returns '0'.

- bit 29 MODE: Endpoint Direction Control bit

- 1 = Endpoint is TX

- 0 = Endpoint is RX

This bit only has any effect where the same endpoint FIFO is used for both TX and RX transactions.

- bit 28 DMAREQEN: Endpoint DMA Request Enable bit

- 1 = DMA requests are enabled for this endpoint

- 0 = DMA requests are disabled for this endpoint

- bit 27 **FRCDATTG:** Force Endpoint Data Toggle Control bit

- 1 = Forces the endpoint data toggle to switch and the data packet to be cleared from the FIFO, regardless of whether an ACK was received.

- 0 = No forced behavior

- bit 26 DMAREQMD: Endpoint DMA Request Mode Control bit

- 1 = DMA Request Mode 1

- 0 = DMA Request Mode 0

This bit must not be cleared either before or in the same cycle as the above DMAREQEN bit is cleared.

- bit 25 DATAWEN: Data Toggle Write Enable bit (Host mode)

- 1 = Enable the current state of the TX Endpoint data toggle (DATATGGL) to be written

- 0 = Disables writing the DATATGGL bit

- bit 24 **DATATGGL:** Data Toggle Control bit (Host mode)

When read, this bit indicates the current state of the TX Endpoint data toggle. If DATAWEN = 1, this bit may be written with the required setting of the data toggle. If DATAWEN = 0, any value written to this bit is ignored.

#### TABLE 12-12: PORTF REGISTER MAP FOR 100-PIN, 124-PIN, AND 144-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |               |               |       |       |      | Bit          | S    |      |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|---------------|---------------|-------|-------|------|--------------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13         | 28/12         | 27/11 | 26/10 | 25/9 | 24/8         | 23/7 | 22/6 | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0500                        | ANSELF                          | 31:16     | _     | -     | —             | —             | _     | —     | —    | —            | _    | -    | —            | -            | _            | _            | _            | —            | 0000          |

| 0000                        | , TOLEI                         | 15:0      | —     | —     | ANSF13        | ANSF12        | —     | —     | —    | —            | —    | _    | —            | —            | _            |              | _            | —            | 3000          |

| 0510                        | TRISF                           | 31:16     | —     | —     | —             | —             | —     | —     | —    | —            | —    | _    | —            | —            | —            | —            | —            | —            | 0000          |

| 0010                        | Indi                            | 15:0      | —     | —     | TRISF13       | TRISF12       | —     | —     | _    | TRISF8       | —    | _    | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | 313F          |

| 0520                        | PORTF                           | 31:16     | —     | —     | —             | —             | —     | —     | -    | —            | —    | _    | —            | -            | _            | _            | _            | —            | 0000          |

| 0520                        | FURT                            | 15:0      | _     | —     | RF13          | RF12          | _     | _     | _    | RF8          | _    | _    | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | xxxx          |

| 0530                        | LATF                            | 31:16     |       | -     | _             | _             |       | _     | _    | _            |      |      | _            |              |              |              |              | _            | 0000          |

| 0550                        | LAII                            | 15:0      | Ι     | _     | LATF13        | LATF12        |       |       | —    | LATF8        | Ι    |      | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 0540                        | ODCF                            | 31:16     |       | _     | —             | —             | -     |       | _    | —            |      | —    | —            | —            | —            | —            | —            | _            | 0000          |

| 0540                        | ODCF                            | 15:0      | Ι     | _     | ODCF13        | ODCF12        |       | _     | _    | ODCF8        |      | _    | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | 0000          |

| 0550                        | CNPUF                           | 31:16     | _     | _     | _             |               | _     | _     | _    | —            | _    | _    | —            | _            | _            | _            | _            | _            | 0000          |

| 0550                        | CNPUF                           | 15:0      | _     | _     | CNPUF13       | CNPUF12       | _     | _     | _    | CNPUF8       | _    | _    | CNPUF5       | CNPUF4       | CNPUF3       | CNPUF2       | CNPUF1       | CNPUF0       | 0000          |

| 0560                        | CNPDF                           | 31:16     | _     | _     | _             |               | _     | _     | _    | —            | _    | _    | —            | _            | _            | _            | _            | _            | 0000          |

| 0560                        | CNPDF                           | 15:0      | _     |       | CNPDF13       | CNPDF12       | _     | _     | _    | CNPDF8       | _    | _    | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | 0000          |

| 0570                        |                                 | 31:16     | _     | _     | —             | —             | _     | _     | _    | —            | _    | -    | _            | -            | -            | _            | -            | _            | 0000          |

| 0570                        | CNCONF                          | 15:0      | ON    | _     | SIDL          |               | _     | _     | _    | —            | _    | -    | _            |              | -            |              |              | _            | 0000          |

| 0500                        |                                 | 31:16     | _     |       | _             | _             | _     | _     | _    | _            | _    |      | _            |              |              |              |              | _            | 0000          |

| 0580                        | CNENF                           | 15:0      | _     | —     | CNIEF13       | CNIEF12       | _     | _     | _    | CNIEF8       | _    | _    | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | 0000          |

|                             |                                 | 31:16     | _     | _     | _             | _             | _     | _     | _    | —            | _    | _    | _            | _            | _            | _            | _            | —            | 0000          |

| 0590                        | CNSTATF                         | 15:0      | _     | _     | CN<br>STATF13 | CN<br>STATF12 | _     | _     | _    | CN<br>STATF8 | _    |      | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | 0000          |

x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal. Legend:

All registers in this table have corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

| REGISTER 20-12: | SQI1STAT1: SQI STATUS REGISTER 1 |

|-----------------|----------------------------------|

|-----------------|----------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |  |

| 22:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        |                   |                   |                   | TXFIFOFR          | EE<7:0>           |                   |                  |                  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 10.0         | —                 |                   | _                 |                   | —                 | —                 | _                | —                |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          | RXFIFOCNT<7:0>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-24 Unimplemented: Read as '0'

bit 23-16 TXFIFOFREE<7:0>: Transmit FIFO Available Word Space bits

bit 15-8 Unimplemented: Read as '0'

bit 7-0 RXFIFOCNT<7:0>: Number of words of read data in the FIFO

| TABLE 22-1: | UART1 THROUGH UART6 REGISTER MAP ( | CONTINUED | ) |

|-------------|------------------------------------|-----------|---|

|             |                                    | CONTINUED | , |

| ess                         |                       | 0                                                                                           |        |         |        |       |        |       |       | Bi                                     | ts                   |         |        |          |          |       |        |       |            |

|-----------------------------|-----------------------|---------------------------------------------------------------------------------------------|--------|---------|--------|-------|--------|-------|-------|----------------------------------------|----------------------|---------|--------|----------|----------|-------|--------|-------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name      | Bit Range                                                                                   | 31/15  | 30/14   | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8                                   | 23/7                 | 22/6    | 21/5   | 20/4     | 19/3     | 18/2  | 17/1   | 16/0  | All Resets |

|                             | U4MODE <sup>(1)</sup> | 31:16                                                                                       | —      | —       | _      |       | —      | —     |       | —                                      | —                    |         | —      |          | —        | —     |        | _     | 0000       |

| 2000                        |                       | 15:0                                                                                        | ON     | —       | SIDL   | IREN  | RTSMD  | _     | UEN   |                                        | WAKE                 | LPBACK  | ABAUD  | RXINV    | BRGH     | PDSE  | L<1:0> | STSEL | 0000       |

| 2610                        | U4STA <sup>(1)</sup>  | 31:16                                                                                       | —      | —       | —      | —     | —      | —     | —     | ADM_EN                                 |                      |         |        | ADDR     |          |       |        |       | 0000       |

| 2010                        |                       | 15:0                                                                                        | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT                                   | URXISE               | EL<1:0> | ADDEN  | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

| 2620                        | U4TXREG               | 31:16                                                                                       | _      | —       | —      | _     | —      | _     | _     | —                                      | —                    | —       | —      | —        | —        | —     | —      | —     | 0000       |

| 2020                        | OTIXILEO              | 15:0                                                                                        | —      | —       | —      | —     | —      | —     | —     | TX8                                    |                      | -       |        | Transmit | Register | -     | -      |       | 0000       |

| 2630                        | U4RXREG               | 31:16                                                                                       | —      | —       | —      | —     | —      | —     | —     | —                                      | —                    | —       | —      | —        | —        | —     | —      | —     | 0000       |

| 2000                        | OHIVINEO              | 15:0                                                                                        | —      | —       | —      | —     | —      | —     | —     | RX8                                    |                      | -       | -      | Receive  | Register | -     | -      |       | 0000       |

| 2640                        | U4BRG <sup>(1)</sup>  | 31:16                                                                                       | —      | —       | _      | _     | —      | —     | —     | —                                      | —                    | —       | —      | -        | —        | —     | —      | _     | 0000       |

| 2040                        | 0401(0)               | 15:0                                                                                        |        |         |        |       |        |       | Bau   | d Rate Gene                            | erator Pres          | caler   |        |          |          |       |        |       | 0000       |

| 2800                        | U5MODE <sup>(1)</sup> | 31:16                                                                                       | _      | _       | _      |       | _      | _     | _     | —                                      | _                    | _       | _      |          | _        | _     | _      |       | 0000       |

| 2000                        | 03WODL V              | 15:0                                                                                        | ON     | _       | SIDL   | IREN  | RTSMD  | —     | UEN   | I<1:0> WAKE LPBACK ABAUD RXINV BRGH PI |                      | PDSE    | L<1:0> | STSEL    | 0000     |       |        |       |            |

| 2810                        | U5STA <sup>(1)</sup>  | 31:16                                                                                       | _      | -       | -      | _     |        | _     | —     | ADM_EN                                 |                      |         |        | ADDR     | R<7:0>   |       |        |       | 0000       |

| 2010                        | 0331A. /              | 15:0                                                                                        | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT                                   | URXISE               | EL<1:0> | ADDEN  | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

| 2820                        | U5TXREG               | 31:16                                                                                       | _      | _       | —      | —     | -      | _     | _     | _                                      | _                    | —       | _      | —        | —        | _     | —      | _     | 0000       |

| 2020                        | USIAREG               | 15:0                                                                                        | _      | -       | -      | _     |        | _     | —     | TX8                                    |                      |         |        | Transmit | Register |       |        |       | 0000       |

| 2830                        | U5RXREG               | 31:16                                                                                       | —      | —       | —      | _     | —      | —     | —     |                                        | —                    | —       | —      | —        | —        | —     | —      | —     | 0000       |

| 2830                        | USKAREG               | 15:0                                                                                        | _      | _       | —      | _     | —      | _     | —     | RX8                                    |                      |         |        | Receive  | Register |       |        |       | 0000       |

| 2840                        | U5BRG <sup>(1)</sup>  | 31:16                                                                                       | _      | _       | _      | -     | _      | —     | _     | —                                      | —                    | —       | —      | —        | _        | _     | —      | _     | 0000       |

| 2840                        | USBKG '               | 15:0                                                                                        |        |         |        |       |        |       | Bau   | d Rate Gene                            | erator Pres          | caler   |        |          |          |       |        |       | 0000       |

| 0 4 00                      | U6MODE <sup>(1)</sup> | 31:16                                                                                       | _      | _       | _      | —     | _      | _     | _     | —                                      | _                    | —       | —      | —        | —        | _     | —      | —     | 0000       |

| 2A00                        | UGINIODE              | 15:0                                                                                        | ON     | _       | SIDL   | IREN  | RTSMD  | —     | UEN   | <1:0>                                  | WAKE                 | LPBACK  | ABAUD  | RXINV    | BRGH     | PDSEI | L<1:0> | STSEL | 0000       |

| 0.40                        | U6STA <sup>(1)</sup>  | 31:16                                                                                       | _      | _       | _      | _     | _      | —     | —     | ADM_EN                                 |                      |         |        | ADDR     | R<7:0>   |       |        |       | 0000       |

| 2A10                        | USTA                  | 15:0                                                                                        | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT                                   | URXISE               | EL<1:0> | ADDEN  | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

|                             |                       | 31:16                                                                                       | _      | —       | —      | _     | _      | _     | —     | —                                      | _                    | —       | —      | -        | _        | —     | —      | -     | 0000       |

| 2A20                        | U6TXREG               | 15:0                                                                                        | _      | _       | _      | _     | _      | _     | _     | TX8                                    |                      |         |        | Transmit | Register |       |        |       | 0000       |

|                             |                       | 31:16                                                                                       | _      | _       | _      | _     | _      | _     | _     | —                                      | _                    | —       | —      | —        | —        | —     | —      | —     | 0000       |

| 2A30                        | U6RXREG               | 15:0                                                                                        | _      | _       | _      | _     |        | _     | _     | RX8                                    | RX8 Receive Register |         |        |          |          |       | 0000   |       |            |

| 0.4.45                      |                       | 31:16                                                                                       | _      | _       | _      | _     | _      | _     | _     |                                        |                      |         |        |          | _        |       |        |       | 0000       |

| 2A40                        | U6BRG <sup>(1)</sup>  | 15:0                                                                                        |        |         |        |       |        |       | Bau   | d Rate Gene                            | erator Pres          | caler   |        |          |          |       |        |       | 0000       |

| Leger                       | · . · ·               | v - unknown value on Reset: unimplemented read as '0' Reset values are shown in hevadecimal |        |         |        |       |        |       |       |                                        |                      |         |        |          |          |       |        |       |            |

Le

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

PIC32MZ Embedded Connectivity (EC) Family

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        |                   | _                 | HR10              | <1:0>             | HR01<3:0>                          |                   |                  |                  |  |  |  |

| 00.40        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                   |                   | MIN10<2:0>        |                   | MIN01<3:0>                         |                   |                  |                  |  |  |  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | —                 |                   | SEC10<2:0>        |                   | SEC01<3:0>                         |                   |                  |                  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                                | U-0               | U-0              | U-0              |  |  |  |

| 7:0          | —                 |                   |                   |                   | _                                  |                   |                  | —                |  |  |  |

|              |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |  |

| Legend:      |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |  |  |  |

0' = Bit is cleared

x = Bit is unknown

#### REGISTER 25-5: ALRMTIME: ALARM TIME VALUE REGISTER

#### -n = Value at POR

bit 31-30 **Unimplemented:** Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, tens digit; contains a value from 0 to 2

'1' = Bit is set

bit 27-24 **HR01<3:0>:** Binary Coded Decimal value of hours bits, ones digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 **MIN10<2:0>:** Binary Coded Decimal value of minutes bits, tens digit; contains a value from 0 to 5 bit 19-16 **MIN01<3:0>:** Binary Coded Decimal value of minutes bits, ones digit; contains a value from 0 to 9

bit 15 Unimplemented: Read as '0'

bit 14-12 **SEC10<2:0>:** Binary Coded Decimal value of seconds bits, tens digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary Coded Decimal value of seconds bits, ones digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

## TABLE 30-5: ETHERNET CONTROLLER REGISTER SUMMARY (CONTINUED)

| ess                         |                                 |               |               |               |               |         |               |               |               | В             | its            |         |               |               |            |          |           |          |     |

|-----------------------------|---------------------------------|---------------|---------------|---------------|---------------|---------|---------------|---------------|---------------|---------------|----------------|---------|---------------|---------------|------------|----------|-----------|----------|-----|

| VIITUAI Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14         | 29/13         | 28/12   | 27/11         | 26/10         | 25/9          | 24/8          | 23/7           | 22/6    | 21/5          | 20/4          | 19/3       | 18/2     | 17/1      | 16/0     |     |

| 2110                        | ETH<br>FRMTXOK                  | 31:16<br>15:0 | _             | —             | —             | -       | _             | —             | -             |               | —<br>CNT<15:0> | —       | —             | —             | —          | _        | —         | -        | 00  |

|                             | ETH                             | 31:16         | _             | _             | _             | _       | _             | _             | _             | -             |                | _       | _             | _             | _          | _        | _         | _        | 00  |

| 120                         | SCOLFRM                         | 15:0          |               |               |               |         |               |               |               | SCOLFRM       | CNT<15:0>      |         |               |               |            |          |           |          | 00  |

| 130                         | ETH                             | 31:16         | —             | —             | —             | —       | _             | —             | -             | —             | —              | _       | —             | —             | —          | —        | —         | —        | 0   |

| 50                          | MCOLFRM                         | 15:0          |               |               |               |         |               |               |               | MCOLFRN       | ICNT<15:0>     |         |               |               |            |          |           |          | 0   |

| 140                         | ETH                             | 31:16         | _             | _             |               |         | _             |               | _             |               | _              | _       | —             | _             |            | —        | _         |          | 0   |

|                             | FRMRXOK                         | 15:0          |               |               |               |         |               |               |               | FRMRXOK       | CNT<15:0>      |         |               |               |            |          |           |          | 0   |

| 150                         | ETH                             | 31:16         | _             | —             | —             | _       | _             | _             | —             | _             | —              | —       | —             | —             | _          | —        | —         | —        | 0   |

|                             | FCSERR                          | 15:0          |               |               |               |         |               |               |               |               | CNT<15:0>      |         |               |               |            |          |           |          | C   |

| 160                         | ETH<br>ALGNERR                  | 31:16         | _             | _             |               |         | _             |               |               | —             | —              | —       |               | _             |            | _        | _         |          | (   |

|                             | ALGNERK                         | 15:0          |               |               |               |         |               |               | 1             |               | CNT<15:0>      |         |               |               |            |          |           |          | (   |

| 200                         | EMAC1                           | 31:16         | -             | -             | _             | —       | -             | -             | -             | -             | _              | _       | _             | _             | _          | —        | _         |          | (   |

| 200                         | CFG1                            | 15:0          | SOFT<br>RESET | SIM<br>RESET  | -             | —       | RESET<br>RMCS | RESET<br>RFUN | RESET<br>TMCS | RESET<br>TFUN | —              | —       | —             | LOOPBACK      | TXPAUSE    | RXPAUSE  | PASSALL   | RXENABLE | E 8 |

|                             | EMAC1                           | 31:16         |               | _             | _             | —       | _             |               |               | _             |                | _       | —             | _             | _          | —        |           |          | (   |

| 210                         | CFG2                            | 15:0          | -             | EXCESS<br>DFR | BP<br>NOBKOFF | NOBKOFF | -             | -             | LONGPRE       | PUREPRE       | AUTOPAD        | VLANPAD | PAD<br>ENABLE | CRC<br>ENABLE | DELAYCRC   | HUGEFRM  | LENGTHCK  | FULLDPLX | ( 4 |

| 220                         | EMAC1                           | 31:16         | —             | _             | —             | —       | —             | _             | _             | _             | _              | —       | —             | —             | _          | _        | _         | _        | C   |

| 20                          | IPGT                            | 15:0          | _             | _             | _             | —       | _             |               |               | _             |                |         |               | Bź            | 2BIPKTGP<6 | :0>      | -         | -        | (   |

| 230                         | EMAC1                           | 31:16         | _             | _             | _             | —       | _             |               |               | —             | _              | _       | _             | _             | —          | _        | _         |          | (   |

| .00                         | IPGR                            | 15:0          | _             |               |               | NB2     | BIPKTGP1<     | 6:0>          |               |               | _              |         |               | NB            | 2BIPKTGP2< | 6:0>     |           |          | 1   |

| 240                         | EMAC1                           | 31:16         | _             | _             | _             | —       | —             | —             | _             | —             | _              | -       | —             | -             | —          | —        | _         | _        | (   |

|                             | CLRT                            | 15:0          |               |               |               |         | CWINDO        | DW<5:0>       |               |               |                | _       | _             | _             |            | RET      | <3:0>     |          | i   |

| 250                         | EMAC1                           | 31:16         | _             |               | —             | —       |               |               |               |               |                | —       |               | —             |            | —        |           |          | (   |

|                             | MAXF                            | 15:0          |               |               |               |         |               |               |               | MACMA         | XF<15:0>       |         |               |               |            |          |           |          |     |

|                             | EMAC1                           | 31:16         | _             |               | —             | —       | _             |               |               | _             |                | _       | _             | _             | _          | —        |           |          | (   |

| 260                         | SUPP                            | 15:0          | —             | —             | _             | —       | RESET<br>RMII | —             | -             | SPEED<br>RMII | —              | —       | —             | —             | —          | —        | —         | —        |     |

| 270                         | EMAC1                           | 31:16         | _             |               | _             | —       | _             |               | _             | —             | _              | _       | —             | —             | —          | —        | _         |          | (   |

| 270                         | TEST                            | 15:0          | _             | —             | —             | —       | —             |               | _             | —             | _              | —       | —             | —             | —          | TESTBP   | TESTPAUSE | SHRTQNTA | A ( |

|                             | EMAC1                           | 31:16         | _             | _             | -             | _       | _             | —             | -             | —             | _              | —       | —             | _             | _          | _        | —         | —        | (   |

| 280                         | MCFG                            | 15:0          | RESET<br>MGMT | -             | -             | —       | _             | -             | -             | —             | _              | —       |               | CLKSE         | EL<3:0>    |          | NOPRE     | SCANINC  | C   |

| 290                         | EMAC1                           | 31:16         | —             | —             | -             | —       | _             | —             | -             | —             | —              | _       | —             | _             | —          | —        | —         | —        | (   |

| 290                         | MCMD                            | 15:0          | —             | —             | -             | —       | _             | —             | -             | —             | —              | _       | —             | _             | —          | —        | SCAN      | READ     | C   |