Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SQI, UART/USART, USB OTG       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 120                                                                              |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-TQFP                                                                         |

| Supplier Device Package    | 144-TQFP (16x16)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048ecm144-i-ph |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

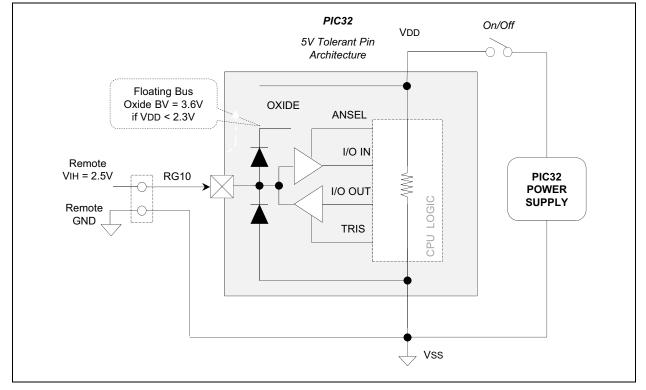

### 2.10.2 5V TOLERANT INPUT PINS

The internal high side diode on 5V tolerant pins are bussed to an internal floating node, rather than being connected to VDD, as shown in Figure 2-7. Voltages on these pins, if VDD < 2.3V, should not exceed roughly 3.2V relative to Vss of the PIC32 device. Voltage of 3.6V or higher will violate the absolute maximum specification, and will stress the oxide layer separating the high side floating node, which impacts device reliability. If a remotely powered "digital-only" signal can be guaranteed to always be  $\leq$  3.2V relative to Vss on the PIC32 device side, a 5V tolerant pin could be used without the need for a digital isolator. This is assuming there is not a ground loop issue, logic ground of the two circuits not at the same absolute level, and a remote logic low input is not less than Vss - 0.3V.

### 4.2 System Bus Arbitration

| Note: | The     | System                                   | Bus       | interconnect     |  |  |  |  |  |  |  |

|-------|---------|------------------------------------------|-----------|------------------|--|--|--|--|--|--|--|

|       |         |                                          |           | nstantiations of |  |  |  |  |  |  |  |

|       | the So  | nicsSX <sup>®</sup> int                  | erconnec  | ct from Sonics,  |  |  |  |  |  |  |  |

|       | Inc. T  | Inc. This document contains materials    |           |                  |  |  |  |  |  |  |  |

|       | that a  | that are (c) 2003-2015 Sonics, Inc., and |           |                  |  |  |  |  |  |  |  |

|       | that co | onstitute pro                            | oprietary | information of   |  |  |  |  |  |  |  |

|       | Sonics  | s, Inc. Son                              | icsSX is  | a registered     |  |  |  |  |  |  |  |

|       | tradem  | nark of S                                | onics, I  | nc. All such     |  |  |  |  |  |  |  |

|       | materi  | als and trad                             | emarks a  | are used under   |  |  |  |  |  |  |  |

|       | license | e from Sonic                             | s, Inc.   |                  |  |  |  |  |  |  |  |

As shown in the PIC32MZ EC Family Block Diagram (see Figure 1-1), there are multiple initiator modules (I1 through I14) in the system that can access various target modules (T1 through T13). Table 4-4 illustrates which initiator can access which target. The System Bus supports simultaneous access to targets by initiators, so long as the initiators are accessing different targets. The System Bus will perform arbitration, if multiple initiators attempt to access the same target.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-1             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | PWPULOCK          | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | PWP<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | PWP<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | PWP<              | 7:0>              |                   |                  |                  |  |  |  |

### REGISTER 5-6: NVMPWP: PROGRAM FLASH WRITE-PROTECT REGISTER

### Legend:

| Legena.           |                  |                                          |

|-------------------|------------------|------------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'       |

| -n = Value at POR | '1' = Bit is set | 0' = Bit is cleared $x = Bit is unknown$ |

bit 31 **PWPULOCK:** Program Flash Memory Page Write-protect Unlock bit

1 = Register is not locked and can be modified

0 = Register is locked and cannot be modified

This bit is only clearable and cannot be set except by any reset.

bit 30-24 Unimplemented: Read as '0'

bit 23-0 PWP<23:0>: Flash Program Write-protect (Page) Address bits

Physical memory below address 0x1Dxxxxxx is write protected, where 'xxxxx' is specified by PWP<23:0>. When PWP<23:0> has a value of '0', write protection is disabled for the entire program Flash. If the specified address falls within the page, the entire page and all pages below the current page will be protected.

**Note:** The bits in this register are only writable when the NVMKEY unlock sequence is followed.

|                             | BLE 7-3:                                    | II            | NIERR |       | EGISTE |       | (CONTI | NUED) |                |                |          |      |      |      |      |      |        |       |            |

|-----------------------------|---------------------------------------------|---------------|-------|-------|--------|-------|--------|-------|----------------|----------------|----------|------|------|------|------|------|--------|-------|------------|

| ess                         | _                                           | æ             |       |       |        |       |        |       |                | В              | its      |      |      |      |      |      |        |       | s          |

| Virtual Address<br>(BF81_#) | (BF81_#)<br>Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13  | 28/12 | 27/11  | 26/10 | 25/9           | 24/8           | 23/7     | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0  | All Resets |

| 0660                        | OFF072                                      | 31:16         | _     | _     | —      | —     | -      | —     | _              | —              |          |      | —    | —    | —    |      | VOFF<1 | 7:16> | 0000       |

| 0000                        | 011072                                      | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0664                        | OFF073                                      | 31:16         | _     | _     | —      | —     | _      |       | —              | —              | _        | _    | —    | —    | —    | _    | VOFF<1 |       | 0000       |

|                             |                                             | 15:0          |       |       | r      |       |        |       |                | VOFF<15:1      |          |      |      |      |      |      |        |       | 0000       |

| 0668                        | OFF074                                      | 31:16         | —     | —     | _      | —     | _      | —     | —              | -              | _        | _    | _    | —    |      | _    | VOFF<1 | 7:16> | 0000       |

|                             |                                             | 15:0          |       |       | 1      | 1     |        | i     |                | VOFF<15:1      | >        | i    | i    | i    | i    |      | VOFF<1 |       | 0000       |

| 066C                        | OFF075                                      | 31:16<br>15:0 | —     |       | _      | _     |        | —     | —              |                |          |      | _    | _    |      | _    | VUFF<1 | 7:16> | 0000       |

|                             |                                             | 31:16         | _     |       |        |       |        | _     | _              | VUFF<15.1      | <u> </u> |      |      |      |      | _    | VOFF<1 | 7:16> | 0000       |

| 0670                        | OFF076                                      | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      |          |      |      |      |      |      | VOITS  |       | 0000       |

|                             | (1)                                         | 31:16         | _     | _     | _      |       | _      | _     | _              | _              | _        | _    | _    | _    | _    |      | VOFF<1 |       | 0000       |

| 0674                        | OFF077 <sup>(2)</sup>                       | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | -     | 0000       |

|                             | . (2)                                       | 31:16         | _     | _     | _      | _     | _      | _     | _              | _              | _        | _    | _    | _    | _    | _    | VOFF<1 | 7:16> | 0000       |

| 0678                        | OFF078 <sup>(2)</sup>                       | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0670                        | OFF079 <sup>(2)</sup>                       | 31:16         | _     | _     | —      | _     | —      | —     | —              | _              | _        | _    | —    | —    | _    | _    | VOFF<1 | 7:16> | 0000       |

| 067C                        | OFF0/9 /                                    | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0680                        | OFF080 <sup>(2)</sup>                       | 31:16         | _     | _     | —      | —     | _      | —     | —              | —              | _        | —    | —    | —    | —    | _    | VOFF<1 | 7:16> | 0000       |

| 0000                        | 011000                                      | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0684                        | OFF081 <sup>(2)</sup>                       | 31:16         | —     | —     | —      | —     | —      | —     | —              | —              | _        | —    | —    | —    | —    | —    | VOFF<1 | 7:16> | 0000       |

|                             | 0.1.001                                     | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      | >        |      |      |      |      |      |        | _     | 0000       |

| 0688                        | OFF082 <sup>(2)</sup>                       | 31:16         | —     | —     | —      | —     | —      | —     | _              | —              |          | —    | _    | —    | _    |      | VOFF<1 | 7:16> | 0000       |

|                             |                                             | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      |          |      |      |      |      |      |        | _     | 0000       |

| 068C                        | OFF083 <sup>(2)</sup>                       | 31:16         | —     | —     | —      | —     | —      | —     | _              |                | _        | _    | —    | —    | —    |      | VOFF<1 |       | 0000       |

|                             |                                             | 15:0<br>31:16 | _     | _     | _      |       |        |       |                | VOFF<15:1      |          |      | _    | _    | _    |      | VOFF<1 |       | 0000       |

| 0690                        | OFF084 <sup>(2)</sup>                       | 15:0          | _     |       | _      | —     | _      | —     | —              | —<br>VOFF<15:1 | _        | _    |      |      |      |      | V0FF<1 |       | 0000       |

|                             |                                             | 31:16         |       |       |        |       | _      | _     | _              | VUFF<15.1      | <u> </u> |      |      |      |      |      | VOFF<1 |       | 0000       |

| 0694                        | OFF085 <sup>(2)</sup>                       | 15:0          |       |       |        |       |        |       |                | VOFF<15:1      |          |      |      | 1    |      |      | 0.10   |       | 0000       |

|                             |                                             | 31:16         | _     | —     | _      | —     | _      | _     | _              | _              |          |      | _    | —    | —    | _    | VOFF<1 | 7:16> | 0000       |

| 0698                        | OFF086 <sup>(2)</sup>                       | 15:0          |       |       |        |       |        | 1     |                | VOFF<15:1      |          | 1    |      | 1    | 1    |      |        | _     | 0000       |

|                             | l                                           |               |       |       |        |       |        |       | in have de sin |                |          |      |      |      |      |      |        |       |            |

#### TARIE 7-3. INTEDDUDT DECISTED MAD (CONTINUED)

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV **Registers**" for more information.

2:

This bit or register is not available on 64-pin devices. This bit or register is not available on devices without a CAN module. 3:

This bit or register is not available on 100-pin devices. 4:

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

This bit or register is not available on devices without a Crypto module. 7:

This bit or register is not available on 124-pin devices. 8:

## 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features    |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | of the PIC32MZ Embedded Connectivity       |  |  |  |  |  |  |  |  |

|       | (EC) Family of devices. It is not intended |  |  |  |  |  |  |  |  |

|       | to be a comprehensive reference source.    |  |  |  |  |  |  |  |  |

|       | To complement the information in this      |  |  |  |  |  |  |  |  |

|       | data sheet, refer to Section 42.           |  |  |  |  |  |  |  |  |

|       | "Oscillators with Enhanced PLL"            |  |  |  |  |  |  |  |  |

|       | (DS60001250), which is available from      |  |  |  |  |  |  |  |  |

|       | the Documentation > Reference Manual       |  |  |  |  |  |  |  |  |

|       | section of the Microchip PIC32 web site    |  |  |  |  |  |  |  |  |

|       | (www.microchip.com/pic32).                 |  |  |  |  |  |  |  |  |

The PIC32MZ EC oscillator system has the following modules and features:

- A total of five external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown with dedicated Back-up FRC (BFRC)

- Dedicated On-Chip PLL for USB peripheral

- Flexible reference clock output

- Multiple clock branches for peripherals for better performance flexibility

A block diagram of the oscillator system is provided in Figure 8-1. Table 8-1 shows the clock distribution.

### TABLE 11-1: USB REGISTER MAP (CONTINUED)

|                    |                     |           |       |               |       |       |           |         |         |         | Bits               |        |                       |                       |        |          |        |       |            |

|--------------------|---------------------|-----------|-------|---------------|-------|-------|-----------|---------|---------|---------|--------------------|--------|-----------------------|-----------------------|--------|----------|--------|-------|------------|

| Virtual<br>Address | Register<br>Name    | Bit Range | 31/15 | 30/14         | 29/13 | 28/12 | 27/11     | 26/10   | 25/9    | 24/8    | 23/7               | 22/6   | 21/5                  | 20/4                  | 19/3   | 18/2     | 17/1   | 16/0  | All Resets |

| 3340               | USB                 | 31:16     | _     | _             | —     | _     | _         | -       | _       | —       | EP7TXD             | EP6TXD | EP5TXD                | EP4TXD                | EP3TXD | EP2TXD   | EP1TXD | -     | 0000       |

| 3340               | DPBFD               | 15:0      | —     | _             |       | —     | _         |         | —       | —       | EP7RXD             | EP6RXD | EP5RXD                | EP4RXD                | EP3RXD | EP2RXD   | EP1RXD | —     | 0000       |

| 3344               | 000                 | 31:16     |       | THHSRTN<15:0> |       |       |           |         |         |         |                    |        |                       | 05E6                  |        |          |        |       |            |

| 5544               | TMCON1              | 15:0      |       |               |       |       |           |         |         | TI      | UCH<15:0>          |        |                       |                       |        |          |        |       | 4074       |

| 3348               | 000                 | 31:16     | _     | -             | —     |       | —         | _       | —       | —       |                    | _      | _                     | _                     |        |          | —      | _     | 0000       |

| 3340               | TMCON2              | 15:0      | _     | _             | —     | _     | _         | _       | _       | _       | — — — — THSBT<3:0> |        |                       |                       | 8:0>   |          | 0000   |       |            |

|                    |                     | 31:16     | _     | _             | LPM   | LPM   |           | LPMNYIE | LPMSTIE | LPMTOIE | _                  |        | _                     | LPMNAK <sup>(1)</sup> | LPME   | N<1:0>   | LPMRES |       | 0000       |

| 3360               | USB<br>LPMR1        | 51.10     |       | _             | ERRIE | RESIE |           |         |         |         |                    | _      | _                     | (2)                   | (2)    | (2)      |        |       | 0000       |

|                    | 2                   | 15:0      |       | ENDPOINT      | <3:0> |       | _         | _       | —       | RMTWAK  |                    | HIRI   | D<3:0>                |                       |        | LNKSTATE | <3:0>  |       | 0000       |

|                    |                     | 31:16     | _     | _             | _     | _     | _         | _       | _       | —       | _                  | -      | —                     | -                     | -      | _        | _      | _     | 0000       |

| 3364               | 64 USB 1<br>LMPR2 1 |           | -     |               |       | LPI   | MFADDR<6: | 0>      |         |         | _                  | _      | LPMERR <sup>(1)</sup> | LPMRES                | LPMNC  | LPMACK   | LPMNY  | LPMST | 0000       |

Legend: Note

1: Device mode.

2: Host mode.

3: 4:

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7).

# REGISTER 11-10: USBIENCSR2: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 2 (ENDPOINT 1-7)

|              |                   |                   | ,                 |                   |                   |                   |                  |                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 04-04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | TXINTERV<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23.10        | SPEE              | D<1:0>            | PROTOCO           | OL<1:0>           | TEP<3:0>          |                   |                  |                  |  |  |  |  |

| 15:8         | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15.6         | —                 | —                 |                   | RXCNT<13:8>       |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   |                   |                   | RXC               | NT<7:0>           |                   |                  |                  |  |  |  |  |

| Legend:           | HC = Hardware Clearable HS = Hardware Settable |                                    |                    |  |  |  |  |

|-------------------|------------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                               | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                               | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-24 TXINTERV<7:0>: Endpoint TX Polling Interval/NAK Limit bits (Host mode)

For Interrupt and Isochronous transfers, this field defines the polling interval for the endpoint. For Bulk endpoints, this field sets the number of frames/microframes after which the endpoint should time out on receiving a stream of NAK responses.

The following table describes the valid values and interpretation for these bits:

| Transfer Type | Speed        | Valid Values (m) | Interpretation                                                                                                |

|---------------|--------------|------------------|---------------------------------------------------------------------------------------------------------------|

| Interrupt     | Low/Full     | 0x01 to 0xFF     | Polling interval is 'm' frames.                                                                               |

|               | High         | 0x01 to 0x10     | Polling interval is 2 <sup>(m-1)</sup> frames.                                                                |

| Isochronous   | Full or High | 0x01 to 0x10     | Polling interval is 2 <sup>(m-1)</sup> frames/microframes.                                                    |

| Bulk          | Full or High | 0x02 to 0x10     | NAK limit is 2 <sup>(m-1)</sup> frames/microframes. A value of '0' or '1' disables the NAK time-out function. |

bit 23-22 SPEED<1:0>: TX Endpoint Operating Speed Control bits (Host mode)

- 11 = Low-Speed

- 10 = Full-Speed

- 01 = Hi-Speed

- 00 = Reserved

bit 21-20 PROTOCOL<1:0>: TX Endpoint Protocol Control bits

- 11 = Interrupt

- 10 = Bulk

- 01 = Isochronous

- 00 = Control

- bit 19-16 TEP<3:0>: TX Target Endpoint Number bits

This value is the endpoint number contained in the TX endpoint descriptor returned to the USB module during device enumeration.

- bit 15-14 Unimplemented: Read as '0'

- bit 13-0 RXCNT<13:0>: Receive Count bits

The number of received data bytes in the endpoint RX FIFO. The value returned changes as the contents of the FIFO change and is only valid while RXPKTRDY is set.

| Peripheral Pin               | [pin name]R SFR      | [pin name]R bits          | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection         |  |  |  |  |

|------------------------------|----------------------|---------------------------|------------------------------------------------------------|--|--|--|--|

| INT3                         | INT3R                | INT3R<3:0>                | 0000 = RPD2                                                |  |  |  |  |

| T2CK                         | T2CKR                | T2CKR<3:0>                | 0001 = RPG8                                                |  |  |  |  |

| T6CK                         | T6CKR                | T6CKR<3:0>                | 0010 = RPF4                                                |  |  |  |  |

| IC3                          | IC3R                 | IC3R<3:0>                 | 0011 = RPD10                                               |  |  |  |  |

| IC7                          | IC7R                 | IC7R<3:0>                 |                                                            |  |  |  |  |

| U1RX                         | U1RXR                | U1RXR<3:0>                | 0101 = RPB9<br>0110 = RPB10                                |  |  |  |  |

| U2CTS                        | U2CTSR               | U2CTSR<3:0>               | 0111 = RPC14                                               |  |  |  |  |

| U5RX                         | U5RXR                | U5RXR<3:0>                | 1000 = RPB5                                                |  |  |  |  |

| U6CTS                        | U6CTSR               | U6CTSR<3:0>               | 1001 = Reserved                                            |  |  |  |  |

| SDI1                         | SDI1R                | SDI1R<3:0>                | $1010 = \text{RPC1}^{(1)}$                                 |  |  |  |  |

| SDI3                         | SDI3R                | SDI3R<3:0>                | $-1011 = \text{RPD14}^{(1)}$                               |  |  |  |  |

| SDI5 <sup>(1)</sup>          | SDI5R <sup>(1)</sup> | SDI5R<3:0> <sup>(1)</sup> | 1100 = RPG1 <sup>(1)</sup><br>1101 = RPA14 <sup>(1)</sup>  |  |  |  |  |

| <u>SS6</u> (1)               | SS6R <sup>(1)</sup>  | SS6R<3:0> <sup>(1)</sup>  | $11101 = RPD6^{(2)}$                                       |  |  |  |  |

| REFCLKI1                     | REFCLKI1R            | REFCLKI1R<3:0>            | 1111 = Reserved                                            |  |  |  |  |

| INT4                         | INT4R                | INT4R<3:0>                | 0000 = RPD3                                                |  |  |  |  |

| T5CK                         | T5CKR                | T5CKR<3:0>                | 0001 = RPG7                                                |  |  |  |  |

| T7CK                         | T7CKR                | T7CKR<3:0>                | 0010 = RPF5<br>0011 = RPD11                                |  |  |  |  |

| IC4                          | IC4R                 | IC4R<3:0>                 | 0100 = RPF0                                                |  |  |  |  |

| IC8                          | IC8R                 | IC8R<3:0>                 |                                                            |  |  |  |  |

| U3RX                         | U3RXR                | U3RXR<3:0>                | 0111 = RPC13                                               |  |  |  |  |

|                              | U4CTSR               | U4CTSR<3:0>               | 1000 = RPB3<br>1001 = Reserved                             |  |  |  |  |

| SDI2                         | SDI2R                | SDI2R<3:0>                | 1010 = RPC4 <sup>(1)</sup>                                 |  |  |  |  |

| SDI4                         | SDI4R                | SDI4R<3:0>                | $- 1011 = \text{RPD15}^{(1)} \\ 1100 = \text{RPG0}^{(1)} $ |  |  |  |  |

| C1RX <sup>(3)</sup>          | C1RXR <sup>(3)</sup> | C1RXR<3:0> <sup>(3)</sup> | 1101 = RPA15 <sup>(1)</sup>                                |  |  |  |  |

| REFCLKI4                     | REFCLKI4R            | REFCLKI4R<3:0>            |                                                            |  |  |  |  |

| INT2                         | INT2R                | INT2R<3:0>                | 0000 = RPD9                                                |  |  |  |  |

| T3CK                         | T3CKR                | T3CKR<3:0>                | 0001 = RPG6                                                |  |  |  |  |

| T8CK                         | TBCKR                | T8CKR<3:0>                | 0010 = RPB8                                                |  |  |  |  |

| IC2                          | IC2R                 | IC2R<3:0>                 | 0011 = RPB15                                               |  |  |  |  |

| IC5                          | IC5R                 | IC5R<3:0>                 |                                                            |  |  |  |  |

| IC9                          | IC9R                 | IC9R<3:0>                 | 0101 = RPB0                                                |  |  |  |  |

| UICTS                        | U1CTSR               | U1CTSR<3:0>               | 0110 = RPE3<br>0111 = RPB7                                 |  |  |  |  |

| U2RX                         | U2RXR                | U2RXR<3:0>                | 1000 = Reserved                                            |  |  |  |  |

| USCTS                        | USCTSR               |                           | 1001 = RPF12 <sup>(1)</sup>                                |  |  |  |  |

| <u>SS1</u>                   |                      | U5CTSR<3:0>               | 1010 = RPD12 <sup>(1)</sup>                                |  |  |  |  |

| <u> </u>                     | SS1R                 | SS1R<3:0>                 |                                                            |  |  |  |  |

|                              | SS3R                 | SS3R<3:0>                 | 1100 = RPC3 <sup>(1)</sup>                                 |  |  |  |  |

| <u>SS4</u><br><u>SS5</u> (1) | SS4R                 | SS4R<3:0>                 | 1101 = RPE9 <sup>(1)</sup>                                 |  |  |  |  |

| 222.1                        | SS5R <sup>(1)</sup>  | SS5R<3:0> <sup>(1)</sup>  | 1110 = Reserved                                            |  |  |  |  |

### TABLE 12-1: INPUT PIN SELECTION

**Note 1:** This selection is not available on 64-pin devices.

**2:** This selection is not available on 64-pin or 100-pin devices.

3: This selection is not available on devices without a CAN module.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7               | Bit<br>30/22/14/6           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3          | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0                |  |  |  |  |

|--------------|---------------------------------|-----------------------------|-------------------|-------------------|----------------------------|-------------------|------------------------|---------------------------------|--|--|--|--|

| 04.04        | U-0                             | U-0                         | U-0               | U-0               | U-0                        | U-0               | R/W-0                  | R/W-0                           |  |  |  |  |

| 31:24        | —                               | —                           | _                 | _                 | _                          | _                 | CAL                    | _<9:8>                          |  |  |  |  |

| 00.40        | R/W-0                           | R/W-0                       | R/W-0             | R/W-0             | R/W-0                      | R/W-0             | R/W-0                  | R/W-0                           |  |  |  |  |

| 23:16        |                                 | CAL<7:0>                    |                   |                   |                            |                   |                        |                                 |  |  |  |  |

|              | R/W-0                           | U-0                         | R/W-0             | U-0               | U-0                        | R/W-0             | R/W-0                  | R/W-0                           |  |  |  |  |

| 15:8         | ON <sup>(1)</sup>               | —                           | SIDL              | —                 | —                          | RTCCLKSEL<1:0>    |                        | RTC<br>OUTSEL<1> <sup>(2)</sup> |  |  |  |  |

|              | R/W-0                           | R-0                         | U-0               | U-0               | R/W-0                      | R-0               | R-0                    | R/W-0                           |  |  |  |  |

| 7:0          | RTC<br>OUTSEL<0> <sup>(2)</sup> | RTC<br>CLKON <sup>(5)</sup> | _                 |                   | RTC<br>WREN <sup>(3)</sup> | RTC<br>SYNC       | HALFSEC <sup>(4)</sup> | RTCOE                           |  |  |  |  |

### REGISTER 25-1: RTCCON: REAL-TIME CLOCK AND CALENDAR CONTROL REGISTER

| Legend | • |

|--------|---|

| Legenu | • |

| Legend:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

### bit 31-26 Unimplemented: Read as '0'

| bit 25-16 | CAL<9:0>: Real-Time Clock Drift Calibration bits, which contain a signed 10-bit integer value                       |

|-----------|---------------------------------------------------------------------------------------------------------------------|

|           | 0111111111 = Maximum positive adjustment, adds 511 real-time clock pulses every one minute                          |

|           | •                                                                                                                   |

|           | •                                                                                                                   |

|           | •                                                                                                                   |

|           | 000000001 = Minimum positive adjustment, adds 1 real-time clock pulse every one minute<br>000000000 = No adjustment |

|           | 1111111111 = Minimum negative adjustment, subtracts 1 real-time clock pulse every one minute                        |

|           | •                                                                                                                   |

|           | •                                                                                                                   |

|           | •<br>1000000000 = Maximum negative adjustment, subtracts 512 real-time clock pulses every one minute                |

| bit 15    | ON: RTCC On bit <sup>(1)</sup>                                                                                      |

|           | 1 = RTCC module is enabled                                                                                          |

|           | 0 = RTCC module is disabled                                                                                         |

| bit 14    | Unimplemented: Read as '0'                                                                                          |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                         |

|           | 1 = Disables RTCC operation when CPU enters Idle mode                                                               |

|           | 0 = Continue normal operation when CPU enters Idle mode                                                             |

| bit 12-11 | Unimplemented: Read as '0'                                                                                          |

|           |                                                                                                                     |

| Note 1:   | The ON bit is only writable when RTCWREN = 1.                                                                       |

| 2:        | Requires RTCOE = 1 (RTCCON<0>) for the output to be active.                                                         |

| 3:        | The RTCWREN bit can be set only when the write sequence is enabled.                                                 |

| 4:        | This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).                   |

| 5:        | This bit is undefined when RTCCLKSEL<1:0> = 00 (LPRC is the clock source).                                          |

| J.        |                                                                                                                     |

#### Note: This register is reset only on a Power-on Reset (POR).

٦

Figure 26-10 shows the Security Association control word structure.

The Crypto Engine fetches different structures for different flows and ensures that hardware fetches minimum words from SA required for processing. The structure is ready for hardware optimal data fetches.

| Bit<br>Range | Bit<br>31/23/15/7              | Bit<br>30/22/14/6                                                                                                                                                                                                                                | Bit<br>29/21/13/5              | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31-24        |                                | —                                                                                                                                                                                                                                                | VERIFY                         | —                 | NO_RX             | OR_EN             | ICVONLY          | IRFLAG           |  |

| 23-16        | LNC                            | LOADIV                                                                                                                                                                                                                                           | FB                             | FLAGS             | —                 | _                 | _                | ALGO<6>          |  |

| 15-8         |                                |                                                                                                                                                                                                                                                  | ALGO                           | <5:0>             |                   |                   | ENC              | KEY<br>SIZE<1>   |  |

| 7-0          | KEY<br>SIZE<0>                 | MU                                                                                                                                                                                                                                               | ILTITASK<2:                    | 0>                |                   | CRYPTOA           | LGO<3:0>         |                  |  |

| bit 31-30    | Reserved:                      | Do not use                                                                                                                                                                                                                                       |                                |                   |                   |                   |                  |                  |  |

| bit 29       | 1 = NIST pr                    | ST Procedure<br>ocedures are<br>use NIST proc                                                                                                                                                                                                    | to be used                     | Setting           |                   |                   |                  |                  |  |

| bit 28       | Reserved:                      | Do not use                                                                                                                                                                                                                                       |                                |                   |                   |                   |                  |                  |  |

| bit 27       |                                | ceive DMA C<br>lculate ICV fo<br>processing                                                                                                                                                                                                      | -                              | -                 | ons               |                   |                  |                  |  |

| bit 26       |                                | R Register Bits<br>register bits w<br>processing                                                                                                                                                                                                 |                                | -                 | ne CSR regis      | ster              |                  |                  |  |

| bit 25       | This affects<br>1 = Only thr   | <b>ICVONLY:</b> Incomplete Check Value Only Flag<br>This affects the SHA-1 algorithm only. It has no effect on the AES algorithm.<br>1 = Only three words of the HMAC result are available<br>0 = All results from the HMAC result are available |                                |                   |                   |                   |                  |                  |  |

| bit 24       | This bit is se<br>1 = Save the | nmediate Res<br>et when the in<br>e immediate r<br>save the imme                                                                                                                                                                                 | nmediate res<br>result for has | ult for hashir    | ng is request     | ed.               |                  |                  |  |

| bit 23       | LNC: Load                      | <ul> <li>0 = Do not save the immediate result</li> <li>LNC: Load New Keys Setting</li> <li>1 = Load a new set of keys for encryption and authentication</li> <li>0 = Do not load new keys</li> </ul>                                             |                                |                   |                   |                   |                  |                  |  |

| bit 22       | 1 = Load the                   | LOADIV: Load IV Setting<br>1 = Load the IV from this Security Association<br>0 = Use the next IV                                                                                                                                                 |                                |                   |                   |                   |                  |                  |  |

| bit 21       | This bit indic<br>1 = Indicate | <b>FB:</b> First Block Setting<br>This bit indicates that this is the first block of data to feed the IV value.<br>1 = Indicates this is the first block of data<br>0 = Indicates this is not the first block of data                            |                                |                   |                   |                   |                  |                  |  |

| bit 20       | 1 = Security                   | FLAGS: Incoming/Outgoing Flow Setting<br>1 = Security Association is associated with an outgoing flow<br>0 = Security Association is associated with an incoming flow                                                                            |                                |                   |                   |                   |                  |                  |  |

|              |                                | Reserved: Do not use                                                                                                                                                                                                                             |                                |                   |                   |                   |                  |                  |  |

### FIGURE 26-10: FORMAT OF SA\_CTRL

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|--------------------------|-------------------------|-------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0                      | U-0                     | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                          |                         | _                       |                   | _                 | _                 | —                | _                |

| 23:16        | R/W-0                    | R/W-0                   | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        |                          |                         | E                       | BUFCNT<7:0        | > <sup>(1)</sup>  |                   |                  |                  |

| 15:8         | U-0                      | U-0                     | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         |                          | _                       | _                       | _                 | —                 | —                 | _                | _                |

| 7.0          | R/W-0                    | R/W-0                   | R/W-0                   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | ETHBUSY <sup>(4,5)</sup> | TXBUSY <sup>(2,6)</sup> | RXBUSY <sup>(3,6)</sup> | _                 | _                 | _                 | _                | —                |

### REGISTER 30-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER

# Legend:

| R = Readable bit  | bit W = Writable bit |                      | t, read as '0'     |

|-------------------|----------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared | x = Bit is unknown |

### bit 31-24 Unimplemented: Read as '0'

### bit 23-16 **BUFCNT<7:0>:** Packet Buffer Count bits<sup>(1)</sup>

Number of packet buffers received in memory. Once a packet has been successfully received, this register is incremented by hardware based on the number of descriptors used by the packet. Software decrements the counter (by writing to the BUFCDEC bit (ETHCON1<0>) for each descriptor used) after a packet has been read out of the buffer. The register does not roll over (0xFF to 0x00) when hardware tries to increment the register and the register is already at 0xFF. Conversely, the register does not roll under (0x00 to 0xFF) when software tries to decrement the register and the register is already at 0x000. When software attempts to decrement the same time that the hardware attempts to increment the counter, the counter value will remain unchanged.

When this register value reaches 0xFF, the RX logic will halt (only if automatic Flow Control is enabled) awaiting software to write the BUFCDEC bit in order to decrement the register below 0xFF.

If automatic Flow Control is disabled, the RXDMA will continue processing and the BUFCNT will saturate at a value of 0xFF.

When this register is non-zero, the PKTPEND status bit will be set and an interrupt may be generated, depending on the value of the ETHIEN bit <PKTPENDIE> register.

When the ETHRXST register is written, the BUFCNT counter is automatically cleared to 0x00.

- **Note:** BUFCNT will not be cleared when ON is set to '0'. This enables software to continue to utilize and decrement this count.

- bit 15-8 Unimplemented: Read as '0'

- bit 7 ETHBUSY: Ethernet Module busy bit<sup>(4,5)</sup>

- 1 = Ethernet logic has been turned on (ON (ETHCON1<15>) = 1) or is completing a transaction 0 = Ethernet logic is idle

This bit indicates that the module has been turned on or is completing a transaction after being turned off.

- Note 1: This bit is only used for RX operations.

- 2: This bit is only affected by TX operations.

- 3: This bit is only affected by RX operations.

- 4: This bit is affected by TX and RX operations.

- 5: This bit will be set when the ON bit (ETHCON1<15>) = 1.

- **6:** This bit will be *cleared* when the ON bit (ETHCON1 < 15 >) = 0.

# REGISTER 30-36: EMAC1MIND: ETHERNET CONTROLLER MAC MII MANAGEMENT INDICATORS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | —                 |                   |                   | -                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | —                 |                   |                   | -                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 0.61         | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   | _                 | _                 |                   | LINKFAIL          | NOTVALID          | SCAN             | MIIMBUSY         |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

### bit 31-4 Unimplemented: Read as '0'

bit 3 LINKFAIL: Link Fail bit

When '1' is returned - indicates link fail has occurred. This bit reflects the value last read from the PHY status register.

bit 2 **NOTVALID:** MII Management Read Data Not Valid bit When '1' is returned - indicates an MII management read cycle has not completed and the Read Data is not yet valid.

### bit 1 SCAN: MII Management Scanning bit When '1' is returned - indicates a scan operation (continuous MII Management Read cycles) is in progress.

### bit 0 MIIMBUSY: MII Management Busy bit

When '1' is returned - indicates MII Management module is currently performing an MII Management Read or Write cycle.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

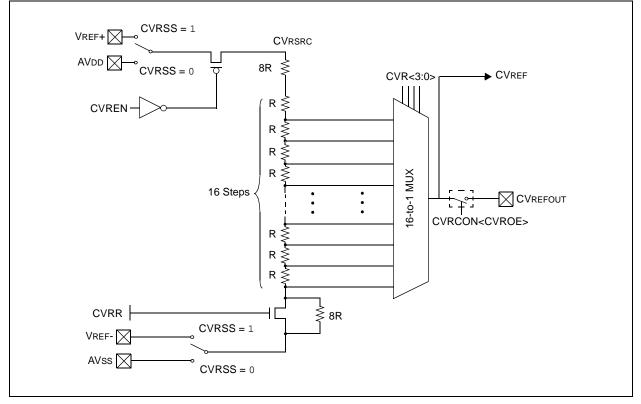

## 32.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

Note: This data sheet summarizes the features of the PIC32MZ Embedded Connectivity (EC) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The comparator voltage reference has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- Output can be connected to a pin

A block diagram of the CVREF module is illustrated in Figure 32-1.

NOTES:

### REGISTER 34-4: DEVCFG1/ADEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

10100 = 1:1048576

10011 = 1:524288 10010 = 1:262144 10001 = 1:13107210000 = 1:65536 01111 = 1:3276801110 = 1:16384 01101 = 1:8192 01100 = 1:4096 01011 = 1:2048 01010 = 1:102401001 = 1:512 01000 = 1:25600111 = 1:128 00110 **= 1:64** 00101 = 1:3200100 = 1:1600011 = 1:8 00010 = 1:4

- 00001 = 1:2

- 00000 = 1:1

All other combinations not shown result in operation = 10100

- bit 15-14 FCKSM<1:0>: Clock Switching and Monitoring Selection Configuration bits

- 11 = Clock switching is enabled and clock monitoring is enabled

- 10 = Clock switching is disabled and clock monitoring is enabled

- ${\tt 01}$  = Clock switching is enabled and clock monitoring is disabled

- 00 = Clock switching is disabled and clock monitoring is disabled

- bit 13-11 Reserved: Write as '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSC2 pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

- bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Posc disabled

- 10 = HS Oscillator mode selected

- 01 = Reserved

- 00 = EC mode selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

### bit 6 FSOSCEN: Secondary Oscillator Enable bit

- 1 = Enable Sosc

- 0 = Disable Sosc

- bit 5-3 **DMTINV<2:0>:** Deadman Timer Count Window Interval bits

- 111 = Window/Interval value is 127/128 counter value

- 110 = Window/Interval value is 63/64 counter value

- 101 = Window/Interval value is 31/32 counter value

- 100 = Window/Interval value is 15/16 counter value

- 011 = Window/Interval value is 7/8 counter value

- 010 = Window/Interval value is 3/4 counter value

- 001 = Window/Interval value is 1/2 counter value

- 000 = Window/Interval value is zero

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |

|--------------|-----------------------------|-------------------|---------------------|-------------------|---------------------|-------------------|-----------------------|------------------|--|

| 04.04        | R                           | R                 | R                   | R                 | R                   | R                 | R                     | R                |  |

| 31:24        |                             | VER<3             | 8:0> <sup>(1)</sup> |                   |                     | DEVID<2           | 27:24> <sup>(1)</sup> |                  |  |

| 00.40        | R                           | R                 | R                   | R                 | R                   | R                 | R                     | R                |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                     |                   |                     |                   |                       |                  |  |

| 45.0         | R                           | R                 | R                   | R                 | R                   | R                 | R                     | R                |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup>  |                   |                     |                   |                     |                   |                       |                  |  |

| 7.0          | R                           | R                 | R                   | R                 | R                   | R                 | R                     | R                |  |

| 7:0          |                             |                   |                     | DEVID<            | 7:0> <sup>(1)</sup> |                   |                       |                  |  |

### REGISTER 34-11: DEVID: DEVICE AND REVISION ID REGISTER

### Legend:

| Logona.           |                  |                                         |  |

|-------------------|------------------|-----------------------------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

| Bit Range        | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 01.04            | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 31:24            |                   |                   |                   | ADCAL             | <31:24>           |                   |                  |                  |  |  |

| 22:16            | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 23:16            |                   |                   |                   | ADCAL             | <23:16>           |                   |                  |                  |  |  |

| 15.0             | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 15:8 ADCAL<15:8> |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0              | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 7:0 ADCAL<7:0>   |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

### **REGISTER 34-12: DEVADCx: DEVICE ADC CALIBRATION REGISTER 'x' ('x' = 1-5)**

| Legend:           |                  |                      |                    |  |

|-------------------|------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | pit, read as '0'   |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

bit 31-0 ADCAL<31:0>: Calibration Data for the ADC Module bits

This data must be copied to the corresponding AD1CALx register. Refer to **Section 28.0** "**Pipelined Analog-to-Digital Converter (ADC)**" for more information.

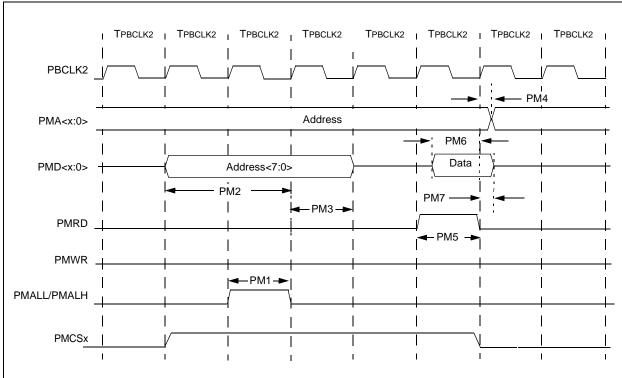

### FIGURE 37-22: PARALLEL MASTER PORT READ TIMING DIAGRAM

### TABLE 37-42: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |           |      |       |            |

|--------------------|---------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|-------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                              | Тур.      | Max. | Units | Conditions |

| PM1                | TLAT    | PMALL/PMALH Pulse Width                                              | _                                                                                                                                                 | 1 TPBCLK2 | _    | —     |            |

| PM2                | Tadsu   | Address Out Valid to PMALL/<br>PMALH Invalid (address setup time)    | —                                                                                                                                                 | 2 TPBCLK2 | —    | —     | _          |

| PM3                | TADHOLD | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | —                                                                                                                                                 | 1 TPBCLK2 | _    | _     | _          |

| PM4                | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                 | —         | _    | ns    | _          |

| PM5                | Trd     | PMRD Pulse Width                                                     | —                                                                                                                                                 | 1 TPBCLK2 | _    | _     | —          |

| PM6                | TDSU    | PMRD or PMENB Active to Data<br>In Valid (data setup time)           | 15                                                                                                                                                | —         | —    | ns    | —          |

| PM7                | TDHOLD  | PMRD or PMENB Inactive to<br>Data In Invalid (data hold time)        | 5                                                                                                                                                 | —         | —    | ns    | _          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

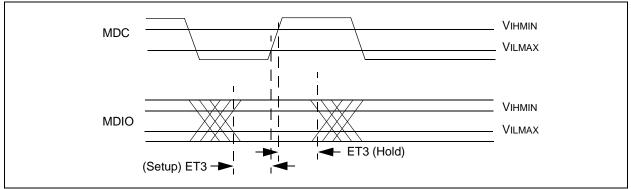

### TABLE 37-45: ETHERNET MODULE SPECIFICATIONS

|                          |                                     |      | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |       |                  |  |

|--------------------------|-------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------|--|

| Param.<br>No.            | Characteristic                      | Min. | Тур.                                                                                                                                            | Max. | Units | Conditions       |  |

| MIIM Timing Requirements |                                     |      |                                                                                                                                                 |      |       |                  |  |

| ET1                      | MDC Duty Cycle                      | 40   | —                                                                                                                                               | 60   | %     | —                |  |

| ET2                      | MDC Period                          | 400  | —                                                                                                                                               | —    | ns    | —                |  |

| ET3                      | MDIO Output Setup and Hold          | 10   | —                                                                                                                                               | 10   | ns    | See Figure 37-24 |  |

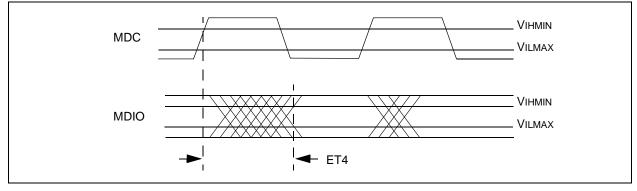

| ET4                      | MDIO Input Setup and Hold           | 0    | —                                                                                                                                               | 300  | ns    | See Figure 37-25 |  |

| MII Timi                 | ng Requirements                     |      |                                                                                                                                                 |      |       |                  |  |

| ET5                      | TX Clock Frequency                  | —    | 25                                                                                                                                              | —    | MHz   | —                |  |

| ET6                      | TX Clock Duty Cycle                 | 35   | —                                                                                                                                               | 65   | %     | —                |  |

| ET7                      | ETXDx, ETEN, ETXERR Output Delay    | 0    | —                                                                                                                                               | 25   | ns    | See Figure 37-26 |  |

| ET8                      | RX Clock Frequency                  | —    | 25                                                                                                                                              | —    | MHz   | —                |  |

| ET9                      | RX Clock Duty Cycle                 | 35   | —                                                                                                                                               | 65   | %     | —                |  |

| ET10                     | ERXDx, ERXDV, ERXERR Setup and Hold | 10   | —                                                                                                                                               | 30   | ns    | See Figure 37-27 |  |

| RMII Timing Requirements |                                     |      |                                                                                                                                                 |      |       |                  |  |

| ET11                     | Reference Clock Frequency           | _    | 50                                                                                                                                              |      | MHz   | —                |  |

| ET12                     | Reference Clock Duty Cycle          | 35   | —                                                                                                                                               | 65   | %     | —                |  |

| ET13                     | ETXDx, ETEN, Setup and Hold         | 2    | —                                                                                                                                               | 16   | ns    | —                |  |

| ET14                     | ERXDx, ERXDV, ERXERR Setup and Hold | 2    | —                                                                                                                                               | 16   | ns    | —                |  |

### FIGURE 37-24: MDIO SOURCED BY THE PIC32 DEVICE

### FIGURE 37-25: MDIO SOURCED BY THE PHY

| Section Name                                                  | Update Description                                                                                                                                                    |  |  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 28.0 "12-bit Pipelined Analog-to-                             | Figure 28-1, Figure 28-2, and Figure 28-3 were updated.                                                                                                               |  |  |

| Digital Converter (ADC)"                                      | Register names were updated in the ADC Register Map (see Table 28-1).                                                                                                 |  |  |

|                                                               | The OVRSAM<2:0> bit values were updated (see Register 28-14).                                                                                                         |  |  |

| 34.0 "Special Features"                                       | The DEVCFG3/ADEVCFG3 register was updated (see Register 34-6).                                                                                                        |  |  |

| 37.0 "Electrical Characteristics"                             | Various electrical specifications were updated, including:                                                                                                            |  |  |

|                                                               | • The minimum value for parameter DC10 (VDD) in the DC Temperature and Voltage Specifications was updated (see Table 37-4).                                           |  |  |

|                                                               | <ul> <li>The minimum and maximum values for parameter BO10 (VBOR) were<br/>updated in the BOR Electrical Characteristics (see Table 37-4).</li> </ul>                 |  |  |

|                                                               | • Updated the third and fourth bullet list items in Note 2 in DC Characteristics:<br>Operating Current (IDD) (see Table 37-6).                                        |  |  |