Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

>< ⊢

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 16 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 13                                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 4x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

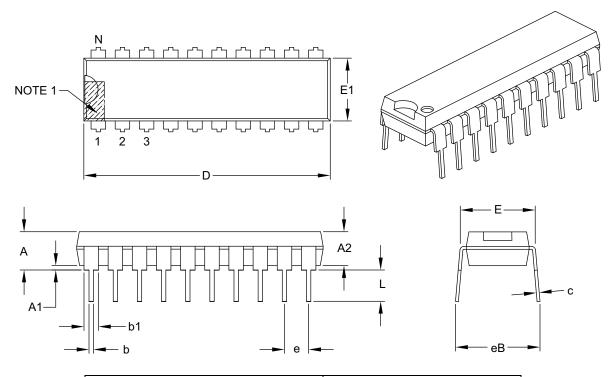

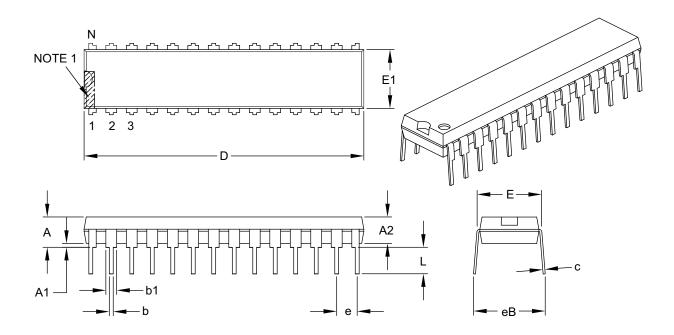

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 18-PDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gp101-e-p |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

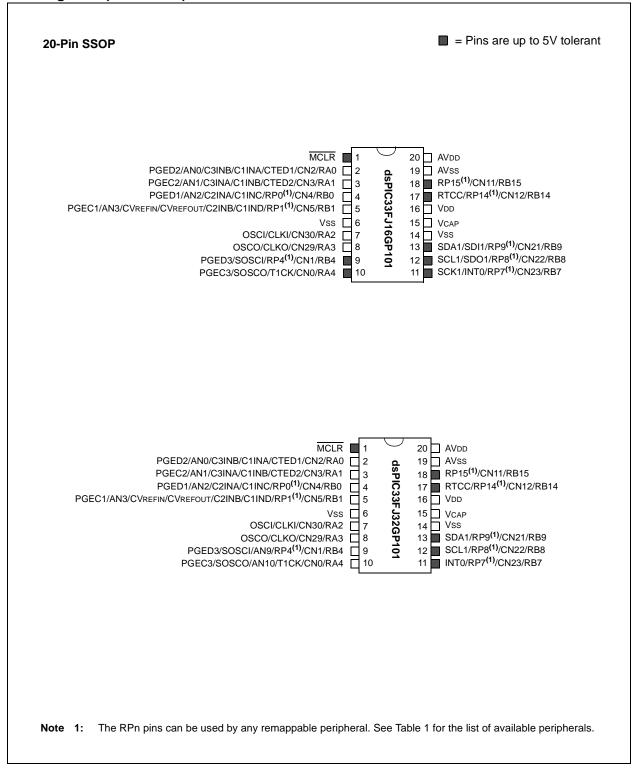

### dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

### Pin Diagrams (Continued)

© 2011-2014 Microchip Technology Inc.

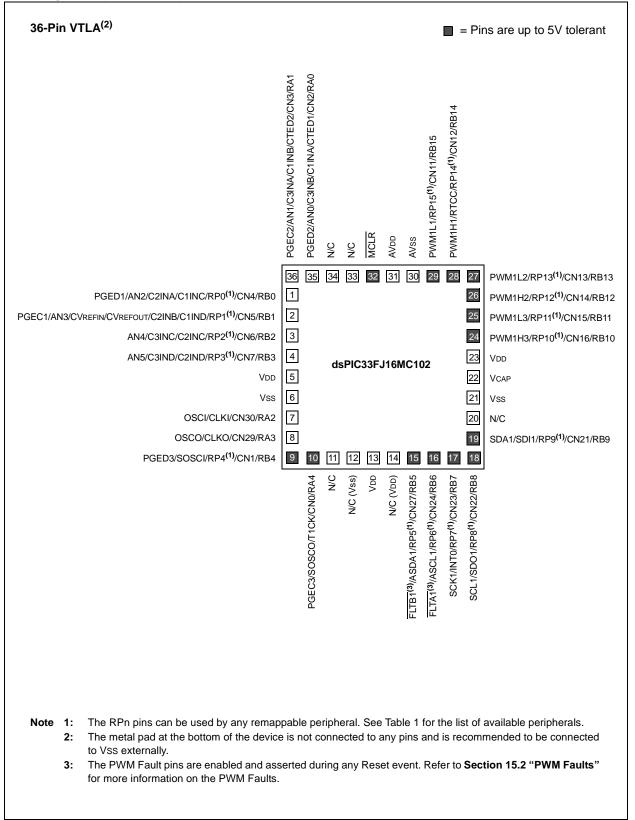

### Pin Diagrams (Continued)

### 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70204) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33FJ16(GP/MC)101/102 The and dsPIC33FJ32(GP/MC)101/102/104 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can serve as a data, address, or address offset register. The 16th Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

There are two classes of instruction in the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices are capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model for the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 is shown in Figure 3-2.

### 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

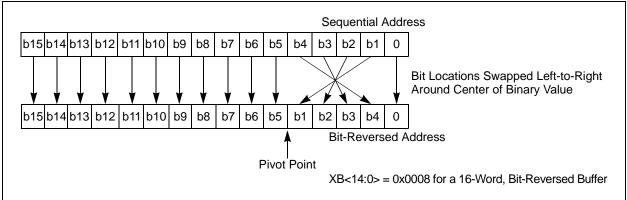

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program-to-data-space mapping feature lets any instruction access program space as if it were data space.

### 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory, while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain Working registers to each address space.

| TABLE 4-  | 17:         | ADC1   | REGIS                   | STER M                          | AP FO  | R dsPIC | 33FJ32(  | GP/MC)1  | 04 DEV  | ICES         |          |       |        |        |          |          |         |               |

|-----------|-------------|--------|-------------------------|---------------------------------|--------|---------|----------|----------|---------|--------------|----------|-------|--------|--------|----------|----------|---------|---------------|

| File Name | SFR<br>Addr | Bit 15 | Bit 14                  | Bit 13                          | Bit 12 | Bit 11  | Bit 10   | Bit 9    | Bit 8   | Bit 7        | Bit 6    | Bit 5 | Bit 4  | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300        |        |                         |                                 |        |         |          |          | ADC1 Da | ata Buffer   | 0        |       |        |        |          |          |         | xxxx          |

| ADC1BUF1  | 0302        |        |                         |                                 |        |         |          |          | ADC1 Da | ata Buffer   | 1        |       |        |        |          |          |         | xxxx          |

| ADC1BUF2  | 0304        |        |                         | ADC1 Data Buffer 2 xxxx         |        |         |          |          |         |              | xxxx     |       |        |        |          |          |         |               |

| ADC1BUF3  | 0306        |        | ADC1 Data Buffer 3 xxxx |                                 |        |         |          |          |         | xxxx         |          |       |        |        |          |          |         |               |

| ADC1BUF4  | 0308        |        | ADC1 Data Buffer 4 xxxx |                                 |        |         |          |          |         | xxxx         |          |       |        |        |          |          |         |               |

| ADC1BUF5  | 030A        |        |                         |                                 |        |         |          |          | ADC1 Da | ata Buffer   | 5        |       |        |        |          |          |         | xxxx          |

| ADC1BUF6  | 030C        |        |                         |                                 |        |         |          |          | ADC1 Da | ata Buffer   | 6        |       |        |        |          |          |         | xxxx          |

| ADC1BUF7  | 030E        |        |                         |                                 |        |         |          |          | ADC1 Da | ata Buffer   | 7        |       |        |        |          |          |         | xxxx          |

| ADC1BUF8  | 0310        |        |                         |                                 |        |         |          |          | ADC1 Da | ata Buffer   | 8        |       |        |        |          |          |         | xxxx          |

| ADC1BUF9  | 0312        |        |                         |                                 |        |         |          |          | ADC1 Da | ata Buffer   | 9        |       |        |        |          |          |         | xxxx          |

| ADC1BUFA  | 0314        |        |                         |                                 |        |         |          |          | ADC1 Da | ita Buffer ' | 10       |       |        |        |          |          |         | xxxx          |

| ADC1BUFB  | 0316        |        |                         |                                 |        |         |          |          | ADC1 Da | ta Buffer    | 11       |       |        |        |          |          |         | xxxx          |

| ADC1BUFC  | 0318        |        |                         |                                 |        |         |          |          | ADC1 Da | ita Buffer 1 | 12       |       |        |        |          |          |         | xxxx          |

| ADC1BUFD  | 031A        |        |                         |                                 |        |         |          |          | ADC1 Da | ita Buffer 1 | 13       |       |        |        |          |          |         | xxxx          |

| ADC1BUFE  | 031C        |        |                         |                                 |        |         |          |          | ADC1 Da | ita Buffer 1 | 14       |       |        |        |          |          |         | xxxx          |

| ADC1BUFF  | 031E        |        |                         |                                 |        |         |          |          | ADC1 Da | ita Buffer 1 | 15       |       |        |        |          |          |         | xxxx          |

| AD1CON1   | 0320        | ADON   | —                       | ADSIDL                          | —      | _       |          | FORM1    | FORM0   | SSRC2        | SSRC1    | SSRC0 | _      | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322        | VCFG2  | VCFG1                   | VCFG0                           | —      | _       | CSCNA    | CHPS1    | CHPS0   | BUFS         | —        | SMPI3 | SMPI2  | SMPI1  | SMPI0    | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324        | ADRC   | —                       | —                               | SAMC4  | SAMC3   | SAMC2    | SAMC1    | SAMC0   | ADCS7        | ADCS6    | ADCS5 | ADCS4  | ADCS3  | ADCS2    | ADCS1    | ADCS0   | 0000          |

| AD1CHS123 | 0326        | —      | _                       | —                               | —      | _       | CH123NB1 | CH123NB0 | CH123SB | —            | —        |       | _      | —      | CH123NA1 | CH123NA0 | CH123SA | 0000          |

| AD1CHS0   | 0328        | CH0NB  | _                       | -                               | CH0SB4 | CH0SB3  | CH0SB2   | CH0SB1   | CH0SB0  | <b>CH0NA</b> | —        |       | CH0SA4 | CH0SA3 | CH0SA2   | CH0SA1   | CH0SA0  | 0000          |

| AD1PCFGL  | 032C        | PCFG15 | _                       | - PCFG<12:0> <sup>(1)</sup> 000 |        |         |          |          | 0000    |              |          |       |        |        |          |          |         |               |

| AD1CSSL   | 0330        | CSS15  | _                       | _                               |        |         |          |          |         |              | CSS12:0> | (1)   |        |        |          |          |         | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PCFG<10:9> and CSS<10:9> bits are available in dsPIC33FJ32(GP/MC)104 devices only.

### TABLE 4-41: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      |    |    | Bit-Rev | ersed Ac | ldress  |

|----|----|-------|-----------|---------|----|----|---------|----------|---------|

| A3 | A2 | A1    | A0        | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0  | 0     | 1         | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0  | 1     | 0         | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0  | 1     | 1         | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1  | 0     | 0         | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1  | 0     | 1         | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1  | 1     | 0         | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1  | 1     | 1         | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0  | 0     | 0         | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0  | 0     | 1         | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0  | 1     | 0         | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0  | 1     | 1         | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1  | 0     | 0         | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1  | 0     | 1         | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1  | 1     | 0         | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1  | 1     | 1         | 15      | 1  | 1  | 1       | 1        | 15      |

### dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| <b>REGISTER 5</b>     | 5-1: NVMCO                      | N: FLASH I               | MEMORY C                    | ONTROL RE             | GISTER                |                       |                       |

|-----------------------|---------------------------------|--------------------------|-----------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>            | R/W-0 <sup>(1)</sup>     | U-0                         | U-0                   | U-0                   | U-0                   | U-0                   |

| WR                    | WREN                            | WRERR                    |                             |                       | —                     |                       | _                     |

| bit 15                |                                 |                          |                             |                       |                       |                       | bit 8                 |

|                       | (4)                             |                          |                             | (4)                   | (4)                   | (4)                   | (4)                   |

| U-0                   | R/W-0 <sup>(1)</sup>            | U-0                      | U-0                         | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  |

|                       | ERASE                           | —                        | —                           | NVMOP3 <sup>(2)</sup> | NVMOP2 <sup>(2)</sup> | NVMOP1 <sup>(2)</sup> | NVMOP0 <sup>(2)</sup> |

| bit 7                 |                                 |                          |                             |                       |                       |                       | bit 0                 |

| Legend:               |                                 | SO = Settat              | ale Only hit                |                       |                       |                       |                       |

| R = Readable          | hit.                            |                          |                             |                       | mantad hit raad       |                       |                       |

|                       |                                 | W = Writabl              |                             | -                     | nented bit, read      |                       |                       |

| -n = Value at I       | POR                             | '1' = Bit is s           | et                          | '0' = Bit is cle      | ared                  | x = Bit is unkr       | IOWN                  |

| bit 15                | WR: Write Con                   | trol bit <sup>(1)</sup>  |                             |                       |                       |                       |                       |

| 5                     |                                 |                          | v program or                | r erase operati       | on; the operatic      | on is self-timed      | and the bit is        |

|                       |                                 | hardware on              |                             | •                     |                       |                       |                       |

|                       | 0 = Program o                   |                          |                             |                       | e                     |                       |                       |

| bit 14                | WREN: Write E                   | nable bit <sup>(1)</sup> |                             |                       |                       |                       |                       |

|                       | 1 = Enables Fl                  |                          | erase operati               | ions                  |                       |                       |                       |

|                       | 0 = Inhibits Fla                |                          |                             |                       |                       |                       |                       |

| bit 13                | WRERR: Write                    | Sequence Er              | ror Flag bit <sup>(1)</sup> | )                     |                       |                       |                       |

|                       |                                 |                          | •                           |                       | rmination has oc      | curred (bit is se     | t automaticallv       |

|                       |                                 | attempt of the           |                             |                       |                       | (                     |                       |

|                       | 0 = The progra                  |                          |                             | pleted normally       | /                     |                       |                       |

| bit 12-7              | Unimplemente                    | ed: Read as 'o           | )'                          |                       |                       |                       |                       |

| bit 6                 | ERASE: Erase                    | /Program Ena             | ble bit <sup>(1)</sup>      |                       |                       |                       |                       |

|                       |                                 |                          |                             |                       | 3:0> on the nex       |                       |                       |

|                       |                                 |                          | -                           | Cified by NVINC       | P<3:0> on the         | next WR comm          | land                  |

| bit 5-4               | Unimplemente                    |                          |                             | (1.0)                 |                       |                       |                       |

| bit 3-0               | NVMOP<3:0>:                     | NVM Operati              | on Selection                | bits <sup>(1,2)</sup> |                       |                       |                       |

|                       | If ERASE = 1:                   | _                        |                             |                       |                       |                       |                       |

|                       | 1111 = No ope                   |                          | 4                           |                       |                       |                       |                       |

|                       | 1101 = Erase (<br>1100 = No ope | •                        | ient                        |                       |                       |                       |                       |

|                       | 0011 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 0010 = Memor                    |                          | operation                   |                       |                       |                       |                       |

|                       | 0001 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 0000 = No ope                   | ration                   |                             |                       |                       |                       |                       |

|                       | If ERASE = 0:                   |                          |                             |                       |                       |                       |                       |

|                       | 1111 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 1101 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 1100 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 0011 = Memor<br>0010 = No ope   |                          | in operation                |                       |                       |                       |                       |

|                       | 0001 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 0000 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | -                               |                          |                             |                       |                       |                       |                       |

|                       | ese bits can only               |                          |                             |                       |                       |                       |                       |

|                       | other combination               |                          |                             | implemented.          | ECISTED               |                       |                       |

| REGISTER 5            | -2. IN VIVINE                   |                          |                             |                       | LOISIEK               |                       |                       |

### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| U-0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| —   | —   |     |     | —   |     |     | _   |

© 2011-2014 Microchip Technology Inc.

#### **Reset Control Register** 6.1

| R/W-0                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0                                                                                                                                                                                                                                                                                                                                                  | U-0                                                                                                                       | U-0              | R/W-0           | R/W-0        |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|--------------|

| TRAPR                                              | IOPUWR                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                    | —                                                                                                                         | _                | СМ              | VREGS        |

| bit 15                                             | •                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                           |                  |                 | bit          |

| R/W-0                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                     | R/W-0            | R/W-1           | R/W-1        |

| EXTR                                               | SWR                                                                                                                                                                                                                                                                                                                                                             | SWDTEN <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                | WDTO                                                                                                                                                                                                                                                                                                                                                 | SLEEP                                                                                                                     | IDLE             | BOR             | POR          |

| bit 7                                              | own                                                                                                                                                                                                                                                                                                                                                             | OWBIEN                                                                                                                                                                                                                                                                                                                                                                                                               | MBIO                                                                                                                                                                                                                                                                                                                                                 | ULL!                                                                                                                      | IDEE             | Dorr            | bit          |

| Legend:                                            |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                           |                  |                 |              |

| R = Readable                                       | bit                                                                                                                                                                                                                                                                                                                                                             | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                       | nit                                                                                                                                                                                                                                                                                                                                                  | II – Unimplem                                                                                                             | nented bit, read | 1 as '0'        |              |

| -n = Value at F                                    |                                                                                                                                                                                                                                                                                                                                                                 | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                      | $0^{\circ} = \text{Bit is clear}$                                                                                         |                  | x = Bit is unki | nown         |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                           |                  |                 | IOWIT        |

| bit 15                                             | TRAPR: Trap                                                                                                                                                                                                                                                                                                                                                     | Reset Flag bit                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                           |                  |                 |              |

|                                                    | -                                                                                                                                                                                                                                                                                                                                                               | onflict Reset has                                                                                                                                                                                                                                                                                                                                                                                                    | s occurred                                                                                                                                                                                                                                                                                                                                           |                                                                                                                           |                  |                 |              |

|                                                    | 0 = A Trap C                                                                                                                                                                                                                                                                                                                                                    | onflict Reset has                                                                                                                                                                                                                                                                                                                                                                                                    | s not occurre                                                                                                                                                                                                                                                                                                                                        | d                                                                                                                         |                  |                 |              |

| oit 14                                             | IOPUWR: Ille                                                                                                                                                                                                                                                                                                                                                    | gal Opcode or l                                                                                                                                                                                                                                                                                                                                                                                                      | <b>Jninitialized</b>                                                                                                                                                                                                                                                                                                                                 | N Access Rese                                                                                                             | t Flag bit       |                 |              |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                 | al opcode detec                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                      | al address mo                                                                                                             | de or Uninitia   | lized W registe | er used as a |

|                                                    | Addroce                                                                                                                                                                                                                                                                                                                                                         | Pointer caused                                                                                                                                                                                                                                                                                                                                                                                                       | a Reset                                                                                                                                                                                                                                                                                                                                              |                                                                                                                           |                  |                 |              |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                      | Reset has not o                                                                                                           | courred          |                 |              |

| bit 13-10                                          | 0 = An Illega                                                                                                                                                                                                                                                                                                                                                   | I Opcode or Uni                                                                                                                                                                                                                                                                                                                                                                                                      | nitialized W                                                                                                                                                                                                                                                                                                                                         | Reset has not o                                                                                                           | ccurred          |                 |              |

|                                                    | 0 = An Illega<br>Unimplemen                                                                                                                                                                                                                                                                                                                                     | I Opcode or Uni<br>Ited: Read as '0                                                                                                                                                                                                                                                                                                                                                                                  | nitialized W                                                                                                                                                                                                                                                                                                                                         | Reset has not o                                                                                                           | ccurred          |                 |              |

|                                                    | 0 = An Illega<br>Unimplemen<br>CM: Configur                                                                                                                                                                                                                                                                                                                     | I Opcode or Uni<br><b>Ited:</b> Read as '0<br>ration Mismatch                                                                                                                                                                                                                                                                                                                                                        | nitialized W l<br>o'<br>Flag bit                                                                                                                                                                                                                                                                                                                     |                                                                                                                           | ccurred          |                 |              |

|                                                    | <ul> <li>0 = An Illega</li> <li>Unimplement</li> <li>CM: Configure</li> <li>1 = A Configure</li> </ul>                                                                                                                                                                                                                                                          | I Opcode or Uni<br>Ited: Read as '0                                                                                                                                                                                                                                                                                                                                                                                  | nitialized W l<br>,'<br>Flag bit<br>h Reset has o                                                                                                                                                                                                                                                                                                    | occurred                                                                                                                  | ccurred          |                 |              |

| bit 9                                              | 0 = An Illega<br>Unimplemen<br>CM: Configu<br>1 = A Configu<br>0 = A Configu                                                                                                                                                                                                                                                                                    | Il Opcode or Uni<br><b>Ited:</b> Read as '0<br>ration Mismatch<br>uration Mismatcl                                                                                                                                                                                                                                                                                                                                   | nitialized W l<br>o'<br>Flag bit<br>h Reset has o<br>h Reset has o                                                                                                                                                                                                                                                                                   | occurred<br>not occurred                                                                                                  | ccurred          |                 |              |

| bit 9                                              | 0 = An Illega<br>Unimplemen<br>CM: Configur<br>1 = A Configu<br>0 = A Configu<br>VREGS: Volt                                                                                                                                                                                                                                                                    | I Opcode or Uni<br><b>ated:</b> Read as '0<br>ration Mismatch<br>uration Mismatcl<br>uration Mismatcl                                                                                                                                                                                                                                                                                                                | nitialized W I<br>'<br>Flag bit<br>h Reset has<br>h Reset has<br>Stand-by Duri                                                                                                                                                                                                                                                                       | occurred<br>not occurred<br>ng Sleep bit                                                                                  | ccurred          |                 |              |

| bit 9                                              | 0 = An Illega<br>Unimplement<br>CM: Configur<br>1 = A Configur<br>0 = A Configur<br>VREGS: Volt<br>1 = Voltage re<br>0 = Voltage re                                                                                                                                                                                                                             | I Opcode or Uni<br><b>ated:</b> Read as '0<br>ration Mismatch<br>uration Mismatcl<br>uration Mismatcl<br>age Regulator S<br>egulator is active<br>egulator goes in                                                                                                                                                                                                                                                   | nitialized W I<br>Flag bit<br>h Reset has<br>h Reset has<br>Stand-by Duri<br>e during Slee<br>to Stand-by r                                                                                                                                                                                                                                          | occurred<br>not occurred<br>ng Sleep bit<br>p                                                                             |                  |                 |              |

| bit 9<br>bit 8                                     | 0 = An Illega<br>Unimplemen<br>CM: Configur<br>1 = A Configu<br>0 = A Configu<br>VREGS: Volt<br>1 = Voltage re<br>0 = Voltage re<br>EXTR: Extern                                                                                                                                                                                                                | Il Opcode or Uni<br><b>ated:</b> Read as 'o<br>ration Mismatch<br>uration Mismatch<br>uration Mismatch<br>age Regulator S<br>egulator is active<br>egulator goes in<br>hal Reset (MCLE                                                                                                                                                                                                                               | nitialized W ।<br>,'<br>Flag bit<br>h Reset has i<br>band-by Duri<br>e during Slee<br>to Stand-by r<br>र) Pin bit                                                                                                                                                                                                                                    | occurred<br>not occurred<br>ng Sleep bit<br>p<br>node during Sle                                                          |                  |                 |              |

| bit 9<br>bit 8                                     | 0 = An Illega<br>Unimplemen<br>CM: Configur<br>1 = A Configu<br>0 = A Configu<br>VREGS: Volt<br>1 = Voltage ro<br>0 = Voltage ro<br>EXTR: Extern<br>1 = A Master                                                                                                                                                                                                | Il Opcode or Uni<br><b>ated:</b> Read as 'o<br>ration Mismatch<br>uration Mismatch<br>uration Mismatch<br>age Regulator S<br>egulator is active<br>egulator goes in<br>hal Reset (MCLF<br>Clear (pin) Res                                                                                                                                                                                                            | nitialized W I<br>Flag bit<br>h Reset has a<br>b Reset has a<br>Stand-by Duri<br>e during Slee<br>to Stand-by r<br>$\overline{R}$ Pin bit<br>et has occurr                                                                                                                                                                                           | occurred<br>not occurred<br>ng Sleep bit<br>p<br>node during Sle                                                          |                  |                 |              |

| bit 9<br>bit 8<br>bit 7                            | 0 = An Illega<br>Unimplement<br>CM: Configur<br>1 = A Configur<br>0 = A Configur<br>VREGS: Volt<br>1 = Voltage re<br>0 = Voltage re<br>EXTR: Extern<br>1 = A Master<br>0 = A Master                                                                                                                                                                             | Il Opcode or Uni<br><b>ated:</b> Read as '0<br>ration Mismatch<br>uration Mismatch<br>uration Mismatch<br>age Regulator S<br>egulator is active<br>egulator goes in<br>hal Reset (MCLF<br>Clear (pin) Res<br>Clear (pin) Res                                                                                                                                                                                         | nitialized W I<br>Flag bit<br>h Reset has o<br>the Reset has o<br>Stand-by Duri<br>e during Slee<br>to Stand-by r<br>R) Pin bit<br>et has occurr<br>et has not occurr                                                                                                                                                                                | occurred<br>not occurred<br>ng Sleep bit<br>p<br>node during Sle<br>red<br>curred                                         |                  |                 |              |

| bit 13-10<br>bit 9<br>bit 8<br>bit 7<br>bit 6      | 0 = An Illega<br>Unimplement<br>CM: Configur<br>1 = A Configur<br>0 = A Configur<br>VREGS: Volt<br>1 = Voltage ru<br>0 = Voltage ru<br>EXTR: Extern<br>1 = A Master<br>0 = A Master<br>SWR: Softwar                                                                                                                                                             | Il Opcode or Uni<br><b>ated:</b> Read as '0<br>ration Mismatch<br>uration Mismatch<br>age Regulator S<br>egulator is active<br>egulator goes in<br>hal Reset (MCLF<br>Clear (pin) Res<br>Clear (pin) Res<br>are Reset (Instru                                                                                                                                                                                        | nitialized W I<br>Flag bit<br>h Reset has of<br>the Reset has of<br>Stand-by Duri<br>e during Slee<br>to Stand-by r<br>R) Pin bit<br>et has occurr<br>et has not occurr<br>et has not occurr<br>et has not occurr                                                                                                                                    | occurred<br>not occurred<br>ng Sleep bit<br>p<br>node during Sle<br>red<br>curred<br>it                                   |                  |                 |              |

| bit 9<br>bit 8<br>bit 7                            | 0 = An Illega<br>Unimplement<br>CM: Configur<br>1 = A Configur<br>0 = A Configur<br>VREGS: Volt<br>1 = Voltage ro<br>0 = Voltage ro<br>EXTR: Extern<br>1 = A Master<br>0 = A Master<br>SWR: Softwa<br>1 = A RESET                                                                                                                                               | Il Opcode or Uni<br><b>ated:</b> Read as '0<br>ration Mismatch<br>uration Mismatch<br>uration Mismatch<br>age Regulator S<br>egulator is active<br>egulator goes in<br>hal Reset (MCLF<br>Clear (pin) Res<br>Clear (pin) Res                                                                                                                                                                                         | nitialized W I<br>Flag bit<br>h Reset has of<br>Stand-by Duri<br>e during Slee<br>to Stand-by r<br>R) Pin bit<br>et has occurr<br>et has not oc<br>iction) Flag b<br>been execute                                                                                                                                                                    | occurred<br>not occurred<br>ng Sleep bit<br>p<br>node during Sle<br>ed<br>curred<br>it                                    |                  |                 |              |

| bit 9<br>bit 8<br>bit 7                            | 0 = An Illega<br>Unimplemen<br>CM: Configur<br>1 = A Configu<br>0 = A Configu<br>VREGS: Volt<br>1 = Voltage ro<br>0 = Voltage ro<br>0 = Voltage ro<br>EXTR: Extern<br>1 = A Master<br>0 = A Master<br>SWR: Softwa<br>1 = A RESET<br>0 = A RESET                                                                                                                 | Il Opcode or Uni<br><b>ated:</b> Read as 'o<br>ration Mismatch<br>uration Mismatch<br>uration Mismatch<br>age Regulator S<br>egulator is active<br>egulator goes in<br>hal Reset (MCLE<br>Clear (pin) Res<br>Clear (pin) Res<br>are Reset (Instru-<br>instruction has                                                                                                                                                | nitialized W I<br>Flag bit<br>h Reset has a<br>band-by Duri<br>e during Slee<br>to Stand-by r<br>$\overline{R}$ ) Pin bit<br>et has occurr<br>et has not oc<br>action) Flag b<br>been execute<br>not been exe                                                                                                                                        | occurred<br>not occurred<br>ng Sleep bit<br>p<br>node during Sle<br>red<br>curred<br>it<br>ed<br>cuted                    |                  |                 |              |

| bit 9<br>bit 8<br>bit 7<br>bit 6                   | 0 = An Illega<br>Unimplemen<br>CM: Configur<br>1 = A Configu<br>0 = A Configu<br>VREGS: Volt<br>1 = Voltage ro<br>0 = Voltage ro<br>EXTR: Extern<br>1 = A Master<br>0 = A Master<br>SWR: Softwa<br>1 = A RESET<br>0 = A RESET<br>SWDTEN: So<br>1 = WDT is e                                                                                                     | Il Opcode or Uni<br><b>ated:</b> Read as '0<br>ration Mismatch<br>uration Mismatch<br>uration Mismatch<br>age Regulator S<br>egulator is active<br>egulator goes in<br>hal Reset (MCLF<br>Clear (pin) Res<br>Clear (pin) Res<br>clear (pin) Res<br>are Reset (Instru-<br>instruction has<br>bitstruction has<br>oftware Enable/I<br>nabled                                                                           | nitialized W I<br>Flag bit<br>h Reset has a<br>band-by Duri<br>e during Slee<br>to Stand-by r<br>$\overline{R}$ ) Pin bit<br>et has occurr<br>et has not oc<br>action) Flag b<br>been execute<br>not been exe                                                                                                                                        | occurred<br>not occurred<br>ng Sleep bit<br>p<br>node during Sle<br>red<br>curred<br>it<br>ed<br>cuted                    |                  |                 |              |

| bit 9<br>bit 8<br>bit 7<br>bit 6                   | 0 = An Illega<br>Unimplement<br>CM: Configur<br>1 = A Configur<br>0 = A Configur<br>VREGS: Volt<br>1 = Voltage re<br>0 = Voltage re<br>0 = Voltage re<br>EXTR: Extern<br>1 = A Master<br>0 = A Master<br>SWR: Softwar<br>1 = A RESET<br>0 = A RESET<br>SWDTEN: Soft<br>1 = WDT is e<br>0 = WDT is d                                                             | Il Opcode or Uni<br><b>ited:</b> Read as 'o<br>ration Mismatch<br>uration Mismatch<br>uration Mismatch<br>age Regulator S<br>egulator is active<br>egulator goes in<br>hal Reset (MCLI<br>Clear (pin) Res<br>Clear (pin) Res<br>are Reset (Instru-<br>instruction has<br>instruction has<br>oftware Enable/I<br>nabled<br>isabled                                                                                    | nitialized W I<br>Flag bit<br>h Reset has i<br>b Reset has i<br>Stand-by Duri<br>e during Slee<br>to Stand-by r<br>R) Pin bit<br>et has occurr<br>et has not oc<br>loction) Flag b<br>been execute<br>not been exe<br>Disable of WI                                                                                                                  | occurred<br>not occurred<br>ng Sleep bit<br>p<br>node during Sle<br>red<br>curred<br>it<br>cuted<br>DT bit <sup>(2)</sup> |                  |                 |              |

| bit 9<br>bit 8<br>bit 7<br>bit 6<br>bit 5          | 0 = An Illega<br>Unimplement<br>CM: Configur<br>1 = A Configur<br>0 = A Configur<br>VREGS: Volt<br>1 = Voltage re<br>0 = Voltage re<br>0 = Voltage re<br>EXTR: Extern<br>1 = A Master<br>0 = A Master<br>SWR: Softwar<br>1 = A RESET<br>SWDTEN: Soft<br>1 = WDT is e<br>0 = WDT is d<br>WDTO: Wate                                                              | I Opcode or Uni<br><b>ited:</b> Read as '0<br>ration Mismatch<br>uration Mismatch<br>uration Mismatch<br>uration Mismatch<br>age Regulator S<br>egulator is active<br>egulator goes in<br>hal Reset (MCLF<br>Clear (pin) Res<br>Clear (pin) Res<br>are Reset (Instru-<br>instruction has in<br>instruction has in<br>oftware Enable/I<br>nabled<br>isabled<br>chdog Timer Tim                                        | nitialized W I<br>Flag bit<br>h Reset has of<br>the Reset has of<br>Stand-by Duri<br>e during Sleet<br>to Stand-by r<br>R) Pin bit<br>et has occurr<br>et has not occurr<br>et has not occurr<br>to been execute<br>not been execute<br>Disable of WI<br>e-out Flag bi                                                                               | occurred<br>not occurred<br>ng Sleep bit<br>p<br>node during Sle<br>red<br>curred<br>it<br>cuted<br>DT bit <sup>(2)</sup> |                  |                 |              |

| bit 9<br>bit 8<br>bit 7<br>bit 6<br>bit 5          | 0 = An Illega<br>Unimplement<br>CM: Configur<br>1 = A Configur<br>0 = A Configur<br>VREGS: Volt<br>1 = Voltage re<br>0 = Voltage re<br>0 = Voltage re<br>EXTR: Extern<br>1 = A Master<br>0 = A Master<br>SWR: Softwar<br>1 = A RESET<br>SWDTEN: Soft<br>1 = WDT is e<br>0 = WDT is d<br>WDTO: Watc<br>1 = WDT time                                              | Il Opcode or Uni<br><b>ited:</b> Read as 'o<br>ration Mismatch<br>uration Mismatch<br>uration Mismatch<br>age Regulator S<br>egulator is active<br>egulator goes in<br>hal Reset (MCLI<br>Clear (pin) Res<br>Clear (pin) Res<br>are Reset (Instru-<br>instruction has<br>instruction has<br>oftware Enable/I<br>nabled<br>isabled                                                                                    | initialized W I<br>Flag bit<br>h Reset has of<br>h Reset has of<br>Stand-by Duri<br>e during Slee<br>to Stand-by r<br>$\overline{R}$ ) Pin bit<br>et has occurr<br>et has not occurr<br>to the not occurr<br>on been execute<br>not been execute<br>Disable of WI<br>e-out Flag bi<br>red                                                            | occurred<br>not occurred<br>ng Sleep bit<br>p<br>node during Sle<br>red<br>curred<br>it<br>cuted<br>DT bit <sup>(2)</sup> |                  |                 |              |

| bit 9<br>bit 8<br>bit 7<br>bit 6                   | 0 = An Illega<br>Unimplement<br>CM: Configur<br>1 = A Configur<br>0 = A Configur<br>VREGS: Volt<br>1 = Voltage ro<br>0 = Voltage ro<br>EXTR: Extern<br>1 = A Master<br>0 = A Master<br>SWR: Softwa<br>1 = A RESET<br>0 = A RESET<br>SWDTEN: Soft<br>1 = WDT is e<br>0 = WDT is d<br>WDTO: Water<br>1 = WDT time<br>0 = WDT time                                 | I Opcode or Uni<br><b>ited:</b> Read as '0<br>ration Mismatch<br>uration Mismatch<br>uration Mismatch<br>uration Mismatch<br>age Regulator S<br>egulator is active<br>egulator goes in<br>hal Reset (MCLF<br>Clear (pin) Res<br>Clear (pin) Res<br>are Reset (Instru-<br>instruction has b<br>instruction has b<br>oftware Enable/I<br>nabled<br>isabled<br>sabled<br>bdog Timer Time<br>e-out has occurr            | initialized W I<br>Flag bit<br>h Reset has of<br>the Reset has of<br>Stand-by Duri<br>e during Slee<br>to Stand-by Duri<br>e during Slee<br>to Stand-by r<br>$\overline{R}$ ) Pin bit<br>et has occurr<br>et has not occurr<br>et has not occur<br>oction) Flag b<br>been execute<br>not been exe<br>Disable of WI<br>e-out Flag bi<br>red<br>curred | occurred<br>not occurred<br>ng Sleep bit<br>p<br>node during Sle<br>red<br>curred<br>it<br>cuted<br>DT bit <sup>(2)</sup> |                  |                 |              |

| bit 9<br>bit 8<br>bit 7<br>bit 6<br>bit 5<br>bit 4 | 0 = An Illega<br>Unimplement<br>CM: Configur<br>1 = A Configur<br>0 = A Configur<br>VREGS: Volt<br>1 = Voltage ro<br>0 = Voltage ro<br>0 = Voltage ro<br>EXTR: Extern<br>1 = A Master<br>0 = A Master<br>SWR: Softwa<br>1 = A RESET<br>0 = A RESET<br>SWDTEN: Sof<br>1 = WDT is e<br>0 = WDT is d<br>WDTO: Watc<br>1 = WDT time<br>0 = WDT time<br>0 = WDT time | I Opcode or Uni<br><b>ited:</b> Read as '0<br>ration Mismatch<br>uration Mismatch<br>uration Mismatch<br>uration Mismatch<br>age Regulator S<br>egulator is active<br>egulator goes in<br>hal Reset (MCLF<br>Clear (pin) Res<br>Clear (pin) Res<br>Clear (pin) Res<br>are Reset (Instru-<br>instruction has b<br>oftware Enable/I<br>nabled<br>isabled<br>hdog Timer Tim<br>e-out has occurr<br>e-out has not occurr | initialized W I<br>Flag bit<br>h Reset has a<br>Stand-by Duri<br>e during Slee<br>to Stand-by r<br>$\overline{R}$ ) Pin bit<br>et has occurr<br>et has not oc<br>loction) Flag b<br>been execute<br>not been exe<br>Disable of WI<br>e-out Flag bit<br>curred<br>o Flag bit<br>o mode                                                                | occurred<br>not occurred<br>ng Sleep bit<br>p<br>node during Sle<br>red<br>curred<br>it<br>cuted<br>DT bit <sup>(2)</sup> |                  |                 |              |

- - 2: If the FWDTEN Configuration bit is set to '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

### 6.2 System Reset

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family of devices have two types of Reset:

- Cold Reset

- Warm Reset

A Cold Reset is the result of a POR or a BOR. On a Cold Reset, the FNOSC<2:0> Configuration bits in the FOSCSEL Configuration register selects the device clock source.

A Warm Reset is the result of all other Reset sources, including the RESET instruction. On Warm Reset, the device will continue to operate from the current clock source as indicated by the Current Oscillator Selection (COSC<2:0>) bits in the Oscillator Control (OSCCON<14:12>) register.

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. The sequence in which this occurs is shown in Figure 6-2.

| Oscillator Mode           | Oscillator<br>Start-up Delay | Oscillator Start-up<br>Timer | PLL Lock Time        | Total Delay                                                       |

|---------------------------|------------------------------|------------------------------|----------------------|-------------------------------------------------------------------|

| FRC, FRCDIV16,<br>FRCDIVN | Toscd(1)                     | —                            | _                    | Toscd                                                             |

| FRCPLL                    | Toscd <sup>(1)</sup>         | —                            | ТLОСК <sup>(3)</sup> | Toscd <sup>(1)</sup> + Tlock <sup>(3)</sup>                       |

| MS                        | Toscd <sup>(1)</sup>         | Tost(2)                      | —                    | Toscd <sup>(1)</sup> + Tost <sup>(2)</sup>                        |

| HS                        | Toscd <sup>(1)</sup>         | Tost <sup>(2)</sup>          | —                    | Toscd <sup>(1)</sup> + Tost <sup>(2)</sup>                        |

| EC                        | —                            | —                            | —                    | —                                                                 |

| MSPLL                     | Toscd(1)                     | Tost(2)                      | TLOCK <sup>(3)</sup> | TOSCD <sup>(1)</sup> + TOST <sup>(2)</sup> + TLOCK <sup>(3)</sup> |