Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 13                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 4x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 18-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gp101-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

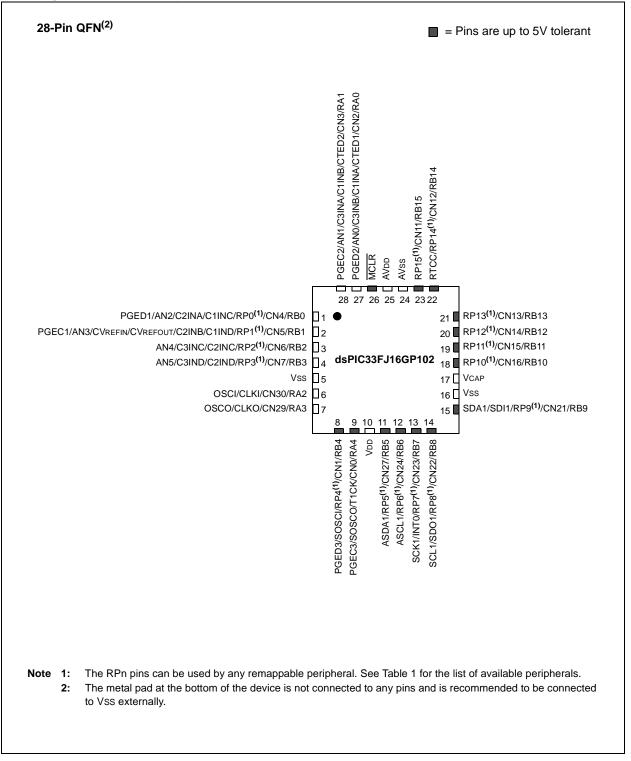

### Pin Diagrams (Continued)

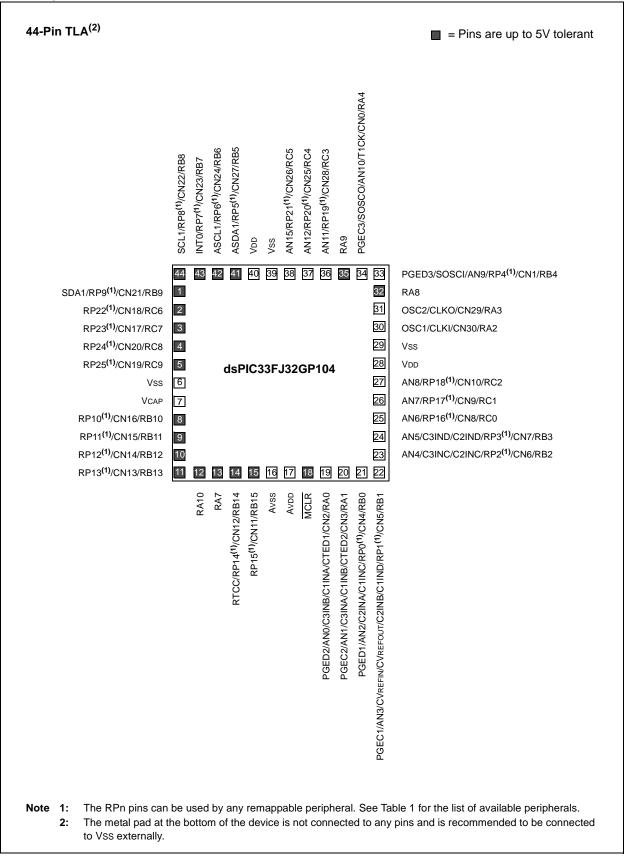

### Pin Diagrams (Continued)

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| TABLE 4-  | 16:         | ADC1   | REGIST                | ER MA  | P FOR c | ISPIC33 | FJXX(G   | P/MC)102             | 2 DEVIC     | ES        | -     |       |        |        |          | -        |         |               |

|-----------|-------------|--------|-----------------------|--------|---------|---------|----------|----------------------|-------------|-----------|-------|-------|--------|--------|----------|----------|---------|---------------|

| File Name | SFR<br>Addr | Bit 15 | Bit 14                | Bit 13 | Bit 12  | Bit 11  | Bit 10   | Bit 9                | Bit 8       | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300        |        |                       |        |         |         |          |                      | ADC1 Data   | Buffer 0  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF1  | 0302        |        |                       |        |         |         |          |                      | ADC1 Data   | Buffer 1  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF2  | 0304        |        |                       |        |         |         |          |                      | ADC1 Data   | Buffer 2  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF3  | 0306        |        |                       |        |         |         |          |                      | ADC1 Data   | Buffer 3  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF4  | 0308        |        |                       |        |         |         |          |                      | ADC1 Data   | Buffer 4  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF5  | 030A        |        |                       |        |         |         |          |                      | ADC1 Data   | Buffer 5  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF6  | 030C        |        |                       |        |         |         |          |                      | ADC1 Data   | Buffer 6  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF7  | 030E        |        |                       |        |         |         |          |                      | ADC1 Data   | Buffer 7  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF8  | 0310        |        |                       |        |         |         |          |                      | ADC1 Data   | Buffer 8  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF9  | 0312        |        | ADC1 Data Buffer 9 xx |        |         |         |          |                      |             |           |       |       | xxxx   |        |          |          |         |               |

| ADC1BUFA  | 0314        |        |                       |        |         |         |          | A                    | ADC1 Data E | Buffer 10 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFB  | 0316        |        |                       |        |         |         |          | ŀ                    | ADC1 Data B | Buffer 11 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFC  | 0318        |        |                       |        |         |         |          | ŀ                    | ADC1 Data E | Buffer 12 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFD  | 031A        |        |                       |        |         |         |          | ŀ                    | ADC1 Data E | Buffer 13 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFE  | 031C        |        |                       |        |         |         |          | A                    | ADC1 Data E | Buffer 14 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFF  | 031E        |        |                       |        |         |         |          | A                    | ADC1 Data E | Buffer 15 |       |       |        |        |          |          |         | xxxx          |

| AD1CON1   | 0320        | ADON   | _                     | ADSIDL | _       | —       | _        | FORM1                | FORM0       | SSRC2     | SSRC1 | SSRC0 | _      | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322        | VCFG2  | VCFG1                 | VCFG0  | _       | —       | CSCNA    | CHPS1                | CHPS0       | BUFS      |       | SMPI3 | SMPI2  | SMPI1  | SMPI0    | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324        | ADRC   | _                     | —      | SAMC4   | SAMC3   | SAMC2    | SAMC1                | SAMC0       | ADCS7     | ADCS6 | ADCS5 | ADCS4  | ADCS3  | ADCS2    | ADCS1    | ADCS0   | 0000          |

| AD1CHS123 | 0326        | —      | _                     | _      | _       | —       | CH123NB1 | CH123NB0             | CH123SB     | _         |       |       | _      | _      | CH123NA1 | CH123NA0 | CH123SA | 0000          |

| AD1CHS0   | 0328        | CH0NB  | _                     | _      | CH0SB4  | CH0SB3  | CH0SB2   | CH0SB1               | CH0SB0      | CH0NA     |       |       | CH0SA4 | CH0SA3 | CH0SA2   | CH0SA1   | CH0SA0  | 0000          |

| AD1PCFGL  | 032C        | —      | _                     | —      | _       | —       |          | 10:9> <sup>(1)</sup> | _           | _         | _     |       |        | PC     | FG<5:0>  |          |         | 0000          |

| AD1CSSL   | 0330        | —      | _                     | —      | —       | _       | CSS<1    | 0:9> <sup>(1)</sup>  | —           | _         | —     |       |        | С      | SS<5:0>  |          |         | 0000          |

### TABLE 4-16: ADC1 REGISTER MAP FOR dsPIC33FJXX(GP/MC)102 DEVICES

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PCFG<10:9> and CSS<10:9> bits are available in dsPIC33FJ32(GP/MC)101/102 devices only.

### TABLE 4-21: COMPARATOR REGISTER MAP

| File Name        | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|------------------|-------------|--------|--------|--------|--------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|---------------|

| CMSTAT           | 0650        | CMSIDL | _      | _      | _      | _        | C3EVT    | C2EVT    | C1EVT    | _        | —        | —        | —        | —        | C3OUT    | C2OUT    | C1OUT    | 0000          |

| CVRCON           | 0652        | —      | _      | _      | _      | _        | VREFSEL  | BGSEL1   | BGSEL0   | CVREN    | CVROE    | CVRR     | _        | CVR3     | CVR2     | CVR1     | CVR0     | 0000          |

| CM1CON           | 0654        | CON    | COE    | CPOL   |        | -        | -        | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM1MSKSRC        | 0656        | _      | _      | -      | _      | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM1MSKCON        | 0658        | HLMS   | —      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM1FLTR          | 065A        | -      | —      |        |        | -        | -        | _        | _        | _        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM2CON           | 065C        | CON    | COE    | CPOL   |        | -        | -        | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM2MSKSRC        | 065E        | -      | —      |        |        | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM2MSKCON        | 0660        | HLMS   | —      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM2FLTR          | 0662        | -      | —      |        |        | -        | -        | _        | _        | _        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM3CON           | 0664        | CON    | COE    | CPOL   |        | -        | -        | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM3MSKSRC        | 0666        | -      | —      |        |        | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| <b>CM3MSKCON</b> | 0668        | HLMS   | _      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM3FLTR          | 066A        | _      | —      | —      | —      | _        | —        | _        | _        | -        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-22: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10                  | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|-------------------------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| RPINR0       | 0680        | _      | —      | —      |        | I      | NT1R<4:0>               |       |       | —     | —     | —     | _     | —     | —          | —     | _     | 1F00          |

| RPINR1       | 0682        | _      | _      | _      | _      | _      | _                       | _     | _     | _     | _     | _     |       | I     | NT2R<4:0>  |       |       | 001F          |

| RPINR3       | 0686        | _      | _      | _      |        | Т      | 3CKR<4:0>               |       |       | _     | _     | _     |       | Т     | 2CKR<4:0>  | •     |       | 1F1F          |

| RPINR4       | 0688        | —      | _      | _      |        | Τŧ     | 5CKR<4:0>(1             | )     |       | _     | _     | _     |       | T4    | CKR<4:0>   | 1)    |       | 1F1F          |

| RPINR7       | 068E        | —      | _      | _      |        |        | IC2R<4:0>               |       |       | _     | _     | —     |       |       | IC1R<4:0>  |       |       | 1F1F          |

| RPINR8       | 0690        | —      | _      | _      | _      | _      | —                       | —     | _     | _     | _     | —     |       |       | IC3R<4:0>  |       |       | 001F          |

| RPINR11      | 0696        | —      | _      | _      | _      | _      | _                       | —     | _     | _     | _     | —     |       | C     | CFAR<4:0   | >     |       | 001F          |

| RPINR18      | 06A4        | —      | _      | _      |        | U      | 1CTSR<4:0>              |       |       | _     | _     | —     |       | U     | 1RXR<4:0:  | >     |       | 1F1F          |

| RPINR20      | 06A8        | —      | _      | _      |        | S      | CK1R<4:0> <sup>(1</sup> | )     |       | _     | _     | —     |       | SI    | DI1R<4:0>( | 1)    |       | 1F1F          |

| RPINR21      | 06AA        | _      | _      | _      | —      | —      | —                       | _     | _     | _     | —     | _     |       | ;     | SS1R<4:0>  |       |       | 001F          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

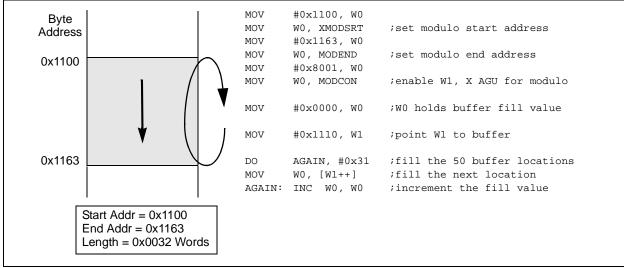

### 4.4 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the circular buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

### 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear). The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

### 4.4.2 W ADDRESS REGISTER SELECTION

- The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select which registers will operate with Modulo Addressing.

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled.

- If YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

# FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts (Part IV)" (DS70300) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family CPU. It has the following features:

- Up to eight processor exceptions and software traps

- Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 7-1. The IVT resides in program memory, starting at location, 000004h. The IVT contains 126 vectors consisting of eight non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR). Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 will take priority over interrupts at any other vector address.

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices implement up to 26 unique interrupts and 4 nonmaskable traps. These are summarized in Table 7-1 and Table 7-2.

### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a way to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications to facilitate evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

# 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices clear their registers in response to a Reset, forcing the PC to zero. The Digital Signal Controller then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

# 12.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Timer2/3 and Timer4/5 have three 2-bit timers that can also be configured as two independent 16-bit timers with selectable operating modes.

Note 1: Timer4 and Timer5 are available in dsPIC33FJ32(GP/MC10X) devices only.

As a 32-bit timer, Timer2/3 and Timer4/5 permit operation in three modes:

- Two independent 16-bit timers (e.g., Timer2 and Timer3 or Timer4 and Timer5) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer (Timer2/3 and Timer4/5)

- Single 32-bit synchronous counter (Timer2/3 and Timer4/5)

Timer2/3 and Timer4/5 also support:

- Timer gate operation

- Selectable prescaler settings

- Timer operation during Idle and Sleep modes

- Interrupt on a 32-bit Period register match

- Time base for input capture and output compare modules (Timer2 and Timer3 only)

- ADC1 event trigger (Timer2/3 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the event trigger. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers (see Register 12-1 through Register 12-4). For 32-bit timer/counter operation, Timer2/4 is the least significant word (Isw) and Timer3/5 is the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are used for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

### 12.1 32-Bit Operation

To configure Timer2/3 and Timer4/5 for 32-bit operation:

- 1. Set the T32 control bit.

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3/PR5 contains the msw of the value, while PR2/PR4 contains the least significant word (lsw).

- 5. If interrupts are required, set the Timer3 (or Timer5) Interrupt Enable bit, T3IE (or T5IE). Use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. While Timer2/Timer4 controls the timer, the interrupt appears as a Timer3/Timer5 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair, TMR3:TMR2 or TMR5:TMR4, which always contains the msw of the count, while TMR2 or TMR4 contains the lsw.

### 12.2 16-Bit Operation

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the Timerx Interrupt Enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

NOTES:

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | RW-0     |

|--------|-----|-----|-----|----------|----------|----------|----------|

| —      | —   | _   | —   | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 |

| bit 15 |     |     |     |          |          |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-12 Unimplemented: Read as '0'

| bit 11-8 | SELSRCC<3:0>: Mask C Ir | nput Select bits |

|----------|-------------------------|------------------|

|          |                         |                  |

| SELSRCC<3:0>: Mask C Input Select bits                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1111 = Reserved                                                                                                                                                                                                                                                |

| 1110 = Reserved                                                                                                                                                                                                                                                |

| 1101 = Reserved                                                                                                                                                                                                                                                |

| 1100 = Reserved                                                                                                                                                                                                                                                |

| 1011 = Reserved                                                                                                                                                                                                                                                |

| 1010 = Reserved                                                                                                                                                                                                                                                |

| 1001 = Reserved                                                                                                                                                                                                                                                |

| 1000 = Reserved                                                                                                                                                                                                                                                |

| 0111 = Reserved                                                                                                                                                                                                                                                |

| 0110 = Reserved                                                                                                                                                                                                                                                |

| 0101 = PWM1H3                                                                                                                                                                                                                                                  |

| 0100 = PWM1L3                                                                                                                                                                                                                                                  |

| 0011 = PWM1H2                                                                                                                                                                                                                                                  |

| 0010 = PWM1L2                                                                                                                                                                                                                                                  |

| 0001 = PWM1H1                                                                                                                                                                                                                                                  |

| 0000 = PWM1L1                                                                                                                                                                                                                                                  |

| SELSRCB<3:0>: Mask B Input Select bits                                                                                                                                                                                                                         |

| SELSINGES. Wask D input Select bits                                                                                                                                                                                                                            |

| 1111 = Reserved                                                                                                                                                                                                                                                |

| -                                                                                                                                                                                                                                                              |

| 1111 = Reserved                                                                                                                                                                                                                                                |

| 1111 = Reserved<br>1110 = Reserved                                                                                                                                                                                                                             |

| 1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved                                                                                                                                                                                                          |

| 1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1100 = Reserved                                                                                                                                                                                       |

| 1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1000 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved                                                                                                                              |

| 1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1000 = Reserved<br>1010 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved                                                                                                           |

| 1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1000 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved                                                                                                                              |

| 1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1000 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0111 = Reserved                                                                     |

| 1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1000 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved                               |

| 1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1000 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = PWM1H3<br>0100 = PWM1L3                                   |

| 1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1001 = Reserved<br>1010 = Reserved<br>1010 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = PWM1H3<br>0100 = PWM1L3<br>0011 = PWM1H2                                     |

| 1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1001 = Reserved<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = PWM1H3<br>0100 = PWM1L3<br>0011 = PWM1H2<br>0010 = PWM1L2 |

| 1111 = Reserved<br>1110 = Reserved<br>1101 = Reserved<br>1001 = Reserved<br>1010 = Reserved<br>1010 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = PWM1H3<br>0100 = PWM1L3<br>0011 = PWM1H2                                     |

|                                                                                                                                                                                                                                                                |

bit 7-4

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| U-0           | U-0                                                                                                     | U-0                                                                                                                 | U-0             | U-0                                  | U-0              | U-0            | U-0    |

|---------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------|------------------|----------------|--------|

|               | _                                                                                                       |                                                                                                                     |                 |                                      | _                |                |        |

| bit 15        |                                                                                                         |                                                                                                                     |                 |                                      |                  |                | bit 8  |

|               |                                                                                                         |                                                                                                                     |                 |                                      |                  |                |        |

| U-0           | R/W-0                                                                                                   | R/W-0                                                                                                               | R/W-0           | R/W-0                                | R/W-0            | R/W-0          | R/W-0  |

|               | CFSEL2                                                                                                  | CFSEL1                                                                                                              | CFSEL0          | CFLTREN                              | CFDIV2           | CFDIV1         | CFDIV0 |

| bit 7         |                                                                                                         |                                                                                                                     |                 |                                      |                  |                | bit 0  |

| Legend:       |                                                                                                         |                                                                                                                     |                 |                                      |                  |                |        |

| R = Readab    | la hit                                                                                                  | W = Writable                                                                                                        | hit             | LI – Unimplom                        | nented bit, read | oo 'O'         |        |

| -n = Value at |                                                                                                         | 1' = Bit is set                                                                                                     |                 | 0 = 0 miniplent<br>0' = Bit is clear |                  | x = Bit is unk | 00000  |

|               | TFOR                                                                                                    |                                                                                                                     |                 |                                      | areu             |                | nown   |

| bit 15-7      | Unimplemen                                                                                              | ted: Read as '                                                                                                      | 0'              |                                      |                  |                |        |

| bit 6-4       | -                                                                                                       | : Comparator I                                                                                                      |                 | ock Select bits                      |                  |                |        |

|               | 110 = Reserv<br>101 = Timer3<br>100 = Timer2<br>011 = Reserv<br>010 = PWM \$<br>001 = Fosc<br>000 = Fcy |                                                                                                                     | Frigger         |                                      |                  |                |        |

| bit 3         | <b>CFLTREN:</b> C<br>1 = Digital filte<br>0 = Digital filte                                             |                                                                                                                     | er Enable bit   |                                      |                  |                |        |

| bit 2-0       | -                                                                                                       | Comparator F<br>Divide 1:128<br>Divide 1:64<br>Divide 1:32<br>Divide 1:16<br>Divide 1:8<br>Divide 1:4<br>Divide 1:2 | ilter Clock Div | ide Select bits                      |                  |                |        |

### REGISTER 20-5: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

# REGISTER 21-6: RTCVAL (WHEN RTCPTR<1:0> = 01): RTCC WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-----|-------|-------|-------|

| —      | —   |     | _   | _   | WDAY2 | WDAY1 | WDAY0 |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 Ur | nimplemented: Read as '0' |

|--------------|---------------------------|

|--------------|---------------------------|

- bit 10-8 **WDAY<2:0>:** Binary Coded Decimal Value of Weekday Digit bits Contains a value from 0 to 6.

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits Contains a value from 0 to 2.

- bit 3-0 **HRONE<3:0>:** Binary Coded Decimal Value of Hour's Ones Digit bits Contains a value from 0 to 9.

- **Note 1:** A write to this register is only allowed when RTCWREN = 1.

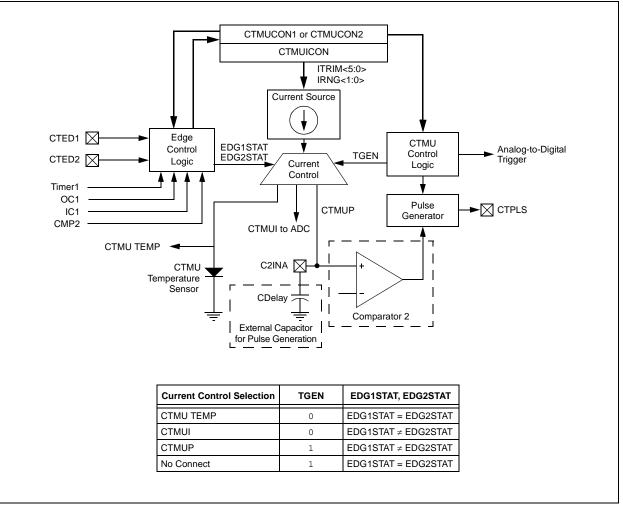

### FIGURE 22-1: CTMU BLOCK DIAGRAM

# 25.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 25.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- Simultaneous debugging sessions

- File History and Bug Tracking:

- Local file history feature

- Built-in support for Bugzilla issue tracker

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| DC CHARACTERISTICS |        |                                                                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |                       |       |                                                                                                                                     |

|--------------------|--------|-----------------------------------------------------------------------|-------------------------------------------------------|---------------------|-----------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                        | Min                                                   | Тур <sup>(1)</sup>  | Мах                   | Units | Conditions                                                                                                                          |

| DI60a              | licl   | Input Low Injection Current                                           | 0                                                     | -5 <sup>(5,8)</sup> | _                     | mA    | All pins excep <u>t VDD,</u> Vss,<br>AVDD, AVss, MCLR,<br>VCAP, SOSCI, SOSCO<br>and RB14                                            |

| DI60b              | ІІСН   | Input High Injection Current                                          | 0                                                     | _                   | +5 <sup>(6,7,8)</sup> | mA    | All pins except VDD,<br>Vss, AVDD, AVss,<br>MCLR, VCAP, SOSCI,<br>SOSCO, RB14 and<br>digital 5V tolerant<br>designated pins         |

| DI60c              | ∑ lict | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | -20 <sup>(9)</sup>                                    | _                   | +20 <sup>(9)</sup>    | mA    | Absolute instantaneous<br>sum of all $\pm$ input<br>injection currents from<br>all I/O pins<br>(  IICL +   IICH  ) $\leq \sum$ IICT |

### TABLE 26-10: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 5: VIL source < (Vss 0.3). Characterized but not tested.

**6:** Non-5V tolerant pins, VIH source > (VDD + 0.3), 5V tolerant pins, VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins, not excluded under IICL or IICH conditions, are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

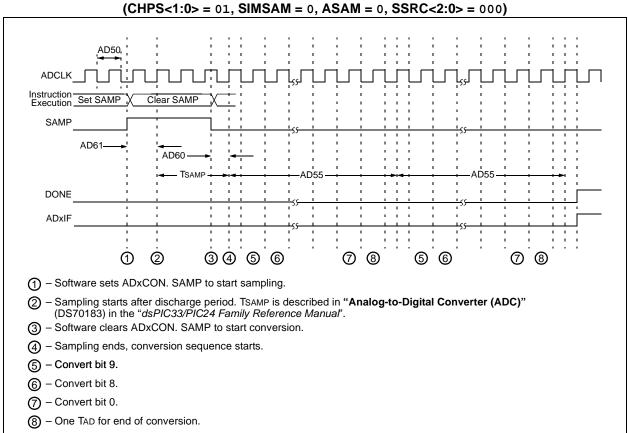

# FIGURE 26-31: ADC CONVERSION TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000

| DC CHARACTERISTICS |        |                         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |    |           |     |            |

|--------------------|--------|-------------------------|-------------------------------------------------------|----|-----------|-----|------------|

| Param<br>No.       | Symbol | Characteristic          | Min. Typ Max. Units Co                                |    |           |     | Conditions |

| VRD310             | CVRES  | Resolution              | CVRSRC/24                                             | _  | CVRSRC/32 | LSb |            |

| VRD311             | CVRAA  | Absolute Accuracy       | —                                                     |    | 0.5       | LSb |            |

| VRD312             | CVRUR  | Unit Resistor Value (R) | _                                                     | 2k |           | Ω   |            |

### TABLE 26-53: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

### TABLE 26-54: CTMU CURRENT SOURCE SPECIFICATIONS

| DC CHARACTERISTICS |                       |                                        | (unless | otherv | rating C<br>vise stat<br>perature | t <b>ed)</b><br>-40°C | ns:3.0V to 3.6V<br>≤ TA ≤ +85°C for Industrial<br>≤ TA ≤ +125°C for Extended |  |  |

|--------------------|-----------------------|----------------------------------------|---------|--------|-----------------------------------|-----------------------|------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol Characteristic |                                        | Min.    | Тур    | Max.                              | Units                 | Conditions                                                                   |  |  |

|                    | CTMU Current Source   |                                        |         |        |                                   |                       |                                                                              |  |  |

| CTMUI1             | Ιουτ1                 | Base Range <sup>(1)</sup>              | 320     | 550    | 980                               | na                    | IRNG<1:0> bits (CTMUICON<9:8>) = 0b01                                        |  |  |

| CTMUI2             | Ιουτ2                 | 10x Range <sup>(1)</sup>               | 3.2     | 5.5    | 9.8                               | μΑ                    | IRNG<1:0> bits (CTMUICON<9:8>) = 0b10                                        |  |  |

| CTMUI3             | Ιουτ3                 | 100x Range <sup>(1)</sup>              | 32      | 55     | 98                                | μA                    | IRNG<1:0> bits (CTMUICON<9:8>) = 0b11                                        |  |  |

|                    |                       |                                        |         | Intern | al Diod                           | e                     |                                                                              |  |  |

| CTMUFV1            | VF                    | Forward Voltage <sup>(2)</sup>         | _       | 0.77   | _                                 | V                     | IRNG<1:0> bits (CTMUICON<9:8>) = 0b11<br>@ +25°C                             |  |  |

| CTMUFV2            | Vfvr                  | Forward Voltage<br>Rate <sup>(2)</sup> | —       | -1.38  | _                                 | mV/⁰C                 | IRNG<1:0> bits (CTMUICON<9:8>) = 0b11                                        |  |  |

Note 1: Nominal value at center point of current trim range (ITRIM<5:0> bits (CTMUICON<15:10>) = 0b000000).

2: ADC module configured for conversion speed of 500 ksps. Parameters are characterized but not tested in manufacturing.

### 27.1 High-Temperature DC Characteristics

### TABLE 27-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                  | Temperature Range | Max MIPS                                                       |

|----------------|----------------------------|-------------------|----------------------------------------------------------------|

|                | (in Volts)                 | (in °C)           | dsPIC33FJ16(GP/MC)101/102 and<br>dsPIC33FJ32(GP/MC)101/102/104 |

| HDC5           | Vbor – 3.6V <sup>(1)</sup> | -40°C to +150°C   | 5                                                              |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules, such as the ADC, etc., may have degraded performances below VDDMIN.

### TABLE 27-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| High Temperature Devices                                                                                                                                                               |        |     |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40 | —           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40 | —           | +150 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     |     | Pint + Pi/c | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | PDMAX  | (   | TJ — TA)/θJ | IA   | W    |

### TABLE 27-3: DC CHARACTERISTICS: OPERATING CURRENT (IDD))

| DC CHARACTERISTICS |                |            | (unless oth      | erwise stated) | litions: 3.0V to 3.6V $0^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |  |  |

|--------------------|----------------|------------|------------------|----------------|----------------------------------------------------------------------------------|--|--|

| Parameter<br>No.   | Typical        | Мах        | Units Conditions |                |                                                                                  |  |  |

| Operating Cur      | rent (IDD) – d | dsPIC33FJ1 | 6(GP/MC)10)      | ( Devices      |                                                                                  |  |  |

| DC20e              | 1.3            | 1.7        | mA               | 3.3V           | LPRC (32.768 kHz)                                                                |  |  |

| DC22e              | 7.0            | 8.5        | mA               | 3.3V           | 5 MIPS                                                                           |  |  |

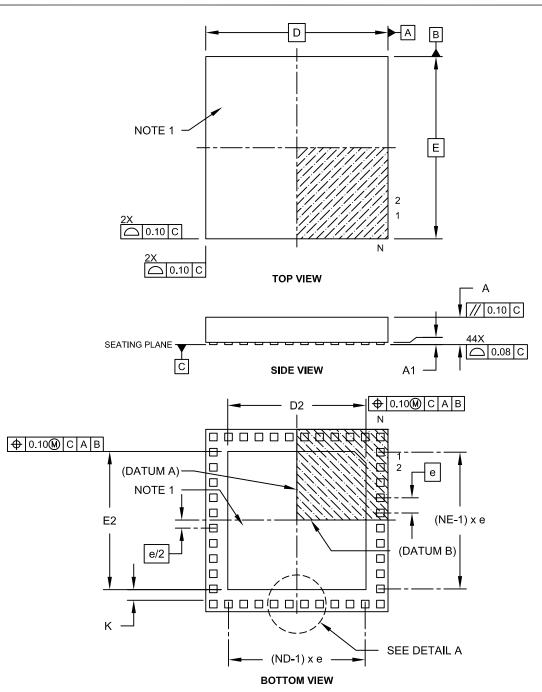

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-157C Sheet 1 of 2

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Pforzheim Tel: 49-7231-424750

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

10/28/13