Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gp102-e-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

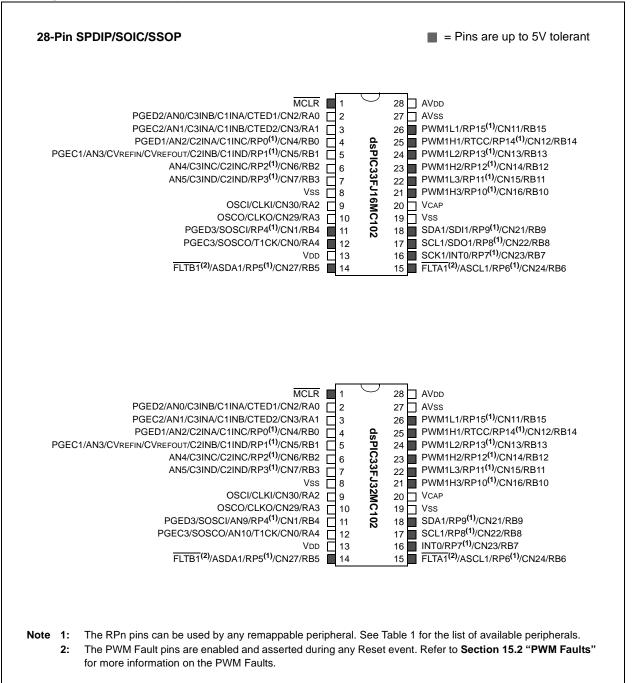

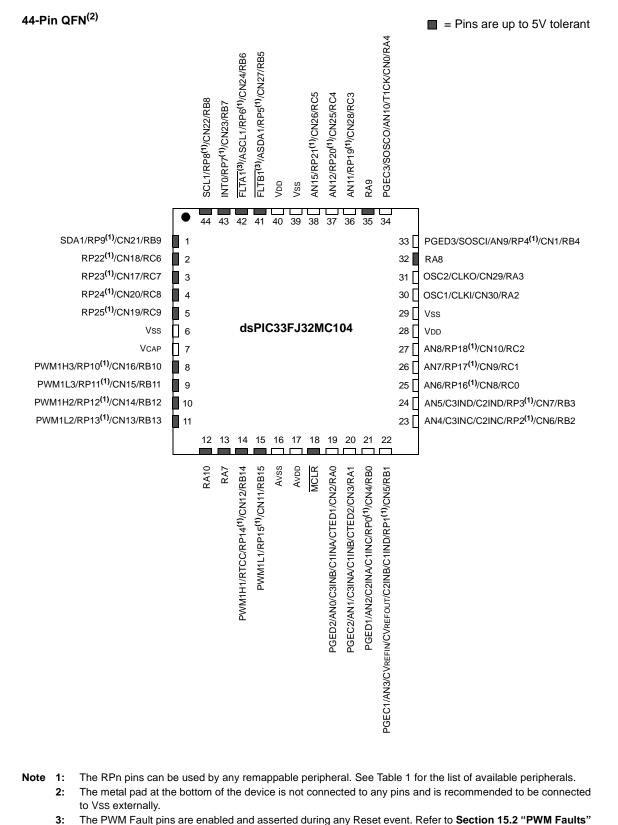

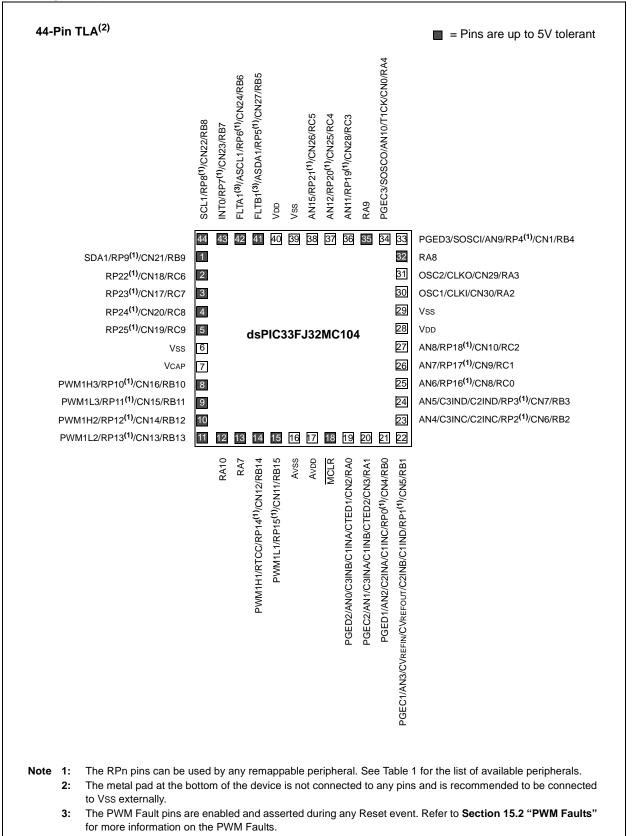

#### **Pin Diagrams (Continued)**

### Pin Diagrams (Continued)

3: The PWM Fault pins are enabled and asserted during any Reset event. Refer to Section 15.2 "PWM Faults" for more information on the PWM Faults.

#### **Pin Diagrams (Continued)**

| Pin Name | Pin<br>Type | Buffer<br>Type              | PPS                    |                                                                                                                                                                                     | Description                                                                                |                    |  |  |  |

|----------|-------------|-----------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------|--|--|--|

| AVdd     | P           | Р                           | No                     | AVDD is connected to V                                                                                                                                                              | og modules. This pin must b<br>DD in the 18-pin dsPIC33FJ<br>evices. In all other devices, | XXGP101 and 20-pin |  |  |  |

| AVss     | Р           | Р                           | No                     | Ground reference for analog modules. AVss is connected to Vss in the 18-pin dsPIC33FJXXGP101 and 20-pin dsPIC33FJXXMC101 devices. In all other devices, AVss is separated from Vss. |                                                                                            |                    |  |  |  |

| Vdd      | Р           | _                           | No                     | Positive supply for perip                                                                                                                                                           | oheral logic and I/O pins.                                                                 |                    |  |  |  |

| VCAP     | Р           | _                           | No                     | CPU logic filter capacitor connection.                                                                                                                                              |                                                                                            |                    |  |  |  |

| Vss      | Р           | _                           | No                     | Ground reference for logic and I/O pins.                                                                                                                                            |                                                                                            |                    |  |  |  |

|          |             | CMOS comp<br>nitt Trigger i | P = Power<br>I = Input |                                                                                                                                                                                     |                                                                                            |                    |  |  |  |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels O = Output PPS = Peripheral Pin Select

**Note 1:** An external pull-down resistor is required for the FLTA1 pin in dsPIC33FJXXMC101 (20-pin) devices.

2: The FLTA1 pin and the PWM1Lx/PWM1Hx pins are available in dsPIC(16/32)MC10X devices only.

3: The FLTB1 pin is available in dsPIC(16/32)MC102/104 devices only.

4: The PWM Fault pins are enabled during any Reset event. Refer to **Section 15.2** "**PWM Faults**" for more information on the PWM Faults.

5: Not all pins are available on all devices. Refer to the specific device in the "**Pin Diagrams**" section for availability.

6: These pins are available in dsPIC33FJ32(GP/MC)104 (44-pin) devices only.

#### TABLE 4-23: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJXXGP101 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| RPOR0        | 06C0        |        | _      |        |        |        | RP1R<4:0> | •     |       | —     |       |       |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR2        | 06C4        | _      | _      | _      | _      | _      | —         | _     | _     | _     | _     | _     |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3        | 06C6        | _      | _      | _      |        |        | RP7R<4:0> | •     |       | —     | _     | _     | _     | _     | _          | _     | _     | 0000          |

| RPOR4        | 06C8        | _      | _      |        |        |        | RP9R<4:0> | >     |       | —     |       |       |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR7        | 06CE        | _      | _      |        |        |        | RP15R<4:0 | >     |       | —     |       |       |       | F     | RP14R<4:0> | >     |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJXXMC101 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4 | Bit 3      | Bit 2     | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|------------|-----------|-------|-------|-------|-------|------------|-------|------------|-----------|-------|-------|---------------|

| RPOR0        | 06C0        | _      | _      | _      |        |            | RP1R<4:0> | •     |       | _     | _     | _          |       |            | RP0R<4:0> |       |       | 0000          |

| RPOR2        | 06C4        | _      | _      | _      | —      | _          | _         | _     | _     | _     | _     | _          |       |            | RP4R<4:0> |       |       | 0000          |

| RPOR3        | 06C6        | _      | _      | _      |        |            | RP7R<4:0> | •     |       | _     | _     | _          | _     | _          | _         | _     | _     | 0000          |

| RPOR4        | 06C8        | _      | _      | _      |        |            | RP9R<4:0> | •     |       | _     | _     | _          |       |            | RP8R<4:0> |       |       | 0000          |

| RPOR6        | 06CC        | _      | _      | _      |        | RP13R<4:0> |           |       | _     | _     | _     | RP12R<4:0> |       |            | 0000      |       |       |               |

| RPOR7        | 06CE        |        | _      | -      |        | RP15R<4:0> |           |       | _     | _     | _     |            | F     | RP14R<4:0> |           |       | 0000  |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-25: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJXX(GP/MC)102 DEVICES

|              |             |        |        |        |        |           |           |       |       |       |       | •····•, |           |           |            |       |       |               |

|--------------|-------------|--------|--------|--------|--------|-----------|-----------|-------|-------|-------|-------|---------|-----------|-----------|------------|-------|-------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11    | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5   | Bit 4     | Bit 3     | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

| RPOR0        | 06C0        | -      | —      | —      |        | RP1R<4:0> |           |       |       | -     | —     | —       | RP0R<4:0> |           |            |       |       | 0000          |

| RPOR1        | 06C2        | _      | _      | _      |        | RP3R<4:0> |           |       |       | _     | _     | —       | RP2R<4:0> |           |            |       |       | 0000          |

| RPOR2        | 06C4        | _      | _      | _      |        | RP5R<4:0> |           |       |       | _     | _     | —       |           |           | RP4R<4:0>  |       |       | 0000          |

| RPOR3        | 06C6        | _      | _      | _      |        | RP7R<4:0> |           |       | _     | _     | —     |         |           | RP6R<4:0> |            |       | 0000  |               |

| RPOR4        | 06C8        | _      | _      | _      |        |           | RP9R<4:0> | >     |       | _     | _     | —       |           |           | RP8R<4:0>  |       |       | 0000          |

| RPOR5        | 06CA        | _      | _      | _      |        |           | RP11R<4:0 | >     |       | _     | _     | —       |           | I         | RP10R<4:0> |       |       | 0000          |

| RPOR6        | 06CC        | _      | _      | _      |        |           | RP13R<4:0 | >     |       | _     | _     | —       |           | I         | RP12R<4:0> |       |       | 0000          |

| RPOR7        | 06CE        | _      | —      | _      |        |           | RP15R<4:0 | >     |       | _     | —     | —       |           |           | RP14R<4:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2014 Microchip Technology Inc.

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| U-0             | U-0                                  | R/W-0            | U-0           | U-0                | U-0              | U-0             | U-0                    |  |

|-----------------|--------------------------------------|------------------|---------------|--------------------|------------------|-----------------|------------------------|--|

| —               |                                      | CTMUIE           | —             | —                  | —                | —               | —                      |  |

| bit 15          |                                      |                  |               |                    |                  |                 | bit 8                  |  |

|                 |                                      |                  |               |                    |                  |                 |                        |  |

| U-0             | U-0                                  | U-0              | U-0           | U-0                | U-0              | R/W-0           | R/W-0                  |  |

|                 |                                      |                  | —             | —                  | —                | U1EIE           | FLTB1IE <sup>(1)</sup> |  |

| bit 7           |                                      |                  |               |                    |                  |                 | bit 0                  |  |

|                 |                                      |                  |               |                    |                  |                 |                        |  |

| Legend:         |                                      |                  |               |                    |                  |                 |                        |  |

| R = Readable b  | bit                                  | W = Writable     | bit           | U = Unimpler       | mented bit, read | l as '0'        |                        |  |

| -n = Value at P | OR                                   | '1' = Bit is set |               | '0' = Bit is cle   | eared            | x = Bit is unki | nown                   |  |

|                 |                                      |                  |               |                    |                  |                 |                        |  |

| bit 15-14       | Unimplemen                           | ted: Read as '   | 0'            |                    |                  |                 |                        |  |

| bit 13          | CTMUIE: CTM                          | MU Interrupt Er  | nable bit     |                    |                  |                 |                        |  |

|                 |                                      | request is enab  |               |                    |                  |                 |                        |  |

|                 | -                                    | request is not e |               |                    |                  |                 |                        |  |

| bit 12-2        | Unimplemen                           | ted: Read as '   | 0'            |                    |                  |                 |                        |  |

| bit 1           | <b>U1EIE:</b> UART                   | 1 Error Interru  | pt Enable bit |                    |                  |                 |                        |  |

|                 |                                      | request is enab  |               |                    |                  |                 |                        |  |

|                 | 0 = Interrupt request is not enabled |                  |               |                    |                  |                 |                        |  |

| bit 0           |                                      | /M1 Fault B Inte | -             | bit <sup>(1)</sup> |                  |                 |                        |  |

|                 | •                                    | request has occ  |               |                    |                  |                 |                        |  |

|                 | 0 = Interrupt r                      | request has not  | occurred      |                    |                  |                 |                        |  |

| Note 1: This    | bit is available                     | e in dsPIC(16/3  | 2)MC102/104   | devices only.      |                  |                 |                        |  |

#### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0                                                     | R/W-1                                         | R/W-0                                                                                 | R/W-0                 | U-0             | R/W-1             | R/W-0           | R/W-0    |  |  |  |  |  |

|---------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|-----------------|-------------------|-----------------|----------|--|--|--|--|--|

| —                                                       | CNIP2                                         | CNIP1                                                                                 | CNIP0                 | —               | CMIP2             | CMIP1           | CMIP0    |  |  |  |  |  |

| bit 15                                                  |                                               |                                                                                       |                       |                 |                   |                 | bit      |  |  |  |  |  |

|                                                         | <b>D A A A</b>                                | <b>D</b> 444 o                                                                        | <b>D M</b> ( <b>a</b> |                 | <b>D</b> 444 4    | <b>D</b> 444 o  |          |  |  |  |  |  |

| U-0                                                     | R/W-1                                         | R/W-0                                                                                 | R/W-0                 | U-0             | R/W-1             | R/W-0           | R/W-0    |  |  |  |  |  |

|                                                         | MI2C1IP2                                      | MI2C1IP1                                                                              | MI2C1IP0              | —               | SI2C1IP2          | SI2C1IP1        | SI2C1IP0 |  |  |  |  |  |

| bit 7                                                   |                                               |                                                                                       |                       |                 |                   |                 | bit      |  |  |  |  |  |

| Legend:                                                 |                                               |                                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

| R = Readab                                              | le bit                                        | W = Writable                                                                          | bit                   | U = Unimple     | emented bit, read | d as '0'        |          |  |  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared |                                               |                                                                                       |                       |                 |                   | x = Bit is unkr | nown     |  |  |  |  |  |

|                                                         |                                               |                                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

| bit 15                                                  | -                                             | ted: Read as '                                                                        |                       |                 |                   |                 |          |  |  |  |  |  |

| bit 14-12                                               |                                               | Change Notifica                                                                       |                       | -               |                   |                 |          |  |  |  |  |  |

|                                                         | 111 = Interru                                 | pt is Priority 7 (                                                                    | highest priorit       | y interrupt)    |                   |                 |          |  |  |  |  |  |

|                                                         | •                                             |                                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         | •                                             |                                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         | 001 = Interru                                 | pt is Priority 1                                                                      |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         | 000 = Interru                                 | pt source is dis                                                                      | abled                 |                 |                   |                 |          |  |  |  |  |  |

| bit 11                                                  | Unimplemented: Read as '0'                    |                                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

| bit 10-8                                                | CMIP<2:0>: Comparator Interrupt Priority bits |                                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         | 111 = Interru                                 | pt is Priority 7 (                                                                    | highest priorit       | y interrupt)    |                   |                 |          |  |  |  |  |  |

|                                                         | •                                             |                                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         | •                                             |                                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         | 001 = Interru                                 | pt is Priority 1                                                                      |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         |                                               | pt source is dis                                                                      | abled                 |                 |                   |                 |          |  |  |  |  |  |

| bit 7                                                   |                                               | Ited: Read as '                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

| bit 6-4                                                 | -                                             | >: I2C1 Master                                                                        |                       | upt Priority bi | ts                |                 |          |  |  |  |  |  |

|                                                         |                                               | pt is Priority 7 (                                                                    |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         | •                                             | . ,                                                                                   |                       | , i ,           |                   |                 |          |  |  |  |  |  |

|                                                         | •                                             |                                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         | •<br>001 = Interru                            | nt in Priority 1                                                                      |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         |                                               | pt is Fridity 1<br>pt source is dis                                                   | abled                 |                 |                   |                 |          |  |  |  |  |  |

| bit 3                                                   |                                               | -                                                                                     |                       |                 |                   |                 |          |  |  |  |  |  |

| bit 2-0                                                 | -                                             | Unimplemented: Read as '0'<br>SI2C1IP<2:0>: I2C1 Slave Events Interrupt Priority bits |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         |                                               | pt is Priority 7 (                                                                    | -                     | -               |                   |                 |          |  |  |  |  |  |

|                                                         | •                                             |                                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         | •                                             |                                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         | •                                             |                                                                                       |                       |                 |                   |                 |          |  |  |  |  |  |

|                                                         | •<br>•<br>001 = Interru                       | pt is Prioritv 1                                                                      |                       |                 |                   |                 |          |  |  |  |  |  |

## REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| U-0           | U-0           | U-0              | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|---------------|---------------|------------------|----------------|------------------|-----------------|-----------------|-------|

| —             | —             | —                |                |                  | RP1R<4:0>       |                 |       |

| bit 15        |               |                  |                |                  |                 |                 | bit 8 |

|               |               |                  |                |                  |                 |                 |       |

| U-0           | U-0           | U-0              | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| _             | —             | —                |                |                  | RP0R<4:0>       |                 |       |

| bit 7         |               |                  |                |                  |                 |                 | bit 0 |

|               |               |                  |                |                  |                 |                 |       |

| Legend:       |               |                  |                |                  |                 |                 |       |

| R = Readable  | e bit         | W = Writable     | bit            | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at | POR           | '1' = Bit is set |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|               |               |                  |                |                  |                 |                 |       |

| bit 15-13     | Unimplemen    | ted: Read as '   | 0'             |                  |                 |                 |       |

| bit 12-8      | RP1R<4:0>:    | Peripheral Outp  | out Function   | is Assigned to F | RP1 Output Pir  | n bits          |       |

|               | (see Table 10 | -2 for periphera | al function nu | mbers)           |                 |                 |       |

|               |               |                  |                |                  |                 |                 |       |

#### REGISTER 10-11: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| bit 4-0 | <b>RP0R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP0 Output Pin bits |

|---------|---------------------------------------------------------------------------------------|

|         | (see Table 10-2 for peripheral function numbers)                                      |

Unimplemented: Read as '0'

#### REGISTER 10-12: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|--------------------------|-------|-------|

| —      | —   | —   |       |       | RP3R<4:0> <sup>(1)</sup> | 1     |       |

| bit 15 |     |     |       |       |                          |       | bit 8 |

|        |     |     |       |       |                          |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|        |     |     |       |       | RP2R<4:0> <sup>(1)</sup> |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 12-8  | <b>RP3R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP3 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                                     |

| bit 7-5   | Unimplemented: Read as '0'                                                                           |

| bit 4-0   | <b>RP2R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP2 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                                     |

**Note 1:** These bits are not available in dsPIC33FJXX(GP/MC)101 devices.

bit 7-5

bit 7

bit 0

# 12.3 Timer2/3 and Timer4/5 Control Registers

| -             |                                                    |                              |                |                  |                 |                 |       |  |  |  |

|---------------|----------------------------------------------------|------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|

| R/W-0         | U-0                                                | R/W-0                        | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |

| TON           |                                                    | TSIDL                        | _              |                  | —               |                 | —     |  |  |  |

| bit 15        |                                                    |                              |                |                  |                 |                 | bit 8 |  |  |  |

|               |                                                    |                              |                |                  |                 |                 |       |  |  |  |

| U-0           | R/W-0                                              | R/W-0                        | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |

| _             | TGATE                                              | TCKPS1                       | TCKPS0         | T32              | —               | TCS             | —     |  |  |  |

| bit 7         |                                                    |                              |                |                  |                 |                 | bit C |  |  |  |

|               |                                                    |                              |                |                  |                 |                 |       |  |  |  |

| Legend:       |                                                    |                              |                |                  |                 |                 |       |  |  |  |

| R = Readabl   | e bit                                              | W = Writable I               | oit            | U = Unimpler     | mented bit, rea | ad as '0'       |       |  |  |  |

| -n = Value at | POR                                                | '1' = Bit is set             |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |

|               |                                                    |                              |                |                  |                 |                 |       |  |  |  |

| bit 15        | TON: Timer2                                        | On bit                       |                |                  |                 |                 |       |  |  |  |

|               | When T32 = 2                                       |                              |                |                  |                 |                 |       |  |  |  |

|               | 1 = Starts 32-                                     |                              |                |                  |                 |                 |       |  |  |  |

|               | 0 = Stops 32-                                      |                              |                |                  |                 |                 |       |  |  |  |

|               | $\frac{\text{When T32} = 0}{1 = \text{Starts 16}}$ |                              |                |                  |                 |                 |       |  |  |  |

|               | 0 = Stops 16-                                      |                              |                |                  |                 |                 |       |  |  |  |

| bit 14        | Unimplemen                                         | ted: Read as 'd              | )'             |                  |                 |                 |       |  |  |  |

| bit 13        | TSIDL: Timer2 Stop in Idle Mode bit                |                              |                |                  |                 |                 |       |  |  |  |

|               |                                                    | ues module ope               |                |                  | lle mode        |                 |       |  |  |  |

|               |                                                    | s module opera               |                | de               |                 |                 |       |  |  |  |

| bit 12-7      | Unimplemen                                         | ted: Read as '0              | )'             |                  |                 |                 |       |  |  |  |

| bit 6         | TGATE: Timer2 Gated Time Accumulation Enable bit   |                              |                |                  |                 |                 |       |  |  |  |

|               | When TCS = 1:<br>This bit is ignored.              |                              |                |                  |                 |                 |       |  |  |  |

|               | When TCS =                                         |                              |                |                  |                 |                 |       |  |  |  |

|               |                                                    | <u>o.</u><br>e accumulatior  | is enabled     |                  |                 |                 |       |  |  |  |

|               |                                                    | e accumulation               |                |                  |                 |                 |       |  |  |  |

| bit 5-4       | TCKPS<1:0>                                         | : Timer2 Input               | Clock Prescale | e Select bits    |                 |                 |       |  |  |  |

|               | 11 <b>= 1:256</b>                                  |                              |                |                  |                 |                 |       |  |  |  |

|               | 10 = 1:64                                          |                              |                |                  |                 |                 |       |  |  |  |

|               | 01 = 1:8<br>00 = 1:1                               |                              |                |                  |                 |                 |       |  |  |  |

| bit 3         |                                                    | imer Mode Sele               | ct bit         |                  |                 |                 |       |  |  |  |

| Sit 0         |                                                    | nd Timer3 form               |                | timer            |                 |                 |       |  |  |  |

|               |                                                    | nd Timer3 act a              |                |                  |                 |                 |       |  |  |  |

| bit 2         | Unimplemen                                         | ted: Read as '               | )'             |                  |                 |                 |       |  |  |  |

| bit 1         | TCS: Timer2                                        | Clock Source S               | elect bit      |                  |                 |                 |       |  |  |  |

|               |                                                    | clock from pin, <sup>-</sup> | Γ2CK (on the r | ising edge)      |                 |                 |       |  |  |  |

|               | 0 = Internal cl                                    |                              |                |                  |                 |                 |       |  |  |  |

| bit 0         | Unimplemen                                         | ted: Read as '0              | )'             |                  |                 |                 |       |  |  |  |

#### REGISTER 12-1: T2CON: TIMER2 CONTROL REGISTER

NOTES:

## 15.0 MOTOR CONTROL PWM MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Motor Control PWM" (DS70187) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ16MC10X devices have a 6-channel Pulse-Width Modulation (PWM) module.

The PWM module has the following features:

- Up to 16-bit resolution

- On-the-fly PWM frequency changes

- Edge-Aligned and Center-Aligned Output modes

- Single Pulse Generation mode

- Interrupt support for asymmetrical updates in Center-Aligned mode

- Output override control for Electrically Commutative Motor (ECM) operation or BLDC

- Special event comparator for scheduling other peripheral events

- Fault pins to optionally drive each of the PWM output pins to a defined state

- Duty cycle updates configurable to be immediate or synchronized to the PWM time base

#### 15.1 PWM1: 6-Channel PWM Module

This module simplifies the task of generating multiple synchronized PWM outputs. The following power and motion control applications are supported by the PWM module:

- 3-Phase AC Induction Motor

- Switched Reluctance (SR) Motor

- Brushless DC (BLDC) Motor

- Uninterruptible Power Supply (UPS)

This module contains three duty cycle generators, numbered 1 through 3. The module has six PWM output pins, numbered PWM1H1/PWM1L1 through PWM1H3/PWM1L3. The six I/O pins are grouped into high/low numbered pairs, denoted by the suffix H or L, respectively. For complementary loads, the low PWM pins are always the complement of the corresponding high I/O pin.

#### 15.2 PWM Faults

The Motor Control PWM module incorporates up to two Fault inputs, FLTA1 and FLTB1. These Fault inputs are implemented with Class B safety features. These features ensure that the PWM outputs enter a safe state when either of the Fault inputs is asserted.

The FLTA1 and FLTB1 pins, when enabled and having ownership of a pin, also enable a soft internal pull-down resistor. The soft pull-down provides a safety feature by automatically asserting the Fault should a break occur in the Fault signal connection.

The implementation of internal pull-down resistors is dependent on the device variant. Table 15-1 describes which devices and pins implement the internal pull-down resistors.

#### TABLE 15-1: INTERNAL PULL-DOWN RESISTORS ON PWM FAULT PINS

| Device           | Fault Pin | Internal<br>Pull-Down<br>Implemented? |

|------------------|-----------|---------------------------------------|

| dsPIC33FJXXMC101 | FLTA1     | No                                    |

| dsPIC33FJXXMC102 | FLTA1     | Yes                                   |

|                  | FLTB1     | Yes                                   |

| dsPIC33FJ32MC104 | FLTA1     | Yes                                   |

|                  | FLTB1     | Yes                                   |

On devices without internal pull-downs on the Fault pin, it is recommended to connect an external pull-down resistor for Class B safety features.

#### 15.2.1 PWM FAULTS AT RESET

During any Reset event, the PWM module maintains ownership of both PWM Fault pins. At Reset, both Faults are enabled in latched mode to guarantee the fail-safe power-up of the application. The application software must clear both of the PWM Faults before enabling the Motor Control PWM module.

The Fault condition must be cleared by the external circuitry driving the Fault input pin high and clearing the Fault interrupt flag. After the Fault pin condition has been cleared, the PWM module restores the PWM output signals on the next PWM period or half-period boundary. Refer to **"Motor Control PWM"** (DS70187) in the "*dsPIC33/PIC24 Family Reference Manual*" for more information on the PWM Faults.

Note: The number of PWM Faults mapped to the device pins depend on the specific variant. Regardless of the variant, both Faults will be enabled during any Reset <u>event.</u> The <u>application</u> must clear both FLTA1 and FLTB1 before enabling the Motor Control PWM module. Refer to the specific device pin diagrams to see which Fault pins are mapped to the device pins.

### 15.3 Write-Protected Registers

On dsPIC33FJ(16/32)MC10X devices, write protection is implemented for the PWMxCON1, PxFLTACON and PxFLTBCON registers. The write protection feature prevents any inadvertent writes to these registers. The write protection feature can be controlled by the PWMLOCK Configuration bit in the FOSCSEL Configuration register. The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring PWMLOCK (FOSCSEL<6>) = 0.

The user application can gain access to these locked registers either by configuring the PWMLOCK bit (FOSCSEL<6>) = 0 or by performing the unlock sequence. To perform the unlock sequence, the user application must write two consecutive values (0xABCD and 0x4321) to the PWMxKEY register to perform the unlock operation. The write access to the PWMxCON1, PxFLTACON or PxFLTBCON registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access.

To write to all registers, the PWMxCON1, PxFLTACON and PxFLTBCON registers require three unlock operations.

The correct unlocking sequence is described in Example 15-1 and Example 15-2.

# 18.3 UART Control Registers

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0                                                                                                               | R/W-0                                  | R/W-0               | R/W-0            | U-0              | R/W-0               | R/W-0           |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------|------------------|------------------|---------------------|-----------------|--|

| UARTEN <sup>(1)</sup> | _                                                                                                                 | USIDL                                  | IREN <sup>(2)</sup> | RTSMD            |                  | UEN1                | UEN0            |  |

| bit 15                |                                                                                                                   |                                        |                     |                  |                  |                     | bit 8           |  |

|                       |                                                                                                                   |                                        |                     |                  |                  |                     |                 |  |

| R/W-0, HC             | R/W-0                                                                                                             | R/W-0, HC                              | R/W-0               | R/W-0            | R/W-0            | R/W-0               | R/W-0           |  |

| WAKE                  | LPBACK                                                                                                            | ABAUD                                  | URXINV              | BRGH             | PDSEL1           | PDSEL0              | STSEL           |  |

| bit 7                 |                                                                                                                   |                                        |                     |                  |                  |                     | bit             |  |

|                       |                                                                                                                   |                                        |                     | . :4             |                  |                     |                 |  |

| Legend:               | L.:4                                                                                                              |                                        | re Clearable b      |                  |                  |                     |                 |  |

| R = Readable          |                                                                                                                   | W = Writable                           |                     | •                | mented bit, read |                     |                 |  |

| -n = Value at F       | VOR                                                                                                               | '1' = Bit is set                       |                     | '0' = Bit is cle | ared             | x = Bit is unkn     | own             |  |

| bit 15                | UARTEN: UA                                                                                                        | RTx Enable bi                          | <sub>t</sub> (1)    |                  |                  |                     |                 |  |

|                       |                                                                                                                   |                                        |                     | e controlled by  | UARTx as defi    | ned by the UEN      | l<1:0> bits     |  |

|                       | 0 = UARTx is                                                                                                      |                                        |                     |                  |                  | JARTx power co      |                 |  |

|                       | minimal                                                                                                           |                                        |                     |                  |                  |                     |                 |  |

| bit 14                | •                                                                                                                 | ted: Read as '                         |                     |                  |                  |                     |                 |  |

| bit 13                |                                                                                                                   | Tx Stop in Idle                        |                     |                  |                  |                     |                 |  |

|                       |                                                                                                                   | nues module op<br>s module oper        |                     |                  | Idle mode        |                     |                 |  |

| bit 12                |                                                                                                                   | •                                      |                     |                  |                  |                     |                 |  |

| DIT 12                | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup><br>1 = IrDA encoder and decoder are enabled |                                        |                     |                  |                  |                     |                 |  |

|                       |                                                                                                                   | oder and deco                          |                     |                  |                  |                     |                 |  |

| bit 11                | RTSMD: UAF                                                                                                        | RTx Mode Sele                          | ction for UxR1      | S Pin bit        |                  |                     |                 |  |

|                       |                                                                                                                   | oin is in Simple:<br>An is in Flow C   |                     |                  |                  |                     |                 |  |

| bit 10                | Unimplemen                                                                                                        | ted: Read as '                         | 0'                  |                  |                  |                     |                 |  |

| bit 9-8               | UEN<1:0>: U                                                                                                       | IARTx Pin Ena                          | ble bits            |                  |                  |                     |                 |  |

|                       |                                                                                                                   | JxRX and BCL<br>JxRX, UxCTS a          |                     |                  |                  | controlled by po    | ort latches     |  |

|                       |                                                                                                                   |                                        |                     |                  |                  | s controlled by p   | oort latches    |  |

|                       | 00 = UxTX a                                                                                                       | nd UxRX pins                           |                     |                  |                  | /BCLK pins are      |                 |  |

|                       | port latc                                                                                                         |                                        |                     |                  |                  |                     |                 |  |

| bit 7                 |                                                                                                                   | -up on Start bi                        |                     |                  |                  |                     |                 |  |

|                       |                                                                                                                   | vill continue to a<br>are on following |                     | RX pin; interru  | ipt is generated | on falling edge     | , bit is cleare |  |

|                       |                                                                                                                   | -up is enabled                         | g namy edge         |                  |                  |                     |                 |  |

| bit 6                 |                                                                                                                   | ARTx Loopback                          | Mode Select         | bit              |                  |                     |                 |  |

|                       |                                                                                                                   | Loopback mod                           |                     |                  |                  |                     |                 |  |

|                       | 0 = Loopbac                                                                                                       | k mode is disa                         | bled                |                  |                  |                     |                 |  |

| bit 5                 |                                                                                                                   | o-Baud Enable                          |                     |                  |                  |                     |                 |  |

|                       |                                                                                                                   |                                        |                     |                  |                  | eception of a Sy    | nc field (55h   |  |

|                       |                                                                                                                   | her data; clear<br>e measuremen        |                     |                  | tion             |                     |                 |  |

|                       |                                                                                                                   |                                        | LIS UISADIEU U      |                  |                  |                     |                 |  |

|                       |                                                                                                                   |                                        |                     |                  | Reference Manu   | al" for information | on on           |  |

|                       | Ibling the UART                                                                                                   |                                        |                     | -                |                  |                     |                 |  |

|                       |                                                                                                                   |                                        |                     |                  |                  |                     |                 |  |

2: This feature is available for 16x BRG mode (BRGH = 0) only.

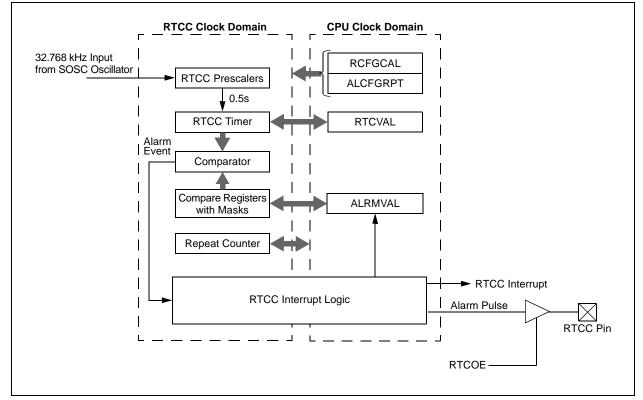

# 21.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 device families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Real-Time Clock and Calendar (RTCC)" (DS70310) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter discusses the Real-Time Clock and Calendar (RTCC) module, available on dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices, and its operation. Some of the key features of the RTCC module are:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- Calendar: weekday, date, month and year

- Alarm configurable

- Year range: 2000 to 2099

- · Leap year correction

- BCD format for compact firmware

- · Optimized for low-power operation

- · User calibration with auto-adjust

- Calibration range: ±2.64 seconds error per month

- Requirements: external 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

The RTCC module is intended for applications where accurate time must be maintained for extended periods of time with minimum to no intervention from the CPU. The RTCC module is optimized for low-power usage to provide extended battery lifetime while keeping track of time.

The RTCC module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099.

The hours are available in 24-hour (military time) format. The clock provides a granularity of one second with half-second visibility to the user.

### FIGURE 21-1: RTCC BLOCK DIAGRAM

| Bit Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCP         | General Segment Code-Protect bit                                                                                                                                                                                                                                                                                                                                                                                    |

|             | <ul><li>1 = User program memory is not code-protected</li><li>0 = Code protection is enabled for the entire program memory space</li></ul>                                                                                                                                                                                                                                                                          |

| GWRP        | General Segment Write-Protect bit                                                                                                                                                                                                                                                                                                                                                                                   |

|             | <ul><li>1 = User program memory is not write-protected</li><li>0 = User program memory is write-protected</li></ul>                                                                                                                                                                                                                                                                                                 |

| IESO        | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Starts up device with FRC, then automatically switches to the user-selected oscillator source when ready</li> <li>0 = Starts up device with user-selected oscillator source</li> </ul>                                                                                                                                                               |

| PWMLOCK     | PWM Lock Enable bit                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | <ul><li>1 = Certain PWM registers may only be written after a key sequence</li><li>0 = PWM registers may be written without a key sequence</li></ul>                                                                                                                                                                                                                                                                |

| WDTWIN<1:0> | Watchdog Timer Window Select bits<br>11 = WDT window is 24% of WDT period<br>10 = WDT window is 37.5% of WDT period<br>01 = WDT window is 50% of WDT period<br>00 = WDT window is 75% of WDT period                                                                                                                                                                                                                 |

| FNOSC<2:0>  | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Reserved; do not use<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Secondary Oscillator (SOSC)<br>011 = Primary Oscillator with PLL module (MS + PLL, EC + PLL)<br>010 = Primary Oscillator (MS, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N and PLL module (FRCDIVN + PLL)<br>000 = Fast RC Oscillator (FRC) |

| FCKSM<1:0>  | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                   |

| IOL1WAY     | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                |

| OSCIOFNC    | OSC2 Pin Function bit (except in MS and HS modes)<br>1 = OSC2 is a clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                    |

| POSCMD<1:0> | Primary Oscillator Mode Select bits         11 = Primary Oscillator is disabled         10 = HS Crystal Oscillator mode (10 MHz-32 MHz)         01 = MS Crystal Oscillator mode (3 MHz-10 MHz)         00 = EC (External Clock) mode (DC-32 MHz)                                                                                                                                                                    |

| FWDTEN      | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled; clearing the SWDTEN bit in the RCON register will have no effect)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                          |

| WINDIS      | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                      |

#### TABLE 23-4: dsPIC33F CONFIGURATION BITS DESCRIPTION

| DC CHARACTERISTICS |                        |               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                               |                  |                             |

|--------------------|------------------------|---------------|-------------------------------------------------------|-------------------------------|------------------|-----------------------------|

| Parameter<br>No.   | Typical <sup>(1)</sup> | Мах           | Units                                                 | Conditions                    |                  |                             |

| Idle Current (II   | DLE): Core Of          | f, Clock On I | Base Current                                          | <sup>(2)</sup> – dsPIC33FJ32( | GP/MC)10X Device | S                           |

| DC40d              | 0.4                    | 1.0           | mA                                                    | -40°C                         |                  |                             |

| DC40a              | 0.4                    | 1.0           | mA                                                    | +25°C                         | - 3.3V           | LPRC                        |

| DC40b              | 0.4                    | 1.0           | mA                                                    | +85°C                         | 3.3 V            | (32.768 kHz) <sup>(3)</sup> |

| DC40c              | 0.5                    | 1.0           | mA                                                    | +125°C                        |                  |                             |

| DC41d              | 0.5                    | 1.1           | mA                                                    | -40°C                         |                  | 1 MIPS <sup>(3)</sup>       |

| DC41a              | 0.5                    | 1.1           | mA                                                    | +25°C                         | - 3.3V           |                             |

| DC41b              | 0.5                    | 1.1           | mA                                                    | +85°C                         |                  |                             |

| DC41c              | 0.8                    | 1.1           | mA                                                    | +125°C                        |                  |                             |

| DC42d              | 0.9                    | 1.6           | mA                                                    | -40°C                         |                  |                             |

| DC42a              | 0.9                    | 1.6           | mA                                                    | +25°C                         | - 3.3V           | 4 MIPS <sup>(3)</sup>       |

| DC42b              | 1.0                    | 1.6           | mA                                                    | +85°C                         | 3.3V             | 4 10115357                  |

| DC42c              | 1.2                    | 1.6           | mA                                                    | +125°C                        |                  |                             |

| DC43a              | 1.6                    | 2.6           | mA                                                    | +25°C                         |                  |                             |

| DC43d              | 1.6                    | 2.6           | mA                                                    | -40°C                         | - 3.3V           | 10 MIPS <sup>(3)</sup>      |

| DC43b              | 1.7                    | 2.6           | mA                                                    | +85°C                         | 3.3V             | 10 1011-517                 |

| DC43c              | 2.0                    | 2.6           | mA                                                    | +125°C                        |                  |                             |

| DC44d              | 2.4                    | 3.8           | mA                                                    | -40°C                         |                  |                             |

| DC44a              | 2.4                    | 3.8           | mA                                                    | +25°C                         | - 3.3V           | 16 MIPS <sup>(3)</sup>      |

| DC44b              | 2.6                    | 3.8           | mA                                                    | +85°C                         | 3.37             |                             |

| DC44c              | 2.9                    | 3.8           | mA                                                    | +125°C                        |                  |                             |

#### TABLE 26-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE) (CONTINUED)

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: Base Idle current is measured as follows:

- CPU core is off, oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- External Secondary Oscillator (SOSC) is disabled (i.e., SOSCO and SOSCI pins are configured as digital I/O inputs)

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (PMDx bits are all zeroed)

- **3:** These parameters are characterized, but not tested in manufacturing.

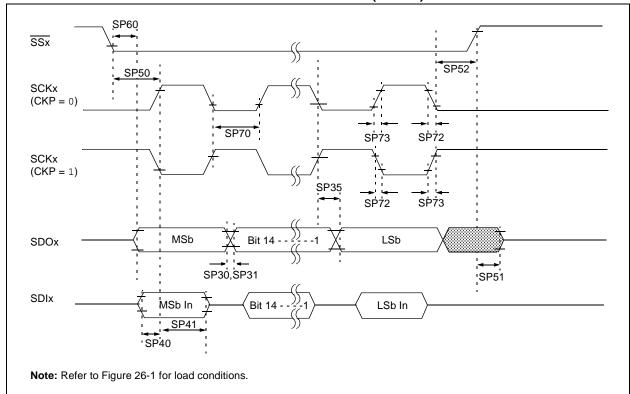

#### FIGURE 26-15: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ16(GP/MC)10X

# TABLE 26-34:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ16(GP/MC)10X

| AC CHARACTERISTICS |                       |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.4V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |

|--------------------|-----------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                                                                                                                                                                                                                                                     | Тур <sup>(2)</sup> | Max | Units | Conditions                           |