Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gp102-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

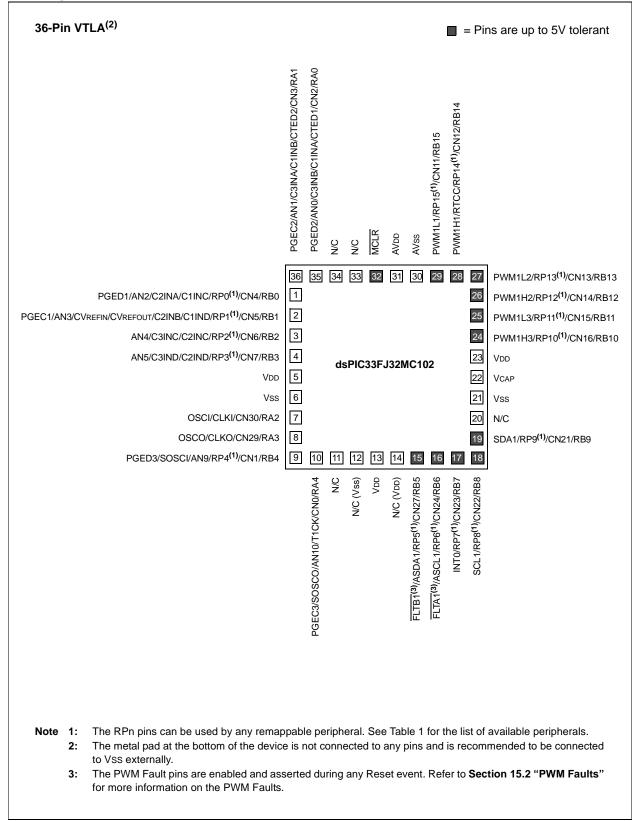

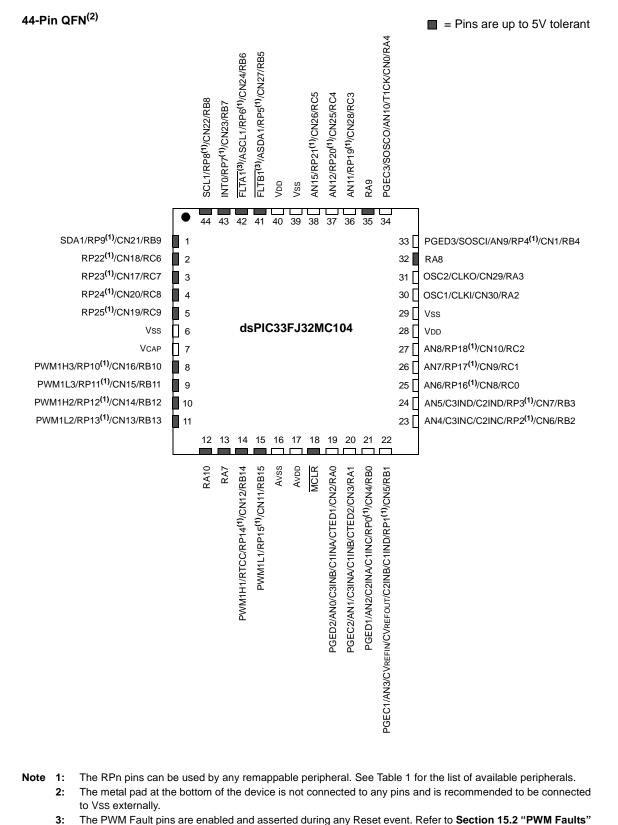

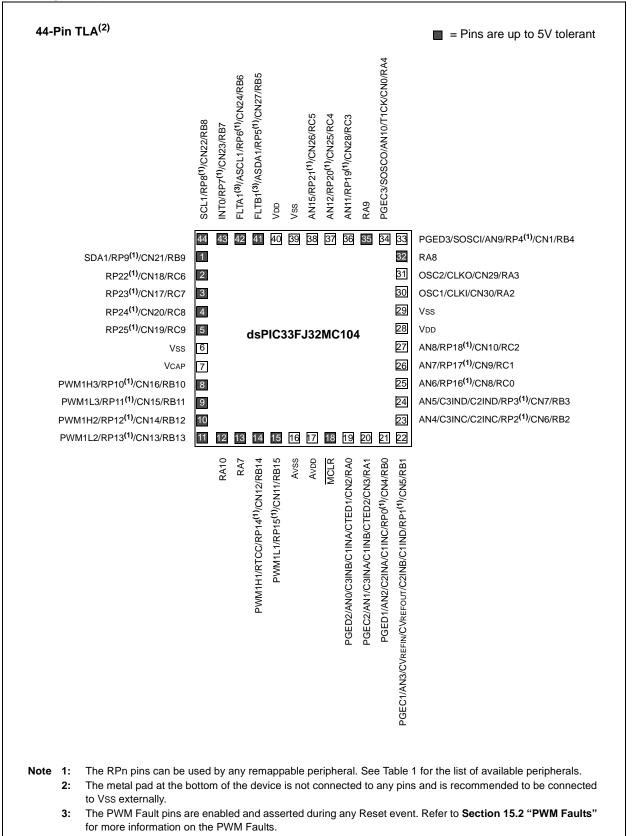

#### **Pin Diagrams (Continued)**

### Pin Diagrams (Continued)

3: The PWM Fault pins are enabled and asserted during any Reset event. Refer to Section 15.2 "PWM Faults" for more information on the PWM Faults.

#### **Pin Diagrams (Continued)**

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts are disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                                                                       |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | 1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                  |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of a magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                                                       |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                     |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                                    |

| Note 1: | This bit can be read or cleared (not set).                                                                                                                                                                                                                                                                                                                                                                                                 |

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

#### 3.6.1 MULTIPLIER

The 17-bit x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17-bit x 17-bit multiplier/scaler is a 33-bit value that is sign-extended to 40 bits. Integer data is inherently represented as a signed 2's complement value, where the Most Significant bit (MSb) is defined as a sign bit. The range of an N-bit 2's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ .

- For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF) including 0.

- For a 32-bit integer, the data range is -2,147,483,648 (0x8000 0000) to 2,147,483,647 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a 2's complement fraction, where the MSb is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit 2's complement fraction with this implied radix point is -1.0 to  $(1 - 2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including 0 and has a precision of 3.01518x10<sup>-5</sup>. In Fractional mode, the 16 x 16 multiply operation generates a 1.31 product that has a precision of 4.65661 x 10<sup>-10</sup>.

The same multiplier is used to support the MCU multiply instructions, which include integer 16-bit signed, unsigned and mixed sign multiply operations.

The MUL instruction can be directed to use byte or word-sized operands. Byte operands will direct a 16-bit result and word operands will direct a 32-bit result to the specified register(s) in the W array.

# 3.6.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/ subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its pre-accumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled using the barrel shifter prior to accumulation.

# 3.6.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side and either true or complement data into the other input.

- In the case of addition, the Carry/Borrow input is active-high and the other input is true data (not complemented).

- In the case of subtraction, the Carry/Borrow input is active-low and the other input is complemented.

The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS Register:

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block that controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described previously, and the SAT<A:B> (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value, to saturate.

Six STATUS Register bits support saturation and overflow:

- OA: ACCA overflowed into guard bits

- OB: ACCB overflowed into guard bits

- SA: ACCA saturated (bit 31 overflow and saturation)

ACCA overflowed into guard bits and saturated (bit 39 overflow and saturation)

- SB: ACCB saturated (bit 31 overflow and saturation)

- ACCB overflowed into guard bits and saturated (bit 39 overflow and saturation)

- OAB: Logical OR of OA and OB

- SAB: Logical OR of SA and SB

or

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when OA and OB are set and the corresponding Overflow Trap Flag Enable bits (OVATE, OVBTE) in the INTCON1 register are set (refer to **Section 7.0 "Interrupt Controller"**). This allows the user application to take immediate action; for example, to correct system gain.

#### TABLE 4-9: INPUT CAPTURE REGISTER MAP

| SFR<br>Addr | Bit 15                                       | Bit 14                             | Bit 13                                            | Bit 12                                                                                                                                                                                                       | Bit 11                                                                                                                                                                                                                                                                                                                                                                       | Bit 10                                                                                         | Bit 9                                                                                                         | Bit 8                                                                                                                       | Bit 7                                                                                                                                     | Bit 6                                                                                                                                                   | Bit 5                                                                                                                                                                 | Bit 4                                                                                                                                                                               | Bit 3                                                                                                                                                                                             | Bit 2                                                                                                                                                                                                           | Bit 1                                                                                                                                                                                                          | Bit 0                                                                                                                                                                                                                                       | All Resets                                                                                                                                                                                                                                                |

|-------------|----------------------------------------------|------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0140        |                                              |                                    |                                                   |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                |                                                                                                               | Input Cap                                                                                                                   | ture 1 Regis                                                                                                                              | ster                                                                                                                                                    |                                                                                                                                                                       |                                                                                                                                                                                     |                                                                                                                                                                                                   |                                                                                                                                                                                                                 |                                                                                                                                                                                                                |                                                                                                                                                                                                                                             | xxxx                                                                                                                                                                                                                                                      |

| 0142        | —                                            | —                                  | ICSIDL                                            | —                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                              | —                                                                                                             | —                                                                                                                           | ICTMR                                                                                                                                     | ICI1                                                                                                                                                    | ICI0                                                                                                                                                                  | ICOV                                                                                                                                                                                | ICBNE                                                                                                                                                                                             | ICM2                                                                                                                                                                                                            | ICM1                                                                                                                                                                                                           | ICM0                                                                                                                                                                                                                                        | 0000                                                                                                                                                                                                                                                      |

| 0144        |                                              |                                    |                                                   |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                |                                                                                                               | Input Cap                                                                                                                   | ture 2 Regis                                                                                                                              | ster                                                                                                                                                    |                                                                                                                                                                       |                                                                                                                                                                                     |                                                                                                                                                                                                   |                                                                                                                                                                                                                 |                                                                                                                                                                                                                |                                                                                                                                                                                                                                             | XXXX                                                                                                                                                                                                                                                      |

| 0146        | —                                            | —                                  | ICSIDL                                            | —                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                              | —                                                                                                             | —                                                                                                                           | ICTMR                                                                                                                                     | ICI1                                                                                                                                                    | ICI0                                                                                                                                                                  | ICOV                                                                                                                                                                                | ICBNE                                                                                                                                                                                             | ICM2                                                                                                                                                                                                            | ICM1                                                                                                                                                                                                           | ICM0                                                                                                                                                                                                                                        | 0000                                                                                                                                                                                                                                                      |

| 0148        |                                              |                                    |                                                   |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                |                                                                                                               | Input Cap                                                                                                                   | ture 3 Regis                                                                                                                              | ster                                                                                                                                                    |                                                                                                                                                                       |                                                                                                                                                                                     |                                                                                                                                                                                                   |                                                                                                                                                                                                                 |                                                                                                                                                                                                                |                                                                                                                                                                                                                                             | XXXX                                                                                                                                                                                                                                                      |

| 014A        |                                              | _                                  | ICSIDL                                            | _                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                              | _                                                                                                             |                                                                                                                             | ICTMR                                                                                                                                     | ICI1                                                                                                                                                    | ICI0                                                                                                                                                                  | ICOV                                                                                                                                                                                | ICBNE                                                                                                                                                                                             | ICM2                                                                                                                                                                                                            | ICM1                                                                                                                                                                                                           | ICM0                                                                                                                                                                                                                                        | 0000                                                                                                                                                                                                                                                      |

|             | Addr<br>0140<br>0142<br>0144<br>0146<br>0148 | Addr         Bit 15           0140 | Addr         Bit 15         Bit 14           0140 | Addr         Bit 15         Bit 14         Bit 13           0140          ICSIDL           0142          ICSIDL           0144          ICSIDL           0146          ICSIDL           0148          ICSIDL | Addr         Bit 15         Bit 14         Bit 13         Bit 12           0140         -         -         ICSIDL         -           0142         -         -         ICSIDL         -           0144         -         -         ICSIDL         -           0146         -         -         ICSIDL         -           0148         -         -         ICSIDL         - | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0           0140 |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-10: OUTPUT COMPARE REGISTER MAP

| SFR<br>Addr | Bit 15                                       | Bit 14                                                                                                                                           | Bit 13                                            | Bit 12                                                           | Bit 11                                                                                                                                                                                                                                                                                     | Bit 10                                                                                         | Bit 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Bit 8                                                                                                                       | Bit 7                                                                                                                                     | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit 5                                                                                                                     | Bit 4                                                                                                                               | Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bit 1                                                                                                                                                             | Bit 0                                                                                                                                                                                                                        | All<br>Resets                                                                            |

|-------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 0180        |                                              | Output Compare 1 Secondary Register                                                                                                              |                                                   |                                                                  |                                                                                                                                                                                                                                                                                            |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                             |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                           | xxxx                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                   |                                                                                                                                                                                                                              |                                                                                          |

| 0182        |                                              | Output Compare 1 Register x                                                                                                                      |                                                   |                                                                  |                                                                                                                                                                                                                                                                                            |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                             | XXXX                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                           |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                   |                                                                                                                                                                                                                              |                                                                                          |

| 0184        | —                                            | —                                                                                                                                                | OCSIDL                                            | —                                                                | —                                                                                                                                                                                                                                                                                          | —                                                                                              | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                                                                           | —                                                                                                                                         | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | —                                                                                                                         | OCFLT                                                                                                                               | OCTSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OCM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OCM1                                                                                                                                                              | OCM0                                                                                                                                                                                                                         | 0000                                                                                     |

| 0186        |                                              |                                                                                                                                                  |                                                   |                                                                  |                                                                                                                                                                                                                                                                                            |                                                                                                | Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | put Compar                                                                                                                  | e 2 Second                                                                                                                                | ary Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | r                                                                                                                         |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                   |                                                                                                                                                                                                                              | XXXX                                                                                     |

| 0188        |                                              | Output Compare 2 Register xxx                                                                                                                    |                                                   |                                                                  |                                                                                                                                                                                                                                                                                            |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XXXX                                                                                                                        |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                           |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                   |                                                                                                                                                                                                                              |                                                                                          |