Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K × 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gp102-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

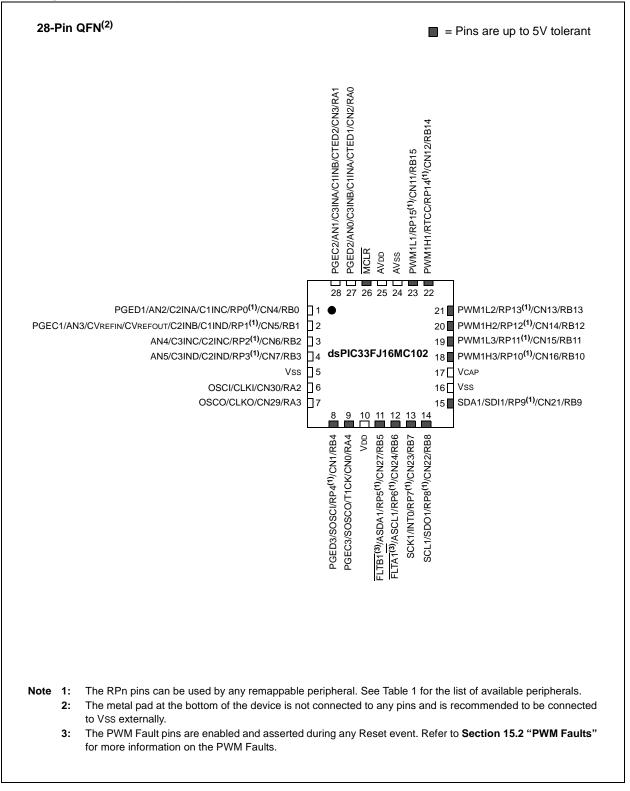

#### Pin Diagrams (Continued)

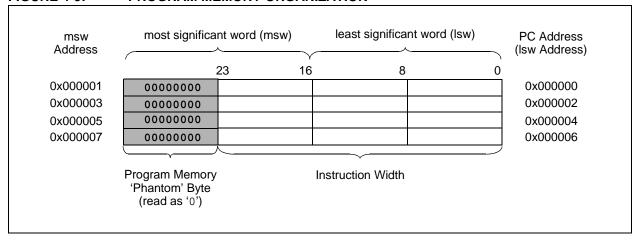

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-3).

Program memory addresses are always word-aligned on the lower word and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

### 4.1.2 INTERRUPT AND TRAP VECTORS

All of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices also have two Interrupt Vector Tables (IVTs), located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the Interrupt Vector Tables is provided in **Section 7.1 "Interrupt Vector Table"**.

#### FIGURE 4-3: PROGRAM MEMORY ORGANIZATION

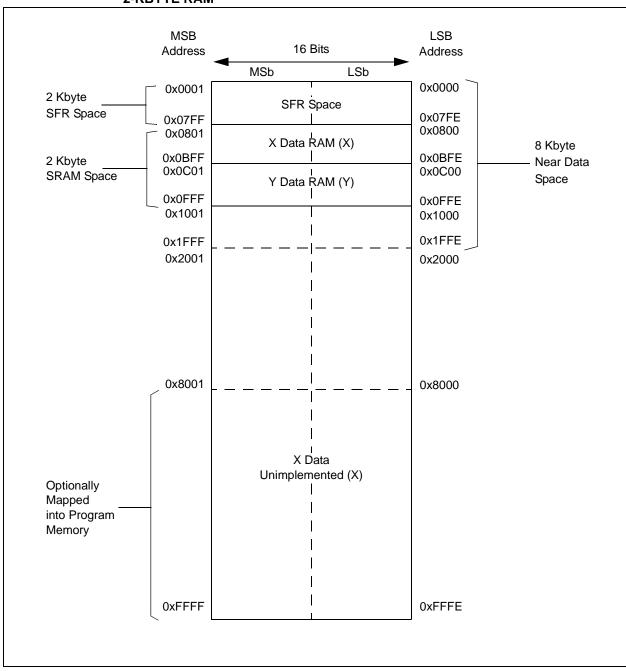

# FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJ32(GP/MC)101/102/104 DEVICES WITH 2-KBYTE RAM

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-40: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing      |

|-------|-----------------------------------------------|

|       | mode specified in the instruction can differ  |

|       | for the source and destination EA. How-       |

|       | ever, the 4-bit Wb (Register Offset) field is |

|       | shared by both source and destination         |

|       | (but typically only used by one).             |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

| Note: | Register                                 | Indirect | with | Register | Offset |  |  |  |

|-------|------------------------------------------|----------|------|----------|--------|--|--|--|

|       | Addressing mode is available only for W9 |          |      |          |        |  |  |  |

|       | (in X space) and W11 (in Y space).       |          |      |          |        |  |  |  |

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.3.5 OTHER INSTRUCTIONS

In addition to the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

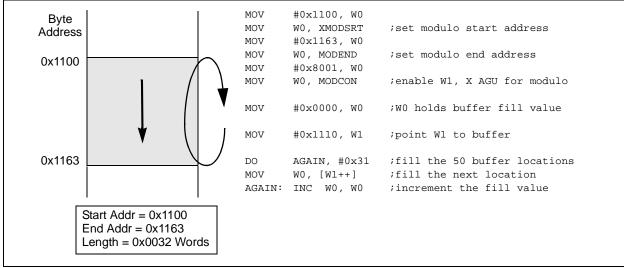

### 4.4 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the circular buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear). The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.4.2 W ADDRESS REGISTER SELECTION

- The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select which registers will operate with Modulo Addressing.

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled.

- If YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

# FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

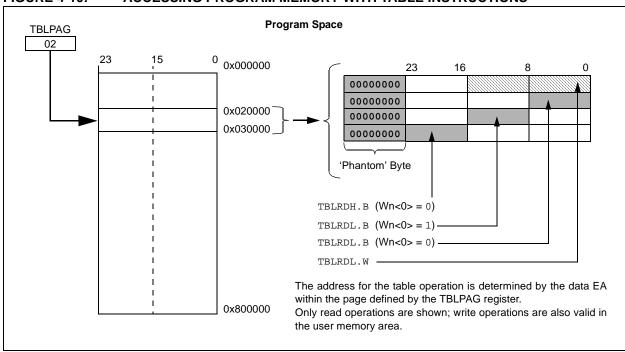

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

#### FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

|                                    |                                                                  |                                                                                      | 0               |                 |                  |          |        |  |  |  |  |

|------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------|-----------------|------------------|----------|--------|--|--|--|--|

| R/W-0                              | R-0                                                              | U-0                                                                                  | U-0             | U-0             | U-0              | U-0      | U-0    |  |  |  |  |

| ALTIVT                             | DISI                                                             | —                                                                                    | —               | —               | —                | —        | —      |  |  |  |  |

| bit 15                             |                                                                  |                                                                                      |                 |                 |                  |          | bit 8  |  |  |  |  |

|                                    |                                                                  |                                                                                      |                 |                 |                  |          |        |  |  |  |  |

| U-0                                | U-0                                                              | U-0                                                                                  | U-0             | U-0             | R/W-0            | R/W-0    | R/W-0  |  |  |  |  |

|                                    |                                                                  | —                                                                                    | —               | _               | INT2EP           | INT1EP   | INT0EP |  |  |  |  |

| bit 7                              |                                                                  |                                                                                      |                 |                 |                  |          | bit (  |  |  |  |  |

|                                    |                                                                  |                                                                                      |                 |                 |                  |          |        |  |  |  |  |

| Legend:                            |                                                                  |                                                                                      |                 |                 |                  |          |        |  |  |  |  |

| R = Readable bit W = Writable bit  |                                                                  |                                                                                      |                 | U = Unimple     | emented bit, rea | d as '0' |        |  |  |  |  |

| -n = Value at POR '1' = Bit is set |                                                                  |                                                                                      | '0' = Bit is cl | eared           | x = Bit is unk   | nown     |        |  |  |  |  |

|                                    |                                                                  |                                                                                      |                 |                 |                  |          |        |  |  |  |  |

| bit 15                             | ALTIVT: Enable Alternate Interrupt Vector Table bit              |                                                                                      |                 |                 |                  |          |        |  |  |  |  |

|                                    |                                                                  | 1 = Uses Alternate Interrupt Vector Table                                            |                 |                 |                  |          |        |  |  |  |  |

| bit 14                             |                                                                  | 0 = Uses standard Interrupt Vector Table (default) DISI: DISI Instruction Status bit |                 |                 |                  |          |        |  |  |  |  |

|                                    |                                                                  | 1 = DISI instruction is active                                                       |                 |                 |                  |          |        |  |  |  |  |

|                                    | 0 = DISI instruction is not active                               |                                                                                      |                 |                 |                  |          |        |  |  |  |  |

| bit 13-3                           | Unimplemen                                                       | ted: Read as '                                                                       | 0'              |                 |                  |          |        |  |  |  |  |

| bit 2                              | INT2EP: Exte                                                     | ernal Interrupt 2                                                                    | 2 Edge Detec    | t Polarity Sele | ct bit           |          |        |  |  |  |  |

|                                    | 1 = Interrupt on negative edge                                   |                                                                                      |                 |                 |                  |          |        |  |  |  |  |

|                                    | 0 = Interrupt on positive edge                                   |                                                                                      |                 |                 |                  |          |        |  |  |  |  |

| bit 1                              | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit     |                                                                                      |                 |                 |                  |          |        |  |  |  |  |

|                                    | 1 = Interrupt on negative edge<br>0 = Interrupt on positive edge |                                                                                      |                 |                 |                  |          |        |  |  |  |  |

| <b>h</b> it 0                      | -                                                                |                                                                                      |                 | t Delevity Cele | -4 h i4          |          |        |  |  |  |  |

| bit 0                              |                                                                  | ernal Interrupt (                                                                    | 0               | a Polarity Sele |                  |          |        |  |  |  |  |

|                                    |                                                                  | on negative ed<br>on positive edg                                                    |                 |                 |                  |          |        |  |  |  |  |

|                                    |                                                                  |                                                                                      | -               |                 |                  |          |        |  |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

# 8.1 CPU Clocking System

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices provide seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with 4x PLL

- Primary (MS, HS or EC) Oscillator

- Primary Oscillator with 4x PLL

- Secondary (LP) Oscillator

- Low-Power RC (LPRC) Oscillator

- FRC Oscillator with postscaler

#### 8.1.1 SYSTEM CLOCK SOURCES

#### 8.1.1.1 Fast RC

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The FRC frequency depends on the FRC accuracy (see Table 26-18) and the value of the FRC Oscillator Tuning register (see Register 8-3).

#### 8.1.1.2 Primary

The primary oscillator can use one of the following as its clock source:

- MS (Crystal): Crystals and ceramic resonators in the range of 4 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 32 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- EC (External Clock): The external clock signal is directly applied to the OSC1 pin.

#### 8.1.1.3 Secondary

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

## 8.1.1.4 Low-Power RC

The Low-Power RC (LPRC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

#### 8.1.1.5 PLL

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip, 4x Phase Lock Loop (PLL) to provide faster output frequencies for device operation. PLL configuration is described in **Section 8.1.3 "PLL Configuration"**.

#### 8.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 23.1 "Configuration Bits" for further details.) The initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 8-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) FOSC is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device, and speeds up to 16 MHz are supported by the dsPIC33FJ16(GP/ MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 architecture.

Instruction execution speed or device operating frequency, FCY, is given by:

#### EQUATION 8-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

| REGISTER              | 10-4: RPINR                                            | 4: PERIPHE       | RAL PIN SE            | LECT INPUT            | REGISTER              | 1                     |                       |  |  |  |  |

|-----------------------|--------------------------------------------------------|------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|

| U-0                   | U-0                                                    | U-0              | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 |  |  |  |  |

| —                     | —                                                      | —                | T5CKR4 <sup>(1)</sup> | T5CKR3 <sup>(1)</sup> | T5CKR2 <sup>(1)</sup> | T5CKR1 <sup>(1)</sup> | T5CKR0 <sup>(1)</sup> |  |  |  |  |

| bit 15                |                                                        |                  |                       |                       |                       |                       | bit 8                 |  |  |  |  |

| U-0                   | U-0                                                    | U-0              | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 |  |  |  |  |

| _                     | _                                                      | _                | T4CKR4 <sup>(1)</sup> | T4CKR3 <sup>(1)</sup> | T4CKR2 <sup>(1)</sup> | T4CKR1 <sup>(1)</sup> | T4CKR0 <sup>(1)</sup> |  |  |  |  |

| bit 7                 |                                                        |                  |                       |                       |                       |                       | bit (                 |  |  |  |  |

|                       |                                                        |                  |                       |                       |                       |                       |                       |  |  |  |  |

| Legend:<br>R = Readab | la hit                                                 | W = Writable     | . hit                 |                       | nantad hit raa        |                       |                       |  |  |  |  |

|                       |                                                        |                  |                       | -                     | nented bit, read      |                       |                       |  |  |  |  |

| -n = Value a          | TPOR                                                   | '1' = Bit is se  | t                     | '0' = Bit is cle      | ared                  | x = Bit is unkr       | nown                  |  |  |  |  |

| bit 15-13             | -                                                      | ted: Read as     |                       |                       |                       |                       |                       |  |  |  |  |

| bit 12-8              | T5CKR<4:0>                                             | : Assign Time    | r5 External Clo       | ck (T5CK) to th       | ne Correspondi        | ng RPn Pin bits       | <sub>S</sub> (1)      |  |  |  |  |

|                       | 11111 <b>= I</b> npu                                   | it tied to Vss   |                       |                       |                       |                       |                       |  |  |  |  |

|                       | 11110 = Res                                            | erved            |                       |                       |                       |                       |                       |  |  |  |  |

|                       |                                                        |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       | •                                                      |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       | •                                                      |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       |                                                        | 11010 = Reserved |                       |                       |                       |                       |                       |  |  |  |  |

|                       | 11001 = Input tied to RP25                             |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       | •                                                      |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       |                                                        |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       | 00001 = Input tied to RP1<br>00000 = Input tied to RP0 |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       |                                                        |                  | (0)                   |                       |                       |                       |                       |  |  |  |  |

| bit 7-5               | •                                                      | ted: Read as     |                       |                       | <b>.</b>              |                       | (1)                   |  |  |  |  |

| bit 4-0               |                                                        |                  | r4 External Clo       | CK (14CK) to the      | ne Correspondi        | ng RPn Pin bits       | 5(1)                  |  |  |  |  |

|                       | 11111 = Inpu<br>11110 = Res                            |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       | •                                                      |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       | •                                                      |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       | 11010 = Res                                            | anvad            |                       |                       |                       |                       |                       |  |  |  |  |

|                       |                                                        | it tied to RP25  |                       |                       |                       |                       |                       |  |  |  |  |

|                       |                                                        |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       |                                                        |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       |                                                        |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       | 00001 = Inpu                                           |                  |                       |                       |                       |                       |                       |  |  |  |  |

|                       | 00000 <b>= Inpu</b>                                    | It tied to RP0   |                       |                       |                       |                       |                       |  |  |  |  |

## REGISTER 10-4: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

| U-0           | U-0        | U-0                                                                                       | R/W-0         | R/W-0             | R/W-0           | R/W-0                   | R/W-0    |  |  |

|---------------|------------|-------------------------------------------------------------------------------------------|---------------|-------------------|-----------------|-------------------------|----------|--|--|

| 0-0           | 0-0        | 0-0                                                                                       | 10,00-0       | 11/00-0           |                 |                         | 10,00-0  |  |  |

|               | —          |                                                                                           |               |                   | RP17R<4:0>(     | .)                      |          |  |  |

| bit 15        |            |                                                                                           |               |                   |                 |                         | bit 8    |  |  |

|               |            |                                                                                           |               |                   |                 |                         |          |  |  |

| U-0           | U-0        | U-0                                                                                       | R/W-0         | R/W-0             | R/W-0           | R/W-0                   | R/W-0    |  |  |

| —             | —          | _                                                                                         |               |                   | RP16R<4:0>(     | 1)                      |          |  |  |

| bit 7         |            | •                                                                                         |               |                   |                 |                         | bit 0    |  |  |

|               |            |                                                                                           |               |                   |                 |                         |          |  |  |

| Legend:       |            |                                                                                           |               |                   |                 |                         |          |  |  |

| R = Readabl   | e bit      | W = Writable                                                                              | bit           | U = Unimplen      | nented bit, rea | d as '0'                |          |  |  |

| -n = Value at | POR        | '1' = Bit is set                                                                          |               | '0' = Bit is clea | ared            | x = Bit is unkr         | iown     |  |  |

|               |            |                                                                                           |               |                   |                 |                         | <b>/</b> |  |  |

| bit 15-13     | Unimplemen | ted: Read as '                                                                            | 0'            |                   |                 |                         |          |  |  |

| bit 12-8      | RP17R<4:0> | Peripheral Ou                                                                             | tput Function | is Assigned to    | RP17 Output I   | Pin bits <sup>(1)</sup> |          |  |  |

|               |            | -2 for peripher                                                                           | •             | •                 | •               |                         |          |  |  |

| bit 7-5       |            | ted: Read as '                                                                            |               | - /               |                 |                         |          |  |  |

|               | -          |                                                                                           |               |                   |                 | - · · · (1)             |          |  |  |

| bit 4-0       | RP16R<4:0> | RP16R<4:0>: Peripheral Output Function is Assigned to RP16 Output Pin bits <sup>(1)</sup> |               |                   |                 |                         |          |  |  |

#### **REGISTER 10-19: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8**

(see Table 10-2 for peripheral function numbers)

| U-0     | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|---------|-----|-----|-------|-------|--------------------------|-------|-------|

|         |     |     |       |       | RP19R<4:0> <sup>(1</sup> | )     |       |

| bit 15  |     |     |       |       |                          |       | bit 8 |

|         |     |     |       |       |                          |       |       |

| U-0     | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

| _       | _   |     |       |       | RP18R<4:0> <sup>(1</sup> | )     |       |

| bit 7   |     |     |       |       |                          |       | bit 0 |

|         |     |     |       |       |                          |       |       |

| Legend: |     |     |       |       |                          |       |       |

| Logonan           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                |

|-----------|-------------------------------------------------------------------------------------------|

| bit 12-8  | RP19R<4:0>: Peripheral Output Function is Assigned to RP19 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                          |

| bit 7-5   | Unimplemented: Read as '0'                                                                |

| bit 4-0   | RP18R<4:0>: Peripheral Output Function is Assigned to RP18 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                          |

Note 1: These bits are available in dsPIC33FJ32(GP/MC)104 devices only.

Note 1: These bits are available in dsPIC33FJ32(GP/MC)104 devices only.

| REGISTER     | 19-4. ADICI                                                                                                                                                                                          | 15123: ADCT                                                                                                                          |                | ANNUL $1, 2,$    | S SELECT RE       | GISTER            |                  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-------------------|-------------------|------------------|--|--|--|--|

| U-0          | U-0                                                                                                                                                                                                  | U-0                                                                                                                                  | U-0            | U-0              | R/W-0             | R/W-0             | R/W-0            |  |  |  |  |

| _            |                                                                                                                                                                                                      | —                                                                                                                                    |                | —                | CH123NB1          | CH123NB0          | CH123SB          |  |  |  |  |

| bit 15       |                                                                                                                                                                                                      | bit 8                                                                                                                                |                |                  |                   |                   |                  |  |  |  |  |

|              |                                                                                                                                                                                                      |                                                                                                                                      |                |                  |                   | DAMO              | DAMO             |  |  |  |  |

| U-0          | U-0                                                                                                                                                                                                  | U-0                                                                                                                                  | U-0            | U-0              | R/W-0             | R/W-0<br>CH123NA0 | R/W-0            |  |  |  |  |

| <br>bit 7    | —                                                                                                                                                                                                    | —                                                                                                                                    | _              | —                | CH123NA1          | CH123NAU          | CH123SA<br>bit ( |  |  |  |  |

|              |                                                                                                                                                                                                      |                                                                                                                                      |                |                  |                   |                   | Dit (            |  |  |  |  |

| Legend:      |                                                                                                                                                                                                      |                                                                                                                                      |                |                  |                   |                   |                  |  |  |  |  |

| R = Readab   | le bit                                                                                                                                                                                               | W = Writable bi                                                                                                                      | t              | U = Unimple      | mented bit, read  | d as '0'          |                  |  |  |  |  |

| -n = Value a | t POR                                                                                                                                                                                                | '1' = Bit is set                                                                                                                     |                | '0' = Bit is cl  | eared             | x = Bit is unkr   | nown             |  |  |  |  |

|              |                                                                                                                                                                                                      |                                                                                                                                      |                |                  |                   |                   |                  |  |  |  |  |

| bit 15-11    | Unimplemen                                                                                                                                                                                           | ted: Read as '0'                                                                                                                     |                |                  |                   |                   |                  |  |  |  |  |

| bit 10-9     | CH123NB<1:                                                                                                                                                                                           | 0>: Channel 1, 2                                                                                                                     | 2, 3 Negative  | Input Select f   | or Sample B bit   | 5                 |                  |  |  |  |  |

|              | dsPIC33FJ16                                                                                                                                                                                          | CH123NB<1:0>: Channel 1, 2, 3 Negative Input Select for Sample B bits<br>dsPIC33FJ16(GP/MC)101/102 Devices Only:                     |                |                  |                   |                   |                  |  |  |  |  |

|              | 11 = Reserved                                                                                                                                                                                        |                                                                                                                                      |                |                  |                   |                   |                  |  |  |  |  |

|              |                                                                                                                                                                                                      | 10 = Reserved                                                                                                                        |                |                  |                   |                   |                  |  |  |  |  |

|              |                                                                                                                                                                                                      | 0x = CH1, CH2, CH3 negative inputs are AVss                                                                                          |                |                  |                   |                   |                  |  |  |  |  |

|              |                                                                                                                                                                                                      | 2(GP/MC)101/10                                                                                                                       |                |                  |                   |                   |                  |  |  |  |  |

|              | 11 = CH1 heg<br>10 = Reserve                                                                                                                                                                         | gative input is AN                                                                                                                   | v9, CH2 nega   | ative input is A | IN10, CH3 nega    | tive input is not | connected        |  |  |  |  |

|              |                                                                                                                                                                                                      | d<br>12, CH3 negative                                                                                                                | e inputs are A | Wss              |                   |                   |                  |  |  |  |  |

|              |                                                                                                                                                                                                      |                                                                                                                                      | •              |                  |                   |                   |                  |  |  |  |  |

|              |                                                                                                                                                                                                      | <u>dsPIC33FJ32(GP/MC)104 Devices Only:</u><br>11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11 |                |                  |                   |                   |                  |  |  |  |  |

|              | 10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8                                                                                                                 |                                                                                                                                      |                |                  |                   |                   |                  |  |  |  |  |

|              | 0x = CH1, CH2, CH3 negative inputs are AVss                                                                                                                                                          |                                                                                                                                      |                |                  |                   |                   |                  |  |  |  |  |

| bit 8        | CH123SB: Ch                                                                                                                                                                                          | nannel 1, 2, 3 Po                                                                                                                    | sitive Input S | Select for Sam   | ple B bit         |                   |                  |  |  |  |  |

|              | dsPIC33FJXX(GP/MC)101 Devices Only:                                                                                                                                                                  |                                                                                                                                      |                |                  |                   |                   |                  |  |  |  |  |

|              | 1 = CH1 positive input is AN3, CH2 and CH3 positive inputs are not connected                                                                                                                         |                                                                                                                                      |                |                  |                   |                   |                  |  |  |  |  |

|              | 0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2                                                                                                                  |                                                                                                                                      |                |                  |                   |                   |                  |  |  |  |  |

|              | All Other Devices:                                                                                                                                                                                   |                                                                                                                                      |                |                  |                   |                   |                  |  |  |  |  |

|              | <ul> <li>1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5</li> <li>0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2</li> </ul> |                                                                                                                                      |                |                  |                   |                   |                  |  |  |  |  |

|              | -                                                                                                                                                                                                    | •                                                                                                                                    | •              | e input is AN1   | , CH3 positive in | iput is Ainz      |                  |  |  |  |  |

| bit 7-3      | -                                                                                                                                                                                                    | ted: Read as '0'                                                                                                                     |                |                  |                   |                   |                  |  |  |  |  |

| bit 2-1      | CH123NA<1:0>: Channel 1, 2, 3 Negative Input Select for Sample A bits                                                                                                                                |                                                                                                                                      |                |                  |                   |                   |                  |  |  |  |  |

|              |                                                                                                                                                                                                      | 10-9> for the ava                                                                                                                    |                |                  |                   |                   |                  |  |  |  |  |

| bit 0        |                                                                                                                                                                                                      | nannel 1, 2, 3 Po                                                                                                                    | =              | Select for Sam   | ple A bit         |                   |                  |  |  |  |  |

|              | Refer to bit 8                                                                                                                                                                                       | for the available                                                                                                                    | settings.      |                  |                   |                   |                  |  |  |  |  |

|              |                                                                                                                                                                                                      |                                                                                                                                      |                |                  |                   |                   |                  |  |  |  |  |

#### REGISTER 19-4: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

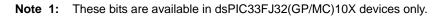

# FIGURE 26-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

## TABLE 26-25: INPUT CAPTURE x (ICx) TIMING REQUIREMENTS

| AC CHARACTERISTICS                                |      |                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |              |       |            |                                  |  |

|---------------------------------------------------|------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|------------|----------------------------------|--|

| Param<br>No. Symbol Characteristic <sup>(1)</sup> |      |                     | Min                                                                                                                                                                                                                                                                               | Мах          | Units | Conditions |                                  |  |

| IC10                                              | TccL | ICx Input Low Time  | No Prescaler                                                                                                                                                                                                                                                                      | 0.5 TCY + 20 | _     | ns         |                                  |  |

|                                                   |      |                     | With Prescaler                                                                                                                                                                                                                                                                    | 10           | —     | ns         |                                  |  |

| IC11                                              | TccH | ICx Input High Time | No Prescaler                                                                                                                                                                                                                                                                      | 0.5 TCY + 20 | _     | ns         |                                  |  |

|                                                   |      |                     | With Prescaler                                                                                                                                                                                                                                                                    | 10           | _     | ns         |                                  |  |

| IC15                                              | TccP | ICx Input Period    |                                                                                                                                                                                                                                                                                   | (Tcy + 40)/N | _     | ns         | N = prescale value<br>(1, 4, 16) |  |

**Note 1:** These parameters are characterized by similarity, but are not tested in manufacturing.

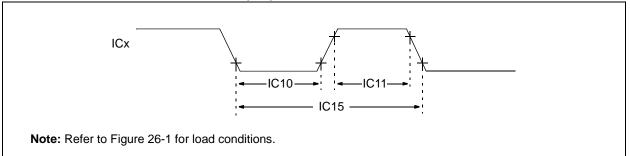

#### FIGURE 26-20: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS FOR dsPIC33FJ32(GP/MC)10X

# TABLE 26-38:SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS<br/>FOR dsPIC33FJ32(GP/MC)10X

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |

|--------------------|-----------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                | Min                                                                                                                                                                                                                                                                                 | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP10               | TscP                  | Maximum SCKx Frequency                       | —                                                                                                                                                                                                                                                                                   | _                  | 15  | MHz   | See Note 3                           |

| SP20               | TscF                  | SCKx Output Fall Time                        | _                                                                                                                                                                                                                                                                                   | —                  | _   | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP21               | TscR                  | SCKx Output Rise Time                        | _                                                                                                                                                                                                                                                                                   | —                  |     | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30               | TdoF                  | SDOx Data Output Fall Time                   |                                                                                                                                                                                                                                                                                     | —                  | _   | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31               | TdoR                  | SDOx Data Output Rise Time                   | _                                                                                                                                                                                                                                                                                   | —                  |     | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    |                                                                                                                                                                                                                                                                                     | 6                  | 20  | ns    |                                      |

| SP36               | TdiV2scH,<br>TdiV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30                                                                                                                                                                                                                                                                                  | —                  | _   | ns    |                                      |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

# TABLE 26-42:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ32(GP/MC)10X

| AC CHARACTERISTICS |                       |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |

|--------------------|-----------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                                                                                                                                                                                                                                                 | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP70               | TscP                  | Maximum SCKx Input Frequency                                 | —                                                                                                                                                                                                                                                                                   | _                  | 11  | MHz   | See Note 3                           |

| SP72               | TscF                  | SCKx Input Fall Time                                         | _                                                                                                                                                                                                                                                                                   | —                  |     | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP73               | TscR                  | SCKx Input Rise Time                                         | —                                                                                                                                                                                                                                                                                   | _                  |     | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                   | —                                                                                                                                                                                                                                                                                   |                    |     | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                   | —                                                                                                                                                                                                                                                                                   |                    |     | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                                                                                                                                                                                                                                                   | 6                  | 20  | ns    |                                      |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                                                                                                                                                                                                                                                  |                    |     | ns    |                                      |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                                                                                                                                                                                                                                                  | —                  | _   | ns    |                                      |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                                                                                                                                                                                                                                                  | _                  | _   | ns    |                                      |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                                                                                                                                                                                                                                                 | —                  | _   | ns    |                                      |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10                                                                                                                                                                                                                                                                                  | —                  | 50  | ns    | See Note 4                           |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 Tcy + 40                                                                                                                                                                                                                                                                        | —                  | —   | ns    | See Note 4                           |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                     | —                                                                                                                                                                                                                                                                                   | _                  | 50  | ns    |                                      |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

## 28.1 Package Marking Information (Continued)

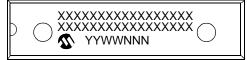

#### 28-Lead SPDIP

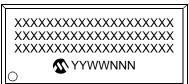

28-Lead SOIC

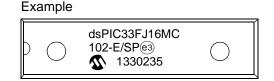

Example

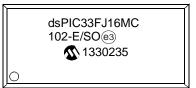

#### 28-Lead SSOP

#### 28-Lead QFN

#### 36-Lead VTLA

## Example

#### Example

#### Example

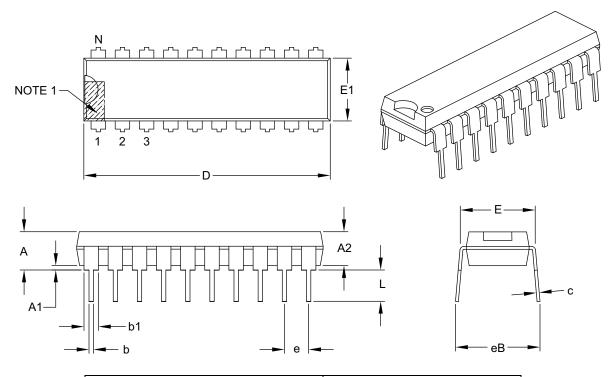

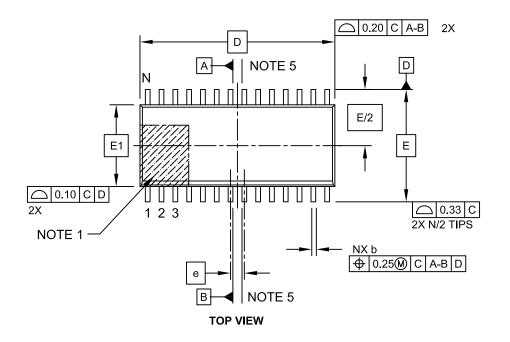

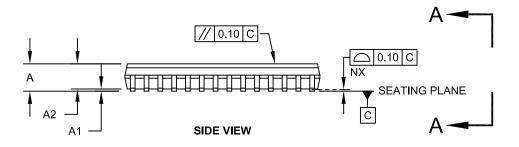

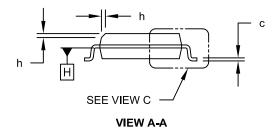

## 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units     |      | INCHES   |       |

|----------------------------|-----------|------|----------|-------|

| Dimensio                   | on Limits | MIN  | NOM      | MAX   |

| Number of Pins             | Ν         |      | 20       |       |

| Pitch                      | е         |      | .100 BSC |       |

| Top to Seating Plane       | Α         | -    | -        | .210  |

| Molded Package Thickness   | A2        | .115 | .130     | .195  |

| Base to Seating Plane      | A1        | .015 | -        | -     |

| Shoulder to Shoulder Width | Е         | .300 | .310     | .325  |

| Molded Package Width       | E1        | .240 | .250     | .280  |

| Overall Length             | D         | .980 | 1.030    | 1.060 |

| Tip to Seating Plane       | L         | .115 | .130     | .150  |

| Lead Thickness             | С         | .008 | .010     | .015  |

| Upper Lead Width           | b1        | .045 | .060     | .070  |

| Lower Lead Width           | b         | .014 | .018     | .022  |

| Overall Row Spacing §      | eB        | -    | -        | .430  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.