Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K × 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

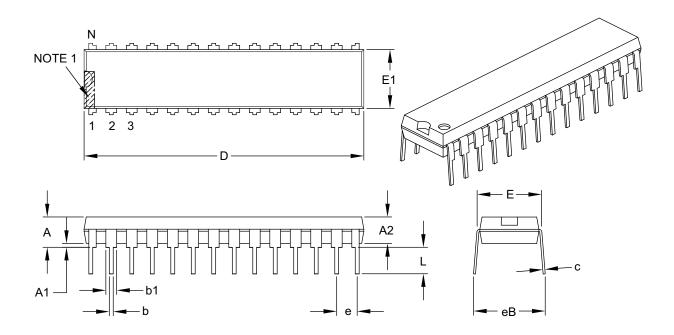

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gp102-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0             | U-0                            | U-0                                   | R/W-0           | R/W-0               | R-0              | R-0              | R-0   |

|-----------------|--------------------------------|---------------------------------------|-----------------|---------------------|------------------|------------------|-------|

| —               | —                              | _                                     | US              | EDT <sup>(1)</sup>  | DL2              | DL1              | DL0   |

| bit 15          |                                |                                       |                 |                     |                  |                  | bit   |

| R/W-0           | R/W-0                          | R/W-1                                 | R/W-0           | R/C-0               | R/W-0            | R/W-0            | R/W-0 |

| SATA            | SATB                           | SATDW                                 | ACCSAT          | IPL3 <sup>(2)</sup> | PSV              | R/W-0            | IF    |

| bit 7           | SAID                           | SAIDW                                 | ACCOAT          | IF L3. 7            | F3V              | RND              | bit   |

|                 |                                |                                       |                 |                     |                  |                  | Dit   |

| Legend:         |                                | C = Clearable                         | e bit           |                     |                  |                  |       |

| R = Readabl     | e bit                          | W = Writable                          | bit             | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is cle | ared                           | 'x = Bit is unk                       | nown            | U = Unimple         | mented bit, read | d as '0'         |       |

| bit 15-13       | Unimplemen                     | ted: Read as '                        | 0'              |                     |                  |                  |       |

| bit 12          | -                              | tiply Unsigned                        |                 | ol bit              |                  |                  |       |

|                 |                                | ne multiplies a                       | •               |                     |                  |                  |       |

|                 | 0 = DSP engi                   | ne multiplies a                       | ire signed      |                     |                  |                  |       |

| bit 11          |                                | Loop Termina                          |                 |                     |                  |                  |       |

|                 | 1 = Terminate<br>0 = No effect | es executing Do                       | o loop at the e | nd of current lo    | oop iteration    |                  |       |

| bit 10-8        | DL<2:0>: DO                    | Loop Nesting                          | Level Status b  | its                 |                  |                  |       |

|                 | 111 <b>= 7</b> DO <b>lo</b>    | ops are active                        |                 |                     |                  |                  |       |

|                 | •                              |                                       |                 |                     |                  |                  |       |

|                 | •<br>001 = 1 DO lo             | on is activo                          |                 |                     |                  |                  |       |

|                 |                                | ops are active                        |                 |                     |                  |                  |       |

| bit 7           | SATA: ACCA                     | Saturation En                         | able bit        |                     |                  |                  |       |

|                 |                                | itor A saturatio                      |                 |                     |                  |                  |       |

|                 |                                | itor A saturatio                      |                 |                     |                  |                  |       |

| bit 6           |                                | Saturation En                         |                 |                     |                  |                  |       |

|                 |                                | tor B saturatio                       |                 |                     |                  |                  |       |

| bit 5           |                                |                                       |                 | ine Saturation      | Enable bit       |                  |       |

|                 |                                | ce write satura                       |                 |                     |                  |                  |       |

|                 |                                | ce write satura                       |                 |                     |                  |                  |       |

| bit 4           | ACCSAT: Acc                    | cumulator Satu                        | uration Mode S  | Select bit          |                  |                  |       |

|                 |                                | ration (super s                       |                 |                     |                  |                  |       |

| L:1 0           |                                | ration (normal                        | ,               | ··· (2)             |                  |                  |       |

| bit 3           |                                | terrupt Priority<br>rrupt Priority Le |                 |                     |                  |                  |       |

|                 |                                | rupt Priority Le                      | •               |                     |                  |                  |       |

| bit 2           |                                |                                       |                 | ace Enable bit      |                  |                  |       |

|                 |                                | space is visible                      |                 |                     |                  |                  |       |

|                 | -                              | space is not vi                       |                 | pace                |                  |                  |       |

| bit 1           |                                | ng Mode Sele                          |                 |                     |                  |                  |       |

|                 |                                | onventional) ro<br>(convergent)       |                 |                     |                  |                  |       |

| bit 0           | IF: Integer or                 | Fractional Mul                        | tiplier Mode S  | elect bit           |                  |                  |       |

|                 | -                              |                                       |                 | iply operations     |                  |                  |       |

|                 | 0 = Fractional                 | l mode is enab                        | led for DSP m   | nultiply operation  | ons              |                  |       |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### 3.6.1 MULTIPLIER

The 17-bit x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17-bit x 17-bit multiplier/scaler is a 33-bit value that is sign-extended to 40 bits. Integer data is inherently represented as a signed 2's complement value, where the Most Significant bit (MSb) is defined as a sign bit. The range of an N-bit 2's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ .

- For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF) including 0.

- For a 32-bit integer, the data range is -2,147,483,648 (0x8000 0000) to 2,147,483,647 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a 2's complement fraction, where the MSb is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit 2's complement fraction with this implied radix point is -1.0 to  $(1 - 2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including 0 and has a precision of 3.01518x10<sup>-5</sup>. In Fractional mode, the 16 x 16 multiply operation generates a 1.31 product that has a precision of 4.65661 x 10<sup>-10</sup>.

The same multiplier is used to support the MCU multiply instructions, which include integer 16-bit signed, unsigned and mixed sign multiply operations.

The MUL instruction can be directed to use byte or word-sized operands. Byte operands will direct a 16-bit result and word operands will direct a 32-bit result to the specified register(s) in the W array.

### 3.6.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/ subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its pre-accumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled using the barrel shifter prior to accumulation.

## 3.6.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side and either true or complement data into the other input.

- In the case of addition, the Carry/Borrow input is active-high and the other input is true data (not complemented).

- In the case of subtraction, the Carry/Borrow input is active-low and the other input is complemented.

The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS Register:

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block that controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described previously, and the SAT<A:B> (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value, to saturate.

Six STATUS Register bits support saturation and overflow:

- OA: ACCA overflowed into guard bits

- OB: ACCB overflowed into guard bits

- SA: ACCA saturated (bit 31 overflow and saturation)

ACCA overflowed into guard bits and saturated (bit 39 overflow and saturation)

- SB: ACCB saturated (bit 31 overflow and saturation)

- ACCB overflowed into guard bits and saturated (bit 39 overflow and saturation)

- OAB: Logical OR of OA and OB

- SAB: Logical OR of SA and SB

or

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when OA and OB are set and the corresponding Overflow Trap Flag Enable bits (OVATE, OVBTE) in the INTCON1 register are set (refer to **Section 7.0 "Interrupt Controller"**). This allows the user application to take immediate action; for example, to correct system gain.

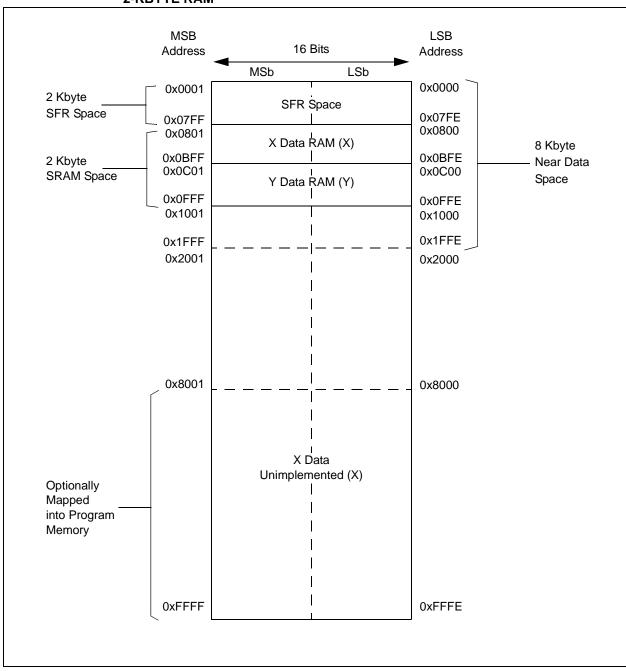

# FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJ32(GP/MC)101/102/104 DEVICES WITH 2-KBYTE RAM

### dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| bit 15          |     |                  |     |                     |              |                 | bit 8 |

|-----------------|-----|------------------|-----|---------------------|--------------|-----------------|-------|

| W-0             | W-0 | W-0              | W-0 | W-0                 | W-0          | W-0             | W-0   |

|                 |     |                  | NVM | KEY<7:0>            |              |                 |       |

| bit 7           |     |                  |     |                     |              |                 | bit ( |

|                 |     |                  |     |                     |              |                 |       |

| Legend:         |     |                  |     |                     |              |                 |       |

| R = Readable    | bit | W = Writable bit |     | U = Unimplemer      | nted bit, re | ad as '0'       |       |

| -n = Value at P | OR  | '1' = Bit is set |     | '0' = Bit is cleare | ed           | x = Bit is unkn | iown  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register bits (write-only)

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 0x000004    | 0x000104     | Reserved           |

| 1             | 0x000006    | 0x000106     | Oscillator Failure |

| 2             | 0x00008     | 0x000108     | Address Error      |

| 3             | 0x00000A    | 0x00010A     | Stack Error        |

| 4             | 0x00000C    | 0x00010C     | Math Error         |

| 5             | 0x00000E    | 0x00010E     | Reserved           |

| 6             | 0x000010    | 0x000110     | Reserved           |

| 7             | 0x000012    | 0x000112     | Reserved           |

#### TABLE 7-2:TRAP VECTORS

#### 7.3 Interrupt Control and Status Registers

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices implement a total of 26 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFSx

- IECx

- IPCx

- INTTREG

#### 7.3.1 INTCON1 AND INTCON2

Global interrupt functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

#### 7.3.2 IFSx Registers

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.3.3 IECx Registers

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.3.4 IPCx Registers

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 7.3.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into Vector Number (VECNUM<6:0>) and Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IPx bits in the first positions of IPC0 (IPC0<2:0>).

#### 7.3.6 STATUS/CONTROL REGISTERS

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality.

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user application can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-28 on the following pages.

#### 8.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip, 4x PLL to obtain higher speeds of operation.

For example, suppose an 8 MHz crystal is being used with the selected oscillator mode of MS with PLL. This provides a Fosc of 8 MHz \* 4 = 32 MHz. The resultant device operating speed is 32/2 = 16 MIPS.

#### EQUATION 8-2: MS WITH PLL MODE EXAMPLE

```

FCY = \frac{FOSC}{2} = \frac{1}{2} (8000000 • 4) = 16 MIPS

```

| TABLE 8-1: | CONFIGURATION BIT VALU | ES FOR CLOCH | <b>SELECTION</b> |  |

|------------|------------------------|--------------|------------------|--|

|            |                        |              |                  |  |

| Oscillator Mode                                            | Oscillator<br>Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Note |

|------------------------------------------------------------|----------------------|-------------|------------|-------------|

| Fast RC Oscillator with Divide-by-n (FRCDIVN)              | Internal             | xx          | 111        | 1, 2        |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal             | xx          | 110        | 1           |

| Low-Power RC Oscillator (LPRC)                             | Internal             | xx          | 101        | 1           |

| Secondary (Timer1) Oscillator (SOSC)                       | Secondary            | xx          | 100        | 1           |

| Primary Oscillator (MS) with PLL (MSPLL)                   | Primary              | 01          | 011        |             |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary              | 00          | 011        | 1           |

| Primary Oscillator (HS)                                    | Primary              | 10          | 010        |             |

| Primary Oscillator (MS)                                    | Primary              | 01          | 010        |             |

| Primary Oscillator (EC)                                    | Primary              | 00          | 010        | 1           |

| Fast RC Oscillator (FRC) with Divide-by-n and PLL (FRCPLL) | Internal             | xx          | 001        | 1           |

| Fast RC Oscillator (FRC)                                   | Internal             | xx          | 000        | 1           |

**Note 1:** OSC2 pin function is determined by the OSCIOFNC Configuration bit.

**2:** This is the default oscillator mode for an unprogrammed (erased) device.

| R/W-0        | R/W-0                                            | R/W-1                        | R/W-1                                                    | R/W-0                        | R/W-0           | R/W-0             | R/W-0       |  |  |  |

|--------------|--------------------------------------------------|------------------------------|----------------------------------------------------------|------------------------------|-----------------|-------------------|-------------|--|--|--|

| ROI          | DOZE2 <sup>(2,3)</sup>                           | DOZE1 <sup>(2,3)</sup>       | DOZE0 <sup>(2,3)</sup>                                   | DOZEN <sup>(1,2,3)</sup>     | FRCDIV2         | FRCDIV1           | FRCDIV0     |  |  |  |

| bit 15       |                                                  |                              |                                                          |                              |                 |                   | bit         |  |  |  |

|              |                                                  |                              |                                                          |                              |                 |                   |             |  |  |  |

| U-0          | U-0                                              | U-0                          | U-0                                                      | U-0                          | U-0             | U-0               | U-0         |  |  |  |

|              | _                                                | _                            |                                                          | —                            |                 |                   | —           |  |  |  |

| bit 7        |                                                  |                              |                                                          |                              |                 |                   | bit         |  |  |  |

| Legend:      |                                                  |                              |                                                          |                              |                 |                   |             |  |  |  |

| R = Readab   | le bit                                           | W = Writable                 | bit                                                      | U = Unimpleme                | ented bit, read | as '0'            |             |  |  |  |

| -n = Value a | t POR                                            | '1' = Bit is set             |                                                          | '0' = Bit is clear           | ed              | x = Bit is unk    | nown        |  |  |  |

|              |                                                  |                              |                                                          |                              |                 |                   |             |  |  |  |

| bit 15       | 1 = Interrupts<br>0 = Interrupts                 | s have no effec              | DOZEN bit and to the |                              | clock/periphera | al clock ratio is | set to 1:1  |  |  |  |

| bit 14-12    | DOZE<2:0>:                                       | Processor Cloo               | ck Reduction S                                           | Select bits <sup>(2,3)</sup> |                 |                   |             |  |  |  |

|              | 111 = Fcy/128                                    |                              |                                                          |                              |                 |                   |             |  |  |  |

|              | 110 = FCY/64<br>101 = FCY/32                     |                              |                                                          |                              |                 |                   |             |  |  |  |

|              | 101 = FCY/16                                     |                              |                                                          |                              |                 |                   |             |  |  |  |

|              | 011 = FCY/8 (                                    | default)                     |                                                          |                              |                 |                   |             |  |  |  |

|              | 010 = FCY/4                                      |                              |                                                          |                              |                 |                   |             |  |  |  |

|              | 001 = FCY/2<br>000 = FCY/1                       |                              |                                                          |                              |                 |                   |             |  |  |  |

| bit 11       |                                                  | E Mode Enabl                 | e bit <sup>(1,2,3)</sup>                                 |                              |                 |                   |             |  |  |  |

|              |                                                  |                              |                                                          | io between the p             | eripheral clock | s and the proc    | essor clock |  |  |  |

|              | 0 = Processo                                     | or clock/periphe             | eral clock ratio                                         | is forced to 1:1             |                 |                   |             |  |  |  |

| bit 10-8     |                                                  |                              | RC Oscillator                                            | Postscaler bits              |                 |                   |             |  |  |  |

|              | 111 = FRC divide-by-256                          |                              |                                                          |                              |                 |                   |             |  |  |  |

|              | 110 = FRC divide-by-64<br>101 = FRC divide-by-32 |                              |                                                          |                              |                 |                   |             |  |  |  |

|              | 100 = FRC di                                     | •                            |                                                          |                              |                 |                   |             |  |  |  |

|              | 011 = FRC di                                     | •                            |                                                          |                              |                 |                   |             |  |  |  |

|              | 010 = FRC di                                     |                              |                                                          |                              |                 |                   |             |  |  |  |

|              | 001 = FRC di                                     | vide-by-2<br>vide-by-1 (defa |                                                          |                              |                 |                   |             |  |  |  |

|              |                                                  | •                            |                                                          |                              |                 |                   |             |  |  |  |

| bit 7-0      | Unimploment                                      | ted: Read as '               | o'                                                       |                              |                 |                   |             |  |  |  |

#### REGISTER 8-2: CLKDIV: CLOCK DIVISOR REGISTER

**Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- **2:** If DOZEN = 1, writes to DOZE<2:0> are ignored.

- 3: If DOZE<2:0> = 000, the DOZEN bit cannot be set by the user; writes are ignored.

#### 10.7 Peripheral Pin Select Registers

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family of devices implements up to 23 registers for remappable peripheral configuration.

Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 10.4.3.1 "Control Register Lock" for a specific command sequence.

#### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0             | U-0 | U-0              | R/W-1  | R/W-1            | R/W-1            | R/W-1           | R/W-1  |

|-----------------|-----|------------------|--------|------------------|------------------|-----------------|--------|

| _               | —   | _                | INT1R4 | INT1R3           | INT1R2           | INT1R1          | INT1R0 |

| bit 15          |     |                  |        |                  |                  |                 | bit 8  |

|                 |     |                  |        |                  |                  |                 |        |

| U-0             | U-0 | U-0              | U-0    | U-0              | U-0              | U-0             | U-0    |

| —               | —   | —                | —      | —                | —                | —               | —      |

| bit 7           |     |                  |        |                  |                  |                 | bit 0  |

|                 |     |                  |        |                  |                  |                 |        |

| Legend:         |     |                  |        |                  |                  |                 |        |

| R = Readable b  | oit | W = Writable     | bit    | U = Unimpler     | mented bit, read | as '0'          |        |

| -n = Value at P | OR  | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| -n = value a | IT POR  | T = Bit is set                 | 0° = Bit is cleared             | X = Bit is unknown |

|--------------|---------|--------------------------------|---------------------------------|--------------------|

| bit 15-13    | Unimple | mented: Read as '0'            |                                 |                    |

| bit 12-8     | INT1R<4 | 1:0>: Assign External Interr   | upt 1 (INTR1) to the Correspond | ding RPn Pin bits  |

|              |         | Input tied to Vss<br>Reserved  |                                 |                    |

|              | •       |                                |                                 |                    |

|              | •       |                                |                                 |                    |

|              |         | Reserved<br>Input tied to RP25 |                                 |                    |

|              |         |                                |                                 |                    |

|              | •       |                                |                                 |                    |

bit 7-0 Unimplemented: Read as '0'

00001 = Input tied to RP1 00000 = Input tied to RP0

# 12.3 Timer2/3 and Timer4/5 Control Registers

| _             |                                       |                              |                |                  |                 |                 |       |

|---------------|---------------------------------------|------------------------------|----------------|------------------|-----------------|-----------------|-------|

| R/W-0         | U-0                                   | R/W-0                        | U-0            | U-0              | U-0             | U-0             | U-0   |

| TON           |                                       | TSIDL                        | _              |                  | —               |                 | _     |

| bit 15        |                                       |                              |                |                  |                 |                 | bit 8 |

|               |                                       |                              |                |                  |                 |                 |       |

| U-0           | R/W-0                                 | R/W-0                        | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |

| _             | TGATE                                 | TCKPS1                       | TCKPS0         | T32              | —               | TCS             | —     |

| bit 7         |                                       |                              |                |                  |                 |                 | bit C |

|               |                                       |                              |                |                  |                 |                 |       |

| Legend:       |                                       |                              |                |                  |                 |                 |       |

| R = Readabl   | e bit                                 | W = Writable I               | oit            | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value at | POR                                   | '1' = Bit is set             |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|               |                                       |                              |                |                  |                 |                 |       |

| bit 15        | TON: Timer2                           | On bit                       |                |                  |                 |                 |       |

|               | When T32 = 2                          |                              |                |                  |                 |                 |       |

|               | 1 = Starts 32-                        |                              |                |                  |                 |                 |       |

|               | 0 = Stops 32-                         |                              |                |                  |                 |                 |       |

|               | <u>When T32 = 0</u><br>1 = Starts 16- |                              |                |                  |                 |                 |       |

|               | 0 = Stops 16-                         |                              |                |                  |                 |                 |       |

| bit 14        | Unimplemen                            | ted: Read as '               | )'             |                  |                 |                 |       |

| bit 13        | TSIDL: Timer                          | 2 Stop in Idle M             | lode bit       |                  |                 |                 |       |

|               |                                       | ues module ope               |                |                  | lle mode        |                 |       |

|               |                                       | s module opera               |                | de               |                 |                 |       |

| bit 12-7      | Unimplemen                            | ted: Read as '0              | )'             |                  |                 |                 |       |

| bit 6         |                                       | er2 Gated Time               | Accumulation   | Enable bit       |                 |                 |       |

|               | When TCS =                            |                              |                |                  |                 |                 |       |

|               | This bit is igno<br>When TCS =        |                              |                |                  |                 |                 |       |

|               |                                       | <u>o.</u><br>e accumulatior  | is enabled     |                  |                 |                 |       |

|               |                                       | e accumulation               |                |                  |                 |                 |       |

| bit 5-4       | TCKPS<1:0>                            | : Timer2 Input               | Clock Prescale | e Select bits    |                 |                 |       |

|               | 11 <b>= 1:256</b>                     |                              |                |                  |                 |                 |       |

|               | 10 = 1:64                             |                              |                |                  |                 |                 |       |

|               | 01 = 1:8<br>00 = 1:1                  |                              |                |                  |                 |                 |       |

| bit 3         |                                       | imer Mode Sele               | ct bit         |                  |                 |                 |       |

| Sit 0         |                                       | nd Timer3 form               |                | timer            |                 |                 |       |

|               |                                       | nd Timer3 act a              |                |                  |                 |                 |       |

| bit 2         | Unimplemen                            | ted: Read as '               | )'             |                  |                 |                 |       |

| bit 1         | TCS: Timer2                           | Clock Source S               | elect bit      |                  |                 |                 |       |

|               |                                       | clock from pin, <sup>-</sup> | Γ2CK (on the r | ising edge)      |                 |                 |       |

|               | 0 = Internal cl                       |                              |                |                  |                 |                 |       |

| bit 0         | Unimplemen                            | ted: Read as '0              | ) <b>'</b>     |                  |                 |                 |       |

#### REGISTER 12-1: T2CON: TIMER2 CONTROL REGISTER

NOTES:

#### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- bit 4-2 SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup>

- 111 = Secondary prescale 1:1

- 110 = Secondary prescale 2:1

- . .

- 000 = Secondary prescale 8:1

- bit 1-0 **PPRE<1:0>:** Primary Prescale bits (Master mode)<sup>(3)</sup>

- 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- **Note 1:** The CKE bit is not used in the Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- **3:** Do not set both primary and secondary prescalers to a value of 1:1.

| R/W-0                                           | R/W-0                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                 | U-0                                                                                                                                                                         | U-0                          | U-0              | U-0                | U-0   |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|--------------------|-------|

| FRMEN                                           | SPIFSD                                                                                                                                                                   | FRMPOL                                                                                                                                                                                                                |                                                                                                                                                                             | —                            |                  | —                  | _     |

| bit 15                                          |                                                                                                                                                                          |                                                                                                                                                                                                                       |                                                                                                                                                                             |                              |                  |                    | bit 8 |

| U-0                                             | U-0                                                                                                                                                                      | U-0                                                                                                                                                                                                                   | U-0                                                                                                                                                                         | U-0                          | U-0              | R/W-0              | U-0   |

|                                                 | <u> </u>                                                                                                                                                                 |                                                                                                                                                                                                                       | <u> </u>                                                                                                                                                                    |                              |                  | FRMDLY             |       |

| pit 7                                           |                                                                                                                                                                          |                                                                                                                                                                                                                       |                                                                                                                                                                             |                              |                  | TRIBET             | bit ( |

|                                                 |                                                                                                                                                                          |                                                                                                                                                                                                                       |                                                                                                                                                                             |                              |                  |                    |       |

| _egend:                                         |                                                                                                                                                                          |                                                                                                                                                                                                                       |                                                                                                                                                                             |                              |                  |                    |       |

| R = Readable                                    | bit                                                                                                                                                                      | W = Writable                                                                                                                                                                                                          | bit                                                                                                                                                                         | U = Unimplen                 | nented bit, read | l as '0'           |       |

| -n = Value at I                                 | POR                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                      |                                                                                                                                                                             | '0' = Bit is clea            | ared             | x = Bit is unknown |       |

|                                                 |                                                                                                                                                                          |                                                                                                                                                                                                                       |                                                                                                                                                                             |                              |                  |                    |       |

|                                                 |                                                                                                                                                                          |                                                                                                                                                                                                                       |                                                                                                                                                                             |                              |                  |                    |       |

| bit 15                                          |                                                                                                                                                                          | ned SPIx Supp                                                                                                                                                                                                         |                                                                                                                                                                             |                              |                  |                    |       |

| bit 15                                          | 1 = Framed S                                                                                                                                                             | Plx support is                                                                                                                                                                                                        | enabled (SSx                                                                                                                                                                | pin is used as               | Frame Sync pu    | ulse input/output  | )     |

|                                                 | 1 = Framed S<br>0 = Framed S                                                                                                                                             | Plx support is<br>Plx support is                                                                                                                                                                                      | enabled (SSx<br>disabled                                                                                                                                                    |                              | Frame Sync pu    | ulse input/output  | )     |

|                                                 | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Frar                                                                                                                      | Plx support is<br>Plx support is<br>ne Sync Pulse                                                                                                                                                                     | enabled (SSx<br>disabled<br>Direction Cor                                                                                                                                   |                              | Frame Sync pu    | Ilse input/output  | )     |

|                                                 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Frar<br>1 = Frame Sy                                                                                                             | Plx support is<br>Plx support is                                                                                                                                                                                      | enabled (SSx<br>disabled<br>Direction Cor<br>(slave)                                                                                                                        |                              | Frame Sync pu    | ulse input/output  | )     |

| bit 14                                          | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Frar<br>1 = Frame Sy<br>0 = Frame Sy                                                                                      | Plx support is<br>Plx support is<br>ne Sync Pulse<br>nc pulse input                                                                                                                                                   | enabled ( <del>SSx</del><br>disabled<br>Direction Cor<br>(slave)<br>tt (master)                                                                                             |                              | Frame Sync pu    | ulse input/output  | )     |

| bit 14                                          | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Fram<br>1 = Frame Sy<br>0 = Frame Sy<br><b>FRMPOL:</b> Fra<br>1 = Frame Sy                                                | PIx support is<br>PIx support is<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act                                                                                             | enabled (SSx<br>disabled<br>Direction Cor<br>(slave)<br>It (master)<br>e Polarity bit<br>ive-high                                                                           |                              | Frame Sync pu    | ulse input/output  | )     |

| bit 14                                          | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Fram<br>1 = Frame Sy<br>0 = Frame Sy<br><b>FRMPOL:</b> Fra<br>1 = Frame Sy                                                | PIx support is<br>PIx support is<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls                                                                                                                | enabled (SSx<br>disabled<br>Direction Cor<br>(slave)<br>It (master)<br>e Polarity bit<br>ive-high                                                                           |                              | Frame Sync pu    | ulse input/output  | )     |

| bit 14<br>bit 13                                | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>0 = Frame Sy                                              | PIx support is<br>PIx support is<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act                                                                                             | enabled (SSx<br>disabled<br>Direction Cor<br>(slave)<br>It (master)<br>e Polarity bit<br>ive-high<br>ive-low                                                                |                              | Frame Sync pu    | ulse input/output  | )     |

| bit 15<br>bit 14<br>bit 13<br>bit 12-2<br>bit 1 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>0 = Frame Sy<br>Unimplemen                                | PIx support is<br>PIx support is<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act<br>nc pulse is act                                                                          | enabled (SSx<br>disabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit<br>ive-high<br>ive-low<br>0'                                                          | ntrol bit                    | Frame Sync pu    | Ilse input/output  | )     |

| bit 14<br>bit 13<br>bit 12-2                    | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>0 = Frame Sy<br>Unimplemen<br>FRMDLY: Fra<br>1 = Frame Sy | PIx support is<br>PIx support is<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act<br>nc pulse is act<br>ted: Read as '<br>me Sync Pulse<br>nc pulse coinci                    | enabled (SSx<br>disabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit<br>ive-high<br>ive-low<br>0'<br>e Edge Select<br>ides with first                      | trol bit<br>bit<br>bit clock | Frame Sync pu    | ulse input/output  | )     |

| bit 14<br>bit 13<br>bit 12-2                    | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>Unimplemen<br>FRMDLY: Fra<br>1 = Frame Sy<br>0 = Frame Sy | Plx support is<br>Plx support is<br>ne Sync Pulse<br>nc pulse input<br>nc pulse output<br>ame Sync Puls<br>nc pulse is act<br>nc pulse is act<br>ted: Read as '<br>me Sync Pulse<br>nc pulse coinci<br>nc pulse prece | enabled (SSx<br>disabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit<br>ive-high<br>ive-low<br>0'<br>e Edge Select<br>ides with first<br>edes first bit cl | trol bit<br>bit<br>bit clock |                  | ulse input/output  | )     |

#### REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

#### 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit<sup>TM</sup> (I<sup>2</sup>C<sup>TM</sup>)" (DS70195) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit<sup>TM</sup> ( $I^2C^{TM}$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addresses

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addresses

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

#### 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7-Bit and 10-Bit Addressing.

The I<sup>2</sup>C module can operate either as a slave or a master on an I<sup>2</sup>C bus.

The following types of  $I^2C$  operation are supported:

- I<sup>2</sup>C slave operation with 7-Bit Addressing

- I<sup>2</sup>C slave operation with 10-Bit Addressing

- I<sup>2</sup>C master operation with 7-Bit or 10-Bit Addressing

For details about the communication sequence in each of these modes, refer to the Microchip web site (www.microchip.com) for the latest *"dsPIC33/PIC24 Family Reference Manual"* sections.

### 17.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CxSTAT are read/write.

- I2CxRSR is the shift register used for shifting data

- I2CxRCV is the receive buffer and the register to which data bytes are written or from which data bytes are read

- I2CxTRN is the transmit register to which bytes are written during a transmit operation

- · I2CxADD register holds the slave address

- ADD10 status bit indicates 10-Bit Addressing mode

- I2CxBRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV and an interrupt pulse is generated.

#### 18.1 UART Helpful Tips

- In multi-node, direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 18.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en554109          |

#### 18.2.1 KEY RESOURCES

- "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33/PIC24 Family Reference Manual"* sections

- Development Tools

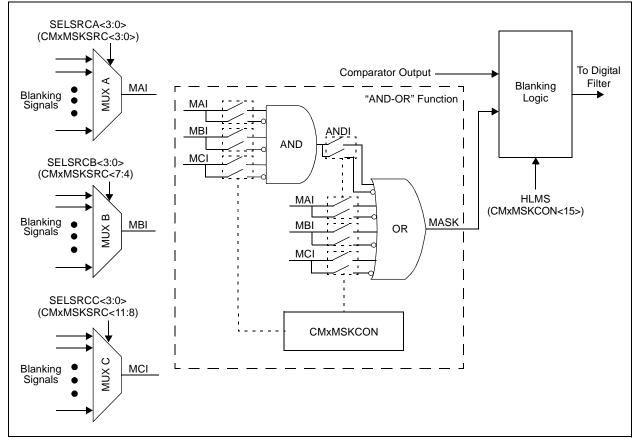

#### FIGURE 20-3: USER-PROGRAMMABLE BLANKING FUNCTION BLOCK DIAGRAM

#### 25.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 25.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 25.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 25.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 25.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

### dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

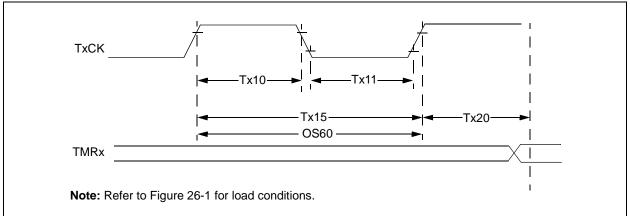

#### FIGURE 26-5: TIMER1/2/3 EXTERNAL CLOCK TIMING CHARACTERISTICS

#### Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) AC CHARACTERISTICS Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial -40°C $\leq$ TA $\leq$ +125°C for Extended Param Characteristic<sup>(2)</sup> Symbol Min Max Units Conditions Тур No. TA10 ТтхН T1CK High Synchronous Greater of: Must also meet ns Time mode 20 or Parameter TA15, (TCY + 20)/N N = prescale value (1, 8, 64, 256) Asynchronous 35 ns \_ \_\_\_\_ TA11 T1CK Low Must also meet TTXL Synchronous Greater of: ns Time mode 20 ns or Parameter TA15, (TCY + 20)/N N = prescale value (1, 8, 64, 256) Asynchronous 10 ns TA15 ΤτχΡ T1CK Input Synchronous Greater of: N = prescale value ns Period mode 40 or (1, 8, 64, 256) (2 TCY + 40)/N **OS60** Ft1 SOSC1/T1CK Oscillator DC 50 kHz \_\_\_\_ Input Frequency Range (oscillator enabled by setting the TCS (T1CON<1>) bit) TA20 TCKEXTMRL Delay from External T1CK 0.75 Tcy + 40 1.75 Tcy + 40 ns Clock Edge to Timer Increment

### TABLE 26-22: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

Note 1: Timer1 is a Type A.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

## TABLE 26-43:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ32(GP/MC)10X

| AC CHARACTERISTICS |                       |                                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                                      |  |

|--------------------|-----------------------|--------------------------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions                           |  |

| SP70               | TscP                  | Maximum SCKx Input Frequency                                 | —                                                     | _                  | 15  | MHz   | See Note 3                           |  |

| SP72               | TscF                  | SCKx Input Fall Time                                         | —                                                     |                    |     | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP73               | TscR                  | SCKx Input Rise Time                                         | —                                                     | _                  | —w  | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                   | _                                                     |                    | _   | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                   | _                                                     |                    | _   | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                     | 6                  | 20  | ns    |                                      |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                    | _                  | _   | ns    |                                      |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                    |                    |     | ns    |                                      |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                    |                    |     | ns    |                                      |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                   | _                  | _   | ns    |                                      |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10                                                    | —                  | 50  | ns    | See Note 4                           |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 Tcy + 40                                          | —                  |     | ns    | See Note 4                           |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCKx clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

#### 27.1 High-Temperature DC Characteristics

#### TABLE 27-1: OPERATING MIPS VS. VOLTAGE

|                | VDD Range                  | Temperature Range | Max MIPS                                                       |  |

|----------------|----------------------------|-------------------|----------------------------------------------------------------|--|

| Characteristic | (in Volts)                 | (in °C)           | dsPIC33FJ16(GP/MC)101/102 and<br>dsPIC33FJ32(GP/MC)101/102/104 |  |

| HDC5           | Vbor – 3.6V <sup>(1)</sup> | -40°C to +150°C   | 5                                                              |  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules, such as the ADC, etc., may have degraded performances below VDDMIN.

#### TABLE 27-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min           | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-----|------|------|

| High Temperature Devices                                                                                                                                                               |        |               |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40           | —   | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40           | —   | +150 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | PINT + PI/O   |     |      | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | PDMAX  | (TJ — TA)/θJA |     |      | W    |

#### TABLE 27-3: DC CHARACTERISTICS: OPERATING CURRENT (IDD))

| DC CHARACT                                              | ERISTICS |     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |             |                   |  |  |

|---------------------------------------------------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|--|--|

| Parameter<br>No.                                        | Typical  | Мах | Units                                                                                                                                                  | Conditions  |                   |  |  |

| Operating Current (IDD) – dsPIC33FJ16(GP/MC)10X Devices |          |     |                                                                                                                                                        |             |                   |  |  |