Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Active                                                                           |

| Core Processor            | dsPIC                                                                            |

| Core Size                 | 16-Bit                                                                           |

| Speed                     | 16 MIPs                                                                          |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals               | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O             | 21                                                                               |

| Program Memory Size       | 16KB (16K x 8)                                                                   |

| rogram Memory Type        | FLASH                                                                            |

| EEPROM Size               | -                                                                                |

| RAM Size                  | 1K x 8                                                                           |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Oata Converters           | A/D 6x10b                                                                        |

| Oscillator Type           | Internal                                                                         |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type             | Surface Mount                                                                    |

| Package / Case            | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package   | 28-QFN (6x6)                                                                     |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gp102t-i-ml |

PSV and Table Data Access Y Data Bus Control Block X Data Bus Interrupt **PORTA** Controller 16 16 16 16 Data Latch Data Latch 23 PCU PCH PCL Y RAM X RAM **PORTB** 23 Program Counter Address Address Loop Control Latch Latch Control Logic Logic 23 16 16 Remappable Address Generator Units Address Latch Program Memory EA MUX ROM Latch Data Latch 24 16 Instruction Decode and Control Instruction Reg 16 Control Signals **DSP** Engine to Various Blocks 16 x 16 OSC2/CLKO OSC1/CLKI Power-up W Register Array Timing Generation Divide Support Timer 16 Oscillator  $\boxtimes \longleftrightarrow$ FRC/LPRC Start-up Time Oscillators Power-on Reset 16-Bit ALU Precision Watchdog Band Gap Reference 16 Brown-out Voltage Regulator Reset  $\boxtimes$  $\boxtimes$  $\boxtimes$ VCAP VDD, VSS MCLR External OC/ Timers CTMU UART1 ADC1 RTCC Interrupts 1-5 PWM1-2 1-3 Comparators **PWM** IC1-IC3 I2C1 CNx 6-ch Not all pins or features are implemented on all device pinout configurations. See the "Pin Diagrams" section for the specific pins Note: and features present on each device.

FIGURE 1-1: dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 BLOCK DIAGRAM

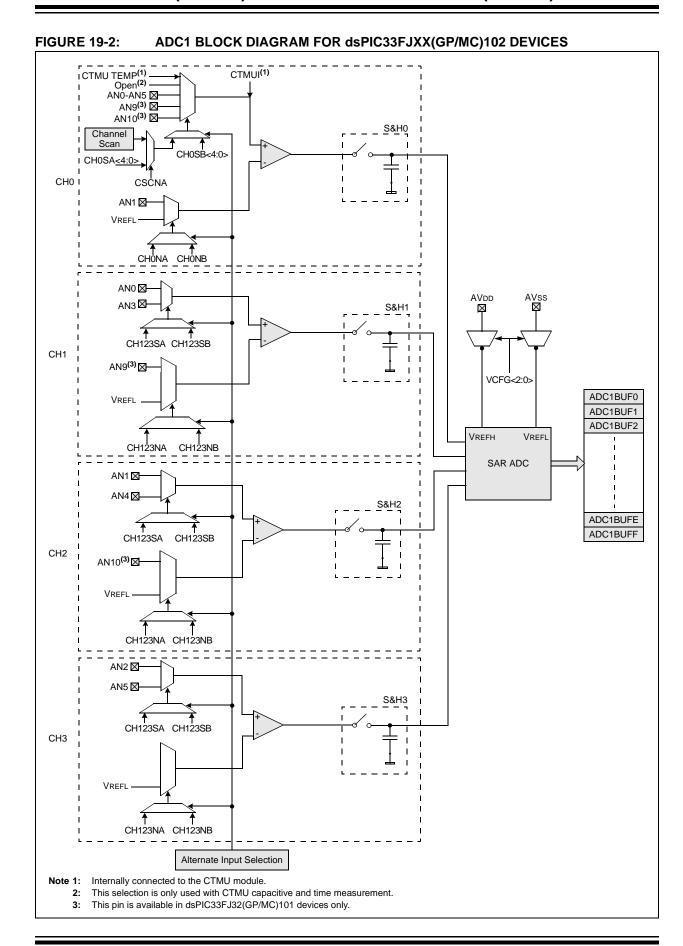

TABLE 4-17: ADC1 REGISTER MAP FOR dsPIC33FJ32(GP/MC)104 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12                                                                          | Bit 11               | Bit 10   | Bit 9    | Bit 8   | Bit 7        | Bit 6     | Bit 5 | Bit 4  | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

|-----------|-------------|--------|--------|--------|---------------------------------------------------------------------------------|----------------------|----------|----------|---------|--------------|-----------|-------|--------|--------|----------|----------|---------|---------------|

| ADC1BUF0  | 0300        |        |        | ·      |                                                                                 | <u> </u>             |          |          | ADC1 Da | ata Buffer   | 0         |       | II.    |        | l .      |          | ·       | xxxx          |

| ADC1BUF1  | 0302        |        |        |        |                                                                                 |                      |          |          | ADC1 Da | ata Buffer   | 1         |       |        |        |          |          |         | xxxx          |

| ADC1BUF2  | 0304        |        |        |        |                                                                                 |                      |          |          | ADC1 Da | ata Buffer   | 2         |       |        |        |          |          |         | xxxx          |

| ADC1BUF3  | 0306        |        |        |        |                                                                                 |                      |          |          | ADC1 Da | ata Buffer   | 3         |       |        |        |          |          |         | xxxx          |

| ADC1BUF4  | 0308        |        |        |        |                                                                                 |                      |          |          | ADC1 Da | ata Buffer   | 4         |       |        |        |          |          |         | xxxx          |

| ADC1BUF5  | 030A        |        |        |        |                                                                                 |                      |          |          | ADC1 Da | ata Buffer   | 5         |       |        |        |          |          |         | xxxx          |

| ADC1BUF6  | 030C        |        |        |        |                                                                                 | ADC1 Data Buffer 6   |          |          |         |              |           |       |        |        |          |          | xxxx    |               |

| ADC1BUF7  | 030E        |        |        |        |                                                                                 | ADC1 Data Buffer 7 x |          |          |         |              |           |       |        |        |          |          | xxxx    |               |

| ADC1BUF8  | 0310        |        |        |        |                                                                                 | ADC1 Data Buffer 8   |          |          |         |              |           |       |        |        |          |          | xxxx    |               |

| ADC1BUF9  | 0312        |        |        |        |                                                                                 |                      |          |          | ADC1 Da | ata Buffer   | 9         |       |        |        |          |          |         | xxxx          |

| ADC1BUFA  | 0314        |        |        |        |                                                                                 |                      |          |          | ADC1 Da | ıta Buffer 1 | 10        |       |        |        |          |          |         | xxxx          |

| ADC1BUFB  | 0316        |        |        |        |                                                                                 |                      |          |          | ADC1 Da | ıta Buffer 1 | 11        |       |        |        |          |          |         | xxxx          |

| ADC1BUFC  | 0318        |        |        |        |                                                                                 |                      |          |          | ADC1 Da | ıta Buffer 1 | 12        |       |        |        |          |          |         | xxxx          |

| ADC1BUFD  | 031A        |        |        |        |                                                                                 |                      |          |          | ADC1 Da | ıta Buffer 1 | 13        |       |        |        |          |          |         | xxxx          |

| ADC1BUFE  | 031C        |        |        |        |                                                                                 |                      |          |          | ADC1 Da | ıta Buffer 1 | 14        |       |        |        |          |          |         | xxxx          |

| ADC1BUFF  | 031E        |        |        |        |                                                                                 |                      |          |          | ADC1 Da | ıta Buffer 1 | 15        |       |        |        |          |          |         | xxxx          |

| AD1CON1   | 0320        | ADON   | _      | ADSIDL | _                                                                               | _                    | _        | FORM1    | FORM0   | SSRC2        | SSRC1     | SSRC0 | _      | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322        | VCFG2  | VCFG1  | VCFG0  | _                                                                               | _                    | CSCNA    | CHPS1    | CHPS0   | BUFS         | _         | SMPI3 | SMPI2  | SMPI1  | SMPI0    | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324        | ADRC   | _      | _      | SAMC4 SAMC3 SAMC2 SAMC1 SAMC0 ADCS7 ADCS6 ADCS5 ADCS4 ADCS3 ADCS2 ADCS1 ADCS0 0 |                      |          |          |         |              |           |       |        |        |          | 0000     |         |               |

| AD1CHS123 | 0326        | _      | _      | _      | _                                                                               | _                    | CH123NB1 | CH123NB0 | CH123SB | _            | -         | -     | _      | _      | CH123NA1 | CH123NA0 | CH123SA | 0000          |

| AD1CHS0   | 0328        | CH0NB  | _      | _      | CH0SB4                                                                          | CH0SB3               | CH0SB2   | CH0SB1   | CH0SB0  | CH0NA        | _         | _     | CH0SA4 | CH0SA3 | CH0SA2   | CH0SA1   | CH0SA0  | 0000          |

| AD1PCFGL  | 032C        | PCFG15 | _      | _      |                                                                                 |                      |          |          |         | F            | PCFG<12:0 | )>(1) |        |        |          |          |         | 0000          |

| AD1CSSL   | 0330        | CSS15  | _      | _      |                                                                                 |                      |          |          |         |              | CSS12:0>  | (1)   |        |        |          |          |         | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PCFG<10:9> and CSS<10:9> bits are available in dsPIC33FJ32(GP/MC)104 devices only.

#### TABLE 4-33: PORTB REGISTER MAP FOR dsPIC33FJ32GP101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8      | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|---------|--------|--------|--------|--------|-----------|------------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        | TRISB< | <15:14> | _      | -      | _      | _      |           | TRISB<9:7: | >     | _     | _     | TRISB4 | _     | _     | TRISE | 3<1:0> | C393          |

| PORTB     | 02CA        | RB<1   | 5:14>   | _      | -      | _      | _      |           | RB<9:7>    |       | _     | _     | RB4    | _     | _     | RB<   | 1:0>   | xxxx          |

| LATB      | 02CC        | LATB<  | 15:14>  | _      | -      | _      | _      | LATB<9:7> |            | _     | _     | LATB4 | _      | _     | LATB  | <1:0> | xxxx   |               |

| ODCB      | 02CE        | ODCB<  | <15:14> | _      | -      | _      | _      |           | ODCB<9:7:  | >     |       | _     |        | _     | _     |       | ı      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-34: PORTB REGISTER MAP FOR dsPIC33FJ32MC101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|--------|---------|--------|--------|--------|-------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        |        | TRISB< | <15:12> |        | _      | _      | -     | TRISB<9:7 | >     | _     | _     | TRISB4 | _     | _     | TRISE | 3<1:0> | F393          |

| PORTB     | 02CA        |        | RB<1   | 5:12>   |        | _      | _      |       | RB<9:7>   |       | _     | _     | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        |        | LATB<  | 15:12>  |        | _      | _      |       | LATB<9:7> | •     | _     | _     | LATB4  | _     | _     | LATB  | <1:0>  | xxxx          |

| ODCB      | 02CE        |        | ODCB<  | <15:12> |        | _      | _      | (     | ODCB<9:7  | >     | _     | _     | _      | _     | -     | _     | -      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-35: PORTB REGISTER MAP FOR dsPIC33FJ32(GP/MC)102 AND dsPIC33FJ32(GP/MC)104 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14      | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|-------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB        | 02C8        |        | TRISB<15:0> |        |        |        |        |       |       |       |       |       | FFFF  |       |       |       |       |               |

| PORTB        | 02CA        |        | RB<15:0>    |        |        |        |        |       |       |       |       |       | xxxx  |       |       |       |       |               |

| LATB         | 02CC        |        | LATB<15:0>  |        |        |        |        |       |       |       |       |       | xxxx  |       |       |       |       |               |

| ODCB         | 02CE        |        | ODCB<15:5>  |        |        |        |        |       |       |       |       |       | 0000  |       |       |       |       |               |

dsPlC33FJ16(GP/MC)101/102 AND dsPlC33FJ32(GP/MC)101/102/104

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-36: PORTC REGISTER MAP FOR dsPIC33FJ32(GP/MC)104 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-----------|-------|--------|-------|-------|--------|-------|-------|-------|-------|---------------|

| TRISC        | 02D0        | _      | _      | _      | _      | _      | _      |           |       |        |       | TRISC | C<9:0> |       |       |       |       | FFFF          |

| PORTC        | 02D2        | _      | _      | _      | _      | _      | _      |           |       |        |       | RC<   | 9:0>   |       |       |       |       | xxxx          |

| LATC         | 02D4        | _      | _      | _      | _      | _      | _      | LATC<9:0> |       |        |       |       |        |       | xxxx  |       |       |               |

| ODCC         | 02D6        | _      | _      | _      | _      | _      | _      |           | ODC   | C<9:6> |       | -     | _      | _     | _     | _     | 1     | 0000          |

$\textbf{Legend:} \ \ x = \text{unknown value on Reset,} \\ \ \ - = \text{unimplemented, read as '0'}. \\ \ \ \text{Reset values are shown in hexadecimal.}$

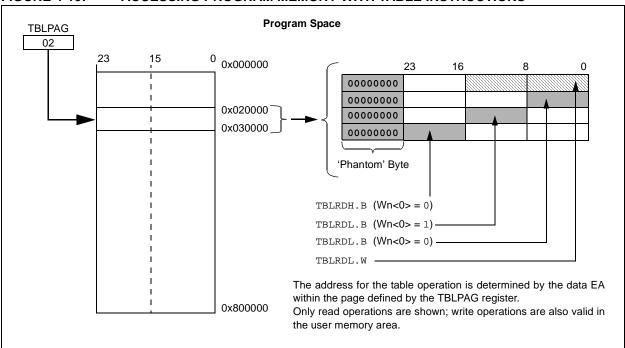

# 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte

of the lower program word is mapped to the

lower byte of a data address. The upper byte

is selected when Byte Select is '1'; the lower

byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0** "Flash **Program Memory**".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

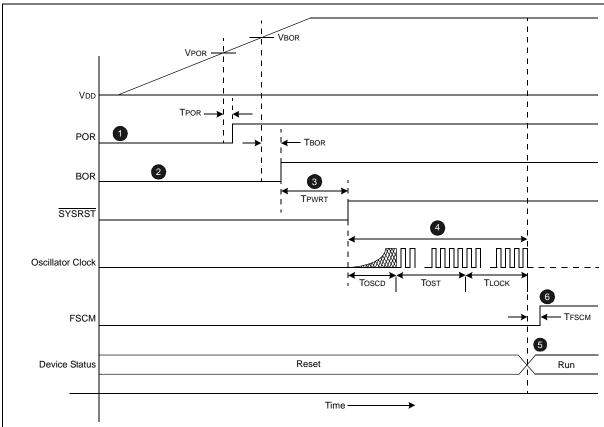

FIGURE 6-2: SYSTEM RESET TIMING

- POR: A POR circuit holds the device in Reset when the power supply is turned on. The POR circuit is active until VDD crosses the VPOR threshold and the delay, TPOR, has elapsed.

- BOR: The on-chip voltage regulator has a BOR circuit that keeps the device in Reset until VDD crosses the VBOR threshold and the delay, TBOR, has elapsed. The delay, TBOR, ensures the voltage regulator output becomes stable.

- 3. PWRT Timer: The Power-up Timer continues to hold the processor in Reset for a specific period of time (TPWRT) after a BOR. The delay, TPWRT, ensures that the system power supplies have stabilized at the appropriate level for full-speed operation. After the delay, TPWRT, has elapsed, the SYSRST becomes inactive, which in turn, enables the selected oscillator to start generating clock cycles.

- 4. Oscillator Delay: The total delay for the clock to be ready for various clock source selections is given in Table 6-1. Refer to Section 8.0 "Oscillator Configuration" for more information.

- 5. When the oscillator clock is ready, the processor begins execution from location, 0x000000. The user application programs a GOTO instruction at the Reset address, which redirects program execution to the appropriate start-up routine.

- The Fail-Safe Clock Monitor (FSCM), if enabled, begins to monitor the system clock when the system clock is ready and the delay, TFSCM, has elapsed.

Note:

TABLE 6-2: OSCILLATOR PARAMETERS

| Symbol | Parameter                        | Value          |

|--------|----------------------------------|----------------|

| VPOR   | POR Threshold                    | 1.8V nominal   |

| TPOR   | POR Extension Time               | 30 μs maximum  |

| VBOR   | BOR Threshold                    | 2.5V nominal   |

| TBOR   | BOR Extension Time               | 100 μs maximum |

| TPWRT  | Power-up Time<br>Delay           | 64 ms nominal  |

| TFSCM  | Fail-Safe Clock<br>Monitor Delay | 900 μs maximum |

When the device exits the Reset condition (begins normal operation), the device operating parameters (voltage, frequency, temperature, etc.) must be within their operating ranges; otherwise, the device may not function correctly. The user application must ensure that the delay between the time power is first applied, and the time SYSRST becomes inactive, is long enough to get all operating parameters within specification.

#### REGISTER 8-3: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| _     | _   |       |       | TUN   | l<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits

011111 = Maximum frequency deviation of 1.453% (7.477 MHz)

011110 = Center frequency + 1.406% (7.474 MHz)

•

•

•

000001 = Center frequency + 0.047% (7.373 MHz)

000000 = Center frequency (7.37 MHz nominal)

111111 = Center frequency – 0.047% (7.367 MHz)

•

•

100001 = Center frequency - 1.453% (7.263 MHz)

100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

#### REGISTER 9-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

bit 3 SPI1MD: SPI1 Module Disable bit

1 = SPI1 module is disabled 0 = SPI1 module is enabled

bit 2-1 **Unimplemented:** Read as '0'

bit 0 **AD1MD:** ADC1 Module Disable bit<sup>(2)</sup>

1 = ADC1 module is disabled 0 = ADC1 module is enabled

Note 1: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

2: PCFGx bits have no effect if the ADC module is disabled by setting this bit. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

#### REGISTER 9-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-------|-------|-------|

| _      | _   | _   | _   | _   | IC3MD | IC2MD | IC1MD |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | _   | _   | _   | OC2MD | OC1MD |

| bit 7 |     |     |     |     |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10 IC3MD: Input Capture 3 Module Disable bit

1 = Input Capture 3 module is disabled0 = Input Capture 3 module is enabled

bit 9 IC2MD: Input Capture 2 Module Disable bit

1 = Input Capture 2 module is disabled0 = Input Capture 2 module is enabled

bit 8 IC1MD: Input Capture 1 Module Disable bit

1 = Input Capture 1 module is disabled 0 = Input Capture 1 module is enabled

bit 7-2 **Unimplemented:** Read as '0'

bit 1 OC2MD: Output Compare 2 Module Disable bit

1 = Output Compare 2 module is disabled0 = Output Compare 2 module is enabled

bit 0 OC1MD: Output Compare 1 Module Disable bit

1 = Output Compare 1 module is disabled0 = Output Compare 1 module is enabled

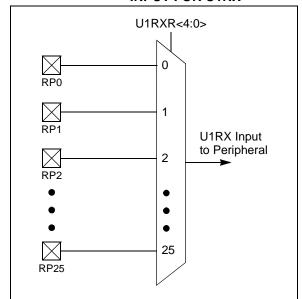

#### 10.4 Peripheral Pin Select (PPS)

Peripheral Pin Select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral Pin Select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

#### 10.4.1 AVAILABLE PINS

The Peripheral Pin Select feature is used with a range of up to 16 pins. The number of available pins depends on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

# 10.4.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of Special Function Registers: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 10.4.2.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-10). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

Figure 10-2 Illustrates remappable pin selection for U1RX input.

Note:

For input mapping only, the Peripheral Pin Select (PPS) functionality does not have priority over the TRISx settings. Therefore, when configuring the RPx pin for input, the corresponding bit in the TRISx register must also be configured for input (i.e., set to '1').

FIGURE 10-2: REMAPPABLE MUX INPUT FOR U1RX

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0    | R/W-0  | R/W-0    | U-0 | R/W-0, HC | R/W-0                | R-0   | R-1   |

|----------|--------|----------|-----|-----------|----------------------|-------|-------|

| UTXISEL1 | UTXINV | UTXISEL0 | _   | UTXBRK    | UTXEN <sup>(1)</sup> | UTXBF | TRMT  |

| bit 15   |        |          |     |           |                      |       | bit 8 |

| R/W-0    | R/W-0    | R/W-0 | R-1   | R-0  | R-0  | R/C-0 | R-0   |

|----------|----------|-------|-------|------|------|-------|-------|

| URXISEL1 | URXISEL0 | ADDEN | RIDLE | PERR | FERR | OERR  | URXDA |

| bit 7    |          |       |       |      |      |       | bit 0 |

| Legend:           | C = Clearable bit | HC = Hardware Clearable bit        |                    |  |

|-------------------|-------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |

- bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx Transmit Polarity Inversion bit

#### If IREN = 0:

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

#### <u>If IREN = 1:</u>

- 1 = IrDA encoded, UxTX Idle state is '1'

- 0 = IrDA encoded, UxTX Idle state is '0'

- bit 12 **Unimplemented:** Read as '0'

- bit 11 UTXBRK: UARTx Transmit Break bit

- 1 = Sends Sync Break on next transmission Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Sync Break transmission is disabled or completed

- bit 10 UTXEN: UARTx Transmit Enable bit<sup>(1)</sup>

- 1 = Transmit is enabled, UxTX pin is controlled by UARTx

- 0 = Transmit is disabled, any pending transmission is aborted and the buffer is reset; UxTX pin is controlled by port

- bit 9 UTXBF: UARTx Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 **TRMT:** Transmit Shift Register Empty bit (read-only)

- 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit Shift Register is not empty, a transmission is in progress or queued

- bit 7-6 URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits

- 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)

- 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)

- 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters

- Note 1: Refer to "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UART module for transmit operation.

#### REGISTER 19-3: AD1CON3: ADC1 CONTROL REGISTER 3

| R/W-0  | U-0 | U-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|--------|-----|-----|----------------------|----------------------|----------------------|----------------------|----------------------|

| ADRC   | _   | _   | SAMC4 <sup>(1)</sup> | SAMC3 <sup>(1)</sup> | SAMC2 <sup>(1)</sup> | SAMC1 <sup>(1)</sup> | SAMC0 <sup>(1)</sup> |

| bit 15 |     |     |                      |                      |                      |                      | bit 8                |

| R/W-0                |

|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| ADCS7 <sup>(2)</sup> | ADCS6 <sup>(2)</sup> | ADCS5 <sup>(2)</sup> | ADCS4 <sup>(2)</sup> | ADCS3 <sup>(2)</sup> | ADCS2 <sup>(2)</sup> | ADCS1 <sup>(2)</sup> | ADCS0 <sup>(2)</sup> |

| bit 7                |                      |                      |                      |                      |                      |                      | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 ADRC: ADC1 Conversion Clock Source bit

1 = ADC1 internal RC clock

0 = Clock derived from system clock

bit 14-13 Unimplemented: Read as '0'

SAMC<4:0>: Auto-Sample Time bits(1) bit 12-8

11111 = 31 TAD

00001 = 1 TAD00000 = 0 TAD

ADCS<7:0>: ADC1 Conversion Clock Select bits(2) bit 7-0

11111111 = Reserved

01000000 = Reserved

$001111111 = TCY \cdot (ADCS < 7:0 > + 1) = 64 \cdot TCY = TAD$

$00000010 = TCY \cdot (ADCS < 7:0 > + 1) = 3 \cdot TCY = TAD$  $00000001 = Tcy \cdot (ADCS < 7:0 > + 1) = 2 \cdot Tcy = TAD$

$000000000 = Tcy \cdot (ADCS < 7:0 > + 1) = 1 \cdot Tcy = TAD$

**Note 1:** This bit is only used if SSRC<2:0> (AD1CON1<7:5>) = 1.

2: This bit is not used if ADRC (AD1CON3<15>) = 1.

#### 20.1 Comparator Control Registers

#### REGISTER 20-1: CMSTAT: COMPARATOR STATUS REGISTER

| R/W-0  | U-0 | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   |

|--------|-----|-----|-----|-----|-------|-------|-------|

| CMSIDL | _   | _   | _   | _   | C3EVT | C2EVT | C1EVT |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   |

|-------|-----|-----|-----|-----|-------|-------|-------|

| _     | _   | _   | _   | _   | C3OUT | C2OUT | C1OUT |

| bit 7 |     |     |     |     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CMSIDL: Comparator Stop in Idle Mode bit

1 = Discontinues operation of all comparators when device enters Idle mode

0 = Continues operation of all comparators in Idle mode

bit 14-11 Unimplemented: Read as '0'

bit 10 C3EVT: Comparator 3 Event Status bit

1 = Comparator event occurred 0 = Comparator event did not occur

bit 9 **C2EVT:** Comparator 2 Event Status bit

1 = Comparator event occurred

0 = Comparator event did not occur

bit 8 C1EVT: Comparator 1 Event Status bit

1 = Comparator event occurred0 = Comparator event did not occur

bit 7-3 **Unimplemented:** Read as '0'

bit 2 C3OUT: Comparator 3 Output Status bit

When CPOL = 0: 1 = VIN+ > VIN- 0 = VIN+ < VIN-When CPOL = 1: 1 = VIN+ < VIN-

0 = VIN+ > VIN-

bit 1 C2OUT: Comparator 2 Output Status bit

When CPOL = 0: 1 = VIN+ > VIN-0 = VIN+ < VIN-When CPOL = 1: 1 = VIN+ < VIN-0 = VIN+ > VIN-

bit 0 C10UT: Comparator 1 Output Status bit

When CPOL = 0: 1 = VIN+ > VIN-0 = VIN+ < VIN-When CPOL = 1: 1 = VIN+ < VIN-0 = VIN+ > VIN-

#### REGISTER 20-2: CMxCON: COMPARATOR x CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-----|-----|-----|-------|-------|

| CON    | COE   | CPOL  | _   | _   | _   | CEVT  | COUT  |

| bit 15 |       |       |     |     |     |       | bit 8 |

| R/W-0  | R/W-0  | U-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|--------|-----|-------|-----|-----|-------|-------|

| EVPOL1 | EVPOL0 | _   | CREF  | _   | _   | CCH1  | CCH0  |

| bit 7  |        |     |       |     |     |       | bit 0 |

Legend:

W = Writable bit R = Readable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **CON:** Comparator x Enable bit

> 1 = Comparator x is enabled 0 = Comparator x is disabled

bit 14 **COE:** Comparator x Output Enable bit

1 = Comparator output is present on the CxOUT pin

0 = Comparator output is internal only

bit 13 **CPOL:** Comparator x Output Polarity Select bit

> 1 = Comparator x output is inverted 0 = Comparator x output is not inverted

Unimplemented: Read as '0'

bit 12-10 bit 9 **CEVT:** Comparator x Event bit

> 1 = Comparator x event according to EVPOL<1:0> settings occurred; disables future triggers and interrupts until the bit is cleared

0 = Comparator x event did not occur

bit 8 **COUT:** Comparator x Output bit

When CPOL = 0 (non-inverted polarity):

1 = VIN+ > VIN-0 = VIN+ < VIN-

When CPOL = 1 (inverted polarity):

1 = VIN+ < VIN-0 = VIN+ > VIN-

bit 7-6 EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits

11 = Trigger/event/interrupt is generated on any change of the comparator output (while CEVT = 0)

10 = Trigger/event/interrupt is generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

Low-to-high transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

High-to-low transition of the comparator output.

01 = Trigger/event/interrupt is generated only on low-to-high transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

Low-to-high transition of the comparator output. 00 = Trigger/event/interrupt generation is disabled

bit 5 Unimplemented: Read as '0'

#### 21.2 RTCC Control Registers

#### REGISTER 21-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

| R/W-0                | U-0 | R/W-0   | R-0     | R-0                    | R/W-0 | R/W-0   | R/W-0   |

|----------------------|-----|---------|---------|------------------------|-------|---------|---------|

| RTCEN <sup>(2)</sup> | _   | RTCWREN | RTCSYNC | HALFSEC <sup>(3)</sup> | RTCOE | RTCPTR1 | RTCPTR0 |

| bit 15               |     |         |         |                        |       |         | bit 8   |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CAL7  | CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

RTCEN: RTCC Enable bit(2)

1 = RTCC module is enabled0 = RTCC module is disabled

bit 14 Unimplemented: Read as '0'

bit 15

bit 13 RTCWREN: RTCC Value Registers Write Enable bit

1 = RTCVALH and RTCVALL registers can be written to by the user

0 = RTCVALH and RTCVALL registers are locked out from being written to by the user

bit 12 RTCSYNC: RTCC Value Registers Read Synchronization bit

1 = RTCVALH, RTCVALL and ALCFGRPT registers can change while reading, due to a rollover ripple, resulting in an invalid data read. If the register is read twice and the results are the same data, the data can be assumed to be valid.

0 = RTCVALH, RTCVALL or ALCFGRPT registers can be read without concern over a rollover ripple

bit 11 HALFSEC: Half-Second Status bit (3)

1 = Second half period of a second

0 = First half period of a second

bit 10 RTCOE: RTCC Output Enable bit

1 = RTCC output is enabled

0 = RTCC output is disabled

bit 9-8 RTCPTR<1:0>: RTCC Value Register Window Pointer bits

Points to the corresponding RTCC Value registers when reading RTCVALH and RTCVALL registers; the RTCPTR<1:0> value decrements on every read or write of RTCVALH until it reaches '00'.

RTCVAL<15:8>:

00 = MINUTES

01 = WEEKDAY

10 = MONTH

11 = Reserved

RTCVAL<7:0>:

00 = SECONDS

01 = HOURS

10 = DAY

11 = YEAR

Note 1: The RCFGCAL register is only affected by a POR.

- **2:** A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

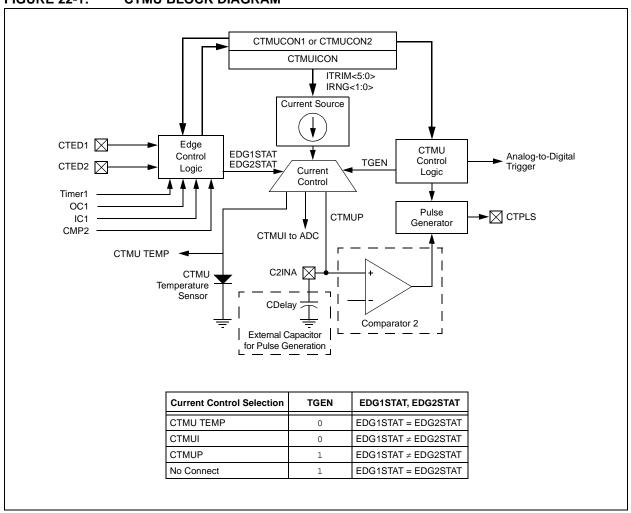

#### FIGURE 22-1: CTMU BLOCK DIAGRAM

TABLE 26-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACT       | DC CHARACTERISTICS  Parameter (1) |            |             | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |       |                                     |  |  |

|------------------|-----------------------------------|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup>            | Max        | Units       | Conditions                                                                                                                                                                                                                                       |       |                                     |  |  |

| Operating Cur    | rent (IDD) <sup>(2)</sup> –       | dsPIC33FJ1 | 6(GP/MC)10X | Devices                                                                                                                                                                                                                                          |       |                                     |  |  |

| DC20d            | 0.7                               | 1.7        | mA          | -40°C                                                                                                                                                                                                                                            |       |                                     |  |  |

| DC20a            | 0.7                               | 1.7        | mA          | +25°C                                                                                                                                                                                                                                            | 3.3V  | LPRC<br>(32.768 kHz) <sup>(3)</sup> |  |  |

| DC20b            | 1.0                               | 1.7        | mA          | +85°C                                                                                                                                                                                                                                            | 3.3V  |                                     |  |  |

| DC20c            | 1.3                               | 1.7        | mA          | +125°C                                                                                                                                                                                                                                           |       |                                     |  |  |

| DC21d            | 1.9                               | 2.6        | mA          | -40°C                                                                                                                                                                                                                                            | 3.3V  |                                     |  |  |

| DC21a            | 1.9                               | 2.6        | mA          | +25°C                                                                                                                                                                                                                                            |       | 1 MIPS <sup>(3)</sup>               |  |  |

| DC21b            | 1.9                               | 2.6        | mA          | +85°C                                                                                                                                                                                                                                            |       | I WIPS(*)                           |  |  |

| DC21c            | 2.0                               | 2.6        | mA          | +125°C                                                                                                                                                                                                                                           |       |                                     |  |  |

| DC22d            | 6.5                               | 8.5        | mA          | -40°C                                                                                                                                                                                                                                            |       | 4 MIPS <sup>(3)</sup>               |  |  |

| DC22a            | 6.5                               | 8.5        | mA          | +25°C                                                                                                                                                                                                                                            | 3.3V  |                                     |  |  |

| DC22b            | 6.5                               | 8.5        | mA          | +85°C                                                                                                                                                                                                                                            | 3.3V  | 4 101115007                         |  |  |

| DC22c            | 6.5                               | 8.5        | mA          | +125°C                                                                                                                                                                                                                                           |       |                                     |  |  |

| DC23d            | 12.2                              | 16         | mA          | -40°C                                                                                                                                                                                                                                            |       |                                     |  |  |

| DC23a            | 12.2                              | 16         | mA          | +25°C                                                                                                                                                                                                                                            | 3.3V  | 10 MIPS <sup>(3)</sup>              |  |  |

| DC23b            | 12.2                              | 16         | mA          | +85°C                                                                                                                                                                                                                                            | 3.31  | 10 MIPS                             |  |  |

| DC23c            | 12.2                              | 16         | mA          | +125°C                                                                                                                                                                                                                                           |       |                                     |  |  |

| DC24d            | 16                                | 21         | mA          | -40°C                                                                                                                                                                                                                                            |       |                                     |  |  |

| DC24a            | 16                                | 21         | mA          | +25°C                                                                                                                                                                                                                                            | 2 2\/ | 16 MIDS                             |  |  |

| DC24b            | 16                                | 21         | mA          | +85°C                                                                                                                                                                                                                                            | 3.3V  | 16 MIPS                             |  |  |

| DC24c            | 16                                | 21         | mA          | +125°C                                                                                                                                                                                                                                           |       |                                     |  |  |

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- 2: IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

- · Oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (PMDx bits are all zeroed)

- CPU executing while (1) statement

- 3: These parameters are characterized, but not tested in manufacturing.

TABLE 26-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACTERISTICS                                                                                   |                        |     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |            |      |                                     |  |  |  |  |

|------------------------------------------------------------------------------------------------------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-------------------------------------|--|--|--|--|

| Parameter<br>No.                                                                                     | Typical <sup>(1)</sup> | Max | Units                                                                                                                                                                                                                                            | Conditions |      |                                     |  |  |  |  |

| Idle Current (IIDLE): Core Off, Clock On Base Current <sup>(2)</sup> – dsPIC33FJ16(GP/MC)10X Devices |                        |     |                                                                                                                                                                                                                                                  |            |      |                                     |  |  |  |  |

| DC40d                                                                                                | 0.4                    | 1.0 | mA                                                                                                                                                                                                                                               | -40°C      |      |                                     |  |  |  |  |

| DC40a                                                                                                | 0.4                    | 1.0 | mA                                                                                                                                                                                                                                               | +25°C      | 3.3V | LPRC<br>(32.768 kHz) <sup>(3)</sup> |  |  |  |  |

| DC40b                                                                                                | 0.4                    | 1.0 | mA                                                                                                                                                                                                                                               | +85°C      |      |                                     |  |  |  |  |

| DC40c                                                                                                | 0.5                    | 1.0 | mA                                                                                                                                                                                                                                               | +125°C     |      |                                     |  |  |  |  |

| DC41d                                                                                                | 0.5                    | 1.1 | mA                                                                                                                                                                                                                                               | -40°C      | 3.3V | 1 MIPS <sup>(3)</sup>               |  |  |  |  |

| DC41a                                                                                                | 0.5                    | 1.1 | mA                                                                                                                                                                                                                                               | +25°C      |      |                                     |  |  |  |  |

| DC41b                                                                                                | 0.5                    | 1.1 | mA                                                                                                                                                                                                                                               | +85°C      |      |                                     |  |  |  |  |

| DC41c                                                                                                | 0.8                    | 1.1 | mA                                                                                                                                                                                                                                               | +125°C     |      |                                     |  |  |  |  |

| DC42d                                                                                                | 0.9                    | 1.6 | mA                                                                                                                                                                                                                                               | -40°C      | 3.3V | 4 MIPS <sup>(3)</sup>               |  |  |  |  |

| DC42a                                                                                                | 0.9                    | 1.6 | mA                                                                                                                                                                                                                                               | +25°C      |      |                                     |  |  |  |  |

| DC42b                                                                                                | 1.0                    | 1.6 | mA                                                                                                                                                                                                                                               | +85°C      |      |                                     |  |  |  |  |

| DC42c                                                                                                | 1.2                    | 1.6 | mA                                                                                                                                                                                                                                               | +125°C     |      |                                     |  |  |  |  |

| DC43a                                                                                                | 1.6                    | 2.6 | mA                                                                                                                                                                                                                                               | +25°C      | 3.3V | 10 MIPS <sup>(3)</sup>              |  |  |  |  |

| DC43d                                                                                                | 1.6                    | 2.6 | mA                                                                                                                                                                                                                                               | -40°C      |      |                                     |  |  |  |  |

| DC43b                                                                                                | 1.7                    | 2.6 | mA                                                                                                                                                                                                                                               | +85°C      |      |                                     |  |  |  |  |

| DC43c                                                                                                | 2                      | 2.6 | mA                                                                                                                                                                                                                                               | +125°C     |      |                                     |  |  |  |  |

| DC44d                                                                                                | 2.4                    | 3.8 | mA                                                                                                                                                                                                                                               | -40°C      |      |                                     |  |  |  |  |

| DC44a                                                                                                | 2.4                    | 3.8 | mA                                                                                                                                                                                                                                               | +25°C      | 3.3V | 16 MIPS <sup>(3)</sup>              |  |  |  |  |

| DC44b                                                                                                | 2.6                    | 3.8 | mA                                                                                                                                                                                                                                               | +85°C      |      |                                     |  |  |  |  |

| DC44c                                                                                                | 2.9                    | 3.8 | mA                                                                                                                                                                                                                                               | +125°C     |      |                                     |  |  |  |  |

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- 2: Base Idle current is measured as follows:

- CPU core is off, oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- External Secondary Oscillator (SOSC) is disabled (i.e., SOSCO and SOSCI pins are configured as digital I/O inputs)

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (PMDx bits are all zeroed)

- 3: These parameters are characterized, but not tested in manufacturing.

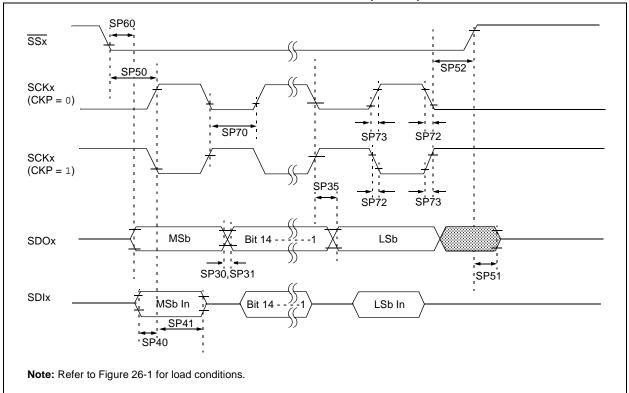

FIGURE 26-15: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ16(GP/MC)10X

| DC Characteristics                          | 282 | Н                                                  |     |

|---------------------------------------------|-----|----------------------------------------------------|-----|

| Brown-out Reset (BOR)                       | 283 | High-Temperature Electrical Characteristics        | 339 |

| Doze Current (IDOZE)289,                    |     | -                                                  | 000 |

| High Temperature                            |     |                                                    |     |

| I/O Pin Input Specifications                | 290 | I/O Ports                                          | 139 |

| I/O Pin Output Specifications               | 292 | Configuring Analog Port Pins                       |     |

| Idle Current (IIDLE)286,                    | 341 | Open-Drain Configuration                           |     |

| Operating Current (IDD)284, 340,            | 341 | Parallel I/O (PIO)                                 |     |

| Operating MIPS vs. Voltage282,              | 340 | Write/Read Timing                                  |     |

| Power-Down Current (IPD)288,                | 341 | I <sup>2</sup> C                                   |     |

| Program Memory                              | 293 | Control Registers                                  | 205 |

| Temperature and Voltage Specifications      | 283 | Operating Modes                                    |     |

| Thermal Operating Conditions282,            | 340 | Registers                                          |     |

| Thermal Packaging                           | 282 | In-Circuit Debugger                                |     |

| Development Support                         | 277 | In-Circuit Serial Programming (ICSP)               |     |

| Assembler                                   |     | Input Capture                                      |     |

| MPASM Assembler                             | 278 | Control Register                                   |     |

| C Compilers                                 |     | Input Change Notification (ICN)                    |     |

| MPLAB XC                                    | 278 | Instruction Addressing Modes                       |     |

| Demonstration/Development Boards            | 280 | File Register Instructions                         |     |

| Evaluation and Starter Kits                 | 280 | Fundamental Modes Supported                        |     |

| MPLAB Assembler, Linker, Librarian          | 278 | MAC Instructions                                   |     |

| MPLAB ICD 3 In-Circuit Debugger System      | 279 | MCU Instructions                                   |     |

| MPLAB PM3 Device Programmer                 | 279 | Move and Accumulator Instructions                  |     |

| MPLAB REAL ICE In-Circuit Emulator System   | 279 | Other Instructions                                 |     |

| MPLAB X Integrated Development              |     | Instruction Set                                    |     |

| Environment Software                        | 277 | matruction oct                                     |     |

| MPLINK Object Linker/MPLIB Object Librarian | 278 | Summary                                            | 260 |

| PICkit 3 In-Circuit Debugger/Programmer     | 279 | Overview                                           |     |

| Software Simulator (MPLAB X SIM)            |     | Symbols Used in Opcode Descriptions                |     |

| Third-Party Development Tools               |     | Instruction-Based Power-Saving Modes               |     |

| Doze Mode                                   | 134 | Idle                                               |     |

| dsPIC33FJ16(GP/MC)101/102                   |     | Sleep                                              |     |

| Device Features                             | 2   | Internet Address                                   |     |

| dsPIC33FJ32(GP/MC)101/102/104               |     | Interrupt Controller                               |     |

| Device Features                             | 3   | Interrupt Registers                                |     |

| F                                           |     | IECx                                               | Q.  |

| E                                           |     | IFSx                                               |     |

| Electrical Characteristics                  | 281 | INTCON1                                            |     |

| Equations                                   |     | INTCON2                                            |     |

| Device Operating Frequency                  | 126 | INTTREG                                            |     |

| Flash Programming Time                      | 84  | IPCx                                               |     |

| Maximum Row Write Time                      |     | Interrupt Setup Procedures                         |     |

| Minimum Row Write Time                      | 84  | Initialization                                     |     |

| MS with PLL Mode                            | 127 | Interrupt Disable                                  |     |

| Errata                                      | 24  | Interrupt Service Routine (ISR)                    |     |

| F                                           |     | Trap Service Routine (TSR)                         |     |

| Г                                           |     | Interrupt Vectors                                  |     |

| Flash Program Memory                        | 83  | Reset Sequence                                     |     |

| Control Registers                           |     | Interrupt Vector Table (IVT)                       |     |

| Operations                                  | 84  | Interrupts Coincident with Power Save Instructions |     |

| Programming Algorithm                       | 84  | interrupts confederit with rower cave instructions | 10- |

| RTSP Operation                              | 84  | L                                                  |     |

| Table Instructions                          | 83  | LPRC Oscillator                                    |     |

| G                                           |     | Use with WDT                                       | 267 |

|                                             |     |                                                    | =0. |

| Getting Started with 16-Bit DSCs            | 33  | M                                                  |     |

| Analog and Digital Pins Configuration       |     | Memory Organization                                | 49  |

| During ICSP                                 |     | Microchip Internet Web Site                        |     |

| Connection Requirements                     |     | Modulo Addressing                                  |     |

| Decoupling Capacitors                       |     | Applicability                                      |     |

| External Oscillator Pins                    |     | Operation Example                                  |     |

| ICSP Pins                                   |     | Start and End Address                              |     |

| Master Clear (MCLR) Pin                     |     | W Address Register Selection                       |     |

| Oscillator Value Conditions on Start-up     |     |                                                    |     |

| Unused I/Os                                 | 36  |                                                    |     |

| ALCFGRPT (Alarm Configuration)             | 248  | PMD3 (Peripheral Module Disable Control 3) | . 137 |

|--------------------------------------------|------|--------------------------------------------|-------|

| ALRMVAL (Alarm Minutes and Seconds Value,  |      | PMD4 (Peripheral Module Disable Control 4) | . 137 |

| ALRMPTR Bits = 00)                         | 254  | PWMxCON1 (PWMx Control 1)                  | . 188 |

| ALRMVAL (Alarm Month and Day Value,        |      | PWMxCON2 (PWMx Control 2)                  | . 189 |

| ALRMPTR Bits = 10)                         | 252  | PWMxKEY (PWMx Unlock)                      | . 196 |

| ALRMVAL (Alarm Weekday and Hours Value,    |      | PxDC1 (PWMx Duty Cycle 1)                  | 195   |

| ALRMPTR Bits = 01)                         | 253  | PxDC2 (PWMx Duty Cycle 2)                  |       |

| CLKDIV (Clock Divisor)                     |      | PxDC3 (PWMx Duty Cycle 3)                  |       |

| CMSTAT (Comparator Status)                 |      | PxDTCON1 (PWMx Dead-Time Control 1)        |       |

| CMxCON (Comparator x Control)              |      | PxDTCON2 (PWMx Dead-Time Control 2)        |       |

| CMxFLTR (Comparator x Filter Control)      |      | PxFLTACON (PWMx Fault A Control)           |       |

| CMxMSKCON (Comparator x Mask               | 2-71 | PxFLTBCON (PWMx Fault B Control)           |       |

| Gating Control)                            | 230  | PxOVDCON (PWMx Override Control)           |       |

| CMxMSKSRC (Comparator x Mask               | 200  | PxSECMP (PWMx Special Event Compare)       |       |

| · •                                        | 227  | ,                                          |       |

| Source Select)                             |      | PxTCON (PWMx Timer Count Value)            |       |

| CORCON (Core Control)                      |      | PxTMR (PWMx Timer Count Value)             |       |

| CTMUCON1 (CTMU Control 1)                  |      | PxTPER (PWMx Time Base Period)             | . 100 |

| CTMUCON2 (CTMU Control 2)                  |      | RCFGCAL (RTCC Calibration                  | 0.45  |

| CTMUICON (CTMU Current Control)            | 259  | and Configuration)                         |       |

| CVRCON (Comparator Voltage                 |      | RCON (Reset Control)                       |       |

| Reference Control)                         |      | RPINR0 (Peripheral Pin Select Input 0)     |       |

| DEVID (Device ID)                          |      | RPINR1 (Peripheral Pin Select Input 1)     |       |

| DEVREV (Device Revision)                   |      | RPINR11 (Peripheral Pin Select Input 11)   |       |

| I2CxCON (I2Cx Control)                     |      | RPINR18 (Peripheral Pin Select Input 18)   |       |

| I2CxMSK (I2Cx Slave Mode Address Mask)     |      | RPINR20 (Peripheral Pin Select Input 20)   |       |

| I2CxSTAT (I2Cx Status)                     | 207  | RPINR21 (Peripheral Pin Select Input 21)   | . 156 |

| ICxCON (Input Capture x Control)           |      | RPINR3 (Peripheral Pin Select Input 3)     |       |

| IEC0 (Interrupt Enable Control 0)          |      | RPINR4 (Peripheral Pin Select Input 4)     | . 150 |

| IEC1 (Interrupt Enable Control 1)          | 109  | RPINR7 (Peripheral Pin Select Input 7)     | . 151 |

| IEC2 (Interrupt Enable Control 2)          | 110  | RPINR8 (Peripheral Pin Select Input 8)     | . 152 |

| IEC3 (Interrupt Enable Control 3)          | 110  | RPOR0 (Peripheral Pin Select Output 0)     | . 157 |

| IEC4 (Interrupt Enable Control 4)          | 111  | RPOR1 (Peripheral Pin Select Output 1)     | . 157 |

| IFS0 (Interrupt Flag Status 0)             |      | RPOR10 (Peripheral Pin Select Output 10)   | . 162 |

| IFS1 (Interrupt Flag Status 1)             |      | RPOR11 (Peripheral Pin Select Output 11)   | . 162 |

| IFS2 (Interrupt Flag Status 2)             |      | RPOR12 (Peripheral Pin Select Output 12)   | . 163 |

| IFS3 (Interrupt Flag Status 3)             |      | RPOR2 (Peripheral Pin Select Output 2)     | . 158 |

| IFS4 (Interrupt Flag Status 4)             |      | RPOR3 (Peripheral Pin Select Output 3)     |       |

| INTCON1 (Interrupt Control 1)              |      | RPOR4 (Peripheral Pin Select Output 4)     |       |

| INTCON2 (Interrupt Control 2)              |      | RPOR5 (Peripheral Pin Select Output 5)     |       |

| INTTREG (Interrupt Control and Status)     |      | RPOR6 (Peripheral Pin Select Output 6)     |       |

| IPC0 (Interrupt Priority Control 0)        |      | RPOR7 (Peripheral Pin Select Output 7)     |       |

| IPC1 (Interrupt Priority Control 1)        |      | RPOR8 (Peripheral Pin Select Output 8)     |       |

| IPC14 (Interrupt Priority Control 14)      |      | RPOR9 (Peripheral Pin Select Output 9)     |       |

| IPC15 (Interrupt Priority Control 15)      |      | RTCVAL (RTCC Minutes and Seconds Value,    |       |

| IPC16 (Interrupt Priority Control 16)      |      | RTCPTR Bits = 00)                          | 251   |

| IPC19 (Interrupt Priority Control 19)      |      | RTCVAL (RTCC Month and Day Value,          | . 201 |

| IPC2 (Interrupt Priority Control 2)        |      | RTCPTR Bits = 10)                          | 2/10  |

| IPC3 (Interrupt Priority Control 3)        |      | RTCVAL (RTCC Weekdays and Hours Value,     | . 243 |

| IPC4 (Interrupt Priority Control 4)        |      | RTCPTR Bits = 01)                          | 250   |

| · · · · · · · · · · · · · · · · · · ·      |      | •                                          | . 250 |

| IPC5 (Interrupt Priority Control 5)        |      | RTCVAL (RTCC Year Value,                   | 040   |

| IPC6 (Interrupt Priority Control 6)        |      | RTCPTR Bits = 11)                          |       |

| IPC7 (Interrupt Priority Control 7)        |      | SPIxCON1 (SPIx Control 1)                  |       |

| IPC9 (Interrupt Priority Control 9)        |      | SPIxCON2 (SPIx Control 2)                  |       |

| NVMCON (Flash Memory Control)              |      | SPIxSTAT (SPIx Status and Control)         |       |

| NVMKEY (Nonvolatile Memory Key)            |      | SR (CPU STATUS) 4                          |       |

| OCxCON (Output Compare x Control)          |      | T1CON (Timer1 Control)                     |       |

| OSCCON (Oscillator Control)                |      | T2CON (Timer2 Control)                     |       |

| OSCTUN (FRC Oscillator Tuning)             |      | T3CON (Timer3 Control)                     |       |

| PADCFG1 (Pad Configuration Control)        |      | T4CON (Timer4 Control)                     |       |

| PMD1 (Peripheral Module Disable Control 1) |      | T5CON (Timer5 Control)                     |       |

| PMD2 (Peripheral Module Disable Control 2) | 136  | UxMODE (UARTx Mode)                        |       |

|                                            |      | UxSTA (UARTx Status and Control)           | . 215 |