Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gp102t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70204) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33FJ16(GP/MC)101/102 The and dsPIC33FJ32(GP/MC)101/102/104 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can serve as a data, address, or address offset register. The 16th Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

There are two classes of instruction in the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices are capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model for the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 is shown in Figure 3-2.

# 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program-to-data-space mapping feature lets any instruction access program space as if it were data space.

# 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory, while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain Working registers to each address space.

# 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Data Memory" (DS70202) and "Program Memory" (DS70203) in the "dsPIC33/PIC24 Family Reference Manual", which are available from the Microchip web site (www.microchip.com).

The device architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

### 4.1 Program Address Space

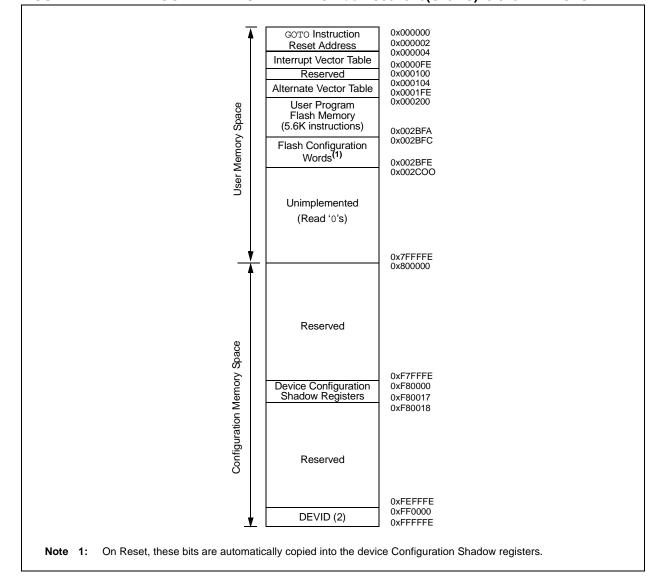

The program address memory space of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The memory maps for the dsPIC33FJ16(GP/MC)101/ 102 and dsPIC33FJ32(GP/MC)101/102/104 family of devices are shown in Figure 4-1 and Figure 4-2.

#### FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33FJ16(GP/MC)101/102 DEVICES

| TABLE | 4-26: | PERI | PHERAI | _ PIN S | ELECT | OUTPU | T REGIS | TER MA | P FOR o | IsPIC33 | 3FJ32(0 | SP/MC) <sup>2</sup> | 04 DE | /ICES |   |

|-------|-------|------|--------|---------|-------|-------|---------|--------|---------|---------|---------|---------------------|-------|-------|---|

|       |       |      |        |         |       |       |         |        |         |         |         |                     |       |       | т |

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11                      | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4      | Bit 3 | Bit 2      | Bit 1 | Bit 0      | All<br>Resets |  |      |

|--------------|-------------|--------|--------|--------|--------|-----------------------------|-----------|-------|-------|-------|-------|------------|------------|-------|------------|-------|------------|---------------|--|------|

| RPOR0        | 06C0        | _      | —      | —      |        |                             | RP1R<4:0> | >     |       | —     | —     | —          |            |       | RP0R<4:0>  |       |            | 0000          |  |      |

| RPOR1        | 06C2        | -      |        | _      |        |                             | RP3R<4:0> | >     |       | _     | _     | _          |            |       | RP2R<4:0>  |       |            | 0000          |  |      |

| RPOR2        | 06C4        | -      |        | _      |        |                             | RP5R<4:0> | >     |       | _     | _     | _          |            |       | RP4R<4:0>  |       |            | 0000          |  |      |

| RPOR3        | 06C6        | —      | _      | _      |        |                             | RP7R<4:0> | >     |       | _     | _     | —          |            |       | RP6R<4:0>  |       |            | 0000          |  |      |

| RPOR4        | 06C8        | _      | _      | _      |        |                             | RP9R<4:0> | >     |       | _     | _     | _          |            |       | RP8R<4:0>  |       |            | 0000          |  |      |

| RPOR5        | 06CA        | _      | _      | _      |        | RP11R<4:0> — —              |           | _     | _     |       | F     | RP10R<4:0> |            |       | 0000       |       |            |               |  |      |

| RPOR6        | 06CC        | _      | _      | _      |        | RP13R<4:0> — — — RP12R<4:0> |           |       |       | 0000  |       |            |            |       |            |       |            |               |  |      |

| RPOR7        | 06CE        | _      | _      | _      |        |                             | RP15R<4:0 | >     |       | _     | _     | _          |            | F     | RP14R<4:0> |       |            | 0000          |  |      |

| RPOR8        | 06D0        | _      | _      | _      |        |                             | RP17R<4:0 | >     |       | _     | _     | _          |            | F     | RP16R<4:0> |       |            | 0000          |  |      |

| RPOR9        | 06D2        | -      |        | _      |        | RP19R<4:0                   |           | R     |       | >     |       | _          | _          | _     |            | F     | RP18R<4:0> |               |  | 0000 |

| RPOR10       | 06D4        | _      | _      | _      |        |                             | RP21R<4:0 | >     |       | _     | _     | _          | RP20R<4:0> |       | 0000       |       |            |               |  |      |

| RPOR11       | 06D6        | _      | _      | _      |        |                             | RP23R<4:0 | >     |       | _     | _     | _          | RP22R<4:0> |       | 0000       |       |            |               |  |      |

| RPOR12       | 06D8        | _      | _      | -      |        |                             | RP25R<4:0 | >     |       | _     | -     | —          | RP24R<4:0> |       | 0000       |       |            |               |  |      |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-27: PORTA REGISTER MAP FOR dsPIC33FJ16(GP/MC)101/102 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3     | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|----------|-----------|------------|-------|-------|---------------|

| TRISA        | 02C0        | _      |        | _      |        | _      | _      | _     | _     | _     | _     | _     |          | -         | rrisa<4:0> |       |       | 001F          |

| PORTA        | 02C2        | —      | _      | _      | _      | _      | _      | _     | _     | -     | —     | _     |          |           | RA<4:0     |       |       | xxxx          |

| LATA         | 02C4        | —      | _      | _      | _      | _      | _      | _     | _     | -     | —     | _     | LATA<4:0 |           | xxxx       |       |       |               |

| ODCA         | 02C6        |        | _      | _      | _      | _      | _      | _     | _     | _     |       | _     | (        | ODCA<4:2> |            | _     | —     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-28: PORTA REGISTER MAP FOR dsPIC33FJ32(GP/MC)101/102 DEVICES

|     | File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|-----|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|------------|-------|------------|-------|-------|---------------|

| Ī   | TRISA        | 02C0        | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |            | ٦     | rrisa<4:0> |       |       | 001F          |

| ſ   | PORTA        | 02C2        | _      | _      | _      | _      | _      | _      | —     |       | _     | _     | _     |            |       | RA<4:0     |       |       | xxxx          |

| ſ   | LATA         | 02C4        | _      | _      | _      | _      | _      | _      | —     |       | _     | _     | _     | LATA<4:0 x |       |            | xxxx  |       |               |

| . [ | ODCA         | 02C6        | _      |        |        | —      |        | _      | _     | _     | _     | _     | _     |            | ODCA  | <3:2>      | _     | -     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed, but the contents of the register remain unchanged.

## 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWM<3:0> bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the bit-reversed address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

**Note:** All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XB<14:0> value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing should not be enabled together. If an application attempts to do so, Bit-Reversed Addressing will assume priority when active. For the X WAGU and Y AGU, Modulo Addressing will be disabled. However, Modulo Addressing will continue to function in the X RAGU.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

|               |               |                                     | 0            |                 |                  |                |        |

|---------------|---------------|-------------------------------------|--------------|-----------------|------------------|----------------|--------|

| R/W-0         | R-0           | U-0                                 | U-0          | U-0             | U-0              | U-0            | U-0    |

| ALTIVT        | DISI          | —                                   | —            | —               | —                | —              | —      |

| bit 15        |               |                                     |              |                 |                  |                | bit 8  |

|               |               |                                     |              |                 |                  |                |        |

| U-0           | U-0           | U-0                                 | U-0          | U-0             | R/W-0            | R/W-0          | R/W-0  |

|               |               | —                                   | —            | _               | INT2EP           | INT1EP         | INT0EP |

| bit 7         |               |                                     |              |                 |                  |                | bit (  |

|               |               |                                     |              |                 |                  |                |        |

| Legend:       |               |                                     |              |                 |                  |                |        |

| R = Readabl   | e bit         | W = Writable                        | bit          | U = Unimple     | emented bit, rea | d as '0'       |        |

| -n = Value at | POR           | '1' = Bit is set                    |              | '0' = Bit is cl | eared            | x = Bit is unk | nown   |

|               |               |                                     |              |                 |                  |                |        |

| bit 15        |               | ble Alternate In                    | •            |                 |                  |                |        |

|               |               | ernate Interrupt<br>ndard Interrupt |              |                 |                  |                |        |

| bit 14        |               | nuard interrupt                     |              |                 |                  |                |        |

|               |               | truction is activ                   |              |                 |                  |                |        |

|               |               | truction is not a                   | -            |                 |                  |                |        |

| bit 13-3      | Unimplemen    | nted: Read as '                     | 0'           |                 |                  |                |        |

| bit 2         | INT2EP: Exte  | ernal Interrupt 2                   | 2 Edge Detec | t Polarity Sele | ct bit           |                |        |

|               | •             | on negative ed                      | •            |                 |                  |                |        |

|               | 0 = Interrupt | on positive edg                     | e            |                 |                  |                |        |

| bit 1         |               | ernal Interrupt 1                   | 0            | t Polarity Sele | ct bit           |                |        |

|               |               | on negative ed                      |              |                 |                  |                |        |

| <b>h</b> it 0 | -             | on positive edg                     |              | t Delevity Cele | -4 h i4          |                |        |

| bit 0         |               | ernal Interrupt (                   | 0            | a Polarity Sele |                  |                |        |

|               |               | on negative ed<br>on positive edg   |              |                 |                  |                |        |

|               |               |                                     | -            |                 |                  |                |        |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

# REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>                                                          |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit                                                                                                     |

|       | 1 = Interrupt request has occurred                                                                                                                           |

|       | 0 = Interrupt request has not occurred                                                                                                                       |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit                                                                                                                 |

|       | 1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                                                                                 |

|       | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>INTOIF: External Interrupt 0 Flag Status bit</li> </ul> |

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| U-0           | U-0        | U-0              | U-0 | U-0               | R/W-0            | R/W-0           | U-0   |

|---------------|------------|------------------|-----|-------------------|------------------|-----------------|-------|

|               | —          | —                | _   | —                 | CMPMD            | RTCCMD          | _     |

| bit 15        |            |                  |     |                   |                  |                 | bit 8 |

|               |            |                  |     |                   |                  |                 |       |

| U-0           | U-0        | U-0              | U-0 | U-0               | U-0              | U-0             | U-0   |

|               | —          | —                | _   | —                 | —                | —               | —     |

| bit 7         |            |                  |     |                   |                  |                 | bit 0 |

|               |            |                  |     |                   |                  |                 |       |

| Legend:       |            |                  |     |                   |                  |                 |       |

| R = Readable  | e bit      | W = Writable b   | bit | U = Unimplem      | nented bit, read | 1 as '0'        |       |

| -n = Value at | POR        | '1' = Bit is set |     | '0' = Bit is clea | ared             | x = Bit is unkn | own   |

|               |            |                  |     |                   |                  |                 |       |

| bit 15-11     | Unimplemen | ted: Read as '0  | ,   |                   |                  |                 |       |

#### REGISTER 9-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 10  | CMPMD: Comparator Module Disable bit |

|---------|--------------------------------------|

|         | 1 = Comparator module is disabled    |

|         | 0 = Comparator module is enabled     |

| bit 9   | RTCCMD: RTCC Module Disable bit      |

|         | 1 = RTCC module is disabled          |

|         | 0 = RTCC module is enabled           |

| bit 8-0 | Unimplemented: Read as '0'           |

#### REGISTER 9-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0             | U-0 | U-0              | U-0 | U-0              | U-0              | U-0             | U-0   |

|-----------------|-----|------------------|-----|------------------|------------------|-----------------|-------|

| —               | —   | —                | —   | —                | —                | —               | _     |

| bit 15          |     |                  |     |                  |                  |                 | bit 8 |

|                 |     |                  |     |                  |                  |                 |       |

| U-0             | U-0 | U-0              | U-0 | U-0              | R/W-0            | U-0             | U-0   |

| —               | —   | —                | —   | —                | CTMUMD           | —               | —     |

| bit 7           |     |                  |     |                  |                  |                 | bit ( |

|                 |     |                  |     |                  |                  |                 |       |

| Legend:         |     |                  |     |                  |                  |                 |       |

| R = Readable    | bit | W = Writable     | bit | U = Unimpler     | nented bit, read | l as '0'        |       |

| -n = Value at I | POR | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

bit 15-3 Unimplemented: Read as '0'

bit 2 CTMUMD: CTMU Module Disable bit

1 = CTMU module is disabled

0 = CTMU module is enabled

bit 1-0 Unimplemented: Read as '0'

### 10.7 Peripheral Pin Select Registers

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family of devices implements up to 23 registers for remappable peripheral configuration.

Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 10.4.3.1 "Control Register Lock" for a specific command sequence.

### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0             | U-0 | U-0              | R/W-1  | R/W-1            | R/W-1            | R/W-1           | R/W-1  |

|-----------------|-----|------------------|--------|------------------|------------------|-----------------|--------|

| _               | —   | _                | INT1R4 | INT1R3           | INT1R2           | INT1R1          | INT1R0 |

| bit 15          |     |                  |        |                  |                  |                 | bit 8  |

|                 |     |                  |        |                  |                  |                 |        |

| U-0             | U-0 | U-0              | U-0    | U-0              | U-0              | U-0             | U-0    |

| —               | —   | —                | —      | —                | —                | —               | —      |

| bit 7           |     |                  |        |                  |                  |                 | bit 0  |

|                 |     |                  |        |                  |                  |                 |        |

| Legend:         |     |                  |        |                  |                  |                 |        |

| R = Readable b  | oit | W = Writable     | bit    | U = Unimpler     | mented bit, read | as '0'          |        |

| -n = Value at P | OR  | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| -n = value a | IT POR  | T = Bit is set                 | 0° = Bit is cleared             | X = Bit is unknown |

|--------------|---------|--------------------------------|---------------------------------|--------------------|

| bit 15-13    | Unimple | mented: Read as '0'            |                                 |                    |

| bit 12-8     | INT1R<4 | 1:0>: Assign External Interr   | upt 1 (INTR1) to the Correspond | ding RPn Pin bits  |

|              |         | Input tied to Vss<br>Reserved  |                                 |                    |

|              | •       |                                |                                 |                    |

|              | •       |                                |                                 |                    |

|              |         | Reserved<br>Input tied to RP25 |                                 |                    |

|              |         |                                |                                 |                    |

|              | •       |                                |                                 |                    |

bit 7-0 Unimplemented: Read as '0'

00001 = Input tied to RP1 00000 = Input tied to RP0

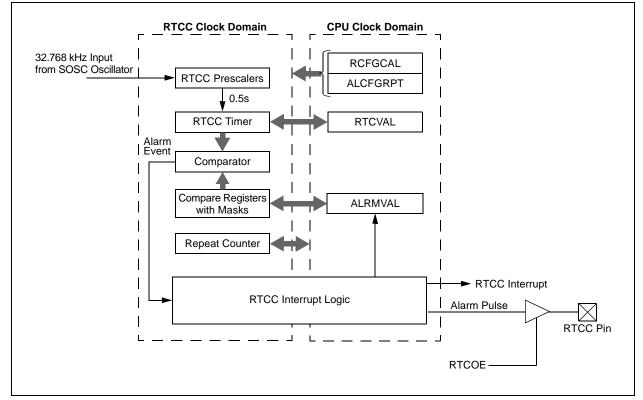

# 21.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 device families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Real-Time Clock and Calendar (RTCC)" (DS70310) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter discusses the Real-Time Clock and Calendar (RTCC) module, available on dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices, and its operation. Some of the key features of the RTCC module are:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- Calendar: weekday, date, month and year

- Alarm configurable

- Year range: 2000 to 2099

- · Leap year correction

- BCD format for compact firmware

- · Optimized for low-power operation

- · User calibration with auto-adjust

- Calibration range: ±2.64 seconds error per month

- Requirements: external 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

The RTCC module is intended for applications where accurate time must be maintained for extended periods of time with minimum to no intervention from the CPU. The RTCC module is optimized for low-power usage to provide extended battery lifetime while keeping track of time.

The RTCC module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099.

The hours are available in 24-hour (military time) format. The clock provides a granularity of one second with half-second visibility to the user.

# FIGURE 21-1: RTCC BLOCK DIAGRAM

# REGISTER 21-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

| bit 7-0 | CAL<7:0>: RTC Drift Calibration bits                                                                         |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|         | 01111111 = Maximum positive adjustment; adds 508 RTC clock pulses every one minute                           |  |  |  |  |  |  |

|         | •                                                                                                            |  |  |  |  |  |  |

|         | •                                                                                                            |  |  |  |  |  |  |

|         | •                                                                                                            |  |  |  |  |  |  |

|         | 00000001 = Minimum positive adjustment; adds 4 RTC clock pulses every one minute<br>00000000 = No adjustment |  |  |  |  |  |  |

|         | 11111111 = Minimum negative adjustment; subtracts 4 RTC clock pulses every one minute                        |  |  |  |  |  |  |

|         | •                                                                                                            |  |  |  |  |  |  |

|         | •                                                                                                            |  |  |  |  |  |  |

|         | •                                                                                                            |  |  |  |  |  |  |

|         | 10000000 = Maximum negative adjustment; subtracts 512 RTC clock pulses every one minute                      |  |  |  |  |  |  |

- **Note 1:** The RCFGCAL register is only affected by a POR.

- **2:** A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

# REGISTER 21-6: RTCVAL (WHEN RTCPTR<1:0> = 01): RTCC WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

|        | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-----|-------|-------|-------|

| —      | —   |     | -   | _   | WDAY2 | WDAY1 | WDAY0 |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| <b>ad as</b> '0' |

|------------------|

| ć                |

bit 10-8 **WDAY<2:0>:** Binary Coded Decimal Value of Weekday Digit bits Contains a value from 0 to 6.

bit 7-6 Unimplemented: Read as '0'

- bit 5-4 HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits Contains a value from 0 to 2.

- bit 3-0 **HRONE<3:0>:** Binary Coded Decimal Value of Hour's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### 22.1 CTMU Control Registers

#### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

| R/W-0         | U-0                                                            | R/W-0                                   | R/W-0               | R/W-0              | R/W-0            | R/W-0                  | R/W-0    |  |  |  |

|---------------|----------------------------------------------------------------|-----------------------------------------|---------------------|--------------------|------------------|------------------------|----------|--|--|--|

| CTMUEN        |                                                                | CTMUSIDL                                | TGEN <sup>(1)</sup> | EDGEN              | EDGSEQEN         | IDISSEN <sup>(2)</sup> | CTTRIG   |  |  |  |

| oit 15        |                                                                |                                         |                     |                    |                  |                        | bit 8    |  |  |  |

|               |                                                                |                                         |                     |                    |                  |                        |          |  |  |  |

| U-0           | U-0                                                            | U-0                                     | U-0                 | U-0                | U-0              | U-0                    | U-0      |  |  |  |

| <br>bit 7     | _                                                              | —                                       | _                   | _                  | _                | —                      | bit 0    |  |  |  |

|               |                                                                |                                         |                     |                    |                  |                        | DILC     |  |  |  |

| _egend:       |                                                                |                                         |                     |                    |                  |                        |          |  |  |  |

| R = Readabl   | e bit                                                          | W = Writable b                          | oit                 | U = Unimplen       | nented bit, read | as '0'                 |          |  |  |  |

| -n = Value at | POR                                                            | '1' = Bit is set                        |                     | '0' = Bit is clea  | ared             | x = Bit is unkno       | own      |  |  |  |

|               |                                                                |                                         |                     |                    |                  |                        |          |  |  |  |

| oit 15        | CTMUEN: C                                                      | TMU Enable bit                          |                     |                    |                  |                        |          |  |  |  |

|               | 1 = Module                                                     |                                         |                     |                    |                  |                        |          |  |  |  |

|               | 0 = Module                                                     |                                         |                     |                    |                  |                        |          |  |  |  |

| bit 14        | Unimpleme                                                      | nted: Read as '0                        | ,                   |                    |                  |                        |          |  |  |  |

| oit 13        |                                                                | CTMU Stop in Id                         |                     |                    |                  |                        |          |  |  |  |

|               | 1 = Discontinues module operation when device enters Idle mode |                                         |                     |                    |                  |                        |          |  |  |  |

|               |                                                                | es module opera                         |                     | ode                |                  |                        |          |  |  |  |

| bit 12        |                                                                | Generation Ena                          |                     |                    |                  |                        |          |  |  |  |

|               |                                                                | s edge delay gen<br>s edge delay gen    |                     |                    |                  |                        |          |  |  |  |

| bit 11        |                                                                | ge Enable bit                           |                     |                    |                  |                        |          |  |  |  |

|               |                                                                | are not blocked                         |                     |                    |                  |                        |          |  |  |  |

|               | 0 = Edges a                                                    | are blocked                             |                     |                    |                  |                        |          |  |  |  |

| oit 10        | EDGSEQEN                                                       | I: Edge Sequenc                         | e Enable bit        |                    |                  |                        |          |  |  |  |

|               |                                                                | event must occur                        |                     | 2 event can oc     | cur              |                        |          |  |  |  |

|               | -                                                              | e sequence is ne                        |                     |                    |                  |                        |          |  |  |  |

| oit 9         | IDISSEN: Ar                                                    | nalog Current So                        | urce Control b      | <sub>oit</sub> (2) |                  |                        |          |  |  |  |

|               | •                                                              | current source ou                       |                     |                    |                  |                        |          |  |  |  |

|               | •                                                              | current source ou                       |                     | bunded             |                  |                        |          |  |  |  |

| bit 8         |                                                                | MU Trigger Con                          |                     |                    |                  |                        |          |  |  |  |

|               | 00                                                             | output is enablec<br>output is disablec |                     |                    |                  |                        |          |  |  |  |

| bit 7-0       |                                                                | nted: Read as '0                        |                     |                    |                  |                        |          |  |  |  |

|               | -                                                              |                                         |                     |                    |                  |                        |          |  |  |  |

|               |                                                                | peripheral input<br>Section 10.4 "P     |                     |                    |                  | able RPn pin. F        | For more |  |  |  |

|               |                                                                | e S&H capacitor                         | -                   | . ,                |                  | nnle/conversion        |          |  |  |  |

2: The ADC module S&H capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

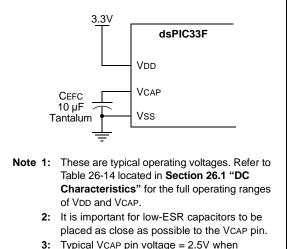

## 23.2 On-Chip Voltage Regulator

All of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 23-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 26-14 located in **Section 26.1** "**DC Characteristics**".

| Note: | It is important for low-ESR capacitors to be |

|-------|----------------------------------------------|

|       | placed as close as possible to the VCAP pin. |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 23-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

**3:** Typical VCAP pin voltage = 2.5V when VDD  $\ge$  VDDMIN.

#### 23.3 BOR: Brown-out Reset

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an Oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

| Base<br>Instr<br># | str Assembly |                                     | Assembly Syntax                 | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|--------------|-------------------------------------|---------------------------------|---------------------------------------------------|---------------|----------------|--------------------------|

| 48                 | MPY          | MPY<br>Wm*Wn, Acc, Wx, Wxd, Wy, Wyd |                                 | Multiply Wm by Wn to Accumulator                  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |              | MPY<br>Wm*Wm,Ad                     | cc,Wx,Wxd,Wy,Wyd                | Square Wm to Accumulator                          | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 49                 | MPY.N        | MPY.N<br>Wm*Wn,Ad                   | cc,Wx,Wxd,Wy,Wyd                | (Multiply Wm by Wn) to Accumulator                | 1             | 1              | None                     |

| 50                 | MSC          | MSC                                 | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd,<br>AWB | Multiply and Subtract from Accumulator            | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 51                 | MUL          | MUL.SS                              | Wb,Ws,Wnd                       | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)          | 1             | 1              | None                     |

|                    |              | MUL.SU                              | Wb,Ws,Wnd                       | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)        | 1             | 1              | None                     |

|                    |              | MUL.US                              | Wb,Ws,Wnd                       | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1             | 1              | None                     |

|                    |              | MUL.UU                              | Wb,Ws,Wnd                       | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1              | None                     |

|                    |              | MUL.SU                              | Wb,#lit5,Wnd                    | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)      | 1             | 1              | None                     |

|                    |              | MUL.UU                              | Wb,#lit5,Wnd                    | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1             | 1              | None                     |

|                    |              | MUL                                 | f                               | W3:W2 = f * WREG                                  | 1             | 1              | None                     |

| 52                 | NEG          | NEG                                 | Acc                             | Negate Accumulator                                | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

|                    |              | NEG                                 | f                               | $f = \overline{f} + 1$                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |              | NEG                                 | f,WREG                          | WREG = $\overline{f}$ + 1                         | 1             | 1              | C,DC,N,OV,2              |

|                    |              | NEG                                 | Ws,Wd                           | $Wd = \overline{Ws} + 1$                          | 1             | 1              | C,DC,N,OV,2              |

| 53                 | NOP          | NOP                                 |                                 | No Operation                                      | 1             | 1              | None                     |

|                    |              | NOPR                                |                                 | No Operation                                      | 1             | 1              | None                     |

| 54                 | POP          | POP                                 | f                               | Pop f from Top-of-Stack (TOS)                     | 1             | 1              | None                     |

|                    |              | POP                                 | Wdo                             | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1              | None                     |

|                    |              | POP.D                               | Wnd                             | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2              | None                     |

|                    |              | POP.S                               |                                 | Pop Shadow Registers                              | 1             | 1              | All                      |

| 55                 | PUSH         | PUSH                                | f                               | Push f to Top-of-Stack (TOS)                      | 1             | 1              | None                     |

|                    |              | PUSH                                | Wso                             | Push Wso to Top-of-Stack (TOS)                    | 1             | 1              | None                     |

|                    |              | PUSH.D                              | Wns                             | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)        | 1             | 2              | None                     |

|                    |              | PUSH.S                              |                                 | Push Shadow Registers                             | 1             | 1              | None                     |

| 56                 | PWRSAV       | PWRSAV                              | #lit1                           | Go into Sleep or Idle mode                        | 1             | 1              | WDTO,Sleep               |

| 57                 | RCALL        | RCALL                               | Expr                            | Relative Call                                     | 1             | 2              | None                     |

|                    |              | RCALL                               | Wn                              | Computed Call                                     | 1             | 2              | None                     |

| 58                 | REPEAT       | REPEAT                              | #lit14                          | Repeat Next Instruction lit14 + 1 times           | 1             | 1              | None                     |

|                    |              | REPEAT                              | Wn                              | Repeat Next Instruction (Wn) + 1 times            | 1             | 1              | None                     |

| 59                 | RESET        | RESET                               |                                 | Software device Reset                             | 1             | 1              | None                     |

| 60                 | RETFIE       | RETFIE                              |                                 | Return from interrupt                             | 1             | 3 (2)          | None                     |

| 61                 | RETLW        | RETLW                               | #lit10,Wn                       | Return with literal in Wn                         | 1             | 3 (2)          | None                     |

| 62                 | RETURN       | RETURN                              |                                 | Return from Subroutine                            | 1             | 3 (2)          | None                     |

| 63                 | RLC          | RLC                                 | f                               | f = Rotate Left through Carry f                   | 1             | 1              | C,N,Z                    |

|                    |              | RLC                                 | f,WREG                          | WREG = Rotate Left through Carry f                | 1             | 1              | C,N,Z                    |

| ~ .                |              | RLC                                 | Ws,Wd                           | Wd = Rotate Left through Carry Ws                 | 1             | 1              | C,N,Z                    |

| 64                 | RLNC         | RLNC                                | f                               | f = Rotate Left (No Carry) f                      | 1             | 1              | N,Z                      |

|                    |              | RLNC                                | f,WREG                          | WREG = Rotate Left (No Carry) f                   | 1             | 1              | N,Z                      |

| ~=                 |              | RLNC                                | Ws,Wd                           | Wd = Rotate Left (No Carry) Ws                    | 1             | 1              | N,Z                      |

| 65                 | RRC          | RRC                                 | f                               | f = Rotate Right through Carry f                  | 1             | 1              | C,N,Z                    |

|                    |              | RRC                                 | f,WREG                          | WREG = Rotate Right through Carry f               | 1             | 1              | C,N,Z                    |

|                    |              | RRC                                 | Ws,Wd                           | Wd = Rotate Right through Carry Ws                | 1             | 1              | C,N,Z                    |

### TABLE 24-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| DC CHARACI                                                                                           | ERISTICS               |     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                  |        |                             |  |  |

|------------------------------------------------------------------------------------------------------|------------------------|-----|-------------------------------------------------------|------------------|--------|-----------------------------|--|--|

| Parameter<br>No.                                                                                     | Typical <sup>(1)</sup> | Мах | Units                                                 | Units Conditions |        |                             |  |  |

| Idle Current (IIDLE): Core Off, Clock On Base Current <sup>(2)</sup> – dsPIC33FJ32(GP/MC)10X Devices |                        |     |                                                       |                  |        |                             |  |  |

| DC40d                                                                                                | 0.4                    | 1.0 | mA                                                    | -40°C            |        |                             |  |  |

| DC40a                                                                                                | 0.4                    | 1.0 | mA                                                    | +25°C            | - 3.3V | LPRC                        |  |  |

| DC40b                                                                                                | 0.4                    | 1.0 | mA                                                    | +85°C            | 3.3 V  | (32.768 kHz) <sup>(3)</sup> |  |  |

| DC40c                                                                                                | 0.5                    | 1.0 | mA                                                    | +125°C           |        |                             |  |  |

| DC41d                                                                                                | 0.5                    | 1.1 | mA                                                    | -40°C            |        |                             |  |  |

| DC41a                                                                                                | 0.5                    | 1.1 | mA                                                    | +25°C            | - 3.3V | 1 MIPS <sup>(3)</sup>       |  |  |

| DC41b                                                                                                | 0.5                    | 1.1 | mA                                                    | +85°C            | 5.5 V  | T IVITE SY 7                |  |  |

| DC41c                                                                                                | 0.8                    | 1.1 | mA                                                    | +125°C           |        |                             |  |  |

| DC42d                                                                                                | 0.9                    | 1.6 | mA                                                    | -40°C            |        |                             |  |  |

| DC42a                                                                                                | 0.9                    | 1.6 | mA                                                    | +25°C            | - 3.3V | 4 MIPS <sup>(3)</sup>       |  |  |

| DC42b                                                                                                | 1.0                    | 1.6 | mA                                                    | +85°C            | 3.3V   | 4 10115357                  |  |  |

| DC42c                                                                                                | 1.2                    | 1.6 | mA                                                    | +125°C           |        |                             |  |  |

| DC43a                                                                                                | 1.6                    | 2.6 | mA                                                    | +25°C            |        |                             |  |  |

| DC43d                                                                                                | 1.6                    | 2.6 | mA                                                    | -40°C            | - 3.3V | 10 MIPS <sup>(3)</sup>      |  |  |

| DC43b                                                                                                | 1.7                    | 2.6 | mA                                                    | +85°C            | 3.3V   | 10 1011-517                 |  |  |

| DC43c                                                                                                | 2.0                    | 2.6 | mA                                                    | +125°C           |        |                             |  |  |

| DC44d                                                                                                | 2.4                    | 3.8 | mA                                                    | -40°C            |        |                             |  |  |

| DC44a                                                                                                | 2.4                    | 3.8 | mA                                                    | +25°C            | - 3.3V | 16 MIPS <sup>(3)</sup>      |  |  |

| DC44b                                                                                                | 2.6                    | 3.8 | mA                                                    | +85°C            | 3.3V   | 10 101173                   |  |  |

| DC44c                                                                                                | 2.9                    | 3.8 | mA                                                    | +125°C           | ]      |                             |  |  |

## TABLE 26-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE) (CONTINUED)

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: Base Idle current is measured as follows:

- CPU core is off, oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- External Secondary Oscillator (SOSC) is disabled (i.e., SOSCO and SOSCI pins are configured as digital I/O inputs)

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (PMDx bits are all zeroed)

- **3:** These parameters are characterized, but not tested in manufacturing.

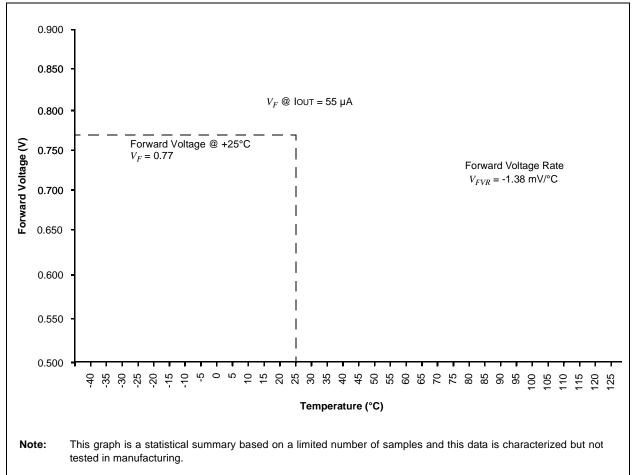

#### FIGURE 26-33: FORWARD VOLTAGE VERSUS TEMPERATURE

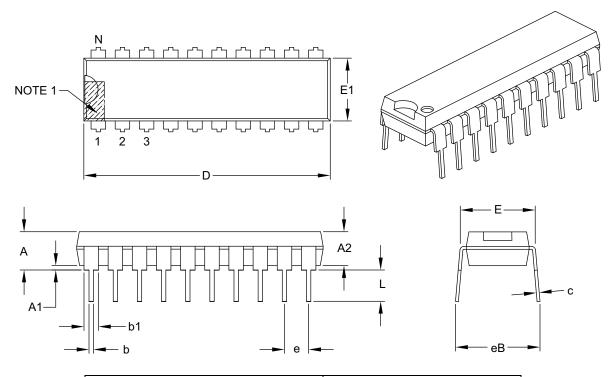

## 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units     | INCHES |          |       |  |

|----------------------------|-----------|--------|----------|-------|--|

| Dimensio                   | on Limits | MIN    | NOM      | MAX   |  |

| Number of Pins             | Ν         |        | 20       |       |  |

| Pitch                      | е         |        | .100 BSC |       |  |

| Top to Seating Plane       | Α         | -      | -        | .210  |  |

| Molded Package Thickness   | A2        | .115   | .130     | .195  |  |

| Base to Seating Plane      | A1        | .015   | -        | -     |  |

| Shoulder to Shoulder Width | Е         | .300   | .310     | .325  |  |

| Molded Package Width       | E1        | .240   | .250     | .280  |  |

| Overall Length             | D         | .980   | 1.030    | 1.060 |  |

| Tip to Seating Plane       | L         | .115   | .130     | .150  |  |

| Lead Thickness             | С         | .008   | .010     | .015  |  |

| Upper Lead Width           | b1        | .045   | .060     | .070  |  |

| Lower Lead Width           | b         | .014   | .018     | .022  |  |

| Overall Row Spacing §      | eB        | -      | -        | .430  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B

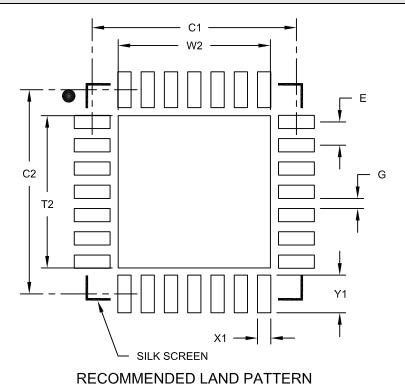

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimensio                   | MIN         | NOM      | MAX  |      |

| Contact Pitch              |             | 0.65 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 4.25 |

| Optional Center Pad Length |             |          | 4.25 |      |

| Contact Pad Spacing        | C1          |          | 5.70 |      |

| Contact Pad Spacing        | C2          |          | 5.70 |      |

| Contact Pad Width (X28)    | X1          |          |      | 0.37 |

| Contact Pad Length (X28)   | Y1          |          |      | 1.00 |

| Distance Between Pads      | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

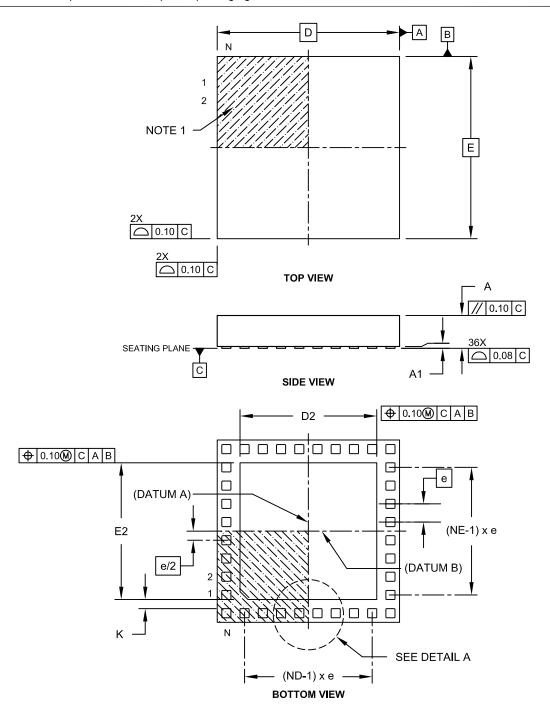

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-187C Sheet 1 of 2

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Tape and Reel FI<br>Temperature Rar | amily —<br>y Size (ř<br>ag (if ap<br>nge —— | Kby | /te) / / / / / / / / / / / / / / / /                                                                                                                                                                                                                                               | Exa<br>a) | amples:<br>dsPIC33FJ16MC102-E/SP:<br>Motor Control dsPIC33,<br>16-Kbyte Program Memory,<br>28-Pin, Extended Temperature,<br>SPDIP package. |

|-------------------------------------|---------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture:                       | 33                                          | =   | 16-bit Digital Signal Controller                                                                                                                                                                                                                                                   |           |                                                                                                                                            |

| Flash Memory Family:                | FJ                                          | =   | Flash program memory, 3.3V                                                                                                                                                                                                                                                         |           |                                                                                                                                            |

| Product Group:                      | GP1<br>MC1                                  | =   |                                                                                                                                                                                                                                                                                    |           |                                                                                                                                            |

| Pin Count:                          | 01<br>02                                    | =   |                                                                                                                                                                                                                                                                                    |           |                                                                                                                                            |

| Temperature Range:                  | l<br>E                                      | =   | -40°C to +85°C (Industrial)<br>-40°C to +125°C (Extended)                                                                                                                                                                                                                          |           |                                                                                                                                            |

| Package:                            | P<br>SS<br>SP<br>SO<br>ML<br>PT<br>TL       |     | Plastic Shrink Small Outline - 5.3 mm body (SSOP)<br>Skinny Plastic Dual In-Line - 300 mil body (SPDIP)<br>Plastic Small Outline - Wide - 7.50 mil body (SOIC)<br>Plastic Quad, No Lead - (28-pin) 6x6 mm body (QFN)<br>Plastic Thin Quad Flatpack - (44-pin) 10x10 mm body (TQFP) |           |                                                                                                                                            |