Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 15                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 4x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

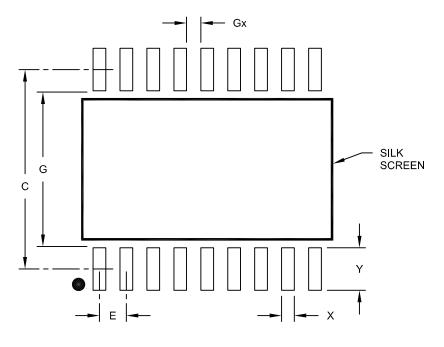

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 20-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16mc101-e-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

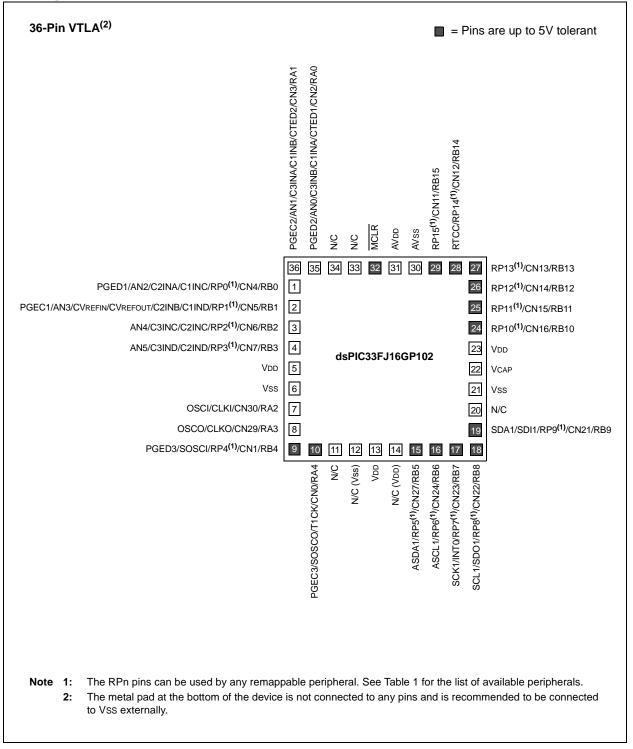

#### Pin Diagrams (Continued)

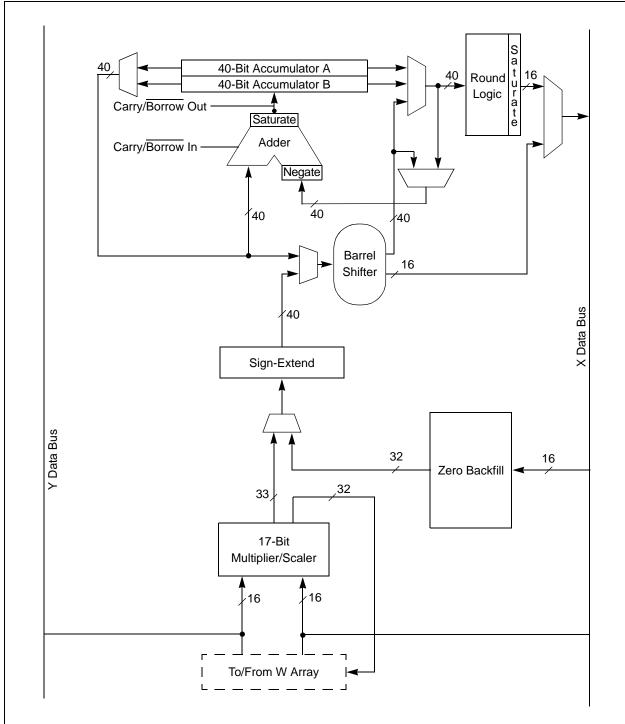

## FIGURE 3-3: DSP ENGINE BLOCK DIAGRAM

NOTES:

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed, but the contents of the register remain unchanged.

### 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWM<3:0> bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the bit-reversed address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

**Note:** All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XB<14:0> value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing should not be enabled together. If an application attempts to do so, Bit-Reversed Addressing will assume priority when active. For the X WAGU and Y AGU, Modulo Addressing will be disabled. However, Modulo Addressing will continue to function in the X RAGU.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

### 6.3 POR

A POR circuit ensures the device is reset from poweron. The POR circuit is active until VDD crosses the VPOR threshold and the delay, TPOR, has elapsed. The delay, TPOR, ensures that the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to **Section 26.0** "**Electrical Characteristics**" for details.

The Power-on Reset (POR) status bit in the Reset Control (RCON<0>) register is set to indicate the Power-on Reset.

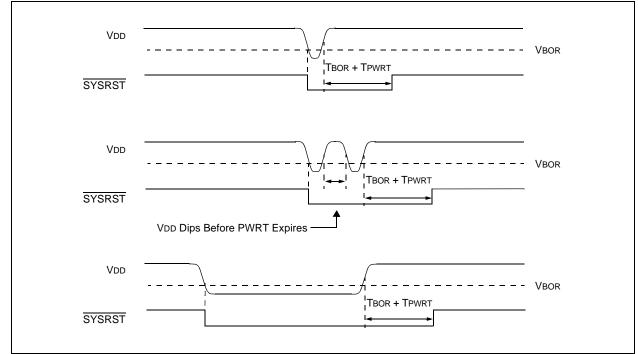

#### 6.4 BOR and PWRT

The on-chip regulator has a BOR circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses the VBOR threshold and the delay, TBOR, has elapsed. The delay, TBOR, ensures the voltage regulator output becomes stable.

The Brown-out Reset (BOR) status bit in the Reset Control (RCON<1>) register is set to indicate the Brown-out Reset.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The Power-up Timer (PWRT) provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

Refer to **Section 23.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The Reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point.

#### FIGURE 6-3: BROWN-OUT RESET SITUATIONS

## REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>                                                          |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit                                                                                                     |

|       | 1 = Interrupt request has occurred                                                                                                                           |

|       | 0 = Interrupt request has not occurred                                                                                                                       |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit                                                                                                                 |

|       | 1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                                                                                 |

|       | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>INTOIF: External Interrupt 0 Flag Status bit</li> </ul> |

| 11.0          | U-0                                          | R/W-0                              | R/W-0                     | R/W-0               | U-0             | U-0             | U-0     |  |  |  |  |  |

|---------------|----------------------------------------------|------------------------------------|---------------------------|---------------------|-----------------|-----------------|---------|--|--|--|--|--|

| U-0           | 0-0                                          | INT2IF                             | T5IF <sup>(1)</sup>       | T4IF <sup>(1)</sup> | 0-0             | 0-0             | 0-0     |  |  |  |  |  |

| bit 15        |                                              | 1111211                            | 1311                      | 1411                |                 |                 | bit     |  |  |  |  |  |

|               |                                              |                                    |                           |                     |                 |                 |         |  |  |  |  |  |

| U-0           | U-0                                          | U-0                                | R/W-0                     | R/W-0               | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |  |

| —             | —                                            | —                                  | INT1IF                    | CNIF                | CMIF            | MI2C1IF         | SI2C1IF |  |  |  |  |  |

| bit 7         |                                              |                                    |                           |                     |                 |                 | bit     |  |  |  |  |  |

| Legend:       |                                              |                                    |                           |                     |                 |                 |         |  |  |  |  |  |

| R = Readable  | e bit                                        | W = Writable                       | bit                       | U = Unimpler        | nented bit, rea | d as '0'        |         |  |  |  |  |  |

| -n = Value at | POR                                          | '1' = Bit is set                   |                           | '0' = Bit is cle    | ared            | x = Bit is unkr | nown    |  |  |  |  |  |

| bit 15-14     | Unimplemen                                   | nted: Read as '                    | כי                        |                     |                 |                 |         |  |  |  |  |  |

| bit 13        | INT2IF: Exter                                | rnal Interrupt 2                   | Flag Status bi            | t                   |                 |                 |         |  |  |  |  |  |

|               | 1 = Interrupt                                | request has occ                    | curred                    |                     |                 |                 |         |  |  |  |  |  |

|               | 0 = Interrupt                                | request has not                    | occurred                  |                     |                 |                 |         |  |  |  |  |  |

| bit 12        | T5IF: Timer5                                 | Interrupt Flag S                   | Status bit <sup>(1)</sup> |                     |                 |                 |         |  |  |  |  |  |

|               |                                              | request has occ                    |                           |                     |                 |                 |         |  |  |  |  |  |

|               |                                              | request has not                    |                           |                     |                 |                 |         |  |  |  |  |  |

| bit 11        |                                              | Interrupt Flag S                   |                           |                     |                 |                 |         |  |  |  |  |  |

|               | •                                            | request has occ                    |                           |                     |                 |                 |         |  |  |  |  |  |

|               | -                                            | request has not                    |                           |                     |                 |                 |         |  |  |  |  |  |

| bit 10-5      | -                                            | nted: Read as '                    |                           |                     |                 |                 |         |  |  |  |  |  |

| bit 4         | INT1IF: External Interrupt 1 Flag Status bit |                                    |                           |                     |                 |                 |         |  |  |  |  |  |

|               |                                              | request has occ<br>request has not |                           |                     |                 |                 |         |  |  |  |  |  |

| bit 3         | CNIF: Input C                                | Change Notifica                    | tion Interrupt            | Flag Status bit     |                 |                 |         |  |  |  |  |  |

|               | -                                            | request has occ                    | -                         | C                   |                 |                 |         |  |  |  |  |  |

|               | 0 = Interrupt                                | request has not                    | occurred                  |                     |                 |                 |         |  |  |  |  |  |

| bit 2         | CMIF: Compa                                  | arator Interrupt                   | Flag Status bi            | it                  |                 |                 |         |  |  |  |  |  |

|               |                                              | request has occ<br>request has not |                           |                     |                 |                 |         |  |  |  |  |  |

| bit 1         | -                                            | 1 Master Event                     |                           | ag Status bit       |                 |                 |         |  |  |  |  |  |

|               |                                              | request has occ                    | •                         | 0                   |                 |                 |         |  |  |  |  |  |

|               |                                              | request has not                    |                           |                     |                 |                 |         |  |  |  |  |  |

|               |                                              |                                    |                           | Otativa 1.34        |                 |                 |         |  |  |  |  |  |

| bit 0         | 512C11F: 12C                                 | 1 Slave Events                     | Interrupt Flag            | Status bit          |                 |                 |         |  |  |  |  |  |

| bit 0         |                                              | request has occ                    |                           | Status dit          |                 |                 |         |  |  |  |  |  |

## REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

# 10.4.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

#### 10.4.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |

|-------|--------------------------------------------------------------------------------------------------|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                     |

|       | See MPLAB IDE Help for more information.                                                         |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

#### 10.4.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

#### 10.4.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

| REGISTER      | 10-9: RPINE               | 20: PERIPH                | ERAL PIN S            | ELECT INPU            | TREGISTER             | 20                      |                       |  |  |  |  |

|---------------|---------------------------|---------------------------|-----------------------|-----------------------|-----------------------|-------------------------|-----------------------|--|--|--|--|

| U-0           | U-0                       | U-0                       | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                   | R/W-1                 |  |  |  |  |

| —             | —                         | —                         | SCK1R4 <sup>(1)</sup> | SCK1R3 <sup>(1)</sup> | SCK1R2 <sup>(1)</sup> | SCK1R1 <sup>(1)</sup>   | SCK1R0 <sup>(1)</sup> |  |  |  |  |

| bit 15        |                           |                           |                       |                       |                       |                         | bit 8                 |  |  |  |  |

|               |                           |                           |                       |                       |                       |                         |                       |  |  |  |  |

| U-0           | U-0                       | U-0                       | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                   | R/W-1                 |  |  |  |  |

|               |                           |                           | SDI1R4 <sup>(1)</sup> | SDI1R3 <sup>(1)</sup> | SDI1R2 <sup>(1)</sup> | SDI1R1 <sup>(1)</sup>   | SDI1R0 <sup>(1)</sup> |  |  |  |  |

| bit 7         |                           |                           |                       |                       |                       |                         | bit 0                 |  |  |  |  |

|               |                           |                           |                       |                       |                       |                         |                       |  |  |  |  |

| Legend:       |                           |                           |                       |                       |                       |                         |                       |  |  |  |  |

| R = Readabl   |                           | W = Writable              |                       | -                     | nented bit, read      |                         |                       |  |  |  |  |

| -n = Value at | t POR                     | '1' = Bit is set          |                       | '0' = Bit is cle      | ared                  | x = Bit is unkr         | IOWN                  |  |  |  |  |

| 1 1 4 5 4 0   |                           |                           | o.!                   |                       |                       |                         |                       |  |  |  |  |

| bit 15-13     | -                         | ted: Read as '            |                       |                       | <b>.</b>              |                         |                       |  |  |  |  |

| bit 12-8      |                           |                           | Clock Input (S        | CK1IN) to the         | Corresponding         | RPn Pin bits            |                       |  |  |  |  |

|               | 11111 = Input tied to Vss |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               | 11110 = Reserved          |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               |                           |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               |                           |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               | 11010 = Reserved          |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               | 11001 <b>= I</b> npu      | ut tied to RP25           |                       |                       |                       |                         |                       |  |  |  |  |

|               | •                         |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               | •                         |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               | 00001 = Inpu              | ut tied to RP1            |                       |                       |                       |                         |                       |  |  |  |  |

|               |                           | 00000 = Input tied to RP0 |                       |                       |                       |                         |                       |  |  |  |  |

| bit 7-5       | Unimplemen                | ted: Read as '            | 0'                    |                       |                       |                         |                       |  |  |  |  |

| bit 4-0       | SDI1R<4:0>:               | Assign SPI1 E             | Data Input (SD        | 11) to the Corre      | esponding RPn         | Pin bits <sup>(1)</sup> |                       |  |  |  |  |

|               | 11111 <b>= I</b> npu      |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               | 11110 <b>= Res</b>        | erved                     |                       |                       |                       |                         |                       |  |  |  |  |

|               | •                         |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               |                           |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               | 11010 = Reserved          |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               |                           | ut tied to RP25           |                       |                       |                       |                         |                       |  |  |  |  |

|               |                           |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               |                           |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               | 00001 = Inpu              | it tied to RP1            |                       |                       |                       |                         |                       |  |  |  |  |

|               | 000001 = Inpu             |                           |                       |                       |                       |                         |                       |  |  |  |  |

|               |                           | •                         |                       |                       |                       |                         |                       |  |  |  |  |

#### REGISTER 10-9: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| U-0           | U-0           | U-0              | R/W-0                                    | R/W-0          | R/W-0                    | R/W-0                   | R/W-0 |

|---------------|---------------|------------------|------------------------------------------|----------------|--------------------------|-------------------------|-------|

| _             | —             | _                |                                          |                | RP25R<4:0> <sup>(1</sup> | )                       |       |

| bit 15        |               |                  |                                          |                |                          |                         | bit 8 |

|               |               |                  |                                          |                |                          |                         |       |

| U-0           | U-0           | U-0              | R/W-0                                    | R/W-0          | R/W-0                    | R/W-0                   | R/W-0 |

| _             | —             | —                |                                          |                | RP24R<4:0> <sup>(1</sup> | )                       |       |

| bit 7         |               | •                |                                          |                |                          |                         | bit 0 |

|               |               |                  |                                          |                |                          |                         |       |

| Legend:       |               |                  |                                          |                |                          |                         |       |

| R = Readable  | e bit         | W = Writable     | bit                                      | U = Unimplen   | nented bit, read         | l as '0'                |       |

| -n = Value at | POR           | '1' = Bit is set | 0' = Bit is cleared $x = Bit is unknown$ |                |                          |                         |       |

|               |               |                  |                                          |                |                          |                         |       |

| bit 15-13     | Unimplemen    | ted: Read as '   | 0'                                       |                |                          |                         |       |

| bit 12-8      | RP25R<4:0>    | Peripheral Ou    | utput Function                           | is Assigned to | RP25 Output F            | Pin bits <sup>(1)</sup> |       |

|               | (see Table 10 | -2 for peripher  | al function nu                           | mbers)         |                          |                         |       |

| bit 7-5       | Unimplemen    | ted: Read as '   | 0'                                       |                |                          |                         |       |

| bit 4-0       | RP24R<4:0>    | Peripheral Ou    | utput Function                           | is Assigned to | RP24 Output F            | Pin bits <sup>(1)</sup> |       |

|               | (see Table 10 | -2 for peripher  | al function nu                           | mbore)         | -                        |                         |       |

#### REGISTER 10-23: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

Note 1: These bits are available in dsPIC33FJ32(GP/MC)104 devices only.

| REGISTE            | R 12-4: 15CO                         | N: IIMER5 C                 | UNIKOL RE               | GISTER                      |                 |                    |             |

|--------------------|--------------------------------------|-----------------------------|-------------------------|-----------------------------|-----------------|--------------------|-------------|

| R/W-0              | U-0                                  | R/W-0                       | U-0                     | U-0                         | U-0             | U-0                | U-0         |

| TON <sup>(3)</sup> | —                                    | TSIDL <sup>(2)</sup>        | —                       | —                           | —               | —                  | —           |

| bit 15             |                                      |                             |                         |                             |                 |                    | bit 8       |

|                    |                                      |                             |                         |                             |                 |                    |             |

| U-0                | R/W-0                                | R/W-0                       | R/W-0                   | U-0                         | U-0             | R/W-0              | U-0         |

| —                  | TGATE <sup>(3)</sup>                 | TCKPS1 <sup>(3)</sup>       | TCKPS0 <sup>(3)</sup>   | —                           | —               | TCS <sup>(3)</sup> | —           |

| bit 7              |                                      |                             |                         |                             |                 |                    | bit 0       |

| 1                  |                                      |                             |                         |                             |                 |                    |             |

| Legend:            | b.1. b.34                            |                             | L.14                    | II II.                      |                 | -l (Q)             |             |

| R = Reada          |                                      | W = Writable                |                         | -                           | mented bit, rea |                    |             |

| -n = Value         | at POR                               | '1' = Bit is set            |                         | '0' = Bit is cle            | eared           | x = Bit is unkn    | own         |

| bit 15             | TON: Timer5                          | On hit(3)                   |                         |                             |                 |                    |             |

| bit 10             | 1 = Starts 16-                       |                             |                         |                             |                 |                    |             |

|                    | 0 = Stops 16-                        |                             |                         |                             |                 |                    |             |

| bit 14             | Unimplemen                           | nted: Read as '             | 0'                      |                             |                 |                    |             |

| bit 13             | TSIDL: Time                          | r5 Stop in Idle I           | Node bit <sup>(2)</sup> |                             |                 |                    |             |

|                    |                                      | ues timer opera             |                         |                             | e mode          |                    |             |

|                    | 0 = Continue                         | s timer operatio            | on in Idle mode         | 9                           |                 |                    |             |

| bit 12-7           | Unimplemen                           | nted: Read as '             | 0'                      | (-)                         |                 |                    |             |

| bit 6              |                                      | er5 Gated Time              | Accumulation            | n Enable bit <sup>(3)</sup> |                 |                    |             |

|                    | <u>When TCS =</u><br>This bit is ign |                             |                         |                             |                 |                    |             |

|                    | When TCS =                           |                             |                         |                             |                 |                    |             |

|                    |                                      | <u>o.</u><br>ne accumulatio | n is enabled            |                             |                 |                    |             |

|                    | 0 = Gated tim                        | ne accumulatio              | n is disabled           |                             |                 |                    |             |

| bit 5-4            | TCKPS<1:0>                           | : Timer5 Input              | Clock Prescal           | e Select bits <sup>(3</sup> | )               |                    |             |

|                    |                                      | rescale value               |                         |                             |                 |                    |             |

|                    | 10 = 1:64 pre                        |                             |                         |                             |                 |                    |             |

|                    | 01 = 1:8 pres<br>00 = 1:1 pres       |                             |                         |                             |                 |                    |             |

| bit 3-2            | -                                    | nted: Read as '             | 0'                      |                             |                 |                    |             |

| bit 1              | -                                    | Clock Source                |                         |                             |                 |                    |             |

|                    |                                      | clock from T5C              |                         |                             |                 |                    |             |

|                    |                                      | lock (Fosc/2)               |                         |                             |                 |                    |             |

| bit 0              | Unimplemen                           | nted: Read as '             | 0'                      |                             |                 |                    |             |

| Note 1:            | This register is ava                 | ailable in dsPIC            | 33FJ32(GP/N             | IC)10X device               | es only.        |                    |             |

|                    | When 32-bit timer                    |                             |                         | -                           | -               | ster (T4CON<3>)    | , the TSIDL |

|                    | hit must be cleared                  | •                           | •                       | ,                           | Ŭ               | . ,                |             |

### REGISTER 12-4: T5CON: TIMER5 CONTROL REGISTER<sup>(1)</sup>

2: When 32-bit timer operation is enabled (132 = 1) in the Timer4 Control register (14CON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

**3:** When the 32-bit timer operation is enabled (T32 = 1) in the Timer4 Control register (T4CON<3>), these bits have no effect.

## 13.1 Input Capture Control Register

### **REGISTER 13-1: ICXCON: INPUT CAPTURE X CONTROL REGISTER**

| U-0            | U-0                                                                                   | R/W-0                                                                                                         | U-0                                                                                           | U-0                           | U-0              | U-0                | U-0   |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------|------------------|--------------------|-------|--|--|--|--|

| —              |                                                                                       | ICSIDL                                                                                                        | —                                                                                             |                               |                  |                    | —     |  |  |  |  |

| it 15          |                                                                                       |                                                                                                               |                                                                                               |                               |                  |                    | bit 8 |  |  |  |  |

|                |                                                                                       |                                                                                                               |                                                                                               |                               |                  |                    |       |  |  |  |  |

| R/W-0          | R/W-0                                                                                 | R/W-0                                                                                                         | R-0, HC                                                                                       | R-0, HC                       | R/W-0            | R/W-0              | R/W-0 |  |  |  |  |

| ICTMR          | ICI1                                                                                  | ICI0                                                                                                          | ICOV                                                                                          | ICBNE                         | ICM2             | ICM1               | ICM0  |  |  |  |  |

| it 7           |                                                                                       |                                                                                                               |                                                                                               |                               |                  |                    | bit ( |  |  |  |  |

| egend:         |                                                                                       | HC = Hardwa                                                                                                   | re Clearable I                                                                                | oit                           |                  |                    |       |  |  |  |  |

| R = Readable   | bit                                                                                   | W = Writable                                                                                                  | bit                                                                                           | U = Unimpler                  | nented bit, read | d as '0'           |       |  |  |  |  |

| n = Value at I | POR                                                                                   | '1' = Bit is set                                                                                              |                                                                                               | '0' = Bit is cle              | ared             | x = Bit is unkr    | nown  |  |  |  |  |

|                |                                                                                       |                                                                                                               |                                                                                               |                               |                  |                    |       |  |  |  |  |

| it 15-14       | Unimplemen                                                                            | ted: Read as '                                                                                                | )'                                                                                            |                               |                  |                    |       |  |  |  |  |

| it 13          | ICSIDL: Input                                                                         | t Capture x Sto                                                                                               | o in Idle Cont                                                                                | rol bit                       |                  |                    |       |  |  |  |  |

|                |                                                                                       | ture x module                                                                                                 |                                                                                               |                               |                  |                    |       |  |  |  |  |

|                |                                                                                       | ture x module                                                                                                 |                                                                                               | o operate in Cl               | PU Idle mode     |                    |       |  |  |  |  |

| it 12-8        | =                                                                                     | ted: Read as '                                                                                                |                                                                                               |                               |                  |                    |       |  |  |  |  |

| it 7           | •                                                                                     | Capture x Tim                                                                                                 |                                                                                               |                               |                  |                    |       |  |  |  |  |

|                |                                                                                       | ntents are capt<br>ntents are capt                                                                            |                                                                                               |                               |                  |                    |       |  |  |  |  |

| it 6-5         | ICI<1:0>: Select Number of Captures per Interrupt bits                                |                                                                                                               |                                                                                               |                               |                  |                    |       |  |  |  |  |

|                | 10 = Interrupt                                                                        | t on every fourt<br>t on every third                                                                          | capture even                                                                                  | t                             |                  |                    |       |  |  |  |  |

|                |                                                                                       | t on every seco<br>t on every captu                                                                           |                                                                                               | vent                          |                  |                    |       |  |  |  |  |

| it 4           | ICOV: Input C                                                                         | ICOV: Input Capture x Overflow Status Flag bit (read-only)                                                    |                                                                                               |                               |                  |                    |       |  |  |  |  |

|                |                                                                                       | ture x overflow<br>Capture x overf                                                                            |                                                                                               |                               |                  |                    |       |  |  |  |  |

| it 3           | ICBNE: Input                                                                          | Capture x Buff                                                                                                | er Empty Sta                                                                                  | tus bit (read-on              | ly)              |                    |       |  |  |  |  |

|                |                                                                                       | oture x buffer is<br>oture x buffer is                                                                        |                                                                                               | least one more                | e capture value  | can be read        |       |  |  |  |  |

| it 2-0         | ICM<2:0>: Inj                                                                         | put Capture x N                                                                                               | Node Select b                                                                                 | oits                          |                  |                    |       |  |  |  |  |

|                | edge c<br>110 = Unuse<br>101 = Captur<br>100 = Captur<br>011 = Captur<br>010 = Captur | detect only, all d<br>d (module is di<br>re mode, every<br>re mode, every<br>re mode, every<br>re mode, every | other control b<br>sabled)<br>16th rising e<br>4th rising edge<br>rising edge<br>falling edge | bits are not app<br>dge<br>ge | licable)         | s in Sleep or Idle |       |  |  |  |  |

|                |                                                                                       | s mode)<br>Capture x modu                                                                                     | ile is turned c                                                                               | off                           |                  |                    |       |  |  |  |  |

### 18.1 UART Helpful Tips

- In multi-node, direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 18.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en554109          |

#### 18.2.1 KEY RESOURCES

- "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33/PIC24 Family Reference Manual"* sections

- Development Tools

|                           | ) U-0                                                                                                                              | U-0                                                                                                                                             | R/W-0                                                            | R/W-0                                        | R/W-0                     | R/W-0    | R/W-0        |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------|---------------------------|----------|--------------|

| CSS15                     | (4)                                                                                                                                | —                                                                                                                                               |                                                                  |                                              | CSS<12:8> <sup>(4,6</sup> | 5)       |              |

| bit 15                    |                                                                                                                                    |                                                                                                                                                 |                                                                  |                                              |                           |          | bit 8        |

| R/W-0                     | ) R/W-0                                                                                                                            | R/W-0                                                                                                                                           | R/W-0                                                            | R/W-0                                        | R/W-0                     | R/W-0    | R/W-0        |

|                           |                                                                                                                                    |                                                                                                                                                 | CSS<7                                                            | 7:0> <sup>(4,5)</sup>                        |                           |          |              |

| bit 7                     |                                                                                                                                    |                                                                                                                                                 |                                                                  |                                              |                           |          | bit 0        |

| Legend:                   |                                                                                                                                    |                                                                                                                                                 |                                                                  |                                              |                           |          |              |

| R = Reada                 | able bit                                                                                                                           | W = Writable b                                                                                                                                  | it                                                               | U = Unimplen                                 | nented bit, rea           | d as '0' |              |

| -n = Value                | at POR                                                                                                                             | '1' = Bit is set                                                                                                                                |                                                                  | 0' = Bit is cleared x = Bit is unknown       |                           |          |              |

| <b>h</b> :+ 44 40         | 0 = Skips AN                                                                                                                       | Nx for input sca<br>k for input scan<br><b>ted:</b> Read as '0'                                                                                 |                                                                  |                                              |                           |          |              |

|                           |                                                                                                                                    | ieu. Neau as 0                                                                                                                                  |                                                                  |                                              |                           |          |              |

| bit 14-13<br>bit 12-0     | CSS<12:0>: /                                                                                                                       | ADC1 Input Sca<br>Nx for input sca                                                                                                              |                                                                  | <sub>Dits</sub> (4,5,6)                      |                           |          |              |

| bit 12-0                  | <b>CSS&lt;12:0&gt;:</b> /<br>1 = Selects A<br>0 = Skips AN2                                                                        | Nx for input sca<br>k for input scan                                                                                                            | n                                                                |                                              |                           |          |              |

|                           | <b>CSS&lt;12:0&gt;:</b> /<br>1 = Selects A                                                                                         | Nx for input sca<br>k for input scan<br>t 14 analog inpu                                                                                        | n<br>ts, all AD1CS                                               | SSL bits can be                              |                           |          | on. However, |

| bit 12-0                  | CSS<12:0>: /<br>1 = Selects A<br>0 = Skips AN<br>On devices withour                                                                | Nx for input sca<br>k for input scan<br>t 14 analog inpu<br>scan without a c                                                                    | n<br>ts, all AD1CS<br>correspondin                               | SSL bits can be                              |                           |          | on. However, |

| bit 12-0                  | CSS<12:0>: /<br>1 = Selects A<br>0 = Skips AN<br>On devices withour<br>inputs selected for<br>CSSx = ANx, when<br>CTMU temperature | Nx for input sca<br>x for input scan<br>t 14 analog input<br>scan without a<br>re x = 0 through<br>a sensor input c                             | n<br>ts, all AD1CS<br>correspondin<br>12 and 15.<br>annot be sca | SSL bits can be<br>g input on the d<br>nned. | evice converts            | S VREFL. |              |

| bit 12-0<br>Note 1:<br>2: | CSSx = ANx, when                                                                                                                   | Nx for input scan<br>x for input scan<br>t 14 analog input<br>scan without a c<br>re $x = 0$ through<br>e sensor input ca<br> ,8:6> bits are av | n<br>ts, all AD1CS<br>correspondin<br>12 and 15.<br>annot be sca | SSL bits can be<br>g input on the d<br>nned. | evice converts            | S VREFL. |              |

# REGISTER 19-6: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2,3)</sup>

they are reserved.

6: The CSS<10:9> bits are available on all devices, excluding the dsPIC33FJ16(GP/MC)101/102 devices, where they are reserved.

# REGISTER 21-10: ALRMVAL (WHEN ALRMPTR<1:0> = 00): ALARM MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| —      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                          |

|-----------|---------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| bit 7     | Unimplemented: Read as '0'                                          |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| Bit Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCP         | General Segment Code-Protect bit                                                                                                                                                                                                                                                                                                                                                                                    |

|             | <ul><li>1 = User program memory is not code-protected</li><li>0 = Code protection is enabled for the entire program memory space</li></ul>                                                                                                                                                                                                                                                                          |

| GWRP        | General Segment Write-Protect bit                                                                                                                                                                                                                                                                                                                                                                                   |

|             | <ul><li>1 = User program memory is not write-protected</li><li>0 = User program memory is write-protected</li></ul>                                                                                                                                                                                                                                                                                                 |

| IESO        | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Starts up device with FRC, then automatically switches to the user-selected oscillator source when ready</li> <li>0 = Starts up device with user-selected oscillator source</li> </ul>                                                                                                                                                               |

| PWMLOCK     | PWM Lock Enable bit                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | <ul><li>1 = Certain PWM registers may only be written after a key sequence</li><li>0 = PWM registers may be written without a key sequence</li></ul>                                                                                                                                                                                                                                                                |

| WDTWIN<1:0> | Watchdog Timer Window Select bits<br>11 = WDT window is 24% of WDT period<br>10 = WDT window is 37.5% of WDT period<br>01 = WDT window is 50% of WDT period<br>00 = WDT window is 75% of WDT period                                                                                                                                                                                                                 |

| FNOSC<2:0>  | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Reserved; do not use<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Secondary Oscillator (SOSC)<br>011 = Primary Oscillator with PLL module (MS + PLL, EC + PLL)<br>010 = Primary Oscillator (MS, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N and PLL module (FRCDIVN + PLL)<br>000 = Fast RC Oscillator (FRC) |

| FCKSM<1:0>  | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                   |

| IOL1WAY     | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                |

| OSCIOFNC    | OSC2 Pin Function bit (except in MS and HS modes)<br>1 = OSC2 is a clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                    |

| POSCMD<1:0> | Primary Oscillator Mode Select bits         11 = Primary Oscillator is disabled         10 = HS Crystal Oscillator mode (10 MHz-32 MHz)         01 = MS Crystal Oscillator mode (3 MHz-10 MHz)         00 = EC (External Clock) mode (DC-32 MHz)                                                                                                                                                                    |

| FWDTEN      | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled; clearing the SWDTEN bit in the RCON register will have no effect)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                          |

| WINDIS      | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                      |

### TABLE 23-4: dsPIC33F CONFIGURATION BITS DESCRIPTION

| DC CHARACTERISTICS |                    |                                      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |                    |      |                  |                                                            |  |

|--------------------|--------------------|--------------------------------------|-----------------------------------------------------------------------|--------------------|------|------------------|------------------------------------------------------------|--|

|                    | DC CHARACTERISTICS |                                      | Operati                                                               |                    |      |                  | $\leq$ TA $\leq$ +85°C for Industrial                      |  |

|                    | 1                  |                                      |                                                                       |                    |      | -40°C :          | $\leq$ TA $\leq$ +125°C for Extended                       |  |

| Param<br>No.       | Symbol             | Characteristic <sup>(3)</sup>        | Min                                                                   | Typ <sup>(1)</sup> | Max  | Units Conditions |                                                            |  |

|                    |                    | Program Flash Memory                 |                                                                       |                    |      |                  |                                                            |  |

| D130a              | Eр                 | Cell Endurance                       | 10,000                                                                | —                  | —    | E/W              | -40°C to +125°C                                            |  |

| D131               | Vpr                | VDD for Read                         | VMIN                                                                  | —                  | 3.6  | V                | VMIN = Minimum operating<br>voltage                        |  |

| D132b              | Vpew               | VDD for Self-Timed Write             | VMIN                                                                  | —                  | 3.6  | V                | VMIN = Minimum operating<br>voltage                        |  |

| D134               | Tretd              | Characteristic Retention             | 20                                                                    | _                  | —    | Year             | Provided no other specifications are violated              |  |

| D135               | IDDP               | Supply Current during<br>Programming | —                                                                     | 10                 | —    | mA               |                                                            |  |

| D137a              | TPE                | Page Erase Time                      | 20.1                                                                  | —                  | 26.5 | ms               | TPE = 168517 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>  |  |

| D137b              | TPE                | Page Erase Time                      | 19.5                                                                  | —                  | 27.3 | ms               | TPE = 168517 FRC cycles,<br>TA = +125°C, See <b>Note 2</b> |  |

| D138a              | Tww                | Word Write Cycle Time                | 47.4                                                                  | —                  | 49.3 | μs               | Tww = 355 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>     |  |

| D138b              | Tww                | Word Write Cycle Time                | 47.4                                                                  |                    | 49.3 | μs               | Tww = 355 FRC cycles,<br>TA = +125°C, See <b>Note 2</b>    |  |

#### TABLE 26-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: Other conditions: FRC = 7.37 MHz, TUN<5:0> = b'011111 (for Min), TUN<5:0> = b'100000 (for Max). This parameter depends on the FRC accuracy (see Table 26-18) and the value of the FRC Oscillator Tuning register (see Register 8-3). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

3: These parameters are ensured by design, but are not characterized or tested in manufacturing.

#### TABLE 26-13: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |                            |    |   |    |                                                          |

|--------------------|--------|----------------------------------------------------------|----------------------------|----|---|----|----------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristics                                          | Min Typ Max Units Comments |    |   |    |                                                          |

|                    | Cefc   | External Filter Capacitor<br>Value <sup>(1)</sup>        | 4.7                        | 10 | _ | μF | Capacitor must be low<br>series resistance<br>(< 5 ohms) |

**Note 1:** Typical VCAP voltage = 2.5V when VDD  $\ge$  VDDMIN.

| AC CHA       | RACTE         | RISTICS                                                                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |    |                | or Industrial     |                           |

|--------------|---------------|------------------------------------------------------------------------------------|-------------------------------------------------------|----|----------------|-------------------|---------------------------|