Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

· >< F

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 16 MIPs                                                                        |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                       |

| Number of I/O              | 15                                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 4x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 20-PDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16mc101-i-p |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. The following pages show their pinout diagrams.

|                  |      | rte)                  |              |                 | Rem                           | appa          | ble l          | Perip | herals                             | 5   | М                 |            | Ŋ                    |      |      |             |      |          |                                 |

|------------------|------|-----------------------|--------------|-----------------|-------------------------------|---------------|----------------|-------|------------------------------------|-----|-------------------|------------|----------------------|------|------|-------------|------|----------|---------------------------------|

| Device           | Pins | Program Flash (Kbyte) | RAM (Kbytes) | Remappable Pins | 16-bit Timer <sup>(1,2)</sup> | Input Capture | Output Compare | UART  | External Interrupts <sup>(3)</sup> | SPI | Motor Control PWM | PWM Faults | 10-Bit, 1.1 Msps ADC | RTCC | I²C™ | Comparators | CTMU | I/O Pins | Packages                        |

| dsPIC33FJ16GP101 | 18   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 13       | PDIP,<br>SOIC                   |

|                  | 20   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | SSOP                            |

| dsPIC33FJ16GP102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | _          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

| dsPIC33FJ16MC101 | 20   | 16                    | 1            | 10              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 1          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | PDIP,<br>SOIC,<br>SSOP          |

| dsPIC33FJ16MC102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

#### TABLE 1:dsPIC33FJ16(GP/MC)101/102 DEVICE FEATURES

**Note 1:** Two out of three timers are remappable.

2: One pair can be combined to create one 32-bit timer.

**3**: Two out of three interrupts are remappable.

NOTES:

#### 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70204) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33FJ16(GP/MC)101/102 The and dsPIC33FJ32(GP/MC)101/102/104 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can serve as a data, address, or address offset register. The 16th Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

There are two classes of instruction in the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices are capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model for the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 is shown in Figure 3-2.

#### 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program-to-data-space mapping feature lets any instruction access program space as if it were data space.

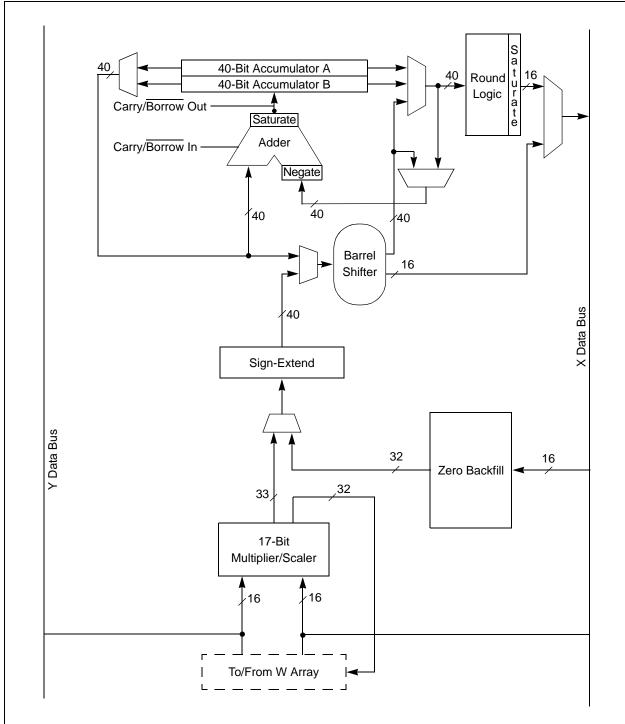

#### 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory, while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain Working registers to each address space.

#### 3.4 CPU Control Registers

| R-0                 | R-0                 | R/C-0                                  | R/C-0             | R-0                     | R/C-0              | R-0               | R/W-0         |

|---------------------|---------------------|----------------------------------------|-------------------|-------------------------|--------------------|-------------------|---------------|

| OA                  | OB                  | SA <sup>(1)</sup>                      | SB <sup>(1)</sup> | OAB                     | SAB                | DA                | DC            |

| bit 15              | ·                   |                                        |                   |                         |                    |                   | bit 8         |

| (2)                 | )) (2)              | (2)                                    |                   |                         |                    |                   |               |

| R/W-0 <sup>(3</sup> |                     | R/W-0 <sup>(3)</sup>                   | R-0               | R/W-0                   | R/W-0              | R/W-0             | R/W-0         |

| IPL2 <sup>(2)</sup> | IPL1 <sup>(2)</sup> | IPL0 <sup>(2)</sup>                    | RA                | N                       | OV                 | Z                 | С             |

| bit 7               |                     |                                        |                   |                         |                    |                   | bit (         |

| Legend:             |                     | C = Clearable                          | bit               |                         |                    |                   |               |

| R = Reada           | able bit            | W = Writable I                         | oit               | U = Unimpler            | mented bit, read   | l as '0'          |               |

| -n = Value          | at POR              | '1' = Bit is set                       |                   | '0' = Bit is cle        | ared               | x = Bit is unkn   | own           |

|                     |                     |                                        |                   |                         |                    |                   |               |

| bit 15              |                     | ator A Overflow                        |                   |                         |                    |                   |               |

|                     |                     | ator A has overf<br>ator A has not o   |                   |                         |                    |                   |               |

| bit 14              |                     | ator B Overflow                        |                   |                         |                    |                   |               |

| DIL 14              |                     | ator B has overf                       |                   |                         |                    |                   |               |

|                     |                     | ator B has not o                       |                   |                         |                    |                   |               |

| bit 13              | SA: Accumul         | ator A Saturatio                       | on 'Sticky' Sta   | itus bit <sup>(1)</sup> |                    |                   |               |

|                     | 1 = Accumula        | ator A is saturat                      | ed or has be      | en saturated at         | some time          |                   |               |

|                     |                     | ator A is not sat                      |                   | (4)                     |                    |                   |               |

| bit 12              |                     | ator B Saturatio                       |                   |                         |                    |                   |               |

|                     |                     | ator B is saturat<br>ator B is not sat |                   | en saturated at         | some time          |                   |               |

| bit 11              | <b>OAB:</b> OA    C | B Combined A                           | ccumulator C      | Verflow Status          | bit                |                   |               |

|                     |                     | ators A or B hav                       |                   |                         |                    |                   |               |

| bit 10              | <b>SAB:</b> SA    S | B Combined Ac                          | cumulator 'S      | ticky' Status bit       |                    |                   |               |

|                     |                     |                                        |                   |                         | urated at some     | time in the past  |               |

|                     |                     | ccumulator A o                         |                   |                         | it will clear SA a | and SB            |               |

| bit 9               | DA: DO LOOP         |                                        |                   | Cleaning this bi        |                    |                   |               |

|                     | 1 = DO loop is      |                                        |                   |                         |                    |                   |               |

|                     |                     | not in progres                         | 5                 |                         |                    |                   |               |

| bit 8               | DC: MCU AL          | U Half Carry/Bo                        | prrow bit         |                         |                    |                   |               |

|                     |                     |                                        | ow-order bit      | (for byte-sized o       | data) or 8th low-  | order bit (for wo | rd-sized data |

|                     |                     | sult occurred                          | h low-order       | hit (for hyte-siz       | ed data) or 8th    | low-order bit (f  | or word-sized |

|                     | •                   | he result occur                        |                   |                         |                    |                   |               |

| Note 1:             | This bit can be rea | nd or cleared (ne                      | ot set).          |                         |                    |                   |               |

|                     | The IPL<2:0> bits   |                                        |                   |                         |                    |                   |               |

|                     | Level. The value in | n parentheses i                        | ndicates the      | IPL if IPL<3> =         | 1. User interru    | ots are disabled  | when          |

|                     | IPL<3> = 1.         |                                        |                   |                         |                    |                   |               |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

**3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

| U-0             | U-0                            | U-0                                   | R/W-0           | R/W-0               | R-0              | R-0              | R-0   |

|-----------------|--------------------------------|---------------------------------------|-----------------|---------------------|------------------|------------------|-------|

| —               | —                              | _                                     | US              | EDT <sup>(1)</sup>  | DL2              | DL1              | DL0   |

| bit 15          |                                |                                       |                 |                     |                  |                  | bit   |

| R/W-0           | R/W-0                          | R/W-1                                 | R/W-0           | R/C-0               | R/W-0            | R/W-0            | R/W-0 |

| SATA            | SATB                           | SATDW                                 | ACCSAT          | IPL3 <sup>(2)</sup> | PSV              | R/W-0            | IF    |

| bit 7           | SAID                           | SAIDW                                 | ACCOAT          | IF L3. 7            | F3V              | RND              | bit   |

|                 |                                |                                       |                 |                     |                  |                  | Dit   |

| Legend:         |                                | C = Clearable                         | e bit           |                     |                  |                  |       |

| R = Readabl     | e bit                          | W = Writable                          | bit             | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is cle | ared                           | 'x = Bit is unk                       | nown            | U = Unimple         | mented bit, read | d as '0'         |       |

| bit 15-13       | Unimplemen                     | ted: Read as '                        | 0'              |                     |                  |                  |       |

| bit 12          | -                              | tiply Unsigned                        |                 | ol bit              |                  |                  |       |

|                 |                                | ne multiplies a                       | •               |                     |                  |                  |       |

|                 | 0 = DSP engi                   | ne multiplies a                       | ire signed      |                     |                  |                  |       |

| bit 11          |                                | Loop Termina                          |                 |                     |                  |                  |       |

|                 | 1 = Terminate<br>0 = No effect | es executing Do                       | o loop at the e | nd of current lo    | oop iteration    |                  |       |

| bit 10-8        | DL<2:0>: DO                    | Loop Nesting                          | Level Status b  | its                 |                  |                  |       |

|                 | 111 <b>= 7</b> DO <b>lo</b>    | ops are active                        |                 |                     |                  |                  |       |

|                 | •                              |                                       |                 |                     |                  |                  |       |

|                 | •<br>001 = 1 DO lo             | on is activo                          |                 |                     |                  |                  |       |

|                 |                                | ops are active                        |                 |                     |                  |                  |       |

| bit 7           | SATA: ACCA                     | Saturation En                         | able bit        |                     |                  |                  |       |

|                 |                                | itor A saturatio                      |                 |                     |                  |                  |       |

|                 |                                | itor A saturatio                      |                 |                     |                  |                  |       |

| bit 6           |                                | Saturation En                         |                 |                     |                  |                  |       |

|                 |                                | tor B saturatio                       |                 |                     |                  |                  |       |

| bit 5           |                                |                                       |                 | ine Saturation      | Enable bit       |                  |       |

|                 |                                | ce write satura                       |                 |                     |                  |                  |       |

|                 |                                | ce write satura                       |                 |                     |                  |                  |       |

| bit 4           | ACCSAT: Acc                    | cumulator Satu                        | uration Mode S  | Select bit          |                  |                  |       |

|                 |                                | ration (super s                       |                 |                     |                  |                  |       |

| L:1 0           |                                | ration (normal                        | ,               | ··· (2)             |                  |                  |       |

| bit 3           |                                | terrupt Priority<br>rrupt Priority Le |                 |                     |                  |                  |       |

|                 |                                | rupt Priority Le                      | •               |                     |                  |                  |       |

| bit 2           |                                |                                       |                 | ace Enable bit      |                  |                  |       |

|                 |                                | space is visible                      |                 |                     |                  |                  |       |

|                 | -                              | space is not vi                       |                 | pace                |                  |                  |       |

| bit 1           |                                | ng Mode Sele                          |                 |                     |                  |                  |       |

|                 |                                | onventional) ro<br>(convergent)       |                 |                     |                  |                  |       |

| bit 0           | IF: Integer or                 | Fractional Mul                        | tiplier Mode S  | elect bit           |                  |                  |       |

|                 | -                              |                                       |                 | iply operations     |                  |                  |       |

|                 | 0 = Fractional                 | l mode is enab                        | led for DSP m   | nultiply operation  | ons              |                  |       |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 ALU is 16 bits wide, and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-Bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.5.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or Integer DSP Multiply (IF)

- Signed or Unsigned DSP Multiply (US)

- · Conventional or Convergent Rounding (RND)

- · Automatic Saturation On/Off for ACCA (SATA)

- Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

A block diagram of the DSP engine is shown in Figure 3-3.

| TABLE 3-1: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

| Instruction | Algebraic<br>Operation | ACC Write<br>Back |

|-------------|------------------------|-------------------|

| CLR         | A = 0                  | Yes               |

| ED          | $A = (x - y)^2$        | No                |

| EDAC        | $A = A + (x - y)^2$    | No                |

| MAC         | A = A + (x * y)        | Yes               |

| MAC         | $A = A + x^2$          | No                |

| MOVSAC      | No change in A         | Yes               |

| MPY         | A = x * y              | No                |

| MPY         | $A = x^2$              | No                |

| MPY.N       | A = -x * y             | No                |

| MSC         | A = A - x * y          | Yes               |

#### FIGURE 3-3: DSP ENGINE BLOCK DIAGRAM

# DS70000652F-page 66

#### TABLE 4-18: CTMU REGISTER MAP

| F | ile Name       | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

|---|----------------|-------------|---------|---------|----------|----------|----------|----------|----------|----------|---------|---------|----------|----------|----------|----------|-------|-------|---------------|

| C | FMUCON1        | 033A        | CTMUEN  | _       | CTMUSIDL | TGEN     | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | _       |          | -        | _        | -        | _     | _     | 0000          |

| C | FMUCON2        | 033C        | EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 |       |       | 0000          |

| C | <b>FMUICON</b> | 033E        | ITRIM5  | ITRIM4  | ITRIM3   | ITRIM2   | ITRIM1   | ITRIM0   | IRNG1    | IRNG0    | —       | —       | -        |          | _        |          |       | -     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-19: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File Name | SFR<br>Addr | Bit 15 | Bit 14                                            | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9         | Bit 8       | Bit 7     | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------------|--------|---------------------------------------------------|---------|---------|---------|--------|---------------|-------------|-----------|----------|-------|-------|-------|-------|-------|-------|---------------|

| ALRMVAL   | 0620        |        | Alarm Value Register Window based on ALRMPTR<1:0> |         |         |         |        |               |             |           |          |       |       |       |       |       |       | xxxx          |

| ALCFGRPT  | 0622        | ALRMEN |                                                   |         |         |         |        |               |             |           |          |       |       |       |       | 0000  |       |               |

| RTCVAL    | 0624        |        |                                                   |         |         |         | RTCC V | alue Register | Window base | d on RTCF | PTR<1:0> |       |       |       |       |       |       | xxxx          |

| RCFGCAL   | 0626        | RTCEN  | —                                                 | RTCWREN | RTCSYNC | HALFSEC | RTCOE  | RTCPTR1       | RTCPTR0     | CAL7      | CAL6     | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-20: PAD CONFIGURATION REGISTER MAP

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|-----------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------|-------|---------------|

| PADCFG1   | 02FC        | _      |        |        |        | _      | _      | _     | -     | _     |       | _     |       |       | _     | RTSECSEL | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| I  | File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|----|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| TR | RISA         | 02C0        |        |        | —      | -      | _      |        | TRISA< | 10:7> |       |       | —     |       |       | TRISA<4:0> |       |       | 001F          |

| PC | ORTA         | 02C2        |        |        | —      |        | _      |        | RA<10  | ):7>  |       | —     | _     |       |       | RA<4:0>    |       |       | xxxx          |

| LA | TA           | 02C4        | _      | _      | _      | _      | -      |        | LATA<1 | 0:7>  |       | —     | _     |       |       | LATA<4:0>  |       |       | xxxx          |

| O  | DCA          | 02C6        |        |        | _      | _      | _      |        | ODCA<  | 10:7> |       | _     | _     |       | ODCA  | <3:2>      |       |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-30: PORTB REGISTER MAP FOR dsPIC33FJ16GP101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|---------|--------|--------|--------|--------|-----------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        | TRISB< | :15:14> | _      | _      | _      | _      | -         | TRISB<9:7 | >     | _     | _     | TRISB4 | _     | _     | TRISE | 3<1:0> | C393          |

| PORTB     | 02CA        | RB<1   | 5:14>   | _      | _      | _      | _      |           | RB<9:7>   |       | _     | _     | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        | LATB<  | 15:14>  | _      | _      | —      | —      | LATB<9:7> |           |       | _     | LATB4 | —      | _     | LATB  | <1:0> | xxxx   |               |

| ODCB      | 02CE        | ODCB<  | :15:14> | _      | _      | -      | -      | ODCB<9:7> |           |       | _     | ODCB4 | _      | _     | _     |       | 0000   |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-31: PORTB REGISTER MAP FOR dsPIC33FJ16MC101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|--------|---------|--------|--------|--------|-------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        |        | TRISB< | <15:12> |        | _      | _      | 1     | RISB<9:7: | >     | _     | _     | TRISB4 | _     | —     | TRISE | 3<1:0> | F393          |

| PORTB     | 02CA        |        | RB<1   | 5:12>   |        |        | _      |       | RB<9:7>   |       | _     |       | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        |        | LATB<  | 15:12>  |        |        | _      |       | LATB<9:7> | •     | _     |       | LATB4  | _     | _     | LATB  | <1:0>  | xxxx          |

| ODCB      | 02CE        |        | ODCB<  | <15:12> |        |        | _      | (     | DDCB<9:7: | >     | -     | _     | ODCB4  |       | _     |       |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-32: PORTB REGISTER MAP FOR dsPIC33FJ16(GP/MC)102 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB        | 02C8        |        |        |        |        |        |        |        | TRISB< | :15:0> |       |       |       |       |       |       |       | FFFF          |

| PORTB        | 02CA        |        |        |        |        |        |        |        | RB<1   | 5:0>   |       |       |       |       |       |       |       | xxxx          |

| LATB         | 02CC        |        |        |        |        |        |        |        | LATB<  | 15:0>  |       |       |       |       |       |       |       | xxxx          |

| ODCB         | 02CE        |        |        |        |        |        | ODCB<  | :15:4> |        |        |       |       |       | _     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed, but the contents of the register remain unchanged.

#### 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWM<3:0> bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the bit-reversed address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

**Note:** All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XB<14:0> value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing should not be enabled together. If an application attempts to do so, Bit-Reversed Addressing will assume priority when active. For the X WAGU and Y AGU, Modulo Addressing will be disabled. However, Modulo Addressing will continue to function in the X RAGU.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### 5.2 RTSP Operation

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions); and to program one word. Table 26-12 shows typical erase and programming times. The 8-row erase pages are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes.

#### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the operation is finished.

The programming time depends on the FRC accuracy (see Table 26-18) and the value of the FRC Oscillator Tuning register (see Register 8-3). Use the following formula to calculate the minimum and maximum values for the Word write time and page erase time (see Parameters D138a and D138b, and Parameters D137a and D137b in Table 26-12, respectively).

#### EQUATION 5-1: PROGRAMMING TIME

$\frac{T}{7.37 \text{ MHz} \times (FRC \text{ Accuracy})\% \times (FRC \text{ Tuning})\%}$

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 2\%$ . If the TUN<5:0> bits (see Register 8-3) are set to `b000000, the minimum row write time is equal to Equation 5-2.

#### EQUATION 5-2: MINIMUM ROW WRITE TIME

$T_{RW} = \frac{355 \ Cycles}{7.37 \ MHz \times (1 + 0.02) \times (1 - 0.00375)} = 47.4 \mu s$

The maximum row write time is equal to Equation 5-3.

# EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{355 \ Cycles}{7.37 \ MHz \times (1 - 0.02) \times (1 - 0.00375)} = 49.3 \mu s$$

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program one word (24 bits) of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

| Note: | Performing a page erase operation on the   |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | last page of program memory will clear the |  |  |  |  |  |  |  |  |

|       | Flash Configuration Words, thereby         |  |  |  |  |  |  |  |  |

|       | enabling code protection as a result.      |  |  |  |  |  |  |  |  |

|       | Therefore, users should avoid performing   |  |  |  |  |  |  |  |  |

|       | page erase operations on the last page of  |  |  |  |  |  |  |  |  |

|       | program memory.                            |  |  |  |  |  |  |  |  |

Refer to **"Flash Programming"** (DS70191) in the *"dsPIC33/PIC24 Family Reference Manual"* for details and codes examples on programming using RTSP.

#### 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

| U-0          | U-0                                                                                                                                                             | U-0                                                        | U-0             | U-0              | U-0              | U-0            | U-0     |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|------------------|------------------|----------------|---------|--|--|--|--|

| _            | —                                                                                                                                                               | _                                                          | _               |                  | —                | —              | —       |  |  |  |  |

| oit 15       |                                                                                                                                                                 |                                                            |                 |                  |                  |                | bit     |  |  |  |  |

|              |                                                                                                                                                                 |                                                            |                 |                  |                  |                |         |  |  |  |  |

| U-0          | R/W-1                                                                                                                                                           | R/W-0                                                      | R/W-0           | U-0              | R/W-1            | R/W-0          | R/W-0   |  |  |  |  |

| —            | AD1IP2                                                                                                                                                          | AD1IP1                                                     | AD1IP0          |                  | U1TXIP2          | U1TXIP1        | U1TXIP0 |  |  |  |  |

| bit 7        |                                                                                                                                                                 |                                                            |                 |                  |                  |                | bit     |  |  |  |  |

| Legend:      |                                                                                                                                                                 |                                                            |                 |                  |                  |                |         |  |  |  |  |

| R = Readat   | ole bit                                                                                                                                                         | W = Writable                                               | bit             | U = Unimpler     | mented bit, read | 1 as '0'       |         |  |  |  |  |

| -n = Value a | at POR                                                                                                                                                          | '1' = Bit is set                                           |                 | '0' = Bit is cle |                  | x = Bit is unk | nown    |  |  |  |  |

|              | •<br>•<br>001 = Interru                                                                                                                                         | pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis |                 | ty interrupt)    |                  |                |         |  |  |  |  |

| bit 3        | Unimplemen                                                                                                                                                      | ted: Read as '                                             | 0'              |                  |                  |                |         |  |  |  |  |

| bit 2-0      | U1TXIP<2:0>                                                                                                                                                     | : UART1 Tran                                               | smitter Interru | pt Priority bits |                  |                |         |  |  |  |  |

|              | U1TXIP<2:0>: UART1 Transmitter Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)<br>•<br>•<br>001 = Interrupt is Priority 1 |                                                            |                 |                  |                  |                |         |  |  |  |  |

#### REGISTER 7-18: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

|               | _             | -                  | -                            |                  |                      |                      |                      |

|---------------|---------------|--------------------|------------------------------|------------------|----------------------|----------------------|----------------------|

| U-0           | U-0           | U-0                | U-0                          | U-0              | U-0                  | U-0                  | U-0                  |

| _             | —             |                    |                              | _                | _                    | _                    | _                    |

| bit 15        |               |                    |                              | •                |                      |                      | bit 8                |

|               |               |                    |                              |                  |                      |                      |                      |

| U-0           | R/W-1         | R/W-0              | R/W-0                        | U-0              | R/W-1                | R/W-0                | R/W-0                |

|               | INT2IP2       | INT2IP1            | INT2IP0                      | —                | T5IP2 <sup>(1)</sup> | T5IP1 <sup>(1)</sup> | T5IP0 <sup>(1)</sup> |

| bit 7         |               |                    |                              |                  | ·                    |                      | bit 0                |

|               |               |                    |                              |                  |                      |                      |                      |

| Legend:       |               |                    |                              |                  |                      |                      |                      |

| R = Readable  | e bit         | W = Writable       | bit                          | U = Unimple      | mented bit, read     | l as '0'             |                      |

| -n = Value at | POR           | '1' = Bit is set   |                              | '0' = Bit is cle | eared                | x = Bit is unkr      | nown                 |

|               |               |                    |                              |                  |                      |                      |                      |

| bit 15-7      | Unimplemen    | ted: Read as '     | 0'                           |                  |                      |                      |                      |

| bit 6-4       | INT2IP<2:0>:  | External Inter     | rupt 2 Priority              | bits             |                      |                      |                      |

|               | 111 = Interru | pt is Priority 7 ( | highest priorit              | ty interrupt)    |                      |                      |                      |

|               | •             |                    |                              |                  |                      |                      |                      |

|               | •             |                    |                              |                  |                      |                      |                      |

|               | 001 = Interru | pt is Priority 1   |                              |                  |                      |                      |                      |

|               | 000 = Interru | pt source is dis   | abled                        |                  |                      |                      |                      |

| bit 3         | Unimplemen    | ted: Read as '     | 0'                           |                  |                      |                      |                      |

| bit 2-0       | T5IP<2:0>: ⊺  | ïmer5 Interrupt    | Priority bits <sup>(1)</sup> | )                |                      |                      |                      |

|               | 111 = Interru | pt is Priority 7 ( | highest priorit              | ty interrupt)    |                      |                      |                      |

|               | •             |                    |                              |                  |                      |                      |                      |

|               | •             |                    |                              |                  |                      |                      |                      |

|               | 001 = Interru | pt is Priority 1   |                              |                  |                      |                      |                      |

|               |               | pt source is dis   | abled                        |                  |                      |                      |                      |

|               | 1.1           |                    |                              |                  |                      |                      |                      |

#### REGISTER 7-22: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

**Note 1:** These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

| R-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0                                    | R/W-0           | R/W-0    | R/W-0 |

|-----------------|-------|------------------|-------|------------------------------------------|-----------------|----------|-------|

| PTDIR           |       |                  |       | PTMR<14:8>                               |                 |          |       |

| bit 15          |       |                  |       |                                          |                 |          | bit 8 |

|                 |       |                  |       |                                          |                 |          |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                    | R/W-0           | R/W-0    | R/W-0 |

|                 |       |                  | PTM   | R<7:0>                                   |                 |          |       |

| bit 7           |       |                  |       |                                          |                 |          | bit 0 |

| Legend:         |       |                  |       |                                          |                 |          |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen                             | nented bit, rea | d as '0' |       |

| -n = Value at P | POR   | '1' = Bit is set |       | 0' = Bit is cleared $x = Bit is unknown$ |                 |          | nown  |

#### REGISTER 15-2: PxTMR: PWMx TIMER COUNT VALUE REGISTER

| bit 15   | PTDIR: PWMx Time Base Count Direction Status bit (read-only) |

|----------|--------------------------------------------------------------|

|          | 1 = PWMx time base is counting down                          |

|          | 0 = PWMx time base is counting up                            |

| bit 14-0 | PTMR <14:0>: PWMx Time Base Register Count Value bits        |

#### REGISTER 15-3: PxTPER: PWMx TIME BASE PERIOD REGISTER

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      |       |       |       | PTPER<14:8 | >     |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | PTPE  | R<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

bit 14-0 **PTPER<14:0>:** PWMx Time Base Period Value bits

| R/W-0                  | R/W-0 | R/W-0            | R/W-0 | R/W-0                  | R/W-0          | R/W-0           | R/W-0 |

|------------------------|-------|------------------|-------|------------------------|----------------|-----------------|-------|

| SEVTDIR <sup>(1)</sup> |       |                  | S     | SEVTCMP<14:8>          | (2)            |                 |       |

| bit 15                 |       |                  |       |                        |                |                 | bit 8 |

|                        |       |                  |       |                        |                |                 |       |

| R/W-0                  | R/W-0 | R/W-0            | R/W-0 | R/W-0                  | R/W-0          | R/W-0           | R/W-0 |

|                        |       |                  | SEVTC | ИР<7:0> <sup>(2)</sup> |                |                 |       |

| bit 7                  |       |                  |       |                        |                |                 | bit 0 |

| Logondi                |       |                  |       |                        |                |                 |       |

| Legend:                | L : 4 |                  |       |                        |                | -l (0)          |       |

| R = Readable           | bit   | W = Writable b   | bit   | U = Unimplem           | ented bit, rea | id as '0'       |       |

| -n = Value at          |       | '1' = Bit is set |       | '0' = Bit is clea      | red            | x = Bit is unkr | nown  |

#### REGISTER 15-4: PxSECMP: PWMx SPECIAL EVENT COMPARE REGISTER

0 = A Special Event Trigger will occur when the PWMx time base is counting up

bit 14-0 SEVTCMP<14:0>: Special Event Compare Value bits<sup>(2)</sup>

**Note 1:** SEVTDIR is compared with PTDIR (PxTMR<15>) to generate the Special Event Trigger.

2: PxSECMP<14:0> is compared with PxTMR<14:0> to generate the Special Event Trigger.

|                                                 | U-0                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                        | R/W-0                                                        | R/W-0                                            |  |  |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------|--|--|--|--|