#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 15                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 4x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 20-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16mc101-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED) |             |                   |           |                                                                                                                                       |  |  |  |  |

|------------------------------------------------|-------------|-------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                       | Pin<br>Type | Buffer<br>Type    | PPS       | Description                                                                                                                           |  |  |  |  |

| SCL1                                           | I/O         | ST                | No        | Synchronous serial clock input/output for I2C1.                                                                                       |  |  |  |  |

| SDA1                                           | I/O         | ST                | No        | Synchronous serial data input/output for I2C1.                                                                                        |  |  |  |  |

| ASCL1                                          | I/O         | ST                | No        | Alternate synchronous serial clock input/output for I2C1.                                                                             |  |  |  |  |

| ASDA1                                          | I/O         | ST                | No        | Alternate synchronous serial data input/output for I2C1.                                                                              |  |  |  |  |

| FLTA1(1,2,4)                                   | 1           | ST                | No        | PWM1 Fault A input.                                                                                                                   |  |  |  |  |

| FLTB1 <sup>(3,4)</sup>                         | 1           | ST                | No        | PWM1 Fault B input.                                                                                                                   |  |  |  |  |

| PWM1L1                                         | 0           |                   | No        | PWM1 Low Output 1.                                                                                                                    |  |  |  |  |

| PWM1H1                                         | 0           |                   | No        | PWM1 High Output 1.                                                                                                                   |  |  |  |  |

| PWM1L2                                         | 0           |                   | No        | PWM1 Low Output 2.                                                                                                                    |  |  |  |  |

| PWM1H2                                         | 0           |                   | No        | PWM1 High Output 2.                                                                                                                   |  |  |  |  |

| PWM1L3                                         | 0           |                   | No        | PWM1 Low Output 3.                                                                                                                    |  |  |  |  |

| PWM1H3                                         | Ō           | _                 | No        | PWM1 High Output 3.                                                                                                                   |  |  |  |  |

| RTCC                                           | 0           | Digital           | No        | RTCC Alarm output.                                                                                                                    |  |  |  |  |

| CTPLS                                          | 0           | Digital           | Yes       | CTMU pulse output.                                                                                                                    |  |  |  |  |

| CTED1                                          | I           | Digital           | No        | CTMU External Edge Input 1.                                                                                                           |  |  |  |  |

| CTED2                                          | I           | Digital           | No        | CTMU External Edge Input 2.                                                                                                           |  |  |  |  |

| CVREFIN                                        | I           | Analog            | No        | Comparator Voltage Positive Reference Input.                                                                                          |  |  |  |  |

| CVREFOUT                                       | 0           | Analog            | No        | Comparator Voltage Positive Reference Output.                                                                                         |  |  |  |  |

| C1INA                                          | I           | Analog            | No        | Comparator 1 Positive Input A.                                                                                                        |  |  |  |  |

| C1INB                                          | i           | Analog            | No        | Comparator 1 Negative Input B.                                                                                                        |  |  |  |  |

| C1INC                                          | i           | Analog            | No        | Comparator 1 Negative Input C.                                                                                                        |  |  |  |  |

| C1IND                                          | i           | Analog            | No        | Comparator 1 Negative Input D.                                                                                                        |  |  |  |  |

| C1OUT                                          | Ō           | Digital           | Yes       | Comparator 1 Output.                                                                                                                  |  |  |  |  |

| C2INA                                          | Ĩ           | Analog            | No        | Comparator 2 Positive Input A.                                                                                                        |  |  |  |  |

| C2INB                                          | l i         | Analog            | No        | Comparator 2 Negative Input B.                                                                                                        |  |  |  |  |

| C2INC                                          | i           | Analog            | No        | Comparator 2 Negative Input D.                                                                                                        |  |  |  |  |

| C2INC<br>C2IND                                 |             | Analog            | No        | Comparator 2 Negative Input C.                                                                                                        |  |  |  |  |

| C2OUT                                          | 0           | Digital           | Yes       | Comparator 2 Output.                                                                                                                  |  |  |  |  |

|                                                |             | •                 |           |                                                                                                                                       |  |  |  |  |

| C3INA                                          |             | Analog            | No        | Comparator 3 Positive Input A.                                                                                                        |  |  |  |  |

| C3INB                                          |             | Analog            | No        | Comparator 3 Negative Input B.                                                                                                        |  |  |  |  |

| C3INC                                          |             | Analog            | No        | Comparator 3 Negative Input C.                                                                                                        |  |  |  |  |

| C3IND<br>C3OUT                                 |             | Analog<br>Digital | No<br>Yes | Comparator 3 Negative Input D.<br>Comparator 3 Output.                                                                                |  |  |  |  |

|                                                |             | ST                |           | Data I/O pin for Programming/Debugging Communication Channel 1.                                                                       |  |  |  |  |

| PGED1                                          | I/O         |                   | No        |                                                                                                                                       |  |  |  |  |

| PGEC1                                          |             | ST                | No        | Clock input pin for Programming/Debugging Communication Channel 1.                                                                    |  |  |  |  |

| PGED2                                          | I/O         | ST                | No        | Data I/O pin for Programming/Debugging Communication Channel 2.                                                                       |  |  |  |  |

| PGEC2                                          | I           | ST                | No        | Clock input pin for Programming/Debugging Communication Channel 2.                                                                    |  |  |  |  |

| PGED3<br>PGEC3                                 | I/O         | ST<br>ST          | No<br>No  | Data I/O pin for Programming/Debugging Communication Channel 3.<br>Clock input pin for Programming/Debugging Communication Channel 3. |  |  |  |  |

|                                                | - ·         |                   |           |                                                                                                                                       |  |  |  |  |

| MCLR                                           | I/P         | ST                | No        | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                            |  |  |  |  |

|                                                |             |                   |           | input or output Analog = Analog input P = Power                                                                                       |  |  |  |  |

| S                                              | I = Schr    | nitt Frigger      | input w   | ith CMOS levels O = Output I = Input                                                                                                  |  |  |  |  |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: An external pull-down resistor is required for the FLTA1 pin in dsPIC33FJXXMC101 (20-pin) devices.

- 2: The FLTA1 pin and the PWM1Lx/PWM1Hx pins are available in dsPIC(16/32)MC10X devices only.

- 3: The FLTB1 pin is available in dsPIC(16/32)MC102/104 devices only.

PPS = Peripheral Pin Select

- 4: The PWM Fault pins are enabled during any Reset event. Refer to **Section 15.2 "PWM Faults"** for more information on the PWM Faults.

- 5: Not all pins are available on all devices. Refer to the specific device in the "**Pin Diagrams**" section for availability.

- 6: These pins are available in dsPIC33FJ32(GP/MC)104 (44-pin) devices only.

| U-0             | U-0                            | U-0                                   | R/W-0           | R/W-0               | R-0              | R-0              | R-0   |

|-----------------|--------------------------------|---------------------------------------|-----------------|---------------------|------------------|------------------|-------|

| —               | —                              | _                                     | US              | EDT <sup>(1)</sup>  | DL2              | DL1              | DL0   |

| bit 15          |                                |                                       |                 |                     |                  |                  | bit   |

| R/W-0           | R/W-0                          | R/W-1                                 | R/W-0           | R/C-0               | R/W-0            | R/W-0            | R/W-0 |

| SATA            | SATB                           | SATDW                                 | ACCSAT          | IPL3 <sup>(2)</sup> | PSV              | R/W-0            | IF    |

| bit 7           | SAID                           | SAIDW                                 | ACCOAT          | IF L3. 7            | F3V              | RND              | bit   |

|                 |                                |                                       |                 |                     |                  |                  | Dit   |

| Legend:         |                                | C = Clearable                         | e bit           |                     |                  |                  |       |

| R = Readabl     | e bit                          | W = Writable                          | bit             | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is cle | ared                           | 'x = Bit is unk                       | nown            | U = Unimple         | mented bit, read | d as '0'         |       |

| bit 15-13       | Unimplemen                     | ted: Read as '                        | 0'              |                     |                  |                  |       |

| bit 12          | -                              | tiply Unsigned                        |                 | ol bit              |                  |                  |       |

|                 |                                | ne multiplies a                       | •               |                     |                  |                  |       |

|                 | 0 = DSP engi                   | ne multiplies a                       | ire signed      |                     |                  |                  |       |

| bit 11          |                                | Loop Termina                          |                 |                     |                  |                  |       |

|                 | 1 = Terminate<br>0 = No effect | es executing Do                       | o loop at the e | nd of current lo    | oop iteration    |                  |       |

| bit 10-8        | DL<2:0>: DO                    | Loop Nesting                          | Level Status b  | its                 |                  |                  |       |

|                 | 111 <b>= 7</b> DO <b>lo</b>    | ops are active                        |                 |                     |                  |                  |       |

|                 | •                              |                                       |                 |                     |                  |                  |       |

|                 | •<br>001 = 1 DO lo             | on is activo                          |                 |                     |                  |                  |       |

|                 |                                | ops are active                        |                 |                     |                  |                  |       |

| bit 7           | SATA: ACCA                     | Saturation En                         | able bit        |                     |                  |                  |       |

|                 |                                | itor A saturatio                      |                 |                     |                  |                  |       |

|                 |                                | itor A saturatio                      |                 |                     |                  |                  |       |

| bit 6           |                                | Saturation En                         |                 |                     |                  |                  |       |

|                 |                                | tor B saturatio                       |                 |                     |                  |                  |       |

| bit 5           |                                |                                       |                 | ine Saturation      | Enable bit       |                  |       |

|                 |                                | ce write satura                       |                 |                     |                  |                  |       |

|                 |                                | ce write satura                       |                 |                     |                  |                  |       |

| bit 4           | ACCSAT: Acc                    | cumulator Satu                        | uration Mode S  | Select bit          |                  |                  |       |

|                 |                                | ration (super s                       |                 |                     |                  |                  |       |

| L:1 0           |                                | ration (normal                        | ,               | ··· (2)             |                  |                  |       |

| bit 3           |                                | terrupt Priority<br>rrupt Priority Le |                 |                     |                  |                  |       |

|                 |                                | rupt Priority Le                      | •               |                     |                  |                  |       |

| bit 2           |                                |                                       |                 | ace Enable bit      |                  |                  |       |

|                 |                                | space is visible                      |                 |                     |                  |                  |       |

|                 | -                              | space is not vi                       |                 | pace                |                  |                  |       |

| bit 1           |                                | ng Mode Sele                          |                 |                     |                  |                  |       |

|                 |                                | onventional) ro<br>(convergent)       |                 |                     |                  |                  |       |

| bit 0           | IF: Integer or                 | Fractional Mul                        | tiplier Mode S  | elect bit           |                  |                  |       |

|                 | -                              |                                       |                 | iply operations     |                  |                  |       |

|                 | 0 = Fractional                 | l mode is enab                        | led for DSP m   | nultiply operation  | ons              |                  |       |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8        | Bit 7        | Bit 6  | Bit 5     | Bit 4         | Bit 3        | Bit 2        | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|---------|--------------|--------------|--------|-----------|---------------|--------------|--------------|---------|-------|---------------|

| WREG0    | 0000        |        |        |        |        |        |        |         | Working Re   | egister 0    |        |           |               |              |              |         |       | xxxx          |

| WREG1    | 0002        |        |        |        |        |        |        |         | Working Re   | egister 1    |        |           |               |              |              |         |       | xxxx          |

| WREG2    | 0004        |        |        |        |        |        |        |         | Working Re   | egister 2    |        |           |               |              |              |         |       | xxxx          |

| WREG3    | 0006        |        |        |        |        |        |        |         | Working Re   | egister 3    |        |           |               |              |              |         |       | xxxx          |

| WREG4    | 0008        |        |        |        |        |        |        |         | Working Re   | egister 4    |        |           |               |              |              |         |       | xxxx          |

| WREG5    | 000A        |        |        |        |        |        |        |         | Working Re   | egister 5    |        |           |               |              |              |         |       | xxxx          |

| WREG6    | 000C        |        |        |        |        |        |        |         | Working Re   | egister 6    |        |           |               |              |              |         |       | xxxx          |

| WREG7    | 000E        |        |        |        |        |        |        |         | Working Re   | egister 7    |        |           |               |              |              |         |       | xxxx          |

| WREG8    | 0010        |        |        |        |        |        |        |         | Working Re   | egister 8    |        |           |               |              |              |         |       | xxxx          |

| WREG9    | 0012        |        |        |        |        |        |        |         | Working Re   | egister 9    |        |           |               |              |              |         |       | xxxx          |

| WREG10   | 0014        |        |        |        |        |        |        |         | Working Re   | gister 10    |        |           |               |              |              |         |       | xxxx          |

| WREG11   | 0016        |        |        |        |        |        |        |         | Working Re   | gister 11    |        |           |               |              |              |         |       | xxxx          |

| WREG12   | 0018        |        |        |        |        |        |        |         | Working Re   | gister 12    |        |           |               |              |              |         |       | xxxx          |

| WREG13   | 001A        |        |        |        |        |        |        |         | Working Re   | gister 13    |        |           |               |              |              |         |       | xxxx          |

| WREG14   | 001C        |        |        |        |        |        |        |         | Working Re   | gister 14    |        |           |               |              |              |         |       | xxxx          |

| WREG15   | 001E        |        |        |        |        |        |        |         | Working Re   | gister 15    |        |           |               |              |              |         |       | 0800          |

| SPLIM    | 0020        |        |        |        |        |        |        | Sta     | ck Pointer L | imit Registe | r      |           |               |              |              |         |       | XXXX          |

| ACCAL    | 0022        |        |        |        |        |        |        | Accum   | ulator A Lov | v Word Reg   | ister  |           |               |              |              |         |       | XXXX          |

| ACCAH    | 0024        |        |        |        |        |        |        | Accum   | ulator A Hig | h Word Reg   | ister  |           |               |              |              |         |       | XXXX          |

| ACCAU    | 0026        |        |        |        |        |        |        | Accumu  | ulator A Upp | er Word Re   | gister |           |               |              |              |         |       | xxxx          |

| ACCBL    | 0028        |        |        |        |        |        |        | Accum   | ulator B Lov | v Word Reg   | ister  |           |               |              |              |         |       | xxxx          |

| ACCBH    | 002A        |        |        |        |        |        |        | Accum   | ulator B Hig | h Word Reg   | ister  |           |               |              |              |         |       | xxxx          |

| ACCBU    | 002C        |        |        |        |        |        |        | Accumu  | ulator B Upp | er Word Re   | gister |           |               |              |              |         |       | xxxx          |

| PCL      | 002E        |        |        |        |        |        |        | Progran | n Counter Lo | w Word Re    | gister |           |               |              |              |         |       | 0000          |

| PCH      | 0030        | —      | —      | —      |        |        |        | —       | —            |              |        | Progra    | m Counter     | High Byte R  | egister      |         |       | 0000          |

| TBLPAG   | 0032        | —      | —      | —      |        |        |        | —       | —            |              |        | Table F   | age Addre     | ss Pointer R | egister      |         |       | 0000          |

| PSVPAG   | 0034        | —      | —      | —      |        |        |        | _       | —            |              | Progra | am Memory | Visibility Pa | age Address  | s Pointer Re | egister |       | 0000          |

| RCOUNT   | 0036        |        |        |        |        |        |        | Repe    | eat Loop Co  | unter Regist | er     |           |               |              |              |         |       | xxxx          |

| DCOUNT   | 0038        |        |        |        |        |        |        |         | DCOUNT       | <15:0>       |        |           |               |              |              |         |       | xxxx          |

| DOSTARTL | 003A        |        |        |        |        |        |        | DOS     | TARTL<15:    | 1>           |        |           |               |              |              |         | 0     | xxxx          |

| DOSTARTH | 003C        | _      | —      | —      | —      | _      | —      |         | -            | —            | —      |           |               | DOSTAR       | TH<5:0>      |         |       | 00xx          |

| DOENDL   | 003E        |        |        |        |        |        |        | DO      | ENDL<15:1    | >            |        |           |               |              |              |         | 0     | XXXX          |

| DOENDH   | 0040        |        | _      | —      | —      | _      | —      |         | _            | —            | _      |           |               | DOE          | NDH          |         |       | 00xx          |

| SR       | 0042        | OA     | OB     | SA     | SB     | OAB    | SAB    | DA      | DC           | IPL2         | IPL1   | IPL0      | RA            | N            | OV           | Z       | С     | 0000          |

#### . . COLL CODE DECISTED MAD

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

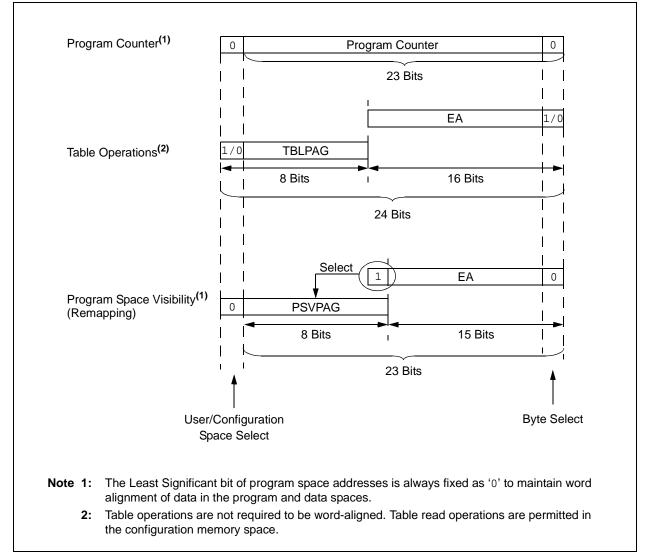

#### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL and TBLRDH).

Program space access through the data space occurs if the MSb of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 0x8000 and higher, maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | Table Reads/Writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction using PSV to access data, to execute in a single cycle.

### FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

| U-0                     | U-0                                                                         | R/W-0                               | R/W-0                | R/W-0                             | U-0             | U-0             | U-0     |  |  |  |  |

|-------------------------|-----------------------------------------------------------------------------|-------------------------------------|----------------------|-----------------------------------|-----------------|-----------------|---------|--|--|--|--|

| —                       | —                                                                           | INT2IE                              | T5IE <sup>(1)</sup>  | T4IE <sup>(1)</sup>               | —               | —               | —       |  |  |  |  |

| bit 15                  |                                                                             |                                     |                      |                                   |                 |                 | bit 8   |  |  |  |  |

|                         |                                                                             |                                     |                      |                                   |                 |                 |         |  |  |  |  |

| U-0                     | U-0                                                                         | U-0                                 | R/W-0                | R/W-0                             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |

|                         | —                                                                           |                                     | INT1IE               | CNIE                              | CMIE            | MI2C1IE         | SI2C1IE |  |  |  |  |

| bit 7                   |                                                                             |                                     |                      |                                   |                 |                 | bit (   |  |  |  |  |

|                         |                                                                             |                                     |                      |                                   |                 |                 |         |  |  |  |  |

| Legend:<br>R = Readable | h:t                                                                         |                                     | h:+                  |                                   | manted hit rea  | d aa '0'        |         |  |  |  |  |

| -n = Value at F         |                                                                             | W = Writable<br>'1' = Bit is set    |                      | 0 = 0 minipler<br>0' = Bit is cle | mented bit, rea |                 | 0.11/2  |  |  |  |  |

| -n = value at r         | POR                                                                         | 1 = Bit is set                      |                      | 0 = Bit is cle                    | ared            | x = Bit is unkn | lown    |  |  |  |  |

| bit 15-14               | Unimplemen                                                                  | ted: Read as '                      | ז'                   |                                   |                 |                 |         |  |  |  |  |

| bit 13                  | -                                                                           | nal Interrupt 2                     |                      |                                   |                 |                 |         |  |  |  |  |

|                         |                                                                             | request is enab                     |                      |                                   |                 |                 |         |  |  |  |  |

|                         | 0 = Interrupt r                                                             | request is not e                    | nabled               |                                   |                 |                 |         |  |  |  |  |

| bit 12                  | T5IE: Timer5                                                                | Interrupt Enabl                     | e bit <sup>(1)</sup> |                                   |                 |                 |         |  |  |  |  |

|                         | 1 = Interrupt request has occurred                                          |                                     |                      |                                   |                 |                 |         |  |  |  |  |

|                         |                                                                             | request has not                     |                      |                                   |                 |                 |         |  |  |  |  |

| bit 11                  |                                                                             | Interrupt Enabl                     |                      |                                   |                 |                 |         |  |  |  |  |

|                         | •                                                                           | request has occ<br>request has not  |                      |                                   |                 |                 |         |  |  |  |  |

| bit 10-5                | -                                                                           | ted: Read as '                      |                      |                                   |                 |                 |         |  |  |  |  |

| bit 4                   | -                                                                           |                                     |                      |                                   |                 |                 |         |  |  |  |  |

| 511 -                   | INT1IE: External Interrupt 1 Enable bit<br>1 = Interrupt request is enabled |                                     |                      |                                   |                 |                 |         |  |  |  |  |

|                         |                                                                             | request is not e                    |                      |                                   |                 |                 |         |  |  |  |  |

| bit 3                   | CNIE: Input C                                                               | hange Notifica                      | tion Interrupt       | Enable bit                        |                 |                 |         |  |  |  |  |

|                         | -                                                                           | request is enab                     | -                    |                                   |                 |                 |         |  |  |  |  |

|                         | 0 = Interrupt r                                                             | request is not e                    | nabled               |                                   |                 |                 |         |  |  |  |  |

| bit 2                   | CMIE: Compa                                                                 | arator Interrupt                    | Enable bit           |                                   |                 |                 |         |  |  |  |  |

|                         | 1 = Interrupt request is enabled                                            |                                     |                      |                                   |                 |                 |         |  |  |  |  |

| 1.16.4                  | •                                                                           | request is not e                    |                      |                                   |                 |                 |         |  |  |  |  |

| bit 1                   |                                                                             | 1 Master Even                       |                      | able bit                          |                 |                 |         |  |  |  |  |

|                         |                                                                             | request is enab<br>request is not e |                      |                                   |                 |                 |         |  |  |  |  |

| bit 0                   | •                                                                           | 1 Slave Events                      |                      | ble bit                           |                 |                 |         |  |  |  |  |

|                         |                                                                             | request is enab                     | -                    |                                   |                 |                 |         |  |  |  |  |

|                         |                                                                             | request is not e                    |                      |                                   |                 |                 |         |  |  |  |  |

|                         |                                                                             |                                     |                      |                                   |                 |                 |         |  |  |  |  |

### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

### REGISTER 7-20: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|---------|-----|-----|-----|-----|---------|---------|---------|

|         |     | —   | _   | —   |         | —       | _       |

| bit 15  |     |     |     |     |         |         | bit 8   |

|         |     |     |     |     |         |         |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| —       | —   | —   | —   | —   | INT1IP2 | INT1IP1 | INT1IP0 |

| bit 7   |     |     |     |     |         |         | bit 0   |

|         |     |     |     |     |         |         |         |

| Logondi |     |     |     |     |         |         |         |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-3 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 2-0  | INT1IP<2:0>: External Interrupt 1 Priority bits            |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •<br>001 = Interrupt is Priority 1                         |

|          | 000 = Interrupt source is disabled                         |

#### REGISTER 7-21: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| U-0                                                                        | R/W-1                | R/W-0                | R/W-0                | U-0          | U-0              | U-0    | U-0   |

|----------------------------------------------------------------------------|----------------------|----------------------|----------------------|--------------|------------------|--------|-------|

| _                                                                          | T4IP2 <sup>(1)</sup> | T4IP1 <sup>(1)</sup> | T4IP0 <sup>(1)</sup> | —            | _                | _      | _     |

| bit 15                                                                     |                      |                      |                      |              |                  |        | bit 8 |

|                                                                            |                      |                      |                      |              |                  |        |       |

| U-0                                                                        | U-0                  | U-0                  | U-0                  | U-0          | U-0              | U-0    | U-0   |

| —                                                                          | —                    | —                    | —                    | —            | —                | —      | —     |

| bit 7                                                                      |                      |                      |                      |              |                  |        | bit 0 |

|                                                                            |                      |                      |                      |              |                  |        |       |

| Legend:                                                                    |                      |                      |                      |              |                  |        |       |

| R = Readable I                                                             | bit                  | W = Writable         | bit                  | U = Unimpler | mented bit, read | as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                      |                      |                      |              |                  |        | nown  |

|                                                                            |                      |                      |                      |              |                  |        |       |

| bit 15                                                                     | Unimplemen           | ted: Read as '       | 0'                   |              |                  |        |       |

| bit 14-12 | T4IP<2:0>: Timer4 Interrupt Priority bits <sup>(1)</sup>   |

|-----------|------------------------------------------------------------|

|           | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|           | •                                                          |

|           | •                                                          |

|           | •                                                          |

|           | 001 = Interrupt is Priority 1                              |

|           | 000 = Interrupt source is disabled                         |

| bit 11-0  | Unimplemented: Read as '0'                                 |

|           |                                                            |

Note 1: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

# 12.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Timer2/3 and Timer4/5 have three 2-bit timers that can also be configured as two independent 16-bit timers with selectable operating modes.

Note 1: Timer4 and Timer5 are available in dsPIC33FJ32(GP/MC10X) devices only.

As a 32-bit timer, Timer2/3 and Timer4/5 permit operation in three modes:

- Two independent 16-bit timers (e.g., Timer2 and Timer3 or Timer4 and Timer5) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer (Timer2/3 and Timer4/5)

- Single 32-bit synchronous counter (Timer2/3 and Timer4/5)

Timer2/3 and Timer4/5 also support:

- Timer gate operation

- Selectable prescaler settings

- Timer operation during Idle and Sleep modes

- Interrupt on a 32-bit Period register match

- Time base for input capture and output compare modules (Timer2 and Timer3 only)

- ADC1 event trigger (Timer2/3 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the event trigger. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers (see Register 12-1 through Register 12-4). For 32-bit timer/counter operation, Timer2/4 is the least significant word (Isw) and Timer3/5 is the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are used for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

#### 12.1 32-Bit Operation

To configure Timer2/3 and Timer4/5 for 32-bit operation:

- 1. Set the T32 control bit.

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3/PR5 contains the msw of the value, while PR2/PR4 contains the least significant word (lsw).

- 5. If interrupts are required, set the Timer3 (or Timer5) Interrupt Enable bit, T3IE (or T5IE). Use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. While Timer2/Timer4 controls the timer, the interrupt appears as a Timer3/Timer5 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair, TMR3:TMR2 or TMR5:TMR4, which always contains the msw of the count, while TMR2 or TMR4 contains the lsw.

#### 12.2 16-Bit Operation

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the Timerx Interrupt Enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

| U-0                                                                  | U-0   | U-0   | U-0              | U-0    | U-0             | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------|-------|------------------|--------|-----------------|-------|-------|

| _                                                                    | _     | _     | —                | —      |                 | AMSK  | <9:8> |

| bit 15                                                               |       |       |                  |        |                 |       | bit 8 |

|                                                                      |       |       |                  |        |                 |       |       |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0            | R/W-0  | R/W-0           | R/W-0 | R/W-0 |

|                                                                      |       |       | AMS              | K<7:0> |                 |       |       |

| bit 7                                                                |       |       |                  |        |                 |       | bit 0 |

|                                                                      |       |       |                  |        |                 |       |       |

| Legend:                                                              |       |       |                  |        |                 |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |                  |        |                 |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit                         |       |       | '0' = Bit is cle | eared  | x = Bit is unkn | iown  |       |

|                                                                      |       |       |                  |        |                 |       |       |

#### REGISTER 17-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Mask for Address Bit x Select bits

1 = Enables masking for Bit x of incoming message address; bit match not required in this position

0 = Disables masking for Bit x; bit match required in this position

# 20.0 COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 device families. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Comparator with Blanking" (DS70647) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

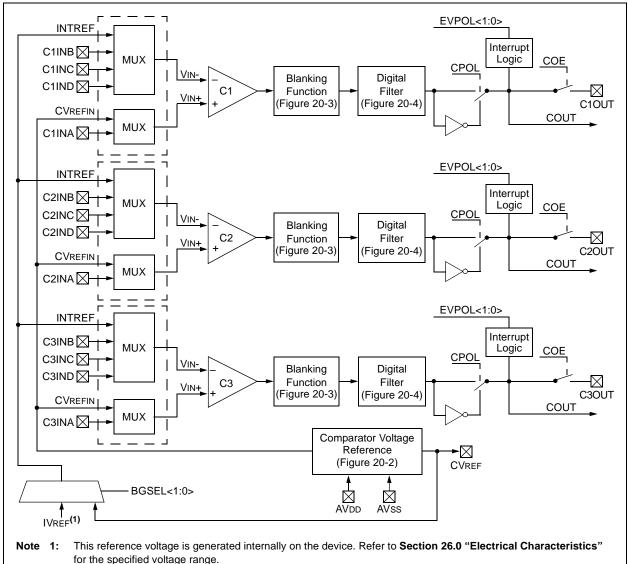

The comparator module provides three comparators that can be configured in different ways. As shown in Figure 20-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

These options allow users to:

- Select the edge for trigger and interrupt generation

- Select low-power control

- Configure the comparator voltage reference and band gap

- · Configure output blanking and masking

The comparator operating mode is determined by the input selections (i.e., whether the input voltage is compared to a second input voltage) to an internal voltage reference.

#### FIGURE 20-1: COMPARATOR I/O OPERATING MODES

| REGISTER 20-4: CMxMSKCON: COMPARATOR x MASK GATING CONTROL<br>REGISTER |                                                                                                                                     |                                                  |                                        |                  |                                        |                    |       |  |  |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------|------------------|----------------------------------------|--------------------|-------|--|--|

| R/W-0                                                                  | U-0                                                                                                                                 | R/W-0                                            | R/W-0                                  | R/W-0            | R/W-0                                  | R/W-0              | R/W-0 |  |  |

| HLMS                                                                   | _                                                                                                                                   | OCEN                                             | OCNEN                                  | OBEN             | OBNEN                                  | OAEN               | OANEN |  |  |

| bit 15                                                                 |                                                                                                                                     |                                                  |                                        |                  |                                        |                    | bit 8 |  |  |

| R/W-0                                                                  | R/W-0                                                                                                                               | R/W-0                                            | R/W-0                                  | R/W-0            | R/W-0                                  | R/W-0              | R/W-0 |  |  |

| NAGS                                                                   | PAGS                                                                                                                                | ACEN                                             | ACNEN                                  | ABEN             | ABNEN                                  | AAEN               | AANEN |  |  |

| bit 7                                                                  | 1                                                                                                                                   | 1                                                |                                        |                  |                                        |                    | bit 0 |  |  |

| Legend:                                                                |                                                                                                                                     |                                                  |                                        |                  |                                        |                    |       |  |  |

| R = Readable b                                                         | oit                                                                                                                                 | W = Writable                                     | bit                                    | U = Unimple      | mented bit, read                       | d as '0'           |       |  |  |

| -n = Value at P                                                        | OR                                                                                                                                  | '1' = Bit is set                                 |                                        | '0' = Bit is cle | eared                                  | x = Bit is unknown |       |  |  |

| bit 15                                                                 | 1 = The mas<br>0 = The mas                                                                                                          | king (blanking)                                  | function will pro<br>function will pro | event any asse   | erted ('0') compa<br>erted ('1') compa |                    |       |  |  |

| bit 14                                                                 | -                                                                                                                                   | nted: Read as                                    |                                        | L :4             |                                        |                    |       |  |  |

| bit 13                                                                 | OCEN: OR Gate C Input Inverted Enable bit<br>1 = MCI is connected to OR gate<br>0 = MCI is not connected to OR gate                 |                                                  |                                        |                  |                                        |                    |       |  |  |

| bit 12                                                                 | OCNEN: OR Gate C Input Inverted Enable bit                                                                                          |                                                  |                                        |                  |                                        |                    |       |  |  |

|                                                                        |                                                                                                                                     | MCI is connec<br>MCI is not con                  |                                        |                  |                                        |                    |       |  |  |

| bit 11                                                                 | OBEN: OR Gate B Input Inverted Enable bit                                                                                           |                                                  |                                        |                  |                                        |                    |       |  |  |

|                                                                        |                                                                                                                                     | onnected to OF<br>ot connected to                |                                        |                  |                                        |                    |       |  |  |

| bit 10                                                                 | OBNEN: OR Gate B Input Inverted Enable bit                                                                                          |                                                  |                                        |                  |                                        |                    |       |  |  |

|                                                                        |                                                                                                                                     | MBI is connect<br>MBI is not con                 |                                        |                  |                                        |                    |       |  |  |

| bit 9                                                                  | OAEN: OR Gate A Input Enable bit                                                                                                    |                                                  |                                        |                  |                                        |                    |       |  |  |

|                                                                        |                                                                                                                                     | onnected to OF<br>ot connected to                |                                        |                  |                                        |                    |       |  |  |

| bit 8                                                                  | OANEN: OR Gate A Input Inverted Enable bit                                                                                          |                                                  |                                        |                  |                                        |                    |       |  |  |

|                                                                        |                                                                                                                                     | MAI is connect<br>MAI is not con                 | •                                      |                  |                                        |                    |       |  |  |

| bit 7                                                                  | NAGS: Negative AND Gate Output Select<br>1 = Inverted ANDI is connected to OR gate<br>0 = Inverted ANDI is not connected to OR gate |                                                  |                                        |                  |                                        |                    |       |  |  |

| bit 6                                                                  | 1 = ANDI is                                                                                                                         | tive AND Gate<br>connected to C<br>not connected | R gate                                 |                  |                                        |                    |       |  |  |

| bit 5                                                                  | 1 = MCI is c                                                                                                                        | O Gate A1 C Inp<br>connected to AN               |                                        | able bit         |                                        |                    |       |  |  |

|                                                                        |                                                                                                                                     | of connected 1-                                  |                                        |                  |                                        |                    |       |  |  |

| bit 4                                                                  |                                                                                                                                     | ot connected to                                  | -                                      | nable bit        |                                        |                    |       |  |  |

# DECISTED 20-4. CMVMSKCON- COMPADATOR V MASK GATING CONTROL

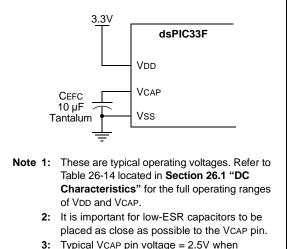

### 23.2 On-Chip Voltage Regulator

All of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 23-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 26-14 located in **Section 26.1** "**DC Characteristics**".

| Note: | It is important for low-ESR capacitors to be |

|-------|----------------------------------------------|

|       | placed as close as possible to the VCAP pin. |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 23-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

**3:** Typical VCAP pin voltage = 2.5V when VDD  $\ge$  VDDMIN.

#### 23.3 BOR: Brown-out Reset

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an Oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

| Field                                                               | Description                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm                                                               | Multiplicand and Multiplier Working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                                        |

| Wm*Wn                                                               | Multiplicand and Multiplier Working register pair for DSP instructions $\in$ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                       |

| Wn                                                                  | One of 16 Working registers ∈ {W0W15}                                                                                                                                                                                                                                |

| Wnd                                                                 | One of 16 destination Working registers ∈ {W0W15}                                                                                                                                                                                                                    |

| Wns                                                                 | One of 16 source Working registers ∈ {W0W15}                                                                                                                                                                                                                         |

| WREG W0 (Working register used in file register instructions)       |                                                                                                                                                                                                                                                                      |

| Ws     Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] } |                                                                                                                                                                                                                                                                      |

| Wso                                                                 | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                      |

| Wx                                                                  | X data space prefetch address register for DSP instructions<br>∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2,<br>[W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2,<br>[W9 + W12], none}                |

| Wxd                                                                 | X data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

| Wy                                                                  | Y data space prefetch address register for DSP instructions<br>∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2,<br>[W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2,<br>[W11 + W12], none} |

| Wyd                                                                 | Y data space prefetch destination register for DSP instructions $\in$ {W4W7}                                                                                                                                                                                         |

# TABLE 24-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| TABLE 24-2:     INSTRUCTION SET OVERVIEW (CONTINUED) |        |                 |                |                                       |               |                |                          |

|------------------------------------------------------|--------|-----------------|----------------|---------------------------------------|---------------|----------------|--------------------------|

| Base<br>Instr<br># Mnemonic                          |        | Assembly Syntax |                | Description                           | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

| 66                                                   | RRNC   | RRNC            | f              | f = Rotate Right (No Carry) f         | 1             | 1              | N,Z                      |

|                                                      |        | RRNC            | f,WREG         | WREG = Rotate Right (No Carry) f      | 1             | 1              | N,Z                      |

|                                                      |        | RRNC            | Ws,Wd          | Wd = Rotate Right (No Carry) Ws       | 1             | 1              | N,Z                      |

| 67                                                   | SAC    | SAC             | Acc,#Slit4,Wdo | Store Accumulator                     | 1             | 1              | None                     |

|                                                      |        | SAC.R           | Acc,#Slit4,Wdo | Store Rounded Accumulator             | 1             | 1              | None                     |

| 68                                                   | SE     | SE              | Ws,Wnd         | Wnd = sign-extended Ws                | 1             | 1              | C,N,Z                    |

| 69                                                   | SETM   | SETM            | f              | f = 0xFFFF                            | 1             | 1              | None                     |

|                                                      |        | SETM            | WREG           | WREG = 0xFFFF                         | 1             | 1              | None                     |

|                                                      |        | SETM            | Ws             | Ws = 0xFFFF                           | 1             | 1              | None                     |