#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 15                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 4x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

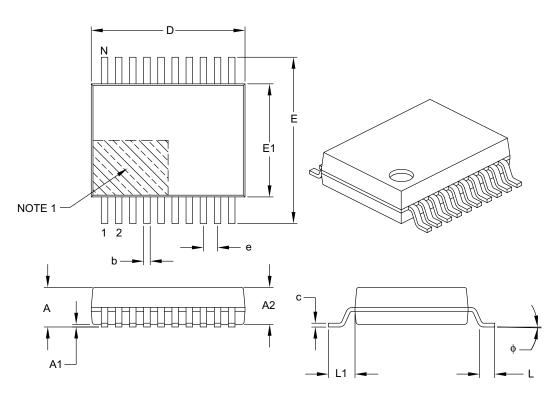

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 20-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16mc101-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

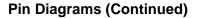

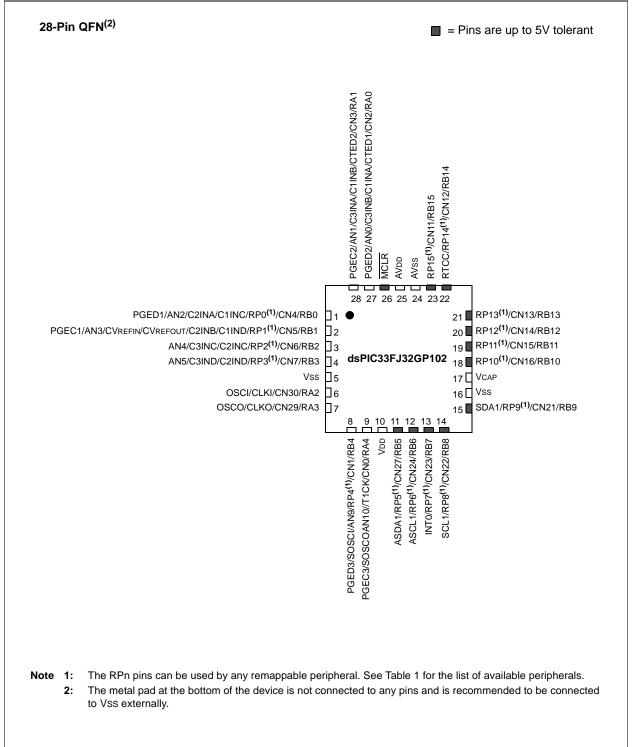

#### Pin Diagrams (Continued)

#### **Table of Contents**

| 1.0   | Device Overview                                                       |       |

|-------|-----------------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers | 33    |

| 3.0   | CPU                                                                   |       |

| 4.0   | Memory Organization                                                   | 49    |

| 5.0   | Flash Program Memory                                                  | 83    |

| 6.0   | Resets                                                                |       |

| 7.0   | Interrupt Controller                                                  | 95    |

| 8.0   | Oscillator Configuration                                              | . 125 |

| 9.0   | Power-Saving Features                                                 | . 133 |

| 10.0  | I/O Ports                                                             | . 139 |

| 11.0  | Timer1                                                                | . 165 |

| 12.0  | Timer2/3 and Timer4/5                                                 | . 167 |

| 13.0  | Input Capture                                                         | . 175 |

| 14.0  | Output Compare                                                        | . 177 |

| 15.0  | Motor Control PWM Module                                              | . 181 |

| 16.0  | Serial Peripheral Interface (SPI)                                     | . 197 |

| 17.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                         | . 203 |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)                    |       |

| 19.0  | 10-Bit Analog-to-Digital Converter (ADC)                              | . 217 |

| 20.0  | Comparator Module                                                     |       |

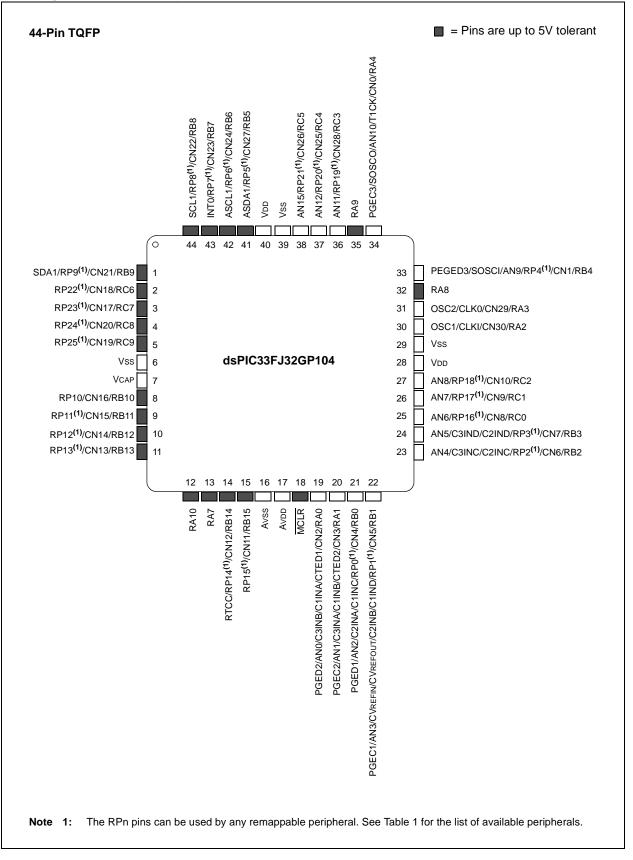

| 21.0  | Real-Time Clock and Calendar (RTCC)                                   | . 243 |

| 22.0  | Charge Time Measurement Unit (CTMU)                                   | . 255 |

| 23.0  | Special Features                                                      | . 261 |

| 24.0  | Instruction Set Summary                                               | . 269 |

| 25.0  | Development Support                                                   | . 277 |

| 26.0  | Electrical Characteristics                                            |       |

| 27.0  | High-Temperature Electrical Characteristics                           |       |

| 28.0  | Packaging Information                                                 | . 343 |

| Appe  | ndix A: Revision History                                              | . 373 |

| Index |                                                                       | 381   |

| The I | /icrochip Web Site                                                    | . 387 |

| Cust  | omer Change Notification Service                                      | . 387 |

| Cust  | omer Support                                                          | . 387 |

| Prod  | uct Identification System                                             | . 389 |

NOTES:

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest "dsPIC33/PIC24 Family Reference Manual" sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, if present on the device (regardless if ADC module is not used) (see Section 2.2 "Decoupling Capacitors")

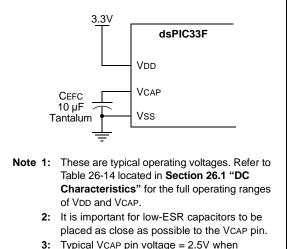

- VCAP (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10V-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

The SA and SB bits are modified each time data passes through the adder/subtracter, but can only be cleared by the user application. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 overflow, and therefore, indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, the SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The Overflow and Saturation Status bits can optionally be viewed in the STATUS Register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). Programmers can check one bit in the STATUS Register to determine whether either accumulator has overflowed, or one bit to determine whether either accumulator has saturated. This is useful for complex number arithmetic, which typically uses both accumulators.

The device supports three Saturation and Overflow modes:

- Bit 39 Overflow and Saturation:

- When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 value (0x7FFFFFFFF) or maximally negative 9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user application. This condition is referred to as 'super saturation' and provides protection against erroneous data or unexpected algorithm problems (such as gain calculations).

- Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFFF) or maximally negative 1.31 value (0x0080000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user application. When this Saturation mode is in effect, the guard bits are not used, so the OA, OB or OAB bits are never set.

- Bit 39 Catastrophic Overflow: The bit 39 Overflow Status bit from the adder is used to set the SA or SB bit, which remains set until cleared by the user application. No saturation operation is performed and the accumulator is allowed to overflow, destroying its sign. If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

#### 3.6.3 ACCUMULATOR 'WRITE BACK'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator which is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- W13, Register Direct:

- The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13]+ = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

#### 3.6.3.1 Round Logic

The round logic is a combinational block that performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value that is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word (lsw) is simply discarded.

Conventional rounding will zero-extend bit 15 of the accumulator and will add it to the ACCxH word (bits 16 through 31 of the accumulator).

- If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented.

- If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged.

A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. In this case, the Least Significant bit (LSb), bit 16 of the accumulator, of ACCxH is examined:

- If it is '1', ACCxH is incremented.

- If it is '0', ACCxH is not modified.

Assuming that bit 16 is effectively random in nature, this scheme removes any rounding bias that may accumulate.

| TABLE 4-  | 17:         | ADC1   | REGIS  | STER M | AP FO  | R dsPIC | 33FJ32(  | GP/MC)1  | 04 DEV  | ICES         |           |                   |        |        |          |          |         |               |

|-----------|-------------|--------|--------|--------|--------|---------|----------|----------|---------|--------------|-----------|-------------------|--------|--------|----------|----------|---------|---------------|

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11  | Bit 10   | Bit 9    | Bit 8   | Bit 7        | Bit 6     | Bit 5             | Bit 4  | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 0         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF1  | 0302        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 1         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF2  | 0304        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 2         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF3  | 0306        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 3         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF4  | 0308        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 4         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF5  | 030A        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 5         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF6  | 030C        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 6         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF7  | 030E        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 7         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF8  | 0310        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 8         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF9  | 0312        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 9         |                   |        |        |          |          |         | xxxx          |

| ADC1BUFA  | 0314        |        |        |        |        |         |          |          | ADC1 Da | ita Buffer ' | 10        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFB  | 0316        |        |        |        |        |         |          |          | ADC1 Da | ta Buffer    | 11        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFC  | 0318        |        |        |        |        |         |          |          | ADC1 Da | ita Buffer 1 | 12        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFD  | 031A        |        |        |        |        |         |          |          | ADC1 Da | ita Buffer 1 | 13        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFE  | 031C        |        |        |        |        |         |          |          | ADC1 Da | ita Buffer 1 | 14        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFF  | 031E        |        |        |        |        |         |          |          | ADC1 Da | ita Buffer 1 | 15        |                   |        |        |          |          |         | xxxx          |

| AD1CON1   | 0320        | ADON   | —      | ADSIDL | —      | _       |          | FORM1    | FORM0   | SSRC2        | SSRC1     | SSRC0             | _      | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322        | VCFG2  | VCFG1  | VCFG0  | —      | _       | CSCNA    | CHPS1    | CHPS0   | BUFS         | —         | SMPI3             | SMPI2  | SMPI1  | SMPI0    | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324        | ADRC   | —      | —      | SAMC4  | SAMC3   | SAMC2    | SAMC1    | SAMC0   | ADCS7        | ADCS6     | ADCS5             | ADCS4  | ADCS3  | ADCS2    | ADCS1    | ADCS0   | 0000          |

| AD1CHS123 | 0326        | —      | _      | —      | —      | _       | CH123NB1 | CH123NB0 | CH123SB | —            | —         |                   | _      | —      | CH123NA1 | CH123NA0 | CH123SA | 0000          |

| AD1CHS0   | 0328        | CH0NB  | _      | —      | CH0SB4 | CH0SB3  | CH0SB2   | CH0SB1   | CH0SB0  | <b>CH0NA</b> | —         |                   | CH0SA4 | CH0SA3 | CH0SA2   | CH0SA1   | CH0SA0  | 0000          |

| AD1PCFGL  | 032C        | PCFG15 | _      | —      |        |         |          |          |         | F            | PCFG<12:0 | )> <sup>(1)</sup> |        |        |          |          |         | 0000          |

| AD1CSSL   | 0330        | CSS15  | _      | _      |        |         |          |          |         |              | CSS12:0>  | (1)               |        |        |          |          |         | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PCFG<10:9> and CSS<10:9> bits are available in dsPIC33FJ32(GP/MC)104 devices only.

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit             |

|-------|----------------------------------------------------|

|       | 1 = Address error trap has occurred                |

|       | 0 = Address error trap has not occurred            |

| bit 2 | STKERR: Stack Error Trap Status bit                |

|       | 1 = Stack error trap has occurred                  |

|       | 0 = Stack error trap has not occurred              |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit |

|       | 1 = Oscillator failure trap has occurred           |

|       | 0 = Oscillator failure trap has not occurred       |

| bit 0 | Unimplemented: Read as '0'                         |

|                                                 | U-0                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                | R/W-0                                                                                                        | R/W-0                                                        | R/W-0                                            |  |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------|--|--|--|

| _                                               | _                                                                                                                                                                                                                                                   | FAOV3H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FAOV3L                                                                                                                                                                                                                                                                               | FAOV2H                                                                                                                                                                                                               | FAOV2L                                                                                                       | FAOV1H                                                       | FAOV1L                                           |  |  |  |

| bit 15                                          |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                      |                                                                                                              |                                                              | bit                                              |  |  |  |

| R/W-0                                           | U-0                                                                                                                                                                                                                                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | U-0                                                                                                                                                                                                                                                                                  | U-0                                                                                                                                                                                                                  | R/W-1                                                                                                        | R/W-1                                                        | R/W-1                                            |  |  |  |

| FLTAM                                           |                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                    | —                                                                                                                                                                                                                    | FAEN3                                                                                                        | FAEN2                                                        | FAEN1                                            |  |  |  |

| bit 7                                           |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                      |                                                                                                              |                                                              | bit                                              |  |  |  |

| Legend:                                         |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                      |                                                                                                              |                                                              |                                                  |  |  |  |

| R = Reada                                       | ble bit                                                                                                                                                                                                                                             | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit                                                                                                                                                                                                                                                                                  | U = Unimplem                                                                                                                                                                                                         | nented bit, read                                                                                             | d as '0'                                                     |                                                  |  |  |  |

| -n = Value                                      | at POR                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                      | '0' = Bit is clea                                                                                                                                                                                                    | ared                                                                                                         | x = Bit is unkr                                              | nown                                             |  |  |  |

|                                                 |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                      |                                                                                                              |                                                              |                                                  |  |  |  |

| bit 15-14                                       | Unimpleme                                                                                                                                                                                                                                           | nted: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0'                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                      |                                                                                                              |                                                              |                                                  |  |  |  |

| bit 13-8                                        | FAOV<3:1>                                                                                                                                                                                                                                           | H:FAOV<3:1>L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | : Fault Input A                                                                                                                                                                                                                                                                      | PWMx Overric                                                                                                                                                                                                         | le Value bits                                                                                                |                                                              |                                                  |  |  |  |

|                                                 | FAOV<3:1>H:FAOV<3:1>L: Fault Input A PWMx Override Value bits<br>1 = The PWMx output pin is driven active on an external Fault input event                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                      |                                                                                                              |                                                              |                                                  |  |  |  |

|                                                 | 0 = The PW                                                                                                                                                                                                                                          | Mx output pin is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | driven inactiv                                                                                                                                                                                                                                                                       | e on an externa                                                                                                                                                                                                      | al Fault input e                                                                                             | vent                                                         |                                                  |  |  |  |

| bit 7                                           | FLTAM: Fau                                                                                                                                                                                                                                          | FLTAM: Fault A Mode bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                      |                                                                                                              |                                                              |                                                  |  |  |  |

|                                                 | 1 = The Fault A input pin functions in the Cycle-by-Cycle mode                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                      |                                                                                                              |                                                              |                                                  |  |  |  |