Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                         |

| Number of I/O              | 15                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 4x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 20-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16mc101t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

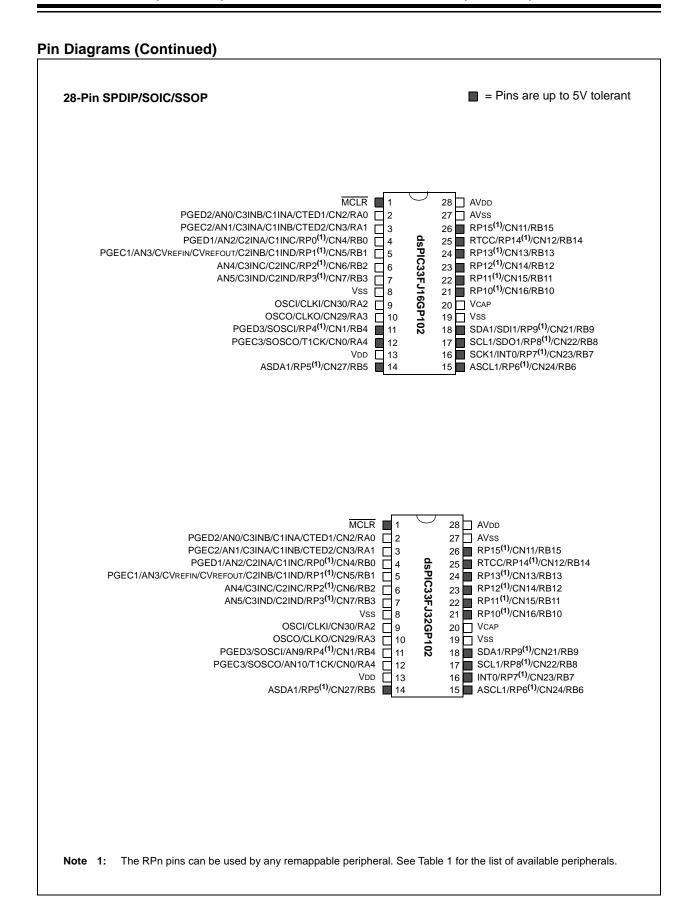

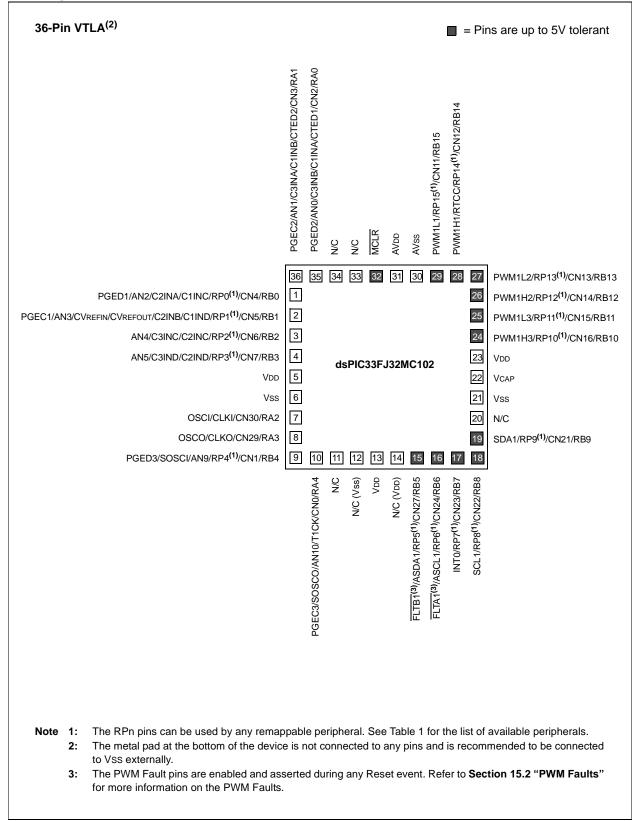

#### **Pin Diagrams (Continued)**

#### Referenced Sources

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the primary reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33FJ16MC102 product page of the Microchip Web site (www.microchip.com). In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "CPU" (DS70204)

- "Data Memory" (DS70202)

- "Program Memory" (DS70203)

- "Flash Programming" (DS70191)

- "Reset" (DS70192)

- "Watchdog Timer and Power-Saving Modes" (DS70196)

- "Timers" (DS70205)

- "Input Capture" (DS70198)

- "Output Compare" (DS70209)

- "Motor Control PWM" (DS70187)

- "Analog-to-Digital Converter (ADC)" (DS70183)

- "UART" (DS70188)

- "Serial Peripheral Interface (SPI)" (DS70206)

- "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- "CodeGuard Security" (DS70199)

- "Programming and Diagnostics" (DS70207)

- "Device Configuration" (DS70194)

- "I/O Ports with Peripheral Pin Select (PPS)" (DS70190)

- "Real-Time Clock and Calendar (RTCC)" (DS70301)

- "Introduction (Part VI)" (DS70655)

- "Oscillator (Part VI)" (DS70644)

- "Interrupts (Part VI)" (DS70633)

- "Comparator with Blanking" (DS70647)

- "Charge Time Measurement Unit (CTMU)" (DS70635)

| 1  | File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|----|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| TR | RISA         | 02C0        |        |        | —      | -      | _      |        | TRISA< | 10:7> |       |       | —     |       |       | TRISA<4:0> |       |       | 001F          |

| PC | ORTA         | 02C2        |        |        | —      |        | _      |        | RA<10  | ):7>  |       | —     | _     |       |       | RA<4:0>    |       |       | xxxx          |

| LA | TA           | 02C4        | _      | _      | _      | _      | -      |        | LATA<1 | 0:7>  |       | —     | _     |       |       | LATA<4:0>  |       |       | xxxx          |

| 0  | DCA          | 02C6        |        |        | _      | _      | _      |        | ODCA<  | 10:7> |       | _     | _     |       | ODCA  | <3:2>      |       |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-30: PORTB REGISTER MAP FOR dsPIC33FJ16GP101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|---------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        | TRISB< | :15:14> | _      | _      | _      | _      | -     | TRISB<9:7 | >     | _     | _     | TRISB4 | _     | _     | TRISE | 3<1:0> | C393          |

| PORTB     | 02CA        | RB<1   | 5:14>   | _      | _      | _      | _      |       | RB<9:7>   |       | _     | _     | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        | LATB<  | 15:14>  | _      | _      | —      | —      |       | LATB<9:7> | •     |       | _     | LATB4  | —     | _     | LATB  | <1:0>  | xxxx          |

| ODCB      | 02CE        | ODCB<  | :15:14> | _      | _      | -      | -      | (     | ODCB<9:7: | >     |       | _     | ODCB4  | _     | _     | _     |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-31: PORTB REGISTER MAP FOR dsPIC33FJ16MC101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13                                      | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|--------|---------------------------------------------|--------|--------|--------|-------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        |        | TRISB< | <15:12>                                     |        | _      | _      | 1     | RISB<9:7: | >     | _     | _     | TRISB4 | _     | —     | TRISE | 3<1:0> | F393          |

| PORTB     | 02CA        |        | RB<1   | 5:12>                                       |        |        | _      |       | RB<9:7>   |       | _     |       | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        |        | LATB<  | 15:12>                                      |        |        | _      |       | LATB<9:7> | •     | _     |       | LATB4  | _     | _     | LATB  | <1:0>  | xxxx          |

| ODCB      | 02CE        |        | ODCB<  | <15:12><br>B<15:12><br>B<15:12><br>B<15:12> |        |        | _      | (     | DDCB<9:7: | >     | -     | _     | ODCB4  |       | _     |       |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-32: PORTB REGISTER MAP FOR dsPIC33FJ16(GP/MC)102 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB        | 02C8        |        |        |        |        |        |        |        | TRISB< | :15:0> |       |       |       |       |       |       |       | FFFF          |

| PORTB        | 02CA        |        |        |        |        |        |        |        | RB<1   | 5:0>   |       |       |       |       |       |       |       | xxxx          |

| LATB         | 02CC        |        |        |        |        |        |        |        | LATB<  | 15:0>  |       |       |       |       |       |       |       | xxxx          |

| ODCB         | 02CE        |        |        |        |        |        | ODCB<  | :15:4> |        |        |       |       |       | _     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# DS70000652F-page 72

#### TABLE 4-37: SYSTEM CONTROL REGISTER MAP

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0 | All<br>Resets   |  |

|-----------|-------------|--------|--------|--------|--------|--------|---------|---------|---------|---------|--------|--------|-------|-------|-------|---------|-------|-----------------|--|

| RCON      | 0740        | TRAPR  | IOPUWR | _      |        | _      | _       | СМ      | VREGS   | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP | IDLE  | BOR     | POR   | xxxx(1)         |  |

| OSCCON    | 0742        | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2   | NOSC1   | NOSC0   | CLKLOCK | IOLOCK | LOCK   | _     | CF    | _     | LPOSCEN | OSWEN | 0300 <b>(2)</b> |  |

| CLKDIV    | 0744        | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | FRCDIV2 | FRCDIV1 | FRCDIV0 | _       |        |        | _     |       |       | _       | _     | 3040            |  |

| OSCTUN    | 0748        | _      | _      | _      | _      | _      | _       | _       | _       | _       |        |        |       |       |       |         |       |                 |  |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the FOSC Configuration bits and by type of Reset.

#### TABLE 4-38: NVM REGISTER MAP

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| NVMCON    | 0760        | WR     | WREN   | WRERR  | _      | -      | _      | -     | _     | _           | ERASE | _     |       | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 | <sub>0000</sub> (1) |

| NVMKEY    | 0766        |        | _      | _      |        |        | —      |       | _     | NVMKEY<7:0> |       |       |       |        |        |        |        | 0000                |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-39: PMD REGISTER MAP

| File Name | SFR<br>Addr | Bit 15              | Bit 14              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------------|---------------------|---------------------|--------|--------|--------|--------|-----------------------|-------|--------|-------|-------|-------|--------|--------|-------|-------|---------------|

| PMD1      | 0770        | T5MD <sup>(2)</sup> | T4MD <sup>(2)</sup> | T3MD   | T2MD   | T1MD   | _      | PWM1MD <sup>(1)</sup> | _     | I2C1MD | _     | U1MD  |       | SPI1MD | -      | —     | AD1MD | 0000          |

| PMD2      | 0772        | _                   | _                   | -      |        | _      | IC3MD  | IC2MD                 | IC1MD | -      |       |       | _     | _      | _      | OC2MD | OC1MD | 0000          |

| PMD3      | 0774        | _                   | _                   | -      |        | _      | CMPMD  | RTCCMD                | _     | -      |       |       | _     | _      | _      | _     | _     | 0000          |

| PMD4      | 0776        | —                   | _                   | _      | _      | _      | _      | _                     | _     | _      | _     | _     | _     |        | CTMUMD | _     | _     | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is available in dsPIC33FJXXMC10X devices only.

2: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

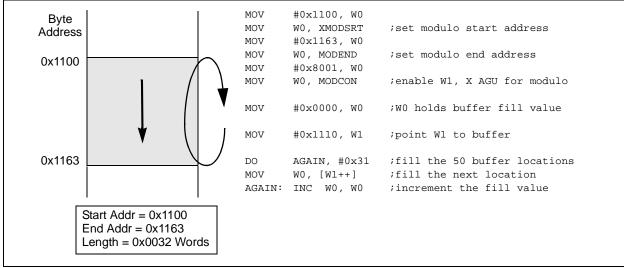

#### 4.4 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the circular buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear). The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.4.2 W ADDRESS REGISTER SELECTION

- The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select which registers will operate with Modulo Addressing.

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled.

- If YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

### FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

|                  | R/W-1                                                                                  | R/W-0                                                                          | R/W-0                                              | U-0                | R/W-1            | R/W-0           | R/W-0  |

|------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------|--------------------|------------------|-----------------|--------|

| _                | T2IP2                                                                                  | T2IP1                                                                          | T2IP0                                              |                    | OC2IP2           | OC2IP1          | OC2IP0 |

| bit 15           |                                                                                        |                                                                                |                                                    |                    |                  |                 | bit 8  |

|                  |                                                                                        |                                                                                |                                                    |                    |                  |                 |        |

| U-0              | R/W-1                                                                                  | R/W-0                                                                          | R/W-0                                              | U-0                | U-0              | U-0             | U-0    |

| _                | IC2IP2                                                                                 | IC2IP1                                                                         | IC2IP0                                             |                    | —                |                 | —      |

| bit 7            |                                                                                        |                                                                                |                                                    |                    |                  |                 | bit    |

| Legend:          |                                                                                        |                                                                                |                                                    |                    |                  |                 |        |

| R = Readab       | le bit                                                                                 | W = Writable                                                                   | bit                                                | U = Unimplen       | nented bit, read | l as '0'        |        |

| -n = Value a     | t POR                                                                                  | '1' = Bit is set                                                               |                                                    | '0' = Bit is cle   |                  | x = Bit is unkr | nown   |

|                  |                                                                                        |                                                                                |                                                    |                    |                  |                 |        |

| bit 15           | Unimplemer                                                                             | nted: Read as '                                                                | 0'                                                 |                    |                  |                 |        |

| bit 14-12        | T2IP<2:0>: 7                                                                           | Fimer2 Interrupt                                                               | Priority bits                                      |                    |                  |                 |        |

|                  | 111 = Interru                                                                          | pt is Priority 7 (                                                             | highest priori                                     | ty interrupt)      |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |

|                  |                                                                                        | ipt is Priority 1<br>ipt source is dis                                         | abled                                              |                    |                  |                 |        |

| bit 11           |                                                                                        | h <b>ted:</b> Read as '                                                        |                                                    |                    |                  |                 |        |

| bit 10-8         | -                                                                                      | : Output Compa                                                                 |                                                    | Interrupt Priori   | ty bits          |                 |        |

|                  |                                                                                        | pt is Priority 7 (                                                             |                                                    | -                  |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |

|                  | 001 = Interr                                                                           | int is Priority 1                                                              |                                                    |                    |                  |                 |        |

|                  |                                                                                        | ipt is Priority 1<br>ipt source is dis                                         | abled                                              |                    |                  |                 |        |

| bit 7            | 000 = Interru                                                                          | ipt is Priority 1<br>ipt source is dis<br>nted: Read as '                      |                                                    |                    |                  |                 |        |

|                  | 000 = Interru<br>Unimplemer                                                            | ipt source is dis<br>nted: Read as '                                           | 0'                                                 | errupt Priority bi | its              |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '<br>Input Capture (                        | 0'<br>Channel 2 Inte                               |                    | its              |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '                                           | 0'<br>Channel 2 Inte                               |                    | its              |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '<br>Input Capture (                        | 0'<br>Channel 2 Inte                               |                    | its              |                 |        |

|                  | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru<br>•<br>•                  | ipt source is dis<br>nted: Read as '<br>Input Capture C<br>ipt is Priority 7 ( | 0'<br>Channel 2 Inte                               |                    | its              |                 |        |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru | ipt source is dis<br>nted: Read as '<br>Input Capture (                        | <sup>0'</sup><br>Channel 2 Inte<br>highest priorit |                    | its              |                 |        |

#### REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| U-0           | U-0        | U-0              | R/W-0          | R/W-0             | R/W-0           | R/W-0                   | R/W-0    |

|---------------|------------|------------------|----------------|-------------------|-----------------|-------------------------|----------|

| 0-0           | 0-0        | 0-0              | 10,00-0        | 11/00-0           |                 |                         | 10,00-0  |

|               | —          |                  |                |                   | RP17R<4:0>(     | .)                      |          |

| bit 15        |            |                  |                |                   |                 |                         | bit 8    |

|               |            |                  |                |                   |                 |                         |          |

| U-0           | U-0        | U-0              | R/W-0          | R/W-0             | R/W-0           | R/W-0                   | R/W-0    |

| —             | —          | _                |                |                   | RP16R<4:0>(     | 1)                      |          |

| bit 7         |            | •                |                |                   |                 |                         | bit 0    |

|               |            |                  |                |                   |                 |                         |          |

| Legend:       |            |                  |                |                   |                 |                         |          |

| R = Readabl   | e bit      | W = Writable     | bit            | U = Unimplen      | nented bit, rea | d as '0'                |          |

| -n = Value at | POR        | '1' = Bit is set |                | '0' = Bit is clea | ared            | x = Bit is unkr         | iown     |

|               |            |                  |                |                   |                 |                         | <b>/</b> |

| bit 15-13     | Unimplemen | ted: Read as '   | 0'             |                   |                 |                         |          |

| bit 12-8      | RP17R<4:0> | Peripheral Ou    | tput Function  | is Assigned to    | RP17 Output I   | Pin bits <sup>(1)</sup> |          |

|               |            | -2 for peripher  | •              | •                 | •               |                         |          |

| bit 7-5       |            | ted: Read as '   |                | - /               |                 |                         |          |

|               | -          |                  |                |                   |                 | - · · · (1)             |          |

| bit 4-0       | RP16R<4:0> | : Peripheral Ou  | Itput Function | is Assigned to    | RP16 Output I   | Pin bits <sup>(1)</sup> |          |

#### **REGISTER 10-19: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8**

(see Table 10-2 for peripheral function numbers)

| U-0     | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|---------|-----|-----|-------|-------|--------------------------|-------|-------|

|         |     |     |       |       | RP19R<4:0> <sup>(1</sup> | )     |       |

| bit 15  |     |     |       |       |                          |       | bit 8 |

|         |     |     |       |       |                          |       |       |

| U-0     | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

| _       | _   |     |       |       | RP18R<4:0> <sup>(1</sup> | )     |       |

| bit 7   |     |     |       |       |                          |       | bit 0 |

|         |     |     |       |       |                          |       |       |

| Legend: |     |     |       |       |                          |       |       |

| Logonan           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-13 | Unimplemented: Read as '0'                                                                |

|-----------|-------------------------------------------------------------------------------------------|

| bit 12-8  | RP19R<4:0>: Peripheral Output Function is Assigned to RP19 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                          |

| bit 7-5   | Unimplemented: Read as '0'                                                                |

| bit 4-0   | RP18R<4:0>: Peripheral Output Function is Assigned to RP18 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                          |

Note 1: These bits are available in dsPIC33FJ32(GP/MC)104 devices only.

Note 1: These bits are available in dsPIC33FJ32(GP/MC)104 devices only.

NOTES:

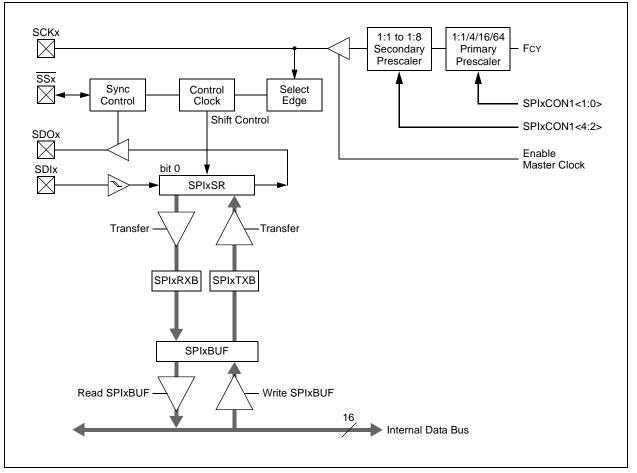

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70206) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters, etc. The SPI module is compatible with SPI and SIOP from Motorola<sup>®</sup>.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of four pins:

- SDIx (serial data input)

- SDOx (serial data output)

- SCKx (shift clock input or output)

- SSx (active-low slave select).

In Master mode operation, SCKx is a clock output. In Slave mode, it is a clock input.

#### FIGURE 16-1: SPIx MODULE BLOCK DIAGRAM

|                           | ) U-0                                                                                                                              | U-0                                                                                                                                             | R/W-0                                                            | R/W-0                                        | R/W-0                     | R/W-0              | R/W-0        |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------|---------------------------|--------------------|--------------|

| CSS15 <sup>(4)</sup> —    |                                                                                                                                    | —                                                                                                                                               |                                                                  |                                              | CSS<12:8> <sup>(4,6</sup> | 5)                 |              |

| bit 15                    |                                                                                                                                    |                                                                                                                                                 |                                                                  |                                              |                           |                    | bit 8        |

| R/W-0                     | ) R/W-0                                                                                                                            | R/W-0                                                                                                                                           | R/W-0                                                            | R/W-0                                        | R/W-0                     | R/W-0              | R/W-0        |

|                           |                                                                                                                                    |                                                                                                                                                 | CSS<7                                                            | 7:0> <sup>(4,5)</sup>                        |                           |                    |              |

| bit 7                     |                                                                                                                                    |                                                                                                                                                 |                                                                  |                                              |                           |                    | bit 0        |

| Legend:                   |                                                                                                                                    |                                                                                                                                                 |                                                                  |                                              |                           |                    |              |

| R = Reada                 | able bit                                                                                                                           | W = Writable b                                                                                                                                  | it                                                               | U = Unimplen                                 | nented bit, rea           | d as '0'           |              |

| -n = Value                | at POR                                                                                                                             | '1' = Bit is set                                                                                                                                |                                                                  | '0' = Bit is clea                            | ared                      | x = Bit is unknown |              |

| <b>h</b> :+ 44 40         | 0 = Skips AN                                                                                                                       | Nx for input sca<br>k for input scan<br><b>ted:</b> Read as '0'                                                                                 |                                                                  |                                              |                           |                    |              |

|                           |                                                                                                                                    | ieu. Neau as 0                                                                                                                                  |                                                                  |                                              |                           |                    |              |

| bit 14-13<br>bit 12-0     | CSS<12:0>: /                                                                                                                       | ADC1 Input Sca<br>Nx for input sca                                                                                                              |                                                                  | <sub>Dits</sub> (4,5,6)                      |                           |                    |              |

| bit 12-0                  | <b>CSS&lt;12:0&gt;:</b> /<br>1 = Selects A<br>0 = Skips AN2                                                                        | Nx for input sca<br>k for input scan                                                                                                            | n                                                                |                                              |                           |                    |              |

|                           | <b>CSS&lt;12:0&gt;:</b> /<br>1 = Selects A                                                                                         | Nx for input sca<br>k for input scan<br>t 14 analog inpu                                                                                        | n<br>ts, all AD1CS                                               | SSL bits can be                              |                           |                    | on. However, |

| bit 12-0                  | CSS<12:0>: /<br>1 = Selects A<br>0 = Skips AN<br>On devices withour                                                                | Nx for input sca<br>k for input scan<br>t 14 analog inpu<br>scan without a c                                                                    | n<br>ts, all AD1CS<br>correspondin                               | SSL bits can be                              |                           |                    | on. However, |

| bit 12-0                  | CSS<12:0>: /<br>1 = Selects A<br>0 = Skips AN<br>On devices withour<br>inputs selected for<br>CSSx = ANx, when<br>CTMU temperature | Nx for input sca<br>x for input scan<br>t 14 analog input<br>scan without a<br>re x = 0 through<br>a sensor input c                             | n<br>ts, all AD1CS<br>correspondin<br>12 and 15.<br>annot be sca | SSL bits can be<br>g input on the d<br>nned. | evice converts            | S VREFL.           |              |

| bit 12-0<br>Note 1:<br>2: | CSSx = ANx, when                                                                                                                   | Nx for input scan<br>x for input scan<br>t 14 analog input<br>scan without a c<br>re $x = 0$ through<br>e sensor input ca<br> ,8:6> bits are av | n<br>ts, all AD1CS<br>correspondin<br>12 and 15.<br>annot be sca | SSL bits can be<br>g input on the d<br>nned. | evice converts            | S VREFL.           |              |

# REGISTER 19-6: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2,3)</sup>

- they are reserved.

6: The CSS<10:9> bits are available on all devices, excluding the dsPIC33E.116(GP/MC)101/102 devices.

- 6: The CSS<10:9> bits are available on all devices, excluding the dsPIC33FJ16(GP/MC)101/102 devices, where they are reserved.

# 20.1 Comparator Control Registers

| R/W-0         | U-0                                                      | U-0                               | U-0            | U-0              | R-0              | R-0             | R-0   |

|---------------|----------------------------------------------------------|-----------------------------------|----------------|------------------|------------------|-----------------|-------|

| CMSIDL        |                                                          | —                                 |                | —                | C3EVT            | C2EVT           | C1EVT |

| bit 15        |                                                          |                                   |                |                  | I.               |                 | bit 8 |

|               |                                                          |                                   |                |                  |                  |                 |       |

| U-0           | U-0                                                      | U-0                               | U-0            | U-0              | R-0              | R-0             | R-0   |

| _             | _                                                        | —                                 | _              |                  | C3OUT            | C2OUT           | C10UT |

| bit 7         |                                                          |                                   |                |                  |                  |                 | bit C |

|               |                                                          |                                   |                |                  |                  |                 |       |

| Legend:       |                                                          |                                   |                |                  |                  |                 |       |

| R = Readable  | e bit                                                    | W = Writable                      | bit            | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value at | POR                                                      | '1' = Bit is set                  |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|               |                                                          |                                   |                |                  |                  |                 |       |

| bit 15        | CMSIDL: Cor                                              | nparator Stop                     | in Idle Mode b | oit              |                  |                 |       |

|               |                                                          |                                   |                |                  | ce enters Idle n | node            |       |

|               |                                                          | -                                 | -              | s in Idle mode   |                  |                 |       |

| bit 14-11     | -                                                        | ted: Read as '                    |                |                  |                  |                 |       |

| bit 10        | -                                                        | parator 3 Even                    |                |                  |                  |                 |       |

|               |                                                          | or event occur                    |                |                  |                  |                 |       |

| bit 9         |                                                          | or event did no<br>barator 2 Even |                |                  |                  |                 |       |

| DIL 9         | -                                                        | or event occur                    |                |                  |                  |                 |       |

|               |                                                          | or event did no                   |                |                  |                  |                 |       |

| bit 8         | C1EVT: Com                                               | parator 1 Even                    | t Status bit   |                  |                  |                 |       |

|               | -                                                        | or event occur                    |                |                  |                  |                 |       |

|               | 0 = Comparat                                             | or event did no                   | ot occur       |                  |                  |                 |       |

| bit 7-3       | Unimplemen                                               | ted: Read as '                    | 0'             |                  |                  |                 |       |

| bit 2         |                                                          | parator 3 Outp                    | ut Status bit  |                  |                  |                 |       |

|               | $\frac{\text{When CPOL}}{1 = \text{VIN} + > \text{VIN}}$ |                                   |                |                  |                  |                 |       |

|               | 1 = VIN + > VII $0 = VIN + < VII$                        | -                                 |                |                  |                  |                 |       |

|               | When CPOL :                                              |                                   |                |                  |                  |                 |       |

|               | 1 = VIN + < VIN                                          | ۷-                                |                |                  |                  |                 |       |

|               | 0 = VIN + > VII                                          |                                   |                |                  |                  |                 |       |

| bit 1         |                                                          | parator 2 Outp                    | ut Status bit  |                  |                  |                 |       |

|               | $\frac{\text{When CPOL}}{1 = \text{VIN+} > \text{VIN}}$  |                                   |                |                  |                  |                 |       |

|               | 1 = VIN + > VII $0 = VIN + < VII$                        |                                   |                |                  |                  |                 |       |

|               | When CPOL :                                              |                                   |                |                  |                  |                 |       |

|               | 1 = VIN + < VIN                                          |                                   |                |                  |                  |                 |       |

|               | 0 = VIN + > VII                                          |                                   |                |                  |                  |                 |       |

| bit 0         |                                                          | parator 1 Outp                    | ut Status bit  |                  |                  |                 |       |

|               | $\frac{\text{When CPOL}}{1 = \text{VIN} + > \text{VIN}}$ |                                   |                |                  |                  |                 |       |

|               | 1 = VIN + > VII $0 = VIN + < VII$                        |                                   |                |                  |                  |                 |       |

|               | When CPOL :                                              |                                   |                |                  |                  |                 |       |

|               | 1 = VIN + < VIN                                          | ۷-                                |                |                  |                  |                 |       |

|               | 0 = VIN + > VIN                                          | 1                                 |                |                  |                  |                 |       |

#### REGISTER 20-1: CMSTAT: COMPARATOR STATUS REGISTER

NOTES:

#### 26.2 AC Characteristics and Timing Parameters

This section defines dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family AC characteristics and timing parameters.

#### TABLE 26-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)                                                                                                                                                                                                               |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC CHARACTERISTICS | $\begin{array}{ll} \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \\ \mbox{Operating voltage VDD range as described in Section 26.1 "DC Characteristics".} \end{array}$ |

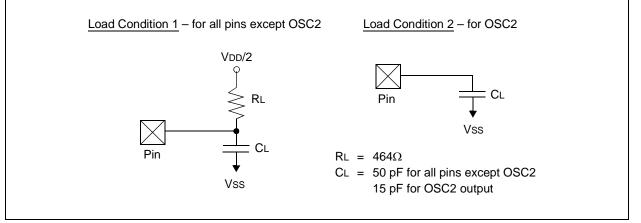

#### FIGURE 26-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 26-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Тур | Max | Units | Conditions                                                   |

|--------------|--------|-----------------------|-----|-----|-----|-------|--------------------------------------------------------------|

| DO50         | Cosc2  | OSC2/SOSC2 Pin        |     | _   | 15  | pF    | In MS and HS modes when external clock is used to drive OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | —   | —   | 50  | pF    | EC mode                                                      |

| DO58         | Св     | SCLx, SDAx            |     |     | 400 | pF    | In I <sup>2</sup> C™ mode                                    |

| AC CHARACTERISTICS (unless otherw |                                          |                                             | Standard Operating<br>(unless otherwise<br>Operating temperate | 2   |     |     |  |

|-----------------------------------|------------------------------------------|---------------------------------------------|----------------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate              | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                     | CKE | СКР | SMP |  |

| 15 MHz                            | Table 26-30                              | —                                           | —                                                              | 0,1 | 0,1 | 0,1 |  |

| 9 MHz                             | —                                        | Table 26-31                                 | —                                                              | 1   | 0,1 | 1   |  |

| 9 MHz                             | —                                        | Table 26-32                                 | —                                                              | 0   | 0,1 | 1   |  |

| 15 MHz                            | _                                        | _                                           | Table 26-33                                                    | 1   | 0   | 0   |  |

| 11 Mhz                            | —                                        | —                                           | Table 26-34                                                    | 1   | 1   | 0   |  |

| 15 MHz                            | _                                        | _                                           | Table 26-35                                                    | 0   | 1   | 0   |  |

| 11 MHz                            |                                          | _                                           | Table 26-36                                                    | 0   | 0   | 0   |  |

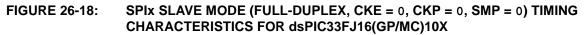

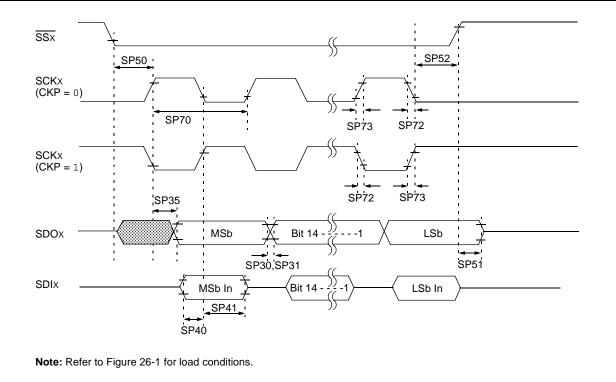

#### FIGURE 26-19: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ32(GP/MC)10X

# TABLE 26-42:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ32(GP/MC)10X

| AC CHARACTERISTICS |                       |                                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                                      |  |

|--------------------|-----------------------|--------------------------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions                           |  |

| SP70               | TscP                  | Maximum SCKx Input Frequency                                 | —                                                     | _                  | 11  | MHz   | See Note 3                           |  |

| SP72               | TscF                  | SCKx Input Fall Time                                         | _                                                     | —                  |     | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP73               | TscR                  | SCKx Input Rise Time                                         | —                                                     | _                  |     | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                   | —                                                     | _                  |     | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                   | —                                                     |                    |     | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                     | 6                  | 20  | ns    |                                      |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                    | _                  |     | ns    |                                      |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                    | —                  | _   | ns    |                                      |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                    | _                  | _   | ns    |                                      |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                   | —                  | _   | ns    |                                      |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10                                                    | —                  | 50  | ns    | See Note 4                           |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 Tcy + 40                                          | —                  | —   | ns    | See Note 4                           |  |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                     | —                                                     | _                  | 50  | ns    |                                      |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

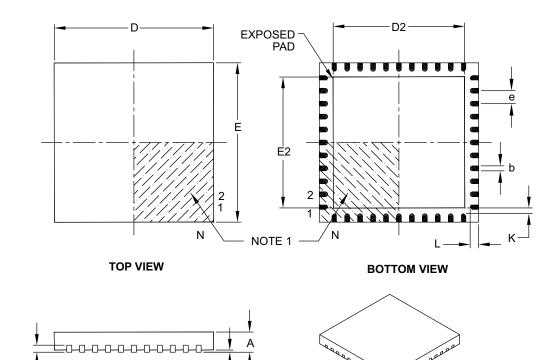

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS   |          |      |  |  |

|------------------------|------------------|---------------|----------|------|--|--|

|                        | Dimension Limits |               |          | MAX  |  |  |

| Number of Pins         | N                |               | 44       |      |  |  |

| Pitch                  | е                |               | 0.65 BSC |      |  |  |

| Overall Height         | A                | 0.80 0.90     |          |      |  |  |

| Standoff               | A1               | 0.00          | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3               | 0.20 REF      |          |      |  |  |

| Overall Width          | E                | 8.00 BSC      |          |      |  |  |

| Exposed Pad Width      | E2               | 6.30          | 6.45     | 6.80 |  |  |

| Overall Length         | D                |               | 8.00 BSC |      |  |  |

| Exposed Pad Length     | D2               | 6.30          | 6.45     | 6.80 |  |  |

| Contact Width          | b                | 0.25 0.30 0.3 |          |      |  |  |

| Contact Length         | L                | 0.30          | 0.40     | 0.50 |  |  |

| Contact-to-Exposed Pad | K                | 0.20          | _        | -    |  |  |

A1

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

A3

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

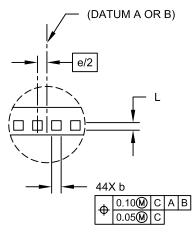

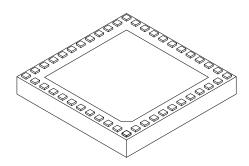

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | MILLIMETERS |          |          |       |  |

|-------------------------|-------------|----------|----------|-------|--|

| Dimension               | Limits      | MIN      | NOM      | MAX   |  |

| Number of Pins          | Ν           |          | 44       |       |  |

| Number of Pins per Side | ND          |          | 12       |       |  |

| Number of Pins per Side | NE          |          | 10       |       |  |

| Pitch                   | е           | 0.50 BSC |          |       |  |

| Overall Height          | А           | 0.80     | 0.90     | 1.00  |  |

| Standoff                | A1          | 0.025    | -        | 0.075 |  |

| Overall Width           | E           |          | 6.00 BSC |       |  |

| Exposed Pad Width       | E2          | 4.40     | 4.55     | 4.70  |  |

| Overall Length          | D           |          | 6.00 BSC |       |  |

| Exposed Pad Length      | D2          | 4.40     | 4.55     | 4.70  |  |

| Contact Width           | b           | 0.20     | 0.25     | 0.30  |  |

| Contact Length          | L           | 0.20     | 0.25     | 0.30  |  |

| Contact-to-Exposed Pad  | К           | 0.20     | -        | -     |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-157C Sheet 2 of 2

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Tape and Reel FI<br>Temperature Rar | amily —<br>y Size (ř<br>ag (if ap<br>nge —— | Kby | /te) / / / / / / / / / / / / / / / /                                                                                                                                                                                                                                               | Exa<br>a) | amples:<br>dsPIC33FJ16MC102-E/SP:<br>Motor Control dsPIC33,<br>16-Kbyte Program Memory,<br>28-Pin, Extended Temperature,<br>SPDIP package. |

|-------------------------------------|---------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture:                       | 33                                          | =   | 16-bit Digital Signal Controller                                                                                                                                                                                                                                                   |           |                                                                                                                                            |

| Flash Memory Family:                | FJ                                          | =   | Flash program memory, 3.3V                                                                                                                                                                                                                                                         |           |                                                                                                                                            |

| Product Group:                      | GP1<br>MC1                                  | =   |                                                                                                                                                                                                                                                                                    |           |                                                                                                                                            |

| Pin Count:                          | 01<br>02                                    | =   |                                                                                                                                                                                                                                                                                    |           |                                                                                                                                            |

| Temperature Range:                  | l<br>E                                      | =   | -40°C to +85°C (Industrial)<br>-40°C to +125°C (Extended)                                                                                                                                                                                                                          |           |                                                                                                                                            |

| Package:                            | P<br>SS<br>SP<br>SO<br>ML<br>PT<br>TL       |     | Plastic Shrink Small Outline - 5.3 mm body (SSOP)<br>Skinny Plastic Dual In-Line - 300 mil body (SPDIP)<br>Plastic Small Outline - Wide - 7.50 mil body (SOIC)<br>Plastic Quad, No Lead - (28-pin) 6x6 mm body (QFN)<br>Plastic Thin Quad Flatpack - (44-pin) 10x10 mm body (TQFP) |           |                                                                                                                                            |