#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Decalis                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16mc102-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest family reference sections of the "dsPIC33/PIC24 Family Reference Manual", which are available the Microchip from web site (www.microchip.com).

This data sheet contains device-specific information for dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 Digital Signal Controller (DSC) devices. These devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit microcontroller (MCU) architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules in the dsPIC33FJ16(GP/ MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family of devices. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

## 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 ALU is 16 bits wide, and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-Bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

### 3.5.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

# 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

# 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or Integer DSP Multiply (IF)

- Signed or Unsigned DSP Multiply (US)

- · Conventional or Convergent Rounding (RND)

- · Automatic Saturation On/Off for ACCA (SATA)

- Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

A block diagram of the DSP engine is shown in Figure 3-3.

| TABLE 3-1: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

| Instruction | Algebraic<br>Operation | ACC Write<br>Back |

|-------------|------------------------|-------------------|

| CLR         | A = 0                  | Yes               |

| ED          | $A = (x - y)^2$        | No                |

| EDAC        | $A = A + (x - y)^2$    | No                |

| MAC         | A = A + (x * y)        | Yes               |

| MAC         | $A = A + x^2$          | No                |

| MOVSAC      | No change in A         | Yes               |

| MPY         | A = x * y              | No                |

| MPY         | $A = x^2$              | No                |

| MPY.N       | A = -x * y             | No                |

| MSC         | A = A - x * y          | Yes               |

| I  | File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|----|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| TR | RISA         | 02C0        |        | -      | —      | -      | _      |        | TRISA< | 10:7> |       |       | —     |       |       | TRISA<4:0> |       |       | 001F          |

| PC | ORTA         | 02C2        |        |        | —      |        | _      |        | RA<10  | ):7>  |       | —     | _     |       |       | RA<4:0>    |       |       | xxxx          |

| LA | TA           | 02C4        | _      | _      | _      | _      | -      |        | LATA<1 | 0:7>  |       | —     | _     |       |       | LATA<4:0>  |       |       | xxxx          |

| 0  | DCA          | 02C6        |        |        | _      | _      | _      |        | ODCA<  | 10:7> |       | _     | _     |       | ODCA  | <3:2>      |       |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-30: PORTB REGISTER MAP FOR dsPIC33FJ16GP101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|---------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        | TRISB< | :15:14> | _      | _      | _      | _      | -     | TRISB<9:7 | >     | _     | _     | TRISB4 | _     | _     | TRISE | 3<1:0> | C393          |

| PORTB     | 02CA        | RB<1   | 5:14>   | _      | _      | _      | _      |       | RB<9:7>   |       | _     | _     | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        | LATB<  | 15:14>  | _      | _      | —      | —      |       | LATB<9:7> | •     |       | _     | LATB4  | —     | _     | LATB  | <1:0>  | xxxx          |

| ODCB      | 02CE        | ODCB<  | :15:14> | _      | _      | -      | -      | (     | ODCB<9:7: | >     |       | _     | ODCB4  | _     | _     | _     |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-31: PORTB REGISTER MAP FOR dsPIC33FJ16MC101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|--------|---------|--------|--------|--------|-------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        |        | TRISB< | <15:12> |        | _      | _      | 1     | RISB<9:7: | >     | _     | _     | TRISB4 | _     | —     | TRISE | 3<1:0> | F393          |

| PORTB     | 02CA        |        | RB<1   | 5:12>   |        |        | _      |       | RB<9:7>   |       | _     |       | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        |        | LATB<  | 15:12>  |        |        | _      |       | LATB<9:7> | •     | _     |       | LATB4  | _     | _     | LATB  | <1:0>  | xxxx          |

| ODCB      | 02CE        |        | ODCB<  | <15:12> |        |        | _      | (     | DDCB<9:7: | >     | -     | _     | ODCB4  |       | _     |       |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-32: PORTB REGISTER MAP FOR dsPIC33FJ16(GP/MC)102 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15     | Bit 14      | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|------------|-------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB        | 02C8        |            | TRISB<15:0> |        |        |        |        |       |       |       | FFFF  |       |       |       |       |       |       |               |

| PORTB        | 02CA        |            |             |        |        |        |        |       | RB<1  | 5:0>  |       |       |       |       |       |       |       | xxxx          |

| LATB         | 02CC        |            | LATB<15:0>  |        |        |        |        |       |       |       | xxxx  |       |       |       |       |       |       |               |

| ODCB         | 02CE        | ODCB<15:4> |             |        |        |        |        |       |       | 0000  |       |       |       |       |       |       |       |               |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

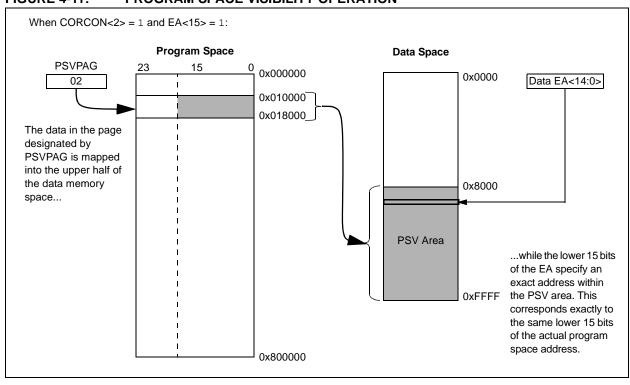

### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL and TBLRDH).

Program space access through the data space occurs if the MSb of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 0x8000 and higher, maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | Table Reads/Writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction using PSV to access data, to execute in a single cycle.

# FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

| U-0     | U-0    | U-0    | U-0    | U-0 | U-0 | U-0 | U-0   |

|---------|--------|--------|--------|-----|-----|-----|-------|

| —       | —      | —      | —      | —   | —   | —   | —     |

| bit 15  |        |        |        |     |     |     | bit 8 |

|         |        |        |        |     |     |     |       |

| U-0     | R/W-1  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0   |

| —       | IC3IP2 | IC3IP1 | IC3IP0 | —   | —   | —   | —     |

| bit 7   |        |        |        |     |     |     | bit 0 |

|         |        |        |        |     |     |     |       |

| Legend: |        |        |        |     |     |     |       |

# REGISTER 7-23: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

|     | iend: |

|-----|-------|

| LCC | ienu. |

|     |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                          |

|----------|---------------------------------------------------------------------|

| bit 6-4  | IC3IP<2:0>: External Interrupt 3 Priority bits                      |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt)          |

|          | •                                                                   |

|          | •                                                                   |

|          | •<br>001 - Interrupt in Priority 1                                  |

|          | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled |

|          |                                                                     |

| bit 3-0  | Unimplemented: Read as '0'                                          |

# REGISTER 7-24: IPC14: INTERRUPT PRIORITY CONTROL REGISTER 14

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1                  | R/W-0                  | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|-------|------------------------|------------------------|------------------------|-----|-----|-----|-------|

| —     | PWM1IP2 <sup>(1)</sup> | PWM1IP1 <sup>(1)</sup> | PWM1IP0 <sup>(1)</sup> | -   | —   | —   | —     |

| bit 7 |                        |                        |                        |     |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 6-4  | PWM1IP<2:0>: PWM1 Interrupt Priority bits <sup>(1)</sup>   |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

| bit 3-0  | Unimplemented: Read as '0'                                 |

|          |                                                            |

Note 1: These bits are available in dsPIC(16/32)MC10X devices only.

| U-0                                | U-0        | U-0             | U-0                                    | U-0                                | R/W-0 | R/W-0  | U-0   |

|------------------------------------|------------|-----------------|----------------------------------------|------------------------------------|-------|--------|-------|

|                                    | —          | —               | _                                      | —                                  | CMPMD | RTCCMD | _     |

| bit 15                             |            |                 |                                        |                                    |       |        | bit 8 |

|                                    |            |                 |                                        |                                    |       |        |       |

| U-0                                | U-0        | U-0             | U-0                                    | U-0                                | U-0   | U-0    | U-0   |

|                                    | —          | —               | _                                      | —                                  | —     | —      | —     |

| bit 7                              |            |                 |                                        |                                    |       |        | bit 0 |

|                                    |            |                 |                                        |                                    |       |        |       |

| Legend:                            |            |                 |                                        |                                    |       |        |       |

| R = Readable                       | e bit      | W = Writable b  | bit                                    | U = Unimplemented bit, read as '0' |       |        |       |

| -n = Value at POR '1' = Bit is set |            |                 | '0' = Bit is cleared x = Bit is unknow |                                    | own   |        |       |

|                                    |            |                 |                                        |                                    |       |        |       |

| bit 15-11                          | Unimplemen | ted: Read as '0 | ,                                      |                                    |       |        |       |

### REGISTER 9-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 10  | CMPMD: Comparator Module Disable bit |

|---------|--------------------------------------|

|         | 1 = Comparator module is disabled    |

|         | 0 = Comparator module is enabled     |

| bit 9   | RTCCMD: RTCC Module Disable bit      |

|         | 1 = RTCC module is disabled          |

|         | 0 = RTCC module is enabled           |

| bit 8-0 | Unimplemented: Read as '0'           |

### REGISTER 9-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0                                | U-0 | U-0 | U-0                                    | U-0 | U-0    | U-0 | U-0   |

|------------------------------------|-----|-----|----------------------------------------|-----|--------|-----|-------|

| —                                  | —   | —   | —                                      | —   | —      | —   | _     |

| bit 15                             |     |     |                                        |     |        |     | bit 8 |

|                                    |     |     |                                        |     |        |     |       |

| U-0                                | U-0 | U-0 | U-0                                    | U-0 | R/W-0  | U-0 | U-0   |

| —                                  | —   | —   | —                                      | —   | CTMUMD | —   | —     |

| bit 7                              |     |     |                                        |     |        |     | bit ( |

|                                    |     |     |                                        |     |        |     |       |

| Legend:                            |     |     |                                        |     |        |     |       |

| R = Readable bit W = Writable bit  |     | bit | U = Unimplemented bit, read as '0'     |     |        |     |       |

| -n = Value at POR '1' = Bit is set |     |     | '0' = Bit is cleared x = Bit is unknow |     | nown   |     |       |

bit 15-3 Unimplemented: Read as '0'

bit 2 CTMUMD: CTMU Module Disable bit

1 = CTMU module is disabled

0 = CTMU module is enabled

bit 1-0 Unimplemented: Read as '0'

# 10.7 Peripheral Pin Select Registers

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family of devices implements up to 23 registers for remappable peripheral configuration.

Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 10.4.3.1 "Control Register Lock" for a specific command sequence.

# REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0                                | U-0                               | U-0 | R/W-1                                           | R/W-1                              | R/W-1  | R/W-1  | R/W-1  |

|------------------------------------|-----------------------------------|-----|-------------------------------------------------|------------------------------------|--------|--------|--------|

| _                                  | —                                 | _   | INT1R4                                          | INT1R3                             | INT1R2 | INT1R1 | INT1R0 |

| bit 15                             |                                   |     |                                                 |                                    |        |        | bit 8  |

|                                    |                                   |     |                                                 |                                    |        |        |        |

| U-0                                | U-0                               | U-0 | U-0                                             | U-0                                | U-0    | U-0    | U-0    |

| —                                  | —                                 | —   | —                                               | —                                  | —      | —      | —      |

| bit 7                              |                                   |     |                                                 |                                    |        |        | bit 0  |

|                                    |                                   |     |                                                 |                                    |        |        |        |

| Legend:                            |                                   |     |                                                 |                                    |        |        |        |

| R = Readable b                     | R = Readable bit W = Writable bit |     | bit                                             | U = Unimplemented bit, read as '0' |        |        |        |

| -n = Value at POR (1' = Bit is set |                                   |     | $0^{\circ}$ = Bit is cleared x = Bit is unknown |                                    |        | nown   |        |

| -n = value a | IT POR  | T = Bit is set                 | 0° = Bit is cleared             | X = Bit is unknown |

|--------------|---------|--------------------------------|---------------------------------|--------------------|

| bit 15-13    | Unimple | mented: Read as '0'            |                                 |                    |

| bit 12-8     | INT1R<4 | 1:0>: Assign External Interr   | upt 1 (INTR1) to the Correspond | ding RPn Pin bits  |

|              |         | Input tied to Vss<br>Reserved  |                                 |                    |

|              | •       |                                |                                 |                    |

|              | •       |                                |                                 |                    |

|              |         | Reserved<br>Input tied to RP25 |                                 |                    |

|              |         |                                |                                 |                    |

|              | •       |                                |                                 |                    |

bit 7-0 Unimplemented: Read as '0'

00001 = Input tied to RP1 00000 = Input tied to RP0

| REGISTER              | 10-4: RPINR                                                                                                   | 4: PERIPHE      | RAL PIN SE            | LECT INPUT            | REGISTER              | 1                     |                       |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| U-0                   | U-0                                                                                                           | U-0             | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 |  |  |  |

| —                     | —                                                                                                             | —               | T5CKR4 <sup>(1)</sup> | T5CKR3 <sup>(1)</sup> | T5CKR2 <sup>(1)</sup> | T5CKR1 <sup>(1)</sup> | T5CKR0 <sup>(1)</sup> |  |  |  |

| bit 15                |                                                                                                               |                 |                       |                       |                       |                       | bit 8                 |  |  |  |

| U-0                   | U-0                                                                                                           | U-0             | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 |  |  |  |

| _                     | _                                                                                                             | _               | T4CKR4 <sup>(1)</sup> | T4CKR3 <sup>(1)</sup> | T4CKR2 <sup>(1)</sup> | T4CKR1 <sup>(1)</sup> | T4CKR0 <sup>(1)</sup> |  |  |  |

| bit 7                 |                                                                                                               |                 |                       |                       |                       |                       | bit (                 |  |  |  |

|                       |                                                                                                               |                 |                       |                       |                       |                       |                       |  |  |  |

| Legend:<br>R = Readab | la hit                                                                                                        | W = Writable    | . hit                 |                       | nantad hit raa        |                       |                       |  |  |  |

|                       |                                                                                                               |                 |                       | -                     | nented bit, read      |                       |                       |  |  |  |

| -n = Value a          | TPOR                                                                                                          | '1' = Bit is se | t                     | '0' = Bit is cle      | ared                  | x = Bit is unkr       | nown                  |  |  |  |

| bit 15-13             | -                                                                                                             | ted: Read as    |                       |                       |                       |                       |                       |  |  |  |

| bit 12-8              | T5CKR<4:0>                                                                                                    | : Assign Time   | r5 External Clo       | ck (T5CK) to th       | ne Correspondi        | ng RPn Pin bits       | <sub>S</sub> (1)      |  |  |  |

|                       | 11111 = Input tied to Vss                                                                                     |                 |                       |                       |                       |                       |                       |  |  |  |

|                       | 11110 = Reserved                                                                                              |                 |                       |                       |                       |                       |                       |  |  |  |

|                       |                                                                                                               |                 |                       |                       |                       |                       |                       |  |  |  |

|                       | •                                                                                                             |                 |                       |                       |                       |                       |                       |  |  |  |

|                       |                                                                                                               |                 |                       |                       |                       |                       |                       |  |  |  |

|                       | 11010 = Res                                                                                                   |                 |                       |                       |                       |                       |                       |  |  |  |

|                       | 11001 = inpu                                                                                                  | It tied to RP25 | )                     |                       |                       |                       |                       |  |  |  |

|                       | •                                                                                                             |                 |                       |                       |                       |                       |                       |  |  |  |

|                       |                                                                                                               |                 |                       |                       |                       |                       |                       |  |  |  |

|                       | 00001 = Input tied to RP1<br>00000 = Input tied to RP0                                                        |                 |                       |                       |                       |                       |                       |  |  |  |

|                       |                                                                                                               |                 | (0)                   |                       |                       |                       |                       |  |  |  |

| bit 7-5               | •                                                                                                             | ted: Read as    |                       |                       | <b>.</b>              |                       | (1)                   |  |  |  |

| bit 4-0               | <b>T4CKR&lt;4:0&gt;:</b> Assign Timer4 External Clock (T4CK) to the Corresponding RPn Pin bits <sup>(1)</sup> |                 |                       |                       |                       |                       |                       |  |  |  |

|                       | 11111 = Inpu<br>11110 = Res                                                                                   |                 |                       |                       |                       |                       |                       |  |  |  |

|                       | •                                                                                                             |                 |                       |                       |                       |                       |                       |  |  |  |

|                       | •                                                                                                             |                 |                       |                       |                       |                       |                       |  |  |  |

|                       | 11010 = Reserved                                                                                              |                 |                       |                       |                       |                       |                       |  |  |  |

|                       |                                                                                                               | it tied to RP25 |                       |                       |                       |                       |                       |  |  |  |

|                       |                                                                                                               |                 |                       |                       |                       |                       |                       |  |  |  |

|                       |                                                                                                               |                 |                       |                       |                       |                       |                       |  |  |  |

|                       |                                                                                                               |                 |                       |                       |                       |                       |                       |  |  |  |

|                       | 00001 = Inpu                                                                                                  |                 |                       |                       |                       |                       |                       |  |  |  |

|                       | 00000 <b>= Inpu</b>                                                                                           | It tied to RP0  |                       |                       |                       |                       |                       |  |  |  |

# REGISTER 10-4: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

### 15.4 PWM Control Registers

#### R/W-0 U-0 R/W-0 U-0 U-0 U-0 U-0 U-0 PTEN PTSIDL bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 PTOPS3 PTOPS2 PTOPS1 PTOPS0 PTCKPS1 PTCKPS0 PTMOD1 PTMOD0 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 PTEN: PWMx Time Base Timer Enable bit 1 = PWMx time base is on 0 = PWMx time base is off bit 14 Unimplemented: Read as '0' bit 13 PTSIDL: PWMx Time Base Stop in Idle Mode bit 1 = PWMx time base halts in CPU Idle mode 0 = PWMx time base runs in CPU Idle mode bit 12-8 Unimplemented: Read as '0' bit 7-4 PTOPS<3:0>: PWMx Time Base Output Postscale Select bits 1111 = 1:16 postscale 0001 = 1:2 postscale 0000 = 1:1 postscale bit 3-2 PTCKPS<1:0>: PWMx Time Base Input Clock Prescale Select bits 11 = PWMx time base input clock period is 64 Tcy (1:64 prescale) 10 = PWMx time base input clock period is 16 Tcy (1:16 prescale) 01 = PWMx time base input clock period is 4 Tcy (1:4 prescale) 00 = PWMx time base input clock period is TCY (1:1 prescale) bit 1-0 PTMOD<1:0>: PWMx Time Base Mode Select bits 11 = PWMx time base operates in a Continuous Up/Down Count mode with interrupts for double **PWM updates** 10 = PWMx time base operates in a Continuous Up/Down Count mode 01 = PWMx time base operates in Single Pulse mode

#### REGISTER 15-1: PxTCON: PWMx TIME BASE CONTROL REGISTER

00 = PWMx time base operates in a Free-Running mode

# REGISTER 20-4: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

| bit 3 | ABEN: AND Gate A1 B Input Inverted Enable bit                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------|

|       | 1 = MBI is connected to AND gate                                                                                  |

|       | 0 = MBI is not connected to AND gate                                                                              |

| bit 2 | ABNEN: AND Gate A1 B Input Inverted Enable bit                                                                    |

|       | <ul><li>1 = Inverted MBI is connected to AND gate</li><li>0 = Inverted MBI is not connected to AND gate</li></ul> |

| bit 1 | AAEN: AND Gate A1 A Input Enable bit                                                                              |

|       | <ul><li>1 = MAI is connected to AND gate</li><li>0 = MAI is not connected to AND gate</li></ul>                   |

| bit 0 | AANEN: AND Gate A1 A Input Inverted Enable bit                                                                    |

|       | <ul><li>1 = Inverted MAI is connected to AND gate</li><li>0 = Inverted MAI is not connected to AND gate</li></ul> |

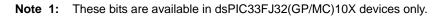

# 21.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 device families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Real-Time Clock and Calendar (RTCC)" (DS70310) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter discusses the Real-Time Clock and Calendar (RTCC) module, available on dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices, and its operation. Some of the key features of the RTCC module are:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- Calendar: weekday, date, month and year

- Alarm configurable

- Year range: 2000 to 2099

- · Leap year correction

- BCD format for compact firmware

- · Optimized for low-power operation

- · User calibration with auto-adjust

- Calibration range: ±2.64 seconds error per month

- Requirements: external 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

The RTCC module is intended for applications where accurate time must be maintained for extended periods of time with minimum to no intervention from the CPU. The RTCC module is optimized for low-power usage to provide extended battery lifetime while keeping track of time.

The RTCC module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099.

The hours are available in 24-hour (military time) format. The clock provides a granularity of one second with half-second visibility to the user.

# FIGURE 21-1: RTCC BLOCK DIAGRAM

Most instructions are a single word. Certain doubleword instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all Table Reads and Writes and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

**Note:** For more details on the instruction set, refer to the *"16-Bit MCU and DSC Programmer's Reference Manual"* (DS70157).

| TABLE 24-1: | SYMBOLS USED IN OPCODE DESCRIPTIONS |

|-------------|-------------------------------------|

|-------------|-------------------------------------|

| Field           | Description                                                                          |  |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------|--|--|--|--|--|

| #text           | Means literal defined by "text"                                                      |  |  |  |  |  |

| (text)          | Means "content of text"                                                              |  |  |  |  |  |

| [text]          | Means "the location addressed by text"                                               |  |  |  |  |  |

| { }             | Optional field or operation                                                          |  |  |  |  |  |

| <n:m></n:m>     | Register bit field                                                                   |  |  |  |  |  |

| .b              | Byte mode selection                                                                  |  |  |  |  |  |

| .d              | Double-Word mode selection                                                           |  |  |  |  |  |

| .S              | Shadow register select                                                               |  |  |  |  |  |

| .W              | Word mode selection (default)                                                        |  |  |  |  |  |

| Acc             | One of two accumulators {A, B}                                                       |  |  |  |  |  |

| AWB             | Accumulator write-back destination address register ∈ {W13, [W13]+ = 2}              |  |  |  |  |  |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |  |  |  |  |  |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |  |  |  |  |  |

| Expr            | Absolute address, label or expression (resolved by the linker)                       |  |  |  |  |  |

| f               | File register address ∈ {0x00000x1FFF}                                               |  |  |  |  |  |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                                 |  |  |  |  |  |

| lit4            | 4-bit unsigned literal $\in \{015\}$                                                 |  |  |  |  |  |

| lit5            | 5-bit unsigned literal $\in \{031\}$                                                 |  |  |  |  |  |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                      |  |  |  |  |  |

| lit10           | 10-bit unsigned literal $\in$ {0255} for Byte mode, {0:1023} for Word mode           |  |  |  |  |  |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                   |  |  |  |  |  |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                   |  |  |  |  |  |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                |  |  |  |  |  |

| None            | Field does not require an entry, can be blank                                        |  |  |  |  |  |

| OA, OB, SA, SB  | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |  |  |  |  |  |

| PC              | Program Counter                                                                      |  |  |  |  |  |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                    |  |  |  |  |  |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                |  |  |  |  |  |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                       |  |  |  |  |  |

| Wb              | Base W register ∈ {W0W15}                                                            |  |  |  |  |  |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |  |  |  |  |  |

| Wdo             | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |  |  |  |  |  |

| Wm, Wn          | Dividend, Divisor Working register pair (direct addressing)                          |  |  |  |  |  |

# 25.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 25.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 25.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 25.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

| DC CHARACTERISTICS                   |                                                                        |     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                |        |                             |  |  |  |

|--------------------------------------|------------------------------------------------------------------------|-----|-------------------------------------------------------|----------------|--------|-----------------------------|--|--|--|

| Parameter Typical <sup>(1)</sup> Max |                                                                        |     | Units                                                 | its Conditions |        |                             |  |  |  |

| Operating Cur                        | Operating Current (IDD) <sup>(2)</sup> – dsPIC33FJ16(GP/MC)10X Devices |     |                                                       |                |        |                             |  |  |  |

| DC20d                                | 0.7                                                                    | 1.7 | mA                                                    | -40°C          |        |                             |  |  |  |

| DC20a                                | 0.7                                                                    | 1.7 | mA                                                    | +25°C          | - 3.3V | LPRC                        |  |  |  |

| DC20b                                | 1.0                                                                    | 1.7 | mA                                                    | +85°C          | 3.3V   | (32.768 kHz) <sup>(3)</sup> |  |  |  |

| DC20c                                | 1.3                                                                    | 1.7 | mA                                                    | +125°C         |        |                             |  |  |  |

| DC21d                                | 1.9                                                                    | 2.6 | mA                                                    | -40°C          |        |                             |  |  |  |

| DC21a                                | 1.9                                                                    | 2.6 | mA                                                    | +25°C          | 3.3V   | 1 MIPS <sup>(3)</sup>       |  |  |  |

| DC21b                                | 1.9                                                                    | 2.6 | mA                                                    | +85°C          |        | T MIPS(*)                   |  |  |  |

| DC21c                                | 2.0                                                                    | 2.6 | mA                                                    | +125°C         |        |                             |  |  |  |

| DC22d                                | 6.5                                                                    | 8.5 | mA                                                    | -40°C          |        |                             |  |  |  |

| DC22a                                | 6.5                                                                    | 8.5 | mA                                                    | +25°C          | - 3.3V | 4 MIPS <sup>(3)</sup>       |  |  |  |

| DC22b                                | 6.5                                                                    | 8.5 | mA                                                    | +85°C          | 3.3V   | 4 MIP5(**                   |  |  |  |

| DC22c                                | 6.5                                                                    | 8.5 | mA                                                    | +125°C         |        |                             |  |  |  |

| DC23d                                | 12.2                                                                   | 16  | mA                                                    | -40°C          |        | 10 MIPS <sup>(3)</sup>      |  |  |  |

| DC23a                                | 12.2                                                                   | 16  | mA                                                    | +25°C          | 2.21/  |                             |  |  |  |

| DC23b                                | 12.2                                                                   | 16  | mA                                                    | +85°C          | - 3.3V | 10 MIPS**                   |  |  |  |

| DC23c                                | 12.2                                                                   | 16  | mA                                                    | +125°C         | ]      |                             |  |  |  |

| DC24d                                | 16                                                                     | 21  | mA                                                    | -40°C          |        |                             |  |  |  |

| DC24a                                | 16                                                                     | 21  | mA                                                    | +25°C          | 3.3V   |                             |  |  |  |

| DC24b                                | 16                                                                     | 21  | mA                                                    | +85°C          | 3.3V   | 16 MIPS                     |  |  |  |

| DC24c                                | 16                                                                     | 21  | mA                                                    | +125°C         | ]      |                             |  |  |  |

### TABLE 26-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

- Oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (PMDx bits are all zeroed)

- CPU executing while(1) statement

- 3: These parameters are characterized, but not tested in manufacturing.

| AC CHARACTERISTICS |               |                                                                                    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |                |                   |                           |  |

|--------------------|---------------|------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------|----------------|-------------------|---------------------------|--|

| Param<br>No.       | Symb          | Characteristic                                                                     | Min                                                   | Тур <sup>(1)</sup> | Max            | Units             | Conditions                |  |

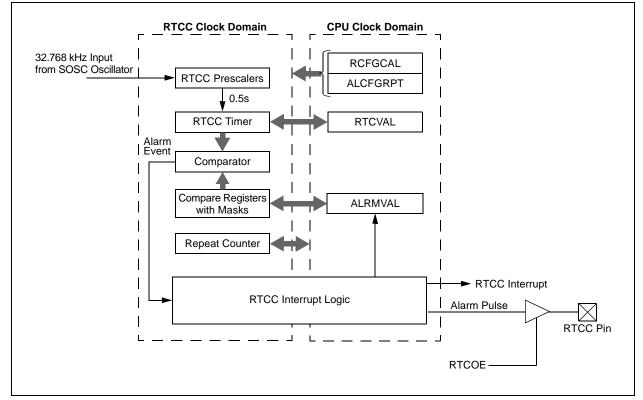

| OS10               | Fin           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                    | _                  | 32             | MHz               | EC                        |  |

|                    |               | Oscillator Crystal Frequency                                                       | 3.0<br>10<br>31                                       |                    | 10<br>32<br>33 | MHz<br>MHz<br>kHz | MS<br>HS<br>SOSC          |  |

| OS20               | Tosc          | Tosc = 1/Fosc                                                                      | 31.25                                                 | —                  | DC             | ns                |                           |  |

| OS25               | Тсү           | Instruction Cycle Time <sup>(2,4)</sup>                                            | 62.5                                                  | _                  | DC             | ns                |                           |  |

| OS30               | TosL,<br>TosH | External Clock in (OSC1) <sup>(5)</sup><br>High or Low Time                        | 0.45 x Tosc                                           | —                  | _              | ns                | EC                        |  |

| OS31               | TosR,<br>TosF | External Clock in (OSC1) <sup>(5)</sup><br>Rise or Fall Time                       | -                                                     | _                  | 20             | ns                | EC                        |  |

| OS40               | TckR          | CLKO Rise Time <sup>(3,5)</sup>                                                    |                                                       | 6                  | 10             | ns                |                           |  |

| OS41               | TckF          | CLKO Fall Time <sup>(3,5)</sup>                                                    |                                                       | 6                  | 10             | ns                |                           |  |

| OS42               | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                             | 14                                                    | 16                 | 18             | mA/V              | VDD = 3.3V,<br>TA = +25°C |  |

### TABLE 26-16: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: Instruction cycle period (TCY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: These parameters are characterized by similarity, but are tested in manufacturing at FIN = 32 MHz only.

- **5:** These parameters are characterized by similarity, but are not tested in manufacturing.

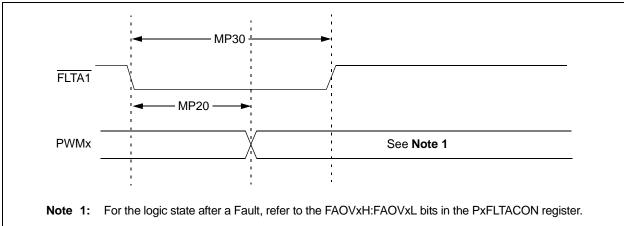

### FIGURE 26-9: MOTOR CONTROL PWMx MODULE FAULT TIMING CHARACTERISTICS

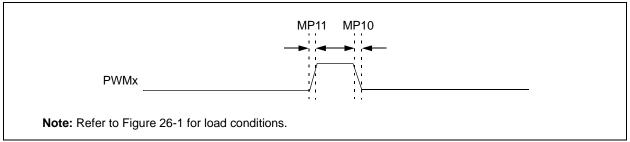

# FIGURE 26-10: MOTOR CONTROL PWMx MODULE TIMING CHARACTERISTICS

# TABLE 26-28: MOTOR CONTROL PWMx MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                              |   |    |    |                    |

|--------------------|--------|-------------------------------------------------------|------------------------------|---|----|----|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                         | Min Typ Max Units Conditions |   |    |    | Conditions         |

| MP10               | TFPWM  | PWM Output Fall Time                                  | —                            | — | —  | ns | See Parameter DO32 |

| MP11               | TRPWM  | PWM Output Rise Time                                  | —                            | — |    | ns | See Parameter DO31 |

| MP20               | Tfd    | Fault Input ↓ to PWM<br>I/O Change                    | —                            | — | 50 | ns |                    |

| MP30               | Tfh    | Minimum Pulse Width                                   | 50                           | _ |    | ns |                    |

**Note 1:** These parameters are characterized by similarity, but are not tested in manufacturing.

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

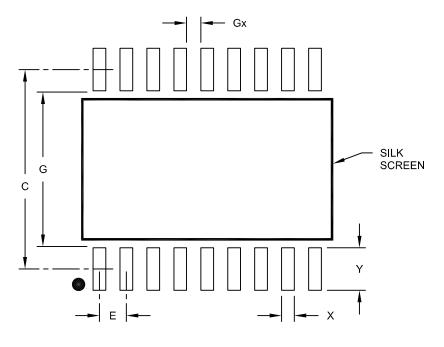

# RECOMMENDED LAND PATTERN

|                       | Units            | MILLIMETERS |      |      |  |

|-----------------------|------------------|-------------|------|------|--|

| Dimension             | Dimension Limits |             | NOM  | MAX  |  |

| Contact Pitch         | E                | 1.27 BSC    |      |      |  |

| Contact Pad Spacing   | С                |             | 9.40 |      |  |

| Contact Pad Width     | Х                |             |      | 0.60 |  |

| Contact Pad Length    | Y                |             |      | 2.00 |  |

| Distance Between Pads | Gx               | 0.67        |      |      |  |

| Distance Between Pads | G                | 7.40        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A

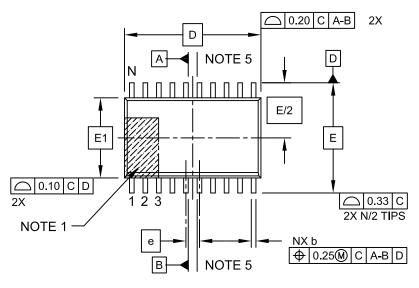

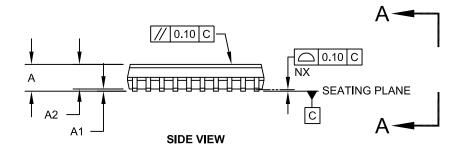

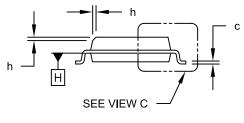

# 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

TOP VIEW

VIEW A-A

Microchip Technology Drawing C04-094C Sheet 1 of 2

# **Revision E (September 2012)**

This revision includes updates to the values in **Section 26.0** "**Electrical Characteristics**" and updated packaging diagrams in **Section 28.0** "**Packaging Information**". There are minor text edits throughout the document.

# Revision F (January 2014)

This revision adds the High-Temperature Electrical Characteristics chapter and updated packaging diagrams in **Section 28.0** "**Packaging Information**". There are minor text edits throughout the document.