Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K × 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16mc102-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. The following pages show their pinout diagrams.

|                  |      | rte)                  |              |                 | Rem                           | appa          | ble l          | Perip | herals                             | 5   | М                 |            | Ŋ                    |      |      |             |      |          |                                 |

|------------------|------|-----------------------|--------------|-----------------|-------------------------------|---------------|----------------|-------|------------------------------------|-----|-------------------|------------|----------------------|------|------|-------------|------|----------|---------------------------------|

| Device           | Pins | Program Flash (Kbyte) | RAM (Kbytes) | Remappable Pins | 16-bit Timer <sup>(1,2)</sup> | Input Capture | Output Compare | UART  | External Interrupts <sup>(3)</sup> | SPI | Motor Control PWM | PWM Faults | 10-Bit, 1.1 Msps ADC | RTCC | I²C™ | Comparators | CTMU | I/O Pins | Packages                        |

| dsPIC33FJ16GP101 | 18   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 13       | PDIP,<br>SOIC                   |

|                  | 20   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | SSOP                            |

| dsPIC33FJ16GP102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | _          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

| dsPIC33FJ16MC101 | 20   | 16                    | 1            | 10              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 1          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | PDIP,<br>SOIC,<br>SSOP          |

| dsPIC33FJ16MC102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

#### TABLE 1:dsPIC33FJ16(GP/MC)101/102 DEVICE FEATURES

**Note 1:** Two out of three timers are remappable.

2: One pair can be combined to create one 32-bit timer.

**3**: Two out of three interrupts are remappable.

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts are disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                                                                       |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | 1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                  |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of a magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                                                       |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                     |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                                    |

| Note 1: | This bit can be read or cleared (not set).                                                                                                                                                                                                                                                                                                                                                                                                 |

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8        | Bit 7        | Bit 6  | Bit 5     | Bit 4         | Bit 3        | Bit 2        | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|---------|--------------|--------------|--------|-----------|---------------|--------------|--------------|---------|-------|---------------|

| WREG0    | 0000        |        |        |        |        |        |        |         | Working Re   | egister 0    |        |           |               |              |              |         |       | xxxx          |

| WREG1    | 0002        |        |        |        |        |        |        |         | Working Re   | egister 1    |        |           |               |              |              |         |       | xxxx          |

| WREG2    | 0004        |        |        |        |        |        |        |         | Working Re   | egister 2    |        |           |               |              |              |         |       | xxxx          |

| WREG3    | 0006        |        |        |        |        |        |        |         | Working Re   | egister 3    |        |           |               |              |              |         |       | xxxx          |

| WREG4    | 0008        |        |        |        |        |        |        |         | Working Re   | egister 4    |        |           |               |              |              |         |       | xxxx          |

| WREG5    | 000A        |        |        |        |        |        |        |         | Working Re   | egister 5    |        |           |               |              |              |         |       | xxxx          |

| WREG6    | 000C        |        |        |        |        |        |        |         | Working Re   | egister 6    |        |           |               |              |              |         |       | xxxx          |

| WREG7    | 000E        |        |        |        |        |        |        |         | Working Re   | egister 7    |        |           |               |              |              |         |       | xxxx          |

| WREG8    | 0010        |        |        |        |        |        |        |         | Working Re   | egister 8    |        |           |               |              |              |         |       | xxxx          |

| WREG9    | 0012        |        |        |        |        |        |        |         | Working Re   | egister 9    |        |           |               |              |              |         |       | xxxx          |

| WREG10   | 0014        |        |        |        |        |        |        |         | Working Re   | gister 10    |        |           |               |              |              |         |       | xxxx          |

| WREG11   | 0016        |        |        |        |        |        |        |         | Working Re   | gister 11    |        |           |               |              |              |         |       | xxxx          |

| WREG12   | 0018        |        |        |        |        |        |        |         | Working Re   | gister 12    |        |           |               |              |              |         |       | xxxx          |

| WREG13   | 001A        |        |        |        |        |        |        |         | Working Re   | gister 13    |        |           |               |              |              |         |       | xxxx          |

| WREG14   | 001C        |        |        |        |        |        |        |         | Working Re   | gister 14    |        |           |               |              |              |         |       | xxxx          |

| WREG15   | 001E        |        |        |        |        |        |        |         | Working Re   | gister 15    |        |           |               |              |              |         |       | 0800          |

| SPLIM    | 0020        |        |        |        |        |        |        | Sta     | ck Pointer L | imit Registe | r      |           |               |              |              |         |       | XXXX          |

| ACCAL    | 0022        |        |        |        |        |        |        | Accum   | ulator A Lov | v Word Reg   | ister  |           |               |              |              |         |       | XXXX          |

| ACCAH    | 0024        |        |        |        |        |        |        | Accum   | ulator A Hig | h Word Reg   | ister  |           |               |              |              |         |       | XXXX          |

| ACCAU    | 0026        |        |        |        |        |        |        | Accumu  | ulator A Upp | er Word Re   | gister |           |               |              |              |         |       | xxxx          |

| ACCBL    | 0028        |        |        |        |        |        |        | Accum   | ulator B Lov | v Word Reg   | ister  |           |               |              |              |         |       | xxxx          |

| ACCBH    | 002A        |        |        |        |        |        |        | Accum   | ulator B Hig | h Word Reg   | ister  |           |               |              |              |         |       | xxxx          |

| ACCBU    | 002C        |        |        |        |        |        |        | Accumu  | ulator B Upp | er Word Re   | gister |           |               |              |              |         |       | xxxx          |

| PCL      | 002E        |        |        |        |        |        |        | Progran | n Counter Lo | w Word Re    | gister |           |               |              |              |         |       | 0000          |

| PCH      | 0030        | —      | —      | —      |        |        |        | _       | —            |              |        | Progra    | m Counter     | High Byte R  | egister      |         |       | 0000          |

| TBLPAG   | 0032        | —      | —      | —      |        |        |        | _       | —            |              |        | Table F   | age Addre     | ss Pointer R | egister      |         |       | 0000          |

| PSVPAG   | 0034        | —      | —      | —      |        |        |        | _       | —            |              | Progra | am Memory | Visibility Pa | age Address  | s Pointer Re | egister |       | 0000          |

| RCOUNT   | 0036        |        |        |        |        |        |        | Repe    | eat Loop Co  | unter Regist | er     |           |               |              |              |         |       | xxxx          |

| DCOUNT   | 0038        |        |        |        |        |        |        |         | DCOUNT       | <15:0>       |        |           |               |              |              |         |       | xxxx          |

| DOSTARTL | 003A        |        |        |        |        |        |        | DOS     | TARTL<15:    | 1>           |        |           |               |              |              |         | 0     | xxxx          |

| DOSTARTH | 003C        | _      | —      | —      | —      | _      | —      |         | -            | —            | —      |           |               | DOSTAR       | TH<5:0>      |         |       | 00xx          |

| DOENDL   | 003E        |        |        |        |        |        |        | DO      | ENDL<15:1    | >            |        |           |               |              |              |         | 0     | XXXX          |

| DOENDH   | 0040        |        | _      | —      | —      | _      | —      |         | _            | —            | _      |           |               | DOE          | NDH          |         |       | 00xx          |

| SR       | 0042        | OA     | OB     | SA     | SB     | OAB    | SAB    | DA      | DC           | IPL2         | IPL1   | IPL0      | RA            | N            | OV           | Z       | С     | 0000          |

#### . . COLL CODE DECISTED MAD

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-23: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJXXGP101 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| RPOR0        | 06C0        |        | _      |        |        |        | RP1R<4:0> | •     |       | —     |       |       |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR2        | 06C4        | _      | _      | _      | _      | _      | —         | _     | _     | _     | _     | _     |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3        | 06C6        | _      | _      | _      |        |        | RP7R<4:0> | •     |       | _     | _     | _     | _     | _     | _          | _     | _     | 0000          |

| RPOR4        | 06C8        | _      | _      |        |        |        | RP9R<4:0> | >     |       | —     |       |       |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR7        | 06CE        | _      | _      |        |        |        | RP15R<4:0 | >     |       | —     |       |       |       | F     | RP14R<4:0> | >     |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJXXMC101 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| RPOR0        | 06C0        | _      | _      | _      |        |        | RP1R<4:0> | •     |       | _     | _     | _     |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR2        | 06C4        | _      | _      | _      | —      | _      | _         | _     | _     | _     | _     | _     |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3        | 06C6        | _      | _      | _      |        |        | RP7R<4:0> | •     |       | _     | _     | _     | _     | _     | _          | _     | _     | 0000          |

| RPOR4        | 06C8        | _      | _      | _      |        |        | RP9R<4:0> | •     |       | _     | _     | _     |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR6        | 06CC        | _      | _      | _      |        |        | RP13R<4:0 | >     |       | _     | _     | _     |       | F     | RP12R<4:0> |       |       | 0000          |

| RPOR7        | 06CE        |        | _      | -      |        |        | RP15R<4:0 | >     |       | _     | _     | _     |       | F     | RP14R<4:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-25: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJXX(GP/MC)102 DEVICES

|              |             |        |        |        |        |        |           |       |       |       |       | •····•, |       |       |            |       |       |               |

|--------------|-------------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|---------|-------|-------|------------|-------|-------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

| RPOR0        | 06C0        | -      | —      | —      |        |        | RP1R<4:0> | >     |       | -     | —     | —       |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR1        | 06C2        | _      | _      | _      |        |        | RP3R<4:0> | >     |       | _     | _     | —       |       |       | RP2R<4:0>  |       |       | 0000          |

| RPOR2        | 06C4        | _      | _      | _      |        |        | RP5R<4:0> | >     |       | _     | _     | —       |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3        | 06C6        | _      | _      | _      |        |        | RP7R<4:0> | >     |       | _     | _     | —       |       |       | RP6R<4:0>  |       |       | 0000          |

| RPOR4        | 06C8        | _      | _      | _      |        |        | RP9R<4:0> | >     |       | _     | _     | —       |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR5        | 06CA        | _      | _      | _      |        |        | RP11R<4:0 | >     |       | _     | _     | —       |       | I     | RP10R<4:0> |       |       | 0000          |

| RPOR6        | 06CC        | _      | _      | _      |        |        | RP13R<4:0 | >     |       | _     | _     | —       |       | I     | RP12R<4:0> |       |       | 0000          |

| RPOR7        | 06CE        | _      | —      | _      |        |        | RP15R<4:0 | >     |       | _     | —     | —       |       |       | RP14R<4:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2014 Microchip Technology Inc.

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| bit 15          |     |                  |     |                     |              |                 | bit 8 |

|-----------------|-----|------------------|-----|---------------------|--------------|-----------------|-------|

| W-0             | W-0 | W-0              | W-0 | W-0                 | W-0          | W-0             | W-0   |

|                 |     |                  | NVM | KEY<7:0>            |              |                 |       |

| bit 7           |     |                  |     |                     |              |                 | bit ( |

|                 |     |                  |     |                     |              |                 |       |

| Legend:         |     |                  |     |                     |              |                 |       |

| R = Readable    | bit | W = Writable bit |     | U = Unimplemer      | nted bit, re | ad as '0'       |       |

| -n = Value at P | OR  | '1' = Bit is set |     | '0' = Bit is cleare | ed           | x = Bit is unkn | iown  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register bits (write-only)

| D / M A       | D 444 A                                                                  | D.4.4. 0                            | DAMA            | DALLA             | DALLA           | DAMA            | D 44/ 6 |  |  |  |  |

|---------------|--------------------------------------------------------------------------|-------------------------------------|-----------------|-------------------|-----------------|-----------------|---------|--|--|--|--|

| R/W-0         | R/W-0                                                                    | R/W-0                               | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |

| NSTDIS        | OVAERR                                                                   | OVBERR                              | COVAERR         | COVBERR           | OVATE           | OVBTE           | COVTE   |  |  |  |  |

| bit 15        |                                                                          |                                     |                 |                   |                 |                 | bi      |  |  |  |  |

| R/W-0         | R/W-0                                                                    | U-0                                 | R/W-0           | R/W-0             | R/W-0           | R/W-0           | U-0     |  |  |  |  |

| SFTACERR      |                                                                          | <u> </u>                            | MATHERR         | ADDRERR           | STKERR          | OSCFAIL         |         |  |  |  |  |

| bit 7         | BIVOLINI                                                                 |                                     |                 | ABBRERR           | OTTLETT         | 00017112        | bi      |  |  |  |  |

|               |                                                                          |                                     |                 |                   |                 |                 |         |  |  |  |  |

| Legend:       |                                                                          |                                     |                 |                   |                 |                 |         |  |  |  |  |

| R = Readabl   | e bit                                                                    | W = Writable                        | bit             | U = Unimplem      | ented bit, read | 1 as '0'        |         |  |  |  |  |

| -n = Value at | POR                                                                      | '1' = Bit is set                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |  |  |  |  |

| 6:4 <i>7</i>  |                                                                          | www.unt.Nie.otie.ev.F               | Niachla hit     |                   |                 |                 |         |  |  |  |  |

| bit 15        |                                                                          | rrupt Nesting E<br>nesting is disat |                 |                   |                 |                 |         |  |  |  |  |

|               |                                                                          | nesting is cloat                    |                 |                   |                 |                 |         |  |  |  |  |

| bit 14        | -                                                                        | cumulator A O                       |                 | lag bit           |                 |                 |         |  |  |  |  |

|               | 1 = Trap was                                                             | caused by ove                       | erflow of Accur | nulator A         |                 |                 |         |  |  |  |  |

|               | 0 = Trap was                                                             | not caused by                       | overflow of Ad  | ccumulator A      |                 |                 |         |  |  |  |  |

| bit 13        |                                                                          | cumulator B O                       | -               | -                 |                 |                 |         |  |  |  |  |

|               |                                                                          | caused by ove<br>not caused by      |                 |                   |                 |                 |         |  |  |  |  |

| bit 12        | -                                                                        | -                                   |                 | Dverflow Trap F   | lag hit         |                 |         |  |  |  |  |

|               |                                                                          |                                     | •               | flow of Accumu    | •               |                 |         |  |  |  |  |

|               | •                                                                        | •                                   | •               | overflow of Accu  |                 |                 |         |  |  |  |  |

| bit 11        | COVBERR: A                                                               | Accumulator B                       | Catastrophic C  | Overflow Trap F   | lag bit         |                 |         |  |  |  |  |

|               |                                                                          |                                     |                 | flow of Accumu    |                 |                 |         |  |  |  |  |

|               | -                                                                        | -                                   | -               | overflow of Accu  | umulator B      |                 |         |  |  |  |  |

| bit 10        |                                                                          | Imulator A Ove                      |                 | able bit          |                 |                 |         |  |  |  |  |

|               | ⊥ = Trap over<br>0 = Trap is di                                          | flow of Accum                       | ulator A        |                   |                 |                 |         |  |  |  |  |

| bit 9         |                                                                          | umulator B Ove                      | erflow Trap En  | able bit          |                 |                 |         |  |  |  |  |

|               |                                                                          | flow of Accum                       |                 |                   |                 |                 |         |  |  |  |  |

|               | 0 = Trap is di                                                           | sabled                              |                 |                   |                 |                 |         |  |  |  |  |

| bit 8         | COVTE: Cata                                                              | astrophic Overf                     | low Trap Enab   | ole bit           |                 |                 |         |  |  |  |  |

|               |                                                                          |                                     | erflow of Accur | mulator A or B i  | s enabled       |                 |         |  |  |  |  |

| hit 7         | 0 = Trap is dis                                                          | sabled<br>Shift Accumula            | tor Error State | ia hit            |                 |                 |         |  |  |  |  |

| bit 7         |                                                                          |                                     |                 | llid accumulator  | chift           |                 |         |  |  |  |  |

|               |                                                                          |                                     |                 | invalid accumul   |                 |                 |         |  |  |  |  |

| bit 6         |                                                                          | ithmetic Error :                    | -               |                   |                 |                 |         |  |  |  |  |

|               |                                                                          | or trap was cau                     | -               | -                 |                 |                 |         |  |  |  |  |

|               |                                                                          | r trap was not                      | -               | ivide-by-zero     |                 |                 |         |  |  |  |  |

| bit 5         | •                                                                        | ted: Read as '                      |                 |                   |                 |                 |         |  |  |  |  |

| bit 4         | MATHERR: Arithmetic Error Status bit<br>1 = Math error trap has occurred |                                     |                 |                   |                 |                 |         |  |  |  |  |

|               | 1 14-41                                                                  |                                     | una al          |                   |                 |                 |         |  |  |  |  |

#### INTOONA, INTERDURT CONTROL DECISTER A

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| REGISTER           | 10-5: RPINK                                                  |                                                                                                 | KAL PIN SE | LECT INPUT       | REGISTER        | 1               |       |

|--------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------|------------------|-----------------|-----------------|-------|

| U-0                | U-0                                                          | U-0                                                                                             | R/W-1      | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| —                  | —                                                            | —                                                                                               | IC2R4      | IC2R3            | IC2R2           | IC2R1           | IC2R0 |

| bit 15             |                                                              |                                                                                                 |            |                  |                 |                 | bit 8 |

|                    |                                                              |                                                                                                 |            |                  |                 |                 |       |

| U-0                | U-0                                                          | U-0                                                                                             | R/W-1      | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|                    | —                                                            | —                                                                                               | IC1R4      | IC1R3            | IC1R2           | IC1R1           | IC1R0 |

| bit 7              |                                                              |                                                                                                 |            |                  |                 |                 | bit ( |

| Legend:            |                                                              |                                                                                                 |            |                  |                 |                 |       |

| R = Readabl        | e bit                                                        | W = Writable I                                                                                  | oit        | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at      | POR                                                          | '1' = Bit is set                                                                                |            | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

| bit 7-5<br>bit 4-0 | 11111 = Inpu<br>11110 = Reso<br>11010 = Reso<br>11001 = Inpu | erved<br>erved<br>it tied to RP25<br>it tied to RP1<br>it tied to RP0<br><b>ted:</b> Read as '0 | ),         |                  |                 |                 |       |

| Uit 4-V            | 11111 = Inpu<br>11110 = Rese<br>11010 = Rese                 | erved<br>erved<br>it tied to RP25<br>it tied to RP1                                             |            | to the Corresp   | onding KPN PI   |                 |       |

#### REGISTER 10-5: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0          | U-0           | U-0              | R/W-0           | R/W-0            | R/W-0                    | R/W-0                   | R/W-0 |

|--------------|---------------|------------------|-----------------|------------------|--------------------------|-------------------------|-------|

| —            | —             | —                |                 |                  | RP21R<4:0> <sup>(1</sup> | )                       |       |

| bit 15       |               |                  |                 |                  |                          |                         | bit 8 |

|              |               |                  |                 |                  |                          |                         |       |

| U-0          | U-0           | U-0              | R/W-0           | R/W-0            | R/W-0                    | R/W-0                   | R/W-0 |

| —            | —             | —                |                 |                  | RP20R<4:0> <sup>(1</sup> | 1)                      |       |

| bit 7        |               |                  |                 |                  |                          |                         | bit 0 |

|              |               |                  |                 |                  |                          |                         |       |

| Legend:      |               |                  |                 |                  |                          |                         |       |

| R = Readab   | le bit        | W = Writable     | bit             | U = Unimpler     | nented bit, read         | 1 as '0'                |       |

| -n = Value a | t POR         | '1' = Bit is set |                 | '0' = Bit is cle | ared                     | x = Bit is unkr         | nown  |

|              |               |                  |                 |                  |                          |                         |       |

| bit 15-13    | Unimplemen    | ted: Read as '   | 0'              |                  |                          |                         |       |

| bit 12-8     | RP21R<4:0>    | Peripheral Ou    | tput Function   | is Assigned to   | RP21 Output F            | Pin bits <sup>(1)</sup> |       |

|              | (see Table 10 | -2 for periphera | al function nur | mbers)           |                          |                         |       |

| bit 7-5      |               | ted: Read as '   |                 | •                |                          |                         |       |

| bit 4-0      | -             |                  |                 | is Assigned to   | RP20 Output F            | Pin bits <sup>(1)</sup> |       |

|              |               | -2 for periphera | -               | •                | 20 0 0 0 0 0 0 0 0       |                         |       |

|              |               |                  |                 | 110010/          |                          |                         |       |

#### REGISTER 10-21: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10

Note 1: These bits are available in dsPIC33FJ32(GP/MC)104 devices only.

#### REGISTER 10-22: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0           | U-0               | U-0              | R/W-0          | R/W-0            | R/W-0                    | R/W-0                   | R/W-0 |

|---------------|-------------------|------------------|----------------|------------------|--------------------------|-------------------------|-------|

| _             |                   | _                |                |                  | RP23R<4:0> <sup>(1</sup> | )                       |       |

| bit 15        | Ŀ                 |                  |                |                  |                          |                         | bit 8 |

|               |                   |                  |                |                  |                          |                         |       |

| U-0           | U-0               | U-0              | R/W-0          | R/W-0            | R/W-0                    | R/W-0                   | R/W-0 |

| —             | —                 | —                |                |                  | RP22R<4:0> <sup>(1</sup> | )                       |       |

| bit 7         | ÷                 |                  |                |                  |                          |                         | bit 0 |

|               |                   |                  |                |                  |                          |                         |       |

| Legend:       |                   |                  |                |                  |                          |                         |       |

| R = Readab    | le bit            | W = Writable     | bit            | U = Unimpler     | nented bit, read         | l as '0'                |       |

| -n = Value at | t POR             | '1' = Bit is set |                | '0' = Bit is cle | ared                     | x = Bit is unkr         | nown  |

|               |                   |                  |                |                  |                          |                         |       |

| bit 15-13     | Unimplemen        | ted: Read as '   | 0'             |                  |                          |                         |       |

| bit 12-8      | RP23R<4:0>        | : Peripheral Ou  | tput Function  | is Assigned to   | RP23 Output F            | Pin bits <sup>(1)</sup> |       |

|               | (see Table 10     | -2 for periphera | al function nu | mbers)           |                          |                         |       |

| bit 7-5       | Unimplemen        | ted: Read as '   | 0'             |                  |                          |                         |       |

| bit 4-0       | RP22R<4:0>        | : Peripheral Ou  | tput Function  | is Assigned to   | RP22 Output F            | Pin bits <sup>(1)</sup> |       |

|               |                   | -2 for periphera |                |                  |                          |                         |       |

| Note 1: ⊺     | hese bits are ava | ilable in dePIC  | 33E 132/CD/N   | AC)104 devices   | only                     |                         |       |

|               | nese bits ale ava |                  | 551 552(GF/N   |                  | only.                    |                         |       |

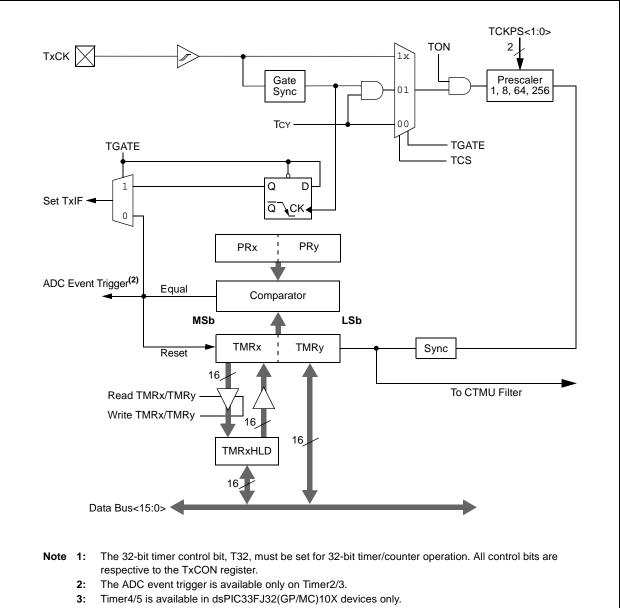

## FIGURE 12-1: TIMER2/3 AND TIMER4/5 (32-BIT) BLOCK DIAGRAM<sup>(1,3,4)</sup>

**4:** Where 'x' or 'y' is present, x = 2 or 4; y = 3 or 5.

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| R/W-0                  | R/W-0 | R/W-0                        | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|------------------------|-------|------------------------------|-------|------------------------------------|-------|--------------------|-------|--|--|

| SEVTDIR <sup>(1)</sup> |       | SEVTCMP<14:8> <sup>(2)</sup> |       |                                    |       |                    |       |  |  |

| bit 15                 |       |                              |       |                                    |       |                    | bit 8 |  |  |

| R/W-0                  | R/W-0 | R/W-0                        | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|                        |       |                              | SEVTC | MP<7:0> <sup>(2)</sup>             |       |                    |       |  |  |

| bit 7                  |       |                              |       |                                    |       |                    | bit 0 |  |  |

| Legend:                |       |                              |       |                                    |       |                    |       |  |  |

| R = Readable           | bit   | W = Writable b               | it    | U = Unimplemented bit, read as '0' |       |                    |       |  |  |

| -n = Value at POR      |       | '1' = Bit is set             |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |  |

#### REGISTER 15-4: PxSECMP: PWMx SPECIAL EVENT COMPARE REGISTER

0 = A Special Event Trigger will occur when the PWMx time base is counting up

bit 14-0 SEVTCMP<14:0>: Special Event Compare Value bits<sup>(2)</sup>

**Note 1:** SEVTDIR is compared with PTDIR (PxTMR<15>) to generate the Special Event Trigger.

2: PxSECMP<14:0> is compared with PxTMR<14:0> to generate the Special Event Trigger.

| R/W-0         | R/W-0                                                                                            | R/W-0                                           | R/W-0 | R/W-0                | R/W-0            | R/W-0              | R/W-0 |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------|-------|----------------------|------------------|--------------------|-------|--|--|--|

| DTBPS1        | DTBPS0                                                                                           | DTB5                                            | DTB4  | DTB3                 | DTB2             | DTB1               | DTB0  |  |  |  |

| bit 15        | •                                                                                                | ·                                               |       | ·                    |                  |                    | bit 8 |  |  |  |

|               |                                                                                                  |                                                 |       |                      |                  |                    |       |  |  |  |

| R/W-0         | R/W-0                                                                                            | R/W-0                                           | R/W-0 | R/W-0                | R/W-0            | R/W-0              | R/W-0 |  |  |  |

| DTAPS1        | DTAPS0                                                                                           | DTA5                                            | DTA4  | DTA3                 | DTA2             | DTA1               | DTA0  |  |  |  |

| bit 7         |                                                                                                  |                                                 |       |                      |                  |                    | bit 0 |  |  |  |

|               |                                                                                                  |                                                 |       |                      |                  |                    |       |  |  |  |

| Legend:       |                                                                                                  |                                                 |       |                      |                  |                    |       |  |  |  |

| R = Readabl   | le bit                                                                                           | W = Writable                                    | bit   | U = Unimpler         | mented bit, read | l as '0'           |       |  |  |  |

| -n = Value at | t POR                                                                                            | '1' = Bit is set                                |       | '0' = Bit is cleared |                  | x = Bit is unknown |       |  |  |  |

|               |                                                                                                  |                                                 |       |                      |                  |                    |       |  |  |  |

| bit 15-14     | DTBPS<1:0>: Dead-Time Unit B Prescale Select bits                                                |                                                 |       |                      |                  |                    |       |  |  |  |

|               |                                                                                                  | 11 = Clock period for Dead-Time Unit B is 8 TCY |       |                      |                  |                    |       |  |  |  |

|               |                                                                                                  | 10 = Clock period for Dead-Time Unit B is 4 Tcy |       |                      |                  |                    |       |  |  |  |

|               | 01 = Clock period for Dead-Time Unit B is 2 Tcy<br>00 = Clock period for Dead-Time Unit B is Tcy |                                                 |       |                      |                  |                    |       |  |  |  |

| bit 13-8      | DTB<5:0>: Unsigned 6-Bit Dead-Time Value for Dead-Time Unit B bits                               |                                                 |       |                      |                  |                    |       |  |  |  |

| bit 7-6       | DTAPS<1:0>: Dead-Time Unit A Prescale Select bits                                                |                                                 |       |                      |                  |                    |       |  |  |  |

|               | 11 = Clock pe                                                                                    | 11 = Clock period for Dead-Time Unit A is 8 Tcy |       |                      |                  |                    |       |  |  |  |

|               |                                                                                                  | 10 = Clock period for Dead-Time Unit A is 4 Tcy |       |                      |                  |                    |       |  |  |  |

|               | 01 = Clock period for Dead-Time Unit A is 2 TCY                                                  |                                                 |       |                      |                  |                    |       |  |  |  |

#### REGISTER 15-7: PxDTCON1: PWMx DEAD-TIME CONTROL REGISTER 1

- 00 = Clock period for Dead-Time Unit A is TCY

- bit 5-0 DTA<5:0>: Unsigned 6-Bit Dead-Time Value for Dead-Time Unit A bits

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| R-0, HSC | R-0, HSC | U-0 | U-0 | U-0 | R/C-0, HS | R-0, HSC | R-0, HSC |

|----------|----------|-----|-----|-----|-----------|----------|----------|

| ACKSTAT  | TRSTAT   | —   | —   | —   | BCL       | GCSTAT   | ADD10    |

| bit 15   |          |     |     |     |           |          | bit 8    |

| R/C-0, HS | R/C-0, HS | R-0, HSC | R/C-0, HSC | R/C-0, HSC | R-0, HSC | R-0, HSC | R-0, HSC |

|-----------|-----------|----------|------------|------------|----------|----------|----------|

| IWCOL     | I2COV     | D_A      | Р          | S          | R_W      | RBF      | TBF      |

| bit 7     | •         |          |            |            |          |          | bit 0    |

| Legend:                  | C = Clearable bit | HSC = Hardware Setta               | ble/Clearable bit  |

|--------------------------|-------------------|------------------------------------|--------------------|

| R = Readable bit         | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR        | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |

| HS = Hardware Settable b | it                |                                    |                    |

| bit 15    | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as $I^2C^{TM}$ master, applicable to master transmit operation)                                                                                                                                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul><li>1 = NACK received from slave</li><li>0 = ACK received from slave</li></ul>                                                                                                                                                                                                                                                                     |

|           | Hardware sets or clears at end of slave Acknowledge.                                                                                                                                                                                                                                                                                                   |

| bit 14    | <ul> <li>TRSTAT: Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)</li> <li>1 = Master transmit is in progress (8 bits + ACK)</li> <li>0 = Master transmit is not in progress</li> <li>Hardware sets at beginning of master transmission. Hardware clears at end of slave Acknowledge.</li> </ul> |

| bit 13-11 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                             |

| bit 10    | BCL: Master Bus Collision Detect bit                                                                                                                                                                                                                                                                                                                   |

|           | <ul> <li>1 = A bus collision has been detected during a master operation</li> <li>0 = No collision</li> <li>Hardware sets at detection of bus collision.</li> </ul>                                                                                                                                                                                    |

| bit 9     | GCSTAT: General Call Status bit                                                                                                                                                                                                                                                                                                                        |

| bit o     | <ul> <li>1 = General call address was received</li> <li>0 = General call address was not received</li> <li>Hardware sets when address matches general call address. Hardware clears at Stop detection.</li> </ul>                                                                                                                                      |

| bit 8     | ADD10: 10-Bit Address Status bit                                                                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = 10-bit address was matched</li> <li>0 = 10-bit address was not matched</li> <li>Hardware sets at match of 2nd byte of matched 10-bit address. Hardware clears at Stop detection.</li> </ul>                                                                                                                                               |

| bit 7     | IWCOL: Write Collision Detect bit                                                                                                                                                                                                                                                                                                                      |

|           | 1 = An attempt to write to the I2CxTRN register failed because the $I^2C$ module is busy<br>0 = No collision                                                                                                                                                                                                                                           |

|           | Hardware sets at occurrence of a write to I2CxTRN while busy (cleared by software).                                                                                                                                                                                                                                                                    |

| bit 6     | I2COV: Receive Overflow Flag bit                                                                                                                                                                                                                                                                                                                       |

|           | 1 = A byte was received while the I2CxRCV register is still holding the previous byte<br>0 = No overflow                                                                                                                                                                                                                                               |

| 1.1. F    | Hardware sets at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                                                                                                                                                                                                                                         |

| bit 5     | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                                                                                                                |

|           | <ul> <li>1 = Indicates that the last byte received was data</li> <li>0 = Indicates that the last byte received was a device address</li> </ul>                                                                                                                                                                                                         |

|           | Hardware clears at device address match. Hardware sets by reception of a slave byte.                                                                                                                                                                                                                                                                   |

#### 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 device families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70635) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four edge input trigger sources

- · Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · Precise time measurement resolution of 200 ps

- Accurate current source suitable for capacitive measurement

- On-chip temperature measurement using a built-in diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 enables the module, the edge delay generation, sequencing of edges, and controls the current source and the output trigger. CTMUCON2 controls the edge source selection, edge source polarity selection and edge sampling mode. The CTMUICON register controls the selection and trim of the current source.

Figure 22-1 shows the CTMU block diagram.

#### 25.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 25.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 25.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 25.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 25.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

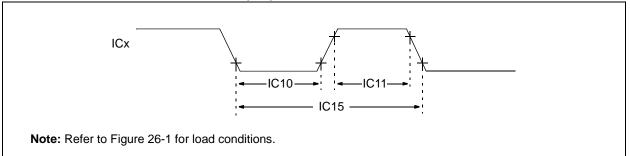

#### FIGURE 26-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

#### TABLE 26-25: INPUT CAPTURE x (ICx) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                      |                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |              |     |       |                                  |  |

|--------------------|--------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|-------|----------------------------------|--|

| Param<br>No.       | Symbol Characteristic <sup>(1)</sup> |                     | istic <sup>(1)</sup>                                                                                                                                                                                                                                                                | Min          | Мах | Units | Conditions                       |  |

| IC10               | TccL                                 | ICx Input Low Time  | No Prescaler                                                                                                                                                                                                                                                                        | 0.5 TCY + 20 | _   | ns    |                                  |  |

|                    |                                      |                     | With Prescaler                                                                                                                                                                                                                                                                      | 10           | —   | ns    |                                  |  |

| IC11               | TccH                                 | ICx Input High Time | No Prescaler                                                                                                                                                                                                                                                                        | 0.5 TCY + 20 | _   | ns    |                                  |  |

|                    |                                      | With Prescaler      |                                                                                                                                                                                                                                                                                     | 10           | _   | ns    |                                  |  |

| IC15               | TccP                                 | ICx Input Period    |                                                                                                                                                                                                                                                                                     | (Tcy + 40)/N | _   | ns    | N = prescale value<br>(1, 4, 16) |  |

**Note 1:** These parameters are characterized by similarity, but are not tested in manufacturing.

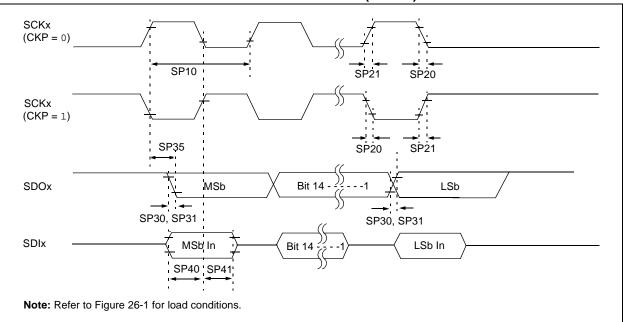

#### FIGURE 26-14: SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS FOR dsPIC33FJ16(GP/MC)10X

# TABLE 26-32:SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ16(GP/MC)10X

| AC CHARACTERISTICS |                       |                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                                       |

|--------------------|-----------------------|-----------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|---------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                 | Min                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions                            |

| SP10               | TscP                  | Maximum SCKx Frequency                        |                                                       | _                  | 10  | MHz   | -40°C to +125°C,<br>see <b>Note 3</b> |

| SP20               | TscF                  | SCKx Output Fall Time                         | _                                                     | —                  | —   | ns    | See Parameter DO32 and <b>Note 4</b>  |

| SP21               | TscR                  | SCKx Output Rise Time                         | _                                                     | —                  | _   | ns    | See Parameter DO31 and <b>Note 4</b>  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                    | _                                                     | _                  | _   | ns    | See Parameter DO32 and <b>Note 4</b>  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                    | _                                                     | _                  | —   | ns    | See Parameter DO31 and <b>Note 4</b>  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge        | _                                                     | 6                  | 20  | ns    |                                       |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                                    | —                  | —   | ns    |                                       |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                                    | _                  |     | ns    |                                       |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge  | 30                                                    | —                  | _   | ns    |                                       |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 100 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.