#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                         |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K × 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16mc102t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

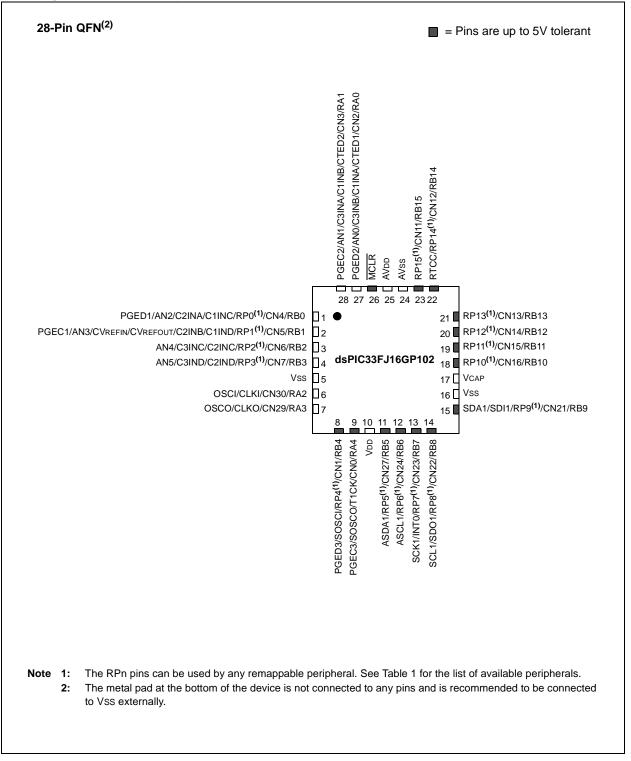

# Pin Diagrams (Continued)

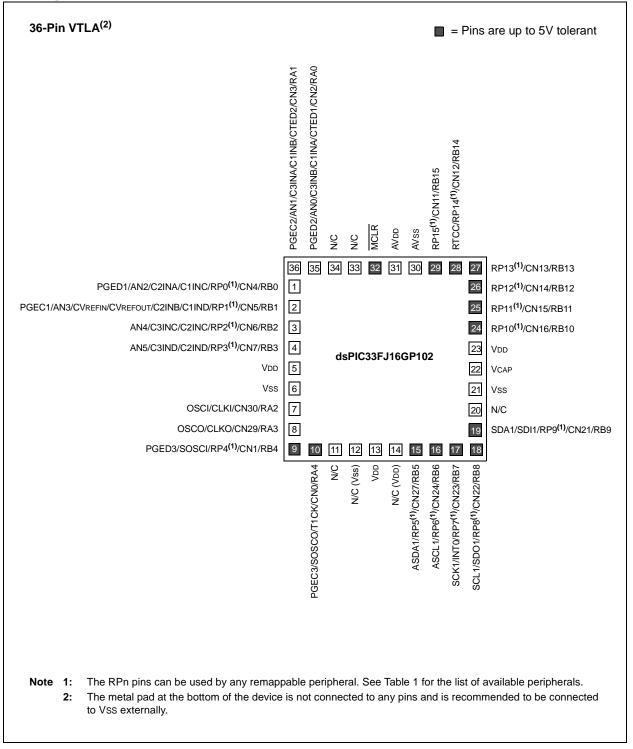

# Pin Diagrams (Continued)

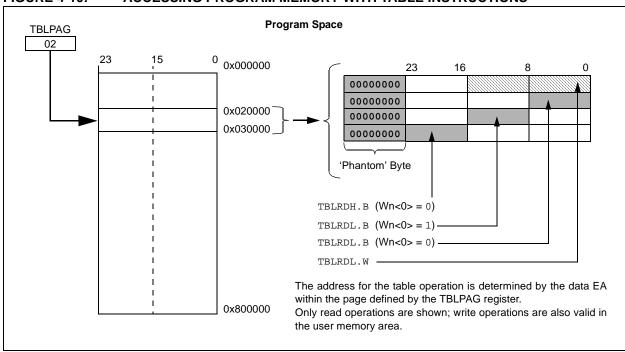

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

#### FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

# 6.3 POR

A POR circuit ensures the device is reset from poweron. The POR circuit is active until VDD crosses the VPOR threshold and the delay, TPOR, has elapsed. The delay, TPOR, ensures that the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to **Section 26.0** "**Electrical Characteristics**" for details.

The Power-on Reset (POR) status bit in the Reset Control (RCON<0>) register is set to indicate the Power-on Reset.

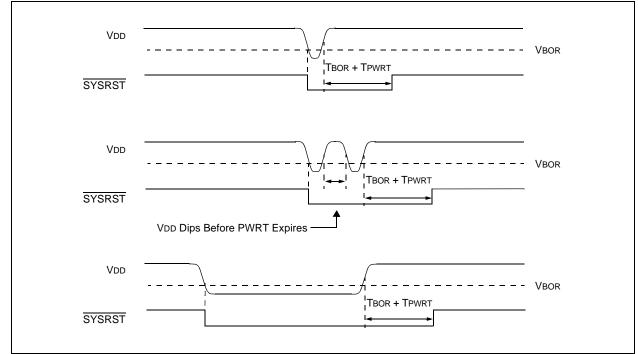

# 6.4 BOR and PWRT

The on-chip regulator has a BOR circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses the VBOR threshold and the delay, TBOR, has elapsed. The delay, TBOR, ensures the voltage regulator output becomes stable.

The Brown-out Reset (BOR) status bit in the Reset Control (RCON<1>) register is set to indicate the Brown-out Reset.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The Power-up Timer (PWRT) provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

Refer to **Section 23.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The Reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point.

#### FIGURE 6-3: BROWN-OUT RESET SITUATIONS

| U-0          | R/W-1                                                                                 | R/W-0                               | R/W-0                 | U-0             | R/W-1             | R/W-0           | R/W-0    |  |  |  |

|--------------|---------------------------------------------------------------------------------------|-------------------------------------|-----------------------|-----------------|-------------------|-----------------|----------|--|--|--|

| —            | CNIP2                                                                                 | CNIP1                               | CNIP0                 | —               | CMIP2             | CMIP1           | CMIP0    |  |  |  |

| bit 15       |                                                                                       |                                     |                       |                 |                   |                 | bit      |  |  |  |

|              | <b>D A A A</b>                                                                        | <b>D</b> 444 o                      | <b>D M</b> ( <b>a</b> |                 | <b>D</b> 444 4    | <b>D</b> 444 o  |          |  |  |  |

| U-0          | R/W-1                                                                                 | R/W-0                               | R/W-0                 | U-0             | R/W-1             | R/W-0           | R/W-0    |  |  |  |

|              | MI2C1IP2                                                                              | MI2C1IP1                            | MI2C1IP0              | —               | SI2C1IP2          | SI2C1IP1        | SI2C1IP0 |  |  |  |

| bit 7        |                                                                                       |                                     |                       |                 |                   |                 | bit      |  |  |  |

| Legend:      |                                                                                       |                                     |                       |                 |                   |                 |          |  |  |  |

| R = Readab   | le bit                                                                                | W = Writable                        | bit                   | U = Unimple     | emented bit, read | d as '0'        |          |  |  |  |

| -n = Value a | t POR                                                                                 | '1' = Bit is set                    |                       | '0' = Bit is cl | eared             | x = Bit is unkr | nown     |  |  |  |

|              |                                                                                       |                                     |                       |                 |                   |                 |          |  |  |  |

| bit 15       | -                                                                                     | ted: Read as '                      |                       |                 |                   |                 |          |  |  |  |

| bit 14-12    |                                                                                       | Change Notifica                     |                       | -               |                   |                 |          |  |  |  |

|              | 111 = Interru                                                                         | pt is Priority 7 (                  | highest priorit       | y interrupt)    |                   |                 |          |  |  |  |

|              | •                                                                                     |                                     |                       |                 |                   |                 |          |  |  |  |

|              | •                                                                                     |                                     |                       |                 |                   |                 |          |  |  |  |

|              | 001 = Interru                                                                         | pt is Priority 1                    |                       |                 |                   |                 |          |  |  |  |

|              | 000 = Interru                                                                         | pt source is dis                    | abled                 |                 |                   |                 |          |  |  |  |

| bit 11       | Unimplemen                                                                            | ted: Read as '                      | 0'                    |                 |                   |                 |          |  |  |  |

| bit 10-8     | CMIP<2:0>: (                                                                          | Comparator Int                      | errupt Priority       | bits            |                   |                 |          |  |  |  |

|              | 111 = Interru                                                                         | pt is Priority 7 (                  | highest priorit       | y interrupt)    |                   |                 |          |  |  |  |

|              | •                                                                                     |                                     |                       |                 |                   |                 |          |  |  |  |

|              | •                                                                                     |                                     |                       |                 |                   |                 |          |  |  |  |

|              | 001 = Interru                                                                         | pt is Priority 1                    |                       |                 |                   |                 |          |  |  |  |

|              |                                                                                       | pt source is dis                    | abled                 |                 |                   |                 |          |  |  |  |

| bit 7        |                                                                                       | Ited: Read as '                     |                       |                 |                   |                 |          |  |  |  |

| bit 6-4      | -                                                                                     | >: I2C1 Master                      |                       | upt Priority bi | ts                |                 |          |  |  |  |

|              |                                                                                       | pt is Priority 7 (                  |                       |                 |                   |                 |          |  |  |  |

|              | •                                                                                     | . ,                                 |                       | , i ,           |                   |                 |          |  |  |  |

|              | •                                                                                     |                                     |                       |                 |                   |                 |          |  |  |  |

|              | •<br>001 = Interru                                                                    | nt in Priority 1                    |                       |                 |                   |                 |          |  |  |  |

|              |                                                                                       | pt is Fridity 1<br>pt source is dis | abled                 |                 |                   |                 |          |  |  |  |

| bit 3        |                                                                                       | -                                   |                       |                 |                   |                 |          |  |  |  |

| bit 2-0      | Unimplemented: Read as '0'<br>SI2C1IP<2:0>: I2C1 Slave Events Interrupt Priority bits |                                     |                       |                 |                   |                 |          |  |  |  |

|              |                                                                                       | pt is Priority 7 (                  | -                     | -               |                   |                 |          |  |  |  |

|              | •                                                                                     |                                     |                       |                 |                   |                 |          |  |  |  |

|              | •                                                                                     |                                     |                       |                 |                   |                 |          |  |  |  |

|              | •                                                                                     |                                     |                       |                 |                   |                 |          |  |  |  |

|              | •<br>•<br>001 = Interru                                                               | pt is Prioritv 1                    |                       |                 |                   |                 |          |  |  |  |

# REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

# 8.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip, 4x PLL to obtain higher speeds of operation.

For example, suppose an 8 MHz crystal is being used with the selected oscillator mode of MS with PLL. This provides a Fosc of 8 MHz \* 4 = 32 MHz. The resultant device operating speed is 32/2 = 16 MIPS.

#### EQUATION 8-2: MS WITH PLL MODE EXAMPLE

```

FCY = \frac{FOSC}{2} = \frac{1}{2} (8000000 • 4) = 16 MIPS

```

| TABLE 8-1: | CONFIGURATION BIT VALU | ES FOR CLOCH | <b>SELECTION</b> |  |

|------------|------------------------|--------------|------------------|--|

|            |                        |              |                  |  |

| Oscillator Mode                                            | Oscillator<br>Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Note |

|------------------------------------------------------------|----------------------|-------------|------------|-------------|

| Fast RC Oscillator with Divide-by-n (FRCDIVN)              | Internal             | xx          | 111        | 1, 2        |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal             | xx          | 110        | 1           |

| Low-Power RC Oscillator (LPRC)                             | Internal             | xx          | 101        | 1           |

| Secondary (Timer1) Oscillator (SOSC)                       | Secondary            | xx          | 100        | 1           |

| Primary Oscillator (MS) with PLL (MSPLL)                   | Primary              | 01          | 011        |             |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary              | 00          | 011        | 1           |

| Primary Oscillator (HS)                                    | Primary              | 10          | 010        |             |

| Primary Oscillator (MS)                                    | Primary              | 01          | 010        |             |

| Primary Oscillator (EC)                                    | Primary              | 00          | 010        | 1           |

| Fast RC Oscillator (FRC) with Divide-by-n and PLL (FRCPLL) | Internal             | xx          | 001        | 1           |

| Fast RC Oscillator (FRC)                                   | Internal             | xx          | 000        | 1           |

**Note 1:** OSC2 pin function is determined by the OSCIOFNC Configuration bit.

**2:** This is the default oscillator mode for an unprogrammed (erased) device.

# 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70193) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

# 10.1 Parallel I/O (PIO) Ports

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Output Latch (LATx) register read the latch. Writes to the Output Latch register write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that is not valid for a particular device will be disabled. This means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| REGISTER      | 10-9: RPINE                 | 20: PERIPH       | ERAL PIN S            | ELECT INPU            | TREGISTER             | 20                      |                       |

|---------------|-----------------------------|------------------|-----------------------|-----------------------|-----------------------|-------------------------|-----------------------|

| U-0           | U-0                         | U-0              | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                   | R/W-1                 |

| —             | —                           | —                | SCK1R4 <sup>(1)</sup> | SCK1R3 <sup>(1)</sup> | SCK1R2 <sup>(1)</sup> | SCK1R1 <sup>(1)</sup>   | SCK1R0 <sup>(1)</sup> |

| bit 15        |                             |                  |                       |                       |                       |                         | bit 8                 |

|               |                             |                  |                       |                       |                       |                         |                       |

| U-0           | U-0                         | U-0              | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                   | R/W-1                 |

|               |                             |                  | SDI1R4 <sup>(1)</sup> | SDI1R3 <sup>(1)</sup> | SDI1R2 <sup>(1)</sup> | SDI1R1 <sup>(1)</sup>   | SDI1R0 <sup>(1)</sup> |

| bit 7         |                             |                  |                       |                       |                       |                         | bit 0                 |

|               |                             |                  |                       |                       |                       |                         |                       |

| Legend:       |                             |                  |                       |                       |                       |                         |                       |

| R = Readabl   |                             | W = Writable     |                       | -                     | nented bit, read      |                         |                       |

| -n = Value at | t POR                       | '1' = Bit is set |                       | '0' = Bit is cle      | ared                  | x = Bit is unkr         | IOWN                  |

| 1 1 4 5 4 0   |                             |                  | o.!                   |                       |                       |                         |                       |

| bit 15-13     | -                           | ted: Read as '   |                       |                       | <b>.</b>              |                         |                       |

| bit 12-8      |                             |                  | Clock Input (S        | CK1IN) to the         | Corresponding         | RPn Pin bits            |                       |

|               | 11111 = Inpu<br>11110 = Res |                  |                       |                       |                       |                         |                       |

|               | 11110 = Res                 | erved            |                       |                       |                       |                         |                       |

|               |                             |                  |                       |                       |                       |                         |                       |

|               |                             |                  |                       |                       |                       |                         |                       |

|               | 11010 = Res                 |                  |                       |                       |                       |                         |                       |

|               | 11001 <b>= I</b> npu        | ut tied to RP25  |                       |                       |                       |                         |                       |

|               | •                           |                  |                       |                       |                       |                         |                       |

|               | •                           |                  |                       |                       |                       |                         |                       |

|               | 00001 = Inpu                | ut tied to RP1   |                       |                       |                       |                         |                       |

|               | 00000 = Inpu                |                  |                       |                       |                       |                         |                       |

| bit 7-5       | Unimplemen                  | ted: Read as '   | 0'                    |                       |                       |                         |                       |

| bit 4-0       | SDI1R<4:0>:                 | Assign SPI1 E    | Data Input (SD        | 11) to the Corre      | esponding RPn         | Pin bits <sup>(1)</sup> |                       |

|               | 11111 <b>= I</b> npu        |                  |                       |                       |                       |                         |                       |

|               | 11110 <b>= Res</b>          | erved            |                       |                       |                       |                         |                       |

|               | •                           |                  |                       |                       |                       |                         |                       |

|               | •                           |                  |                       |                       |                       |                         |                       |

|               | 11010 = Res                 | erved            |                       |                       |                       |                         |                       |

|               |                             | ut tied to RP25  |                       |                       |                       |                         |                       |

|               |                             |                  |                       |                       |                       |                         |                       |

|               |                             |                  |                       |                       |                       |                         |                       |

|               | 00001 = Inpu                | it tied to RP1   |                       |                       |                       |                         |                       |

|               | 000001 = Inpu               |                  |                       |                       |                       |                         |                       |

|               |                             | •                |                       |                       |                       |                         |                       |

# REGISTER 10-9: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

NOTES:

NOTES:

NOTES:

# 18.1 UART Helpful Tips

- In multi-node, direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

# 18.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | the product page using the link above,  |  |  |  |  |  |  |

|       | enter this URL in your browser:         |  |  |  |  |  |  |

|       | http://www.microchip.com/wwwproducts/   |  |  |  |  |  |  |

|       | Devices.aspx?dDocName=en554109          |  |  |  |  |  |  |

### 18.2.1 KEY RESOURCES

- "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33/PIC24 Family Reference Manual"* sections

- Development Tools

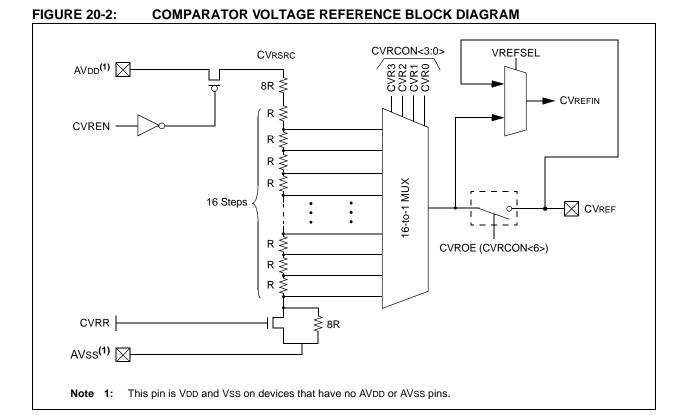

#### FIGURE 20-3: USER-PROGRAMMABLE BLANKING FUNCTION BLOCK DIAGRAM

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| REGISTER      | 20-2: CMxC                                             | ON: COMPA                                                 | RATOR x CO                    | ONTROL REG        | GISTER          |                                      |                |

|---------------|--------------------------------------------------------|-----------------------------------------------------------|-------------------------------|-------------------|-----------------|--------------------------------------|----------------|

| R/W-0         | R/W-0                                                  | R/W-0                                                     | U-0                           | U-0               | U-0             | R/W-0                                | R/W-0          |

| CON           | COE                                                    | CPOL                                                      | _                             | _                 | _               | CEVT                                 | COUT           |

| bit 15        |                                                        |                                                           |                               |                   |                 |                                      | bit 8          |

| R/W-0         | R/W-0                                                  | U-0                                                       | R/W-0                         | U-0               | U-0             | R/W-0                                | R/W-0          |

| EVPOL1        | EVPOL0                                                 | 0-0                                                       | CREF                          |                   |                 | CCH1                                 | CCH0           |

| bit 7         | LVIOLO                                                 |                                                           | GIVEI                         |                   |                 | Com                                  | bit C          |

|               |                                                        |                                                           |                               |                   |                 |                                      |                |

| Legend:       |                                                        |                                                           |                               |                   |                 |                                      |                |

| R = Readable  |                                                        | W = Writable                                              |                               | -                 | nented bit, rea |                                      |                |

| -n = Value at | POR                                                    | '1' = Bit is se                                           | t                             | '0' = Bit is clea | ared            | x = Bit is unkr                      | iown           |

| bit 15        | CON: Compa                                             | arator x Enable                                           | bit                           |                   |                 |                                      |                |

|               | =                                                      | tor x is enable                                           |                               |                   |                 |                                      |                |

|               |                                                        | tor x is disable                                          |                               |                   |                 |                                      |                |

| bit 14        | COE: Compa                                             | arator x Output                                           | Enable bit                    |                   |                 |                                      |                |

|               |                                                        | tor output is pr<br>tor output is in                      | esent on the C<br>ternal only | xOUT pin          |                 |                                      |                |

| bit 13        | CPOL: Comp                                             | parator x Outpu                                           | it Polarity Sele              | ct bit            |                 |                                      |                |

|               |                                                        | tor x output is tor x output is                           |                               |                   |                 |                                      |                |

| bit 12-10     | Unimplemen                                             | ted: Read as                                              | 0'                            |                   |                 |                                      |                |

| bit 9         | CEVT: Comp                                             | arator x Event                                            | bit                           |                   |                 |                                      |                |

|               | interrupts                                             | ator x event ac<br>s until the bit is<br>ator x event dic | cleared                       | POL<1:0> set      | ings occurred   | ; disables future                    | e triggers and |

| bit 8         | COUT: Comp                                             | parator x Outpu                                           | ıt bit                        |                   |                 |                                      |                |

|               | 1 = VIN+ > VI                                          |                                                           | ted polarity):                |                   |                 |                                      |                |

|               | 0 = VIN+ < VI                                          |                                                           |                               |                   |                 |                                      |                |

|               | $\frac{\text{When CPOL}}{1 = \text{VIN+} < \text{VI}}$ | = 1 (inverted p                                           | olarity):                     |                   |                 |                                      |                |

|               | 0 = VIN + > VI                                         |                                                           |                               |                   |                 |                                      |                |

| bit 7-6       | EVPOL<1:0>                                             | . Trigger/Ever                                            | t/Interrupt Pola              | arity Select bits |                 |                                      |                |

|               | 10 = Trigger/                                          |                                                           | is generated                  |                   |                 | ator output (whil<br>tion of the pol |                |

|               | If $CPOL = 1$ (                                        | (inverted polari                                          |                               | 1421.14           |                 |                                      |                |

|               | •                                                      | (non-inverted p                                           | •                             | արտ.              |                 |                                      |                |

|               |                                                        |                                                           | comparator ou                 | ıtput.            |                 |                                      |                |

|               |                                                        | event/interrupt/<br>ator output (wh                       |                               | only on low-      | to-high transi  | tion of the pol                      | arity selected |

|               |                                                        | (inverted polari<br>ransition of the                      | t <u>y):</u><br>comparator οι | itput.            |                 |                                      |                |

|               | -                                                      | (non-inverted p                                           | -                             |                   |                 |                                      |                |

|               | Low-to-high t                                          | ransition of the                                          | comparator o                  | -                 |                 |                                      |                |

|               | 00 = Trigger/                                          | event/interrupt                                           | generation is o               | disabled          |                 |                                      |                |

|               |                                                        | ted: Read as                                              |                               |                   |                 |                                      |                |

#### CISTED 20 2 CMACONI COMPADATOD & CONTROL DECISTED

| Bit Field    | Description                                                                                                                                                                                        |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDTPRE       | Watchdog Timer Prescaler bit                                                                                                                                                                       |

|              | 1 = 1:128                                                                                                                                                                                          |

|              | 0 = 1:32                                                                                                                                                                                           |

| WDTPOST<3:0> | Watchdog Timer Postscaler bits                                                                                                                                                                     |

|              | 1111 = 1:32,768                                                                                                                                                                                    |

|              | 1110 = 1:16,384                                                                                                                                                                                    |

|              |                                                                                                                                                                                                    |

|              |                                                                                                                                                                                                    |

|              | •<br>0001 = 1:2                                                                                                                                                                                    |

|              | 0001 = 1.2<br>0000 = 1:1                                                                                                                                                                           |

| PLLKEN       | PLL Lock Enable bit                                                                                                                                                                                |

|              | 1 = Clock switch to PLL will wait until the PLL lock signal is valid                                                                                                                               |

|              | 0 = Clock switch will not wait for the PLL lock signal                                                                                                                                             |

| ALTI2C       | Alternate I <sup>2</sup> C <sup>™</sup> Pins bit                                                                                                                                                   |

|              | $1 = I^2C$ is mapped to SDA1/SCL1 pins                                                                                                                                                             |

|              | $0 = I^2C$ is mapped to ASDA1/ASCL1 pins                                                                                                                                                           |

| ICS<1:0>     | ICD Communication Channel Select bits                                                                                                                                                              |

|              | 11 = Communicate on PGEC1 and PGED1                                                                                                                                                                |

|              | 10 = Communicate on PGEC2 and PGED2                                                                                                                                                                |

|              | 01 = Communicate on PGEC3 and PGED3                                                                                                                                                                |

| PWMPIN       | 00 = Reserved, do not use Motor Control PWM Module Pin Mode bit                                                                                                                                    |

| PVVIVIPIN    |                                                                                                                                                                                                    |

|              | <ul> <li>1 = PWM module pins controlled by PORT register at device Reset (tri-stated)</li> <li>0 = PWM module pins controlled by PWM module at device Reset (configured as output pins)</li> </ul> |

| HPOL         | Motor Control PWM High Side Polarity bit                                                                                                                                                           |

|              | 1 = PWM module high side output pins have active-high output polarity                                                                                                                              |

|              | 0 = PWM module high side output pins have active-low output polarity                                                                                                                               |

| LPOL         | Motor Control PWM Low Side Polarity bit                                                                                                                                                            |

|              | 1 = PWM module low side output pins have active-high output polarity                                                                                                                               |

|              | 0 = PWM module low side output pins have active-low output polarity                                                                                                                                |

# TABLE 23-4: dsPIC33F CONFIGURATION BITS DESCRIPTION (CONTINUED)

| DC CHARACTERISTICS |                        |               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                               |                  |                             |  |  |

|--------------------|------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------|-----------------------------|--|--|

| Parameter<br>No.   | Typical <sup>(1)</sup> | Мах           | Units Conditions                                                                                                                                                                                                                                                                        |                               |                  |                             |  |  |

| Idle Current (II   | DLE): Core Of          | f, Clock On I | Base Current                                                                                                                                                                                                                                                                            | <sup>(2)</sup> – dsPIC33FJ32( | GP/MC)10X Device | S                           |  |  |

| DC40d              | 0.4                    | 1.0           | mA                                                                                                                                                                                                                                                                                      | -40°C                         |                  |                             |  |  |

| DC40a              | 0.4                    | 1.0           | mA                                                                                                                                                                                                                                                                                      | +25°C                         | - 3.3V           | LPRC                        |  |  |

| DC40b              | 0.4                    | 1.0           | mA                                                                                                                                                                                                                                                                                      | +85°C                         | 3.3 V            | (32.768 kHz) <sup>(3)</sup> |  |  |

| DC40c              | 0.5                    | 1.0           | mA                                                                                                                                                                                                                                                                                      | +125°C                        |                  |                             |  |  |

| DC41d              | 0.5                    | 1.1           | mA                                                                                                                                                                                                                                                                                      | -40°C                         |                  |                             |  |  |

| DC41a              | 0.5                    | 1.1           | mA                                                                                                                                                                                                                                                                                      | +25°C                         | - 3.3V           | 1 MIPS <sup>(3)</sup>       |  |  |

| DC41b              | 0.5                    | 1.1           | mA                                                                                                                                                                                                                                                                                      | +85°C                         | 5.5 V            | T IVITE SY 7                |  |  |

| DC41c              | 0.8                    | 1.1           | mA                                                                                                                                                                                                                                                                                      | +125°C                        |                  |                             |  |  |

| DC42d              | 0.9                    | 1.6           | mA                                                                                                                                                                                                                                                                                      | -40°C                         |                  |                             |  |  |

| DC42a              | 0.9                    | 1.6           | mA                                                                                                                                                                                                                                                                                      | +25°C                         | - 3.3V           | 4 MIPS <sup>(3)</sup>       |  |  |

| DC42b              | 1.0                    | 1.6           | mA                                                                                                                                                                                                                                                                                      | +85°C                         | 3.3V             | 4 10115357                  |  |  |

| DC42c              | 1.2                    | 1.6           | mA                                                                                                                                                                                                                                                                                      | +125°C                        |                  |                             |  |  |

| DC43a              | 1.6                    | 2.6           | mA                                                                                                                                                                                                                                                                                      | +25°C                         |                  |                             |  |  |

| DC43d              | 1.6                    | 2.6           | mA                                                                                                                                                                                                                                                                                      | -40°C                         | - 3.3V           | 10 MIPS <sup>(3)</sup>      |  |  |

| DC43b              | 1.7                    | 2.6           | mA                                                                                                                                                                                                                                                                                      | +85°C                         | 3.3V             | 10 1011-517                 |  |  |

| DC43c              | 2.0                    | 2.6           | mA                                                                                                                                                                                                                                                                                      | +125°C                        |                  |                             |  |  |

| DC44d              | 2.4                    | 3.8           | mA                                                                                                                                                                                                                                                                                      | -40°C                         |                  |                             |  |  |

| DC44a              | 2.4                    | 3.8           | mA                                                                                                                                                                                                                                                                                      | +25°C                         | - 3.3V           | 16 MIPS <sup>(3)</sup>      |  |  |

| DC44b              | 2.6                    | 3.8           | mA                                                                                                                                                                                                                                                                                      | +85°C                         | 3.3V             | 10 1011103-7                |  |  |

| DC44c              | 2.9                    | 3.8           | mA                                                                                                                                                                                                                                                                                      | +125°C                        |                  |                             |  |  |

# TABLE 26-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE) (CONTINUED)

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: Base Idle current is measured as follows:

- CPU core is off, oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- External Secondary Oscillator (SOSC) is disabled (i.e., SOSCO and SOSCI pins are configured as digital I/O inputs)

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (PMDx bits are all zeroed)

- **3:** These parameters are characterized, but not tested in manufacturing.

| AC CH        | ARACTER | RISTICS          |                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                             |  |

|--------------|---------|------------------|---------------------------|-------------------------------------------------------|------|-------|-----------------------------|--|

| Param<br>No. | Symbol  | Charac           | teristic                  | Min <sup>(1)</sup>                                    | Max  | Units | Conditions                  |  |

| IM10         | TLO:SCL | Clock Low Time   | 100 kHz mode              | Tcy/2 (BRG + 1)                                       | _    | μS    |                             |  |

|              |         |                  | 400 kHz mode              | Tcy/2 (BRG + 1)                                       |      | μS    |                             |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                       |      | μS    |                             |  |

| IM11         | THI:SCL | Clock High Time  | 100 kHz mode              | Tcy/2 (BRG + 1)                                       |      | μS    |                             |  |

|              |         |                  | 400 kHz mode              | Tcy/2 (BRG + 1)                                       |      | μS    |                             |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                       |      | μS    |                             |  |

| IM20         | TF:SCL  | SDAx and SCLx    | 100 kHz mode              |                                                       | 300  | ns    | CB is specified to be       |  |

|              |         | Fall Time        | 400 kHz mode              | 20 + 0.1 Св                                           | 300  | ns    | from 10 to 400 pF           |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> |                                                       | 100  | ns    |                             |  |

| IM21         | TR:SCL  | SDAx and SCLx    | 100 kHz mode              | _                                                     | 1000 | ns    | CB is specified to be       |  |

|              |         | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                           | 300  | ns    | from 10 to 400 pF           |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | —                                                     | 300  | ns    | 1                           |  |

| IM25         | TSU:DAT | Data Input       | 100 kHz mode              | 250                                                   | _    | ns    |                             |  |

|              |         | Setup Time       | 400 kHz mode              | 100                                                   |      | ns    | -                           |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 40                                                    |      | ns    | 1                           |  |

| IM26         | THD:DAT | Data Input       | 100 kHz mode              | 0                                                     |      | μS    |                             |  |

|              |         | Hold Time        | 400 kHz mode              | 0                                                     | 0.9  | μS    | -                           |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 0.2                                                   |      | μS    | -                           |  |

| IM30         | TSU:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 1)                                       |      | μS    | Only relevant for           |  |

|              |         | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 1)                                       |      | μS    | Repeated Start              |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                       |      | μS    | condition                   |  |

| IM31         | THD:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 1)                                       |      | μS    | After this period the first |  |

|              |         | Hold Time        | 400 kHz mode              | Tcy/2 (BRG + 1)                                       |      | μS    | clock pulse is generated    |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                       |      | μS    | 1                           |  |

| IM33         | Tsu:sto | Stop Condition   | 100 kHz mode              | Tcy/2 (BRG + 1)                                       |      | μS    |                             |  |

|              |         | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 1)                                       |      | μS    | -                           |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                       |      | μS    | 1                           |  |

| IM34         | THD:STO | Stop Condition   | 100 kHz mode              | Tcy/2 (BRG + 1)                                       |      | ns    |                             |  |

|              |         | Hold Time        | 400 kHz mode              | Tcy/2 (BRG + 1)                                       |      | ns    |                             |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                       |      | ns    |                             |  |

| IM40         | TAA:SCL | Output Valid     | 100 kHz mode              | —                                                     | 3500 | ns    |                             |  |

|              |         | from Clock       | 400 kHz mode              | —                                                     | 1000 | ns    |                             |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                     | 400  | ns    |                             |  |

| IM45         | TBF:SDA | Bus Free Time    | 100 kHz mode              | 4.7                                                   |      | μS    | Time the bus must be        |  |

| -            | _       |                  | 400 kHz mode              | 1.3                                                   |      | μS    | free before a new           |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 0.5                                                   | _    | μs    | transmission can start      |  |

| IM50         | Св      | Bus Capacitive L |                           |                                                       | 400  | pF    |                             |  |

| IM51         | TPGD    | Pulse Gobbler De |                           | 65                                                    | 390  | ns    | See Note 3                  |  |

# TABLE 26-45: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

Note 1: BRG is the value of the I<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70195) in the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site for the latest "dsPIC33/PIC24 Family Reference Manual" sections.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** Typical value for this parameter is 130 ns.

| AC CHARACTERISTICS |        |                                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V}^{(6)} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |          |                                   |       |                                                                                  |  |

|--------------------|--------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------|-------|----------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                      | Min.                                                                                                                                                                                                                                                                                          | Тур      | Max.                              | Units | Conditions                                                                       |  |

|                    |        |                                                                     | Devic                                                                                                                                                                                                                                                                                         | e Suppl  | у                                 |       |                                                                                  |  |

| AD01               | AVdd   | Module VDD Supply <sup>(2,4)</sup>                                  | Greater of:<br>VDD – 0.3<br>or 2.9                                                                                                                                                                                                                                                            | _        | Lesser of:<br>VDD + 0.3<br>or 3.6 | V     |                                                                                  |  |

| AD02               | AVss   | Module Vss Supply <sup>(2,5)</sup>                                  | Vss - 0.3                                                                                                                                                                                                                                                                                     | _        | Vss + 0.3                         | V     |                                                                                  |  |

| AD09               | IAD    | Operating Current                                                   | _                                                                                                                                                                                                                                                                                             | 7.0      | 9.0                               | mA    | See Note 1                                                                       |  |

|                    |        |                                                                     | Anal                                                                                                                                                                                                                                                                                          | og Input | :                                 |       |                                                                                  |  |

| AD12               | VINH   | Input Voltage Range<br><sub>VINH</sub> (2)                          | VINL                                                                                                                                                                                                                                                                                          | _        | AVdd                              | V     | This voltage reflects S&H<br>Channels 0, 1, 2 and 3<br>(CH0-CH3), positive input |  |

| AD13               | VINL   | Input Voltage Range<br><sub>VINL</sub> (2)                          | AVss                                                                                                                                                                                                                                                                                          | —        | AVss + 1V                         | V     | This voltage reflects S&H<br>Channels 0, 1, 2 and 3<br>(CH0-CH3), negative input |  |

| AD17               | Rin    | Recommended<br>Impedance of Analog<br>Voltage Source <sup>(3)</sup> | —                                                                                                                                                                                                                                                                                             |          | 200                               | Ω     |                                                                                  |  |

### TABLE 26-47: ADC MODULE SPECIFICATIONS

**Note 1:** These parameters are not characterized or tested in manufacturing.

2: These parameters are characterized, but are not tested in manufacturing.

3: These parameters are assured by design, but are not characterized or tested in manufacturing.

4: This pin may not be available on all devices; in which case, this pin will be connected to VDD internally. See the "**Pin Diagrams**" section for availability.

5: This pin may not be available on all devices; in which case, this pin will be connected to Vss internally. See the "**Pin Diagrams**" section for availability.

**6:** Overall functional device operation at VBOR < VDD < VDDMIN is ensured but not characterized. All device analog modules, such as the ADC, etc., will function but with degraded performance below VDDMIN.

#### TABLE 26-50: COMPARATOR TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}\mbox{C} \leq \mbox{TA} \leq +85^{\circ}\mbox{C for Industrial} \\ & -40^{\circ}\mbox{C} \leq \mbox{TA} \leq +125^{\circ}\mbox{C for Extended} \end{array}$ |     |       |            |  |

|--------------------|--------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic                                        | Min. Typ Max.                                                                                                                                                                                                                                                                                                     |     | Units | Conditions |  |

| 300                | TRESP  | Response Time <sup>(1,2)</sup>                        | _                                                                                                                                                                                                                                                                                                                 | 150 | 400   | ns         |  |

| 301                | TMC20V | Comparator Mode Change to Output Valid <sup>(1)</sup> | —                                                                                                                                                                                                                                                                                                                 |     | 10    | μS         |  |

| 302                | Ton2ov | Comparator Enabled to<br>Output Valid <sup>(1)</sup>  | —                                                                                                                                                                                                                                                                                                                 |     | 10    | μs         |  |

Note 1: Parameters are characterized but not tested.

2: Response time is measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

### TABLE 26-51: COMPARATOR MODULE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |             |       |            |  |

|--------------------|--------|--------------------------------------------|-------------------------------------------------------|------|-------------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic                             | Min.                                                  | Тур  | Max.        | Units | Conditions |  |