Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

>< ⊢

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 16 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 13                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

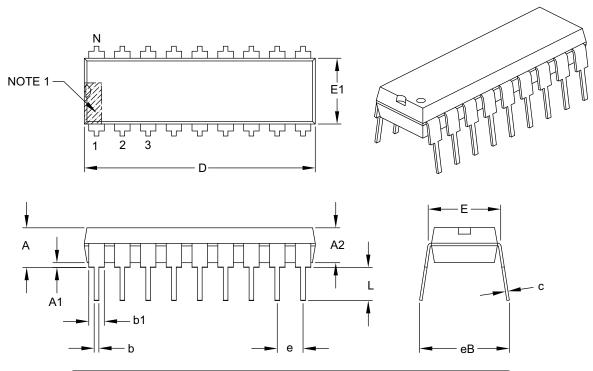

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 18-PDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp101-e-p |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

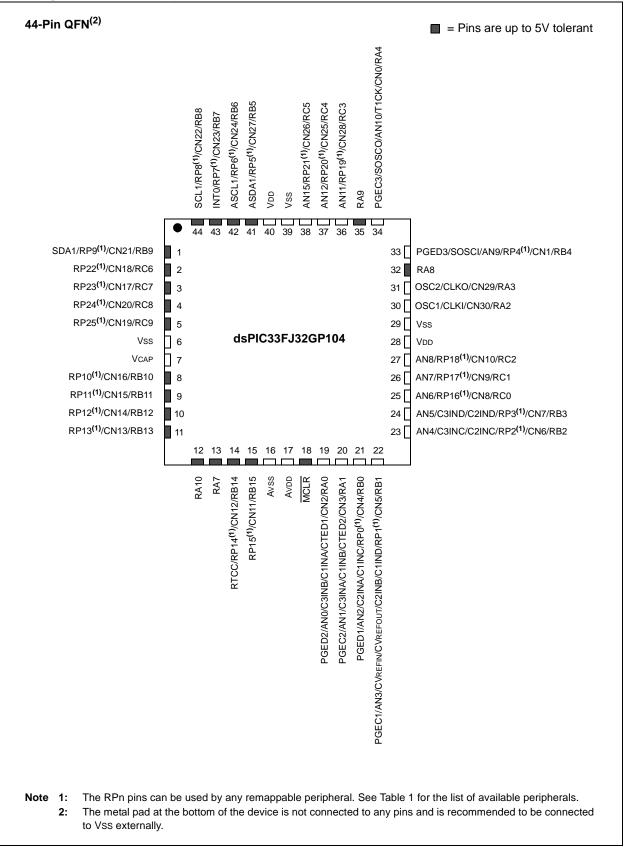

# Pin Diagrams (Continued)

## TABLE 4-33: PORTB REGISTER MAP FOR dsPIC33FJ32GP101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|---------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        | TRISB< | :15:14> | —      |        |        | —      | -     | TRISB<9:7 | >     |       | —     | TRISB4 |       |       | TRISE | 3<1:0> | C393          |

| PORTB     | 02CA        | RB<1   | 5:14>   | _      | _      | _      | —      |       | RB<9:7>   |       | _     | _     | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        | LATB<  | 15:14>  | _      | _      | _      | —      |       | LATB<9:7> | >     | _     | _     | LATB4  | _     | _     | LATB  | <1:0>  | xxxx          |

| ODCB      | 02CE        | ODCB<  | :15:14> | _      | _      |        | _      | (     | ODCB<9:7  | >     | -     | _     | _      |       |       | -     |        | 0000          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-34: PORTB REGISTER MAP FOR dsPIC33FJ32MC101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|--------|---------|--------|--------|--------|-------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        |        | TRISB< | <15:12> |        | —      | _      | -     | TRISB<9:7 | >     | _     | —     | TRISB4 | _     | _     | TRISE | 3<1:0> | F393          |

| PORTB     | 02CA        |        | RB<1   | 5:12>   |        | _      | _      |       | RB<9:7>   |       | _     | —     | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        |        | LATB<  | 15:12>  |        | _      | _      |       | LATB<9:7> | •     | _     | —     | LATB4  | _     | _     | LATB  | <1:0>  | xxxx          |

| ODCB      | 02CE        |        | ODCB<  | <15:12> |        | _      | _      | (     | ODCB<9:7: | >     | _     | —     | _      | _     | _     | —     | _      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-35: PORTB REGISTER MAP FOR dsPIC33FJ32(GP/MC)102 AND dsPIC33FJ32(GP/MC)104 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|-----------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB        | 02C8        |        |        |        |        |        |           |       | TRISB< | :15:0> |       |       |       |       |       |       |       | FFFF          |

| PORTB        | 02CA        |        |        |        |        |        |           |       | RB<1   | 5:0>   |       |       |       |       |       |       |       | xxxx          |

| LATB         | 02CC        |        |        |        |        |        |           |       | LATB<  | 15:0>  |       |       |       |       |       |       |       | xxxx          |

| ODCB         | 02CE        |        |        |        |        | 0      | DCB<15:5> |       |        |        |       |       | -     | _     | _     | _     | —     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-36: PORTC REGISTER MAP FOR dsPIC33FJ32(GP/MC)104 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|-------|-------|-------|-------|---------------|

| TRISC        | 02D0        | —      | _      | _      | —      | _      | —      |       |       |        |       | TRISC | C<9:0> |       |       |       |       | FFFF          |

| PORTC        | 02D2        |        | _      | _      | —      | _      | _      |       |       |        |       | RC<   | :9:0>  |       |       |       |       | xxxx          |

| LATC         | 02D4        |        | _      | _      | —      | _      | _      |       |       |        |       | LATC  | <9:0>  |       |       |       |       | xxxx          |

| ODCC         | 02D6        | _      | _      | _      | —      | _      | —      |       | ODC   | C<9:6> |       |       | —      | _     | _     | —     |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER 5            | 5-1: NVMCO                      | N: FLASH I               | MEMORY C                    | ONTROL RE             | GISTER                |                       |                       |

|-----------------------|---------------------------------|--------------------------|-----------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>            | R/W-0 <sup>(1)</sup>     | U-0                         | U-0                   | U-0                   | U-0                   | U-0                   |

| WR                    | WREN                            | WRERR                    |                             |                       | —                     |                       | _                     |

| bit 15                |                                 |                          |                             |                       |                       |                       | bit 8                 |

|                       |                                 |                          |                             | (4)                   | (4)                   | (4)                   | (4)                   |

| U-0                   | R/W-0 <sup>(1)</sup>            | U-0                      | U-0                         | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  |

|                       | ERASE                           | —                        | —                           | NVMOP3 <sup>(2)</sup> | NVMOP2 <sup>(2)</sup> | NVMOP1 <sup>(2)</sup> | NVMOP0 <sup>(2)</sup> |

| bit 7                 |                                 |                          |                             |                       |                       |                       | bit 0                 |

| Legend:               |                                 | SO = Settat              | ale Only hit                |                       |                       |                       |                       |

| R = Readable          | hit.                            |                          |                             |                       | mantad hit raad       |                       |                       |

|                       |                                 | W = Writabl              |                             | -                     | nented bit, read      |                       |                       |

| -n = Value at I       | POR                             | '1' = Bit is s           | et                          | '0' = Bit is cle      | ared                  | x = Bit is unkr       | IOWN                  |

| bit 15                | WR: Write Con                   | trol bit <sup>(1)</sup>  |                             |                       |                       |                       |                       |

| 5                     |                                 |                          | v program or                | r erase operati       | on; the operatic      | on is self-timed      | and the bit is        |

|                       |                                 | hardware on              |                             | •                     |                       |                       |                       |

|                       | 0 = Program o                   |                          |                             |                       | e                     |                       |                       |

| bit 14                | WREN: Write E                   | nable bit <sup>(1)</sup> |                             |                       |                       |                       |                       |

|                       | 1 = Enables Fl                  |                          | erase operati               | ions                  |                       |                       |                       |

|                       | 0 = Inhibits Fla                |                          |                             |                       |                       |                       |                       |

| bit 13                | WRERR: Write                    | Sequence Er              | ror Flag bit <sup>(1)</sup> | )                     |                       |                       |                       |

|                       |                                 |                          | •                           |                       | rmination has oc      | curred (bit is se     | t automaticallv       |

|                       |                                 | attempt of the           |                             |                       |                       | (                     |                       |

|                       | 0 = The progra                  |                          |                             | pleted normally       | /                     |                       |                       |

| bit 12-7              | Unimplemente                    | ed: Read as 'o           | )'                          |                       |                       |                       |                       |

| bit 6                 | ERASE: Erase                    | /Program Ena             | ble bit <sup>(1)</sup>      |                       |                       |                       |                       |

|                       |                                 |                          |                             |                       | 3:0> on the nex       |                       |                       |

|                       |                                 |                          | -                           | Cified by NVINC       | P<3:0> on the         | next WR comm          | land                  |

| bit 5-4               | Unimplemente                    |                          |                             | (1.0)                 |                       |                       |                       |

| bit 3-0               | NVMOP<3:0>:                     | NVM Operati              | on Selection                | bits <sup>(1,2)</sup> |                       |                       |                       |

|                       | If ERASE = 1:                   | _                        |                             |                       |                       |                       |                       |

|                       | 1111 = No ope                   |                          | 4                           |                       |                       |                       |                       |

|                       | 1101 = Erase (<br>1100 = No ope | •                        | ient                        |                       |                       |                       |                       |

|                       | 0011 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 0010 = Memor                    |                          | operation                   |                       |                       |                       |                       |

|                       | 0001 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 0000 = No ope                   | ration                   |                             |                       |                       |                       |                       |

|                       | If ERASE = 0:                   |                          |                             |                       |                       |                       |                       |

|                       | 1111 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 1101 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 1100 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 0011 = Memor<br>0010 = No ope   |                          | in operation                |                       |                       |                       |                       |

|                       | 0001 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 0000 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | -                               |                          |                             |                       |                       |                       |                       |

|                       | ese bits can only               |                          |                             |                       |                       |                       |                       |

|                       | other combination               |                          |                             | implemented.          | ECISTED               |                       |                       |

| REGISTER 5            | -2. IN VIVINE                   |                          |                             |                       | LOISIEK               |                       |                       |

# REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| U-0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| —   | —   |     |     | —   |     |     | _   |

© 2011-2014 Microchip Technology Inc.

# 8.3 Clock Switching Operation

Applications are free to switch among any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects of this flexibility, dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices have a safeguard lock built into the switch process.

| Note: | Primary Oscillator mode has three different |

|-------|---------------------------------------------|

|       | submodes (MS, HS and EC), which are         |

|       | determined by the POSCMD<1:0> Config-       |

|       | uration bits. While an application can      |

|       | switch to and from Primary Oscillator       |

|       | mode in software, it cannot switch among    |

|       | the different primary submodes without      |

|       | reprogramming the device.                   |

# 8.3.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 23.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

# 8.3.2 OSCILLATOR SWITCHING SEQUENCE

Performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit (OSCCON<0>) to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- The clock switching hardware compares the COSCx status bits with the new value of the NOSCx control bits. If they are the same, the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- 2. If a valid clock switch has been initiated, the LOCK and CF (OSCCON<5,3>) status bits are cleared.

- 3. The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bit values are transferred to the COSCx status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM is enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to "Oscillator (Part VI)" (DS70644) in the "dsPIC33/PIC24 Family Reference Manual" for details.

# 8.4 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then, the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a Warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

# 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70196) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. Devices can manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

# 9.1 Clock Frequency and Clock Switching

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC<2:0> bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration**".

# 9.2 Instruction-Based Power-Saving Modes

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices have two special powersaving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

# 9.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device will wake-up from Sleep mode on any of the these events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

## EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE; Put the device into SLEEP modePWRSAV #IDLE\_MODE; Put the device into IDLE mode

#### **PMD Control Registers** 9.5

| R/W-0       U-0       R/W-0       U-0       R/W-0       U-0       R/W-0         I2C1MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0               | R/W-0               | R/W-0            | R/W-0                  | R/W-0          | U-0            | R/W-0     | U-0                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|------------------|------------------------|----------------|----------------|-----------|----------------------|

| R/W-0       U-0       R/W-0       U-0       R/W-0       U-0       R/W-0         I2C1MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | T5MD <sup>(1)</sup> | T4MD <sup>(1)</sup> | T3MD             | T2MD                   | T1MD           | _              | PWM1MD    | _                    |

| I2C1MD       -       U1MD       -       SPI1MD       -       AD1MDf2         bit 7       bit       -       bit       bit       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       nn = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is disabled       0 = Timer7 module is disabled         bit 14       T4MD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer7 module is disabled       0 = Timer7 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is enabled         bit 14       T4MD: Timer2 Module Disable bit       1 = Timer2 module is enabled       0 = Timer7 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled         bit 11       Timer1 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15              | •                   |                  | 1                      |                |                |           | bit                  |

| I2C1MD       -       U1MD       -       SPI1MD       -       AD1MDf2         bit 7       bit       -       bit       bit       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       nn = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is disabled       0 = Timer7 module is disabled         bit 14       T4MD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer7 module is disabled       0 = Timer7 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is enabled         bit 14       T4MD: Timer2 Module Disable bit       1 = Timer2 module is enabled       0 = Timer7 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled         bit 11       Timer1 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                     |                  |                        |                |                |           |                      |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 T5MD: Timer5 Module Disable bit <sup>(1)</sup><br>1 = Timer5 module is enabled<br>0 = Timer5 module is enabled<br>0 = Timer4 module is enabled<br>0 = Timer4 module is disabled<br>0 = Timer3 module is enabled<br>0 = Timer3 module is enabled<br>0 = Timer4 module Disable bit<br>1 = Timer2 Module Disable bit<br>1 = Timer2 Module Disable bit<br>1 = Timer2 module is disabled<br>0 = Timer4 module is enabled<br>0 = Timer7 module is enabled<br>0 = Timer7 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer1 module is disabled<br>0 = UART1 modul | R/W-0               | U-0                 | R/W-0            | U-0                    | R/W-0          | U-0            | U-0       | R/W-0                |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>in = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 T5MD: Timer5 Module Disable bit <sup>(1)</sup><br>1 = Timer5 module is disabled<br>0 = Timer5 module is disabled<br>0 = Timer4 module is disabled<br>0 = Timer4 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is enabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is enabled<br>0 = Timer2 module is enabled<br>0 = Timer1 module is disabled<br>0 = Timer1 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is enabled<br>0 = Timer4 module is disabled<br>0 = UXM11 module is disabled<br>0 = UXM11 module is disabled<br>0 = UART1 module is disabled<br>0 = UART4 module i | I2C1MD              |                     | U1MD             |                        | SPI1MD         | _              | —         | AD1MD <sup>(2)</sup> |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         Dit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is enabled         0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 14       T4MD: Timer6 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is disabled         Dit 12       T2MD: Timer1 Module Disable bit       1 = Timer2 module is disabled       0 = Timer2 module is disabled         Dit 11       T1MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer4 module is disabled         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 11       T1MD: PWM1 Module Disable bit       1 = PWM1 module is disabled       0 = PWM1 module is disabled       0         Dit 10       Unimplemented: Read as '0'       0       0       0       0       0         Dit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 7               |                     |                  |                        |                |                |           | bit                  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         Dit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is enabled         0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 14       T4MD: Timer6 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is disabled         Dit 12       T2MD: Timer1 Module Disable bit       1 = Timer2 module is disabled       0 = Timer2 module is disabled         Dit 11       T1MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer4 module is disabled         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 11       T1MD: PWM1 Module Disable bit       1 = PWM1 module is disabled       0 = PWM1 module is disabled       0         Dit 10       Unimplemented: Read as '0'       0       0       0       0       0         Dit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Legend:             |                     |                  |                        |                |                |           |                      |

| m = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer5 module is disabled         bit 14       TAMD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer4 module is disabled       0 = Timer4 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer3 module is disabled       0 = Timer3 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer3 module is disabled       0 = Timer3 module is disabled         bit 12       T2MD: Timer2 Module Disable bit       1 = Timer3 module is disabled       0 = Timer3 module is disabled         bit 12       T2MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 11       T1MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 10       Unimplemented: Read as '0'       0       0       0         bit 8       Unimplemented: Read as '0'       0       1 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 7       I2C1MD: I2C1 Module Disable bit       1 = I2C1 module is disabled       0 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 6       Unimplemented: Read as '0'       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                   | le bit              | W = Writable     | bit                    | U = Unimplem   | ented bit, rea | ad as '0' |                      |

| bit 15       T5MD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled         0 = Timer5 module is disabled         1 = Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer4 module is disabled         0 = Timer4 module is disabled         0 = Timer4 module is disabled         0 = Timer3 module is disabled         0 = Timer3 module is disabled         0 = Timer3 module is enabled         0 = Timer3 module is disabled         0 = Timer1 module Disable bit         1 = Timer1 module is disabled         0 = WM1MD: PVM1 Module Disable bit         1 = PWM1 module is disabled         0 = PVWM1 module is disabled         0 = PVW1 module is disabled         0 = VIM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -n = Value a        | t POR               | '1' = Bit is set | t                      | •              |                |           | nown                 |

| 1 = Timer5 module is disabled         0 = Timer5 module is enabled         0 = Timer4 Module Disable bit         1 = Timer4 module is enabled         0 = Timer4 module is enabled         0 = Timer3 module is enabled         0 = Timer3 module is disable bit         1 = Timer3 module is disabled         0 = Timer2 module is enabled         0 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 module is disabled         0 = PWM1 MD: PWM1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is enabled         0 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module Disable bit         1 = UART1 module is disabled         0 = UART1 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                     |                  |                        |                |                |           |                      |

| 0 = Timer5 module is enabled         bit 14       T4MD: Timer4 Module Disable bit         1 = Timer4 module is disabled         0 = Timer3 Module Disable bit         1 = Timer3 module is enabled         0 = Timer4 module is disabled         0 = Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer2 module is enabled         0 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWM1 module is disabled         0 = I2C1 Module Disable bit         1 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 15              | T5MD: Time          | r5 Module Disa   | ble bit <sup>(1)</sup> |                |                |           |                      |

| bit 14       T4MD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer4 module is disabled         0 = Timer4 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 module is disabled         0 = PWM1 module is disabled         0 = I2C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is disabled         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     | 1 = Timer5 n        | nodule is disabl | ed                     |                |                |           |                      |

| 1 = Timer4 module is disabled         0 = Timer4 module is enabled         0 = Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer3 module is enabled         0 = Timer3 module is enabled         0 = Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer2 module is enabled         0 = Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWM1 module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module Disable bit         1 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled         0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     | 0 <b>= Timer5 n</b> | nodule is enable | ed                     |                |                |           |                      |

| 0 = Timer4 module is enabled         bit 13       T3MD: Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is enabled         0 = Timer3 module is enabled         0 = Timer2 module is enabled         0 = Timer2 module is enabled         0 = Timer1 module is disabled         0 = PWM1MD: PVW1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PUM1 module is disabled         0 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled         0 = UART1 module is enabled         0 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14              |                     |                  |                        |                |                |           |                      |

| bit 13       T3MD: Timer3 Module Disable bit         1 = Timer3 module is disabled       0 = Timer3 module is enabled         0 = Timer3 module is enabled       0 = Timer2 Module Disable bit         1 = Timer2 module is disabled       0 = Timer2 module is enabled         0 = Timer2 module is disabled       0 = Timer2 module is disabled         0 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is disabled       0 = PWM1 MD: PWM1 Module Disable bit         1 = PWM1 module is disabled       0 = PWM1 module is disabled         0 = PWM1 module is disabled       0 = PWM1 module is enabled         0 = PWM1 module is disabled       0 = PUM1 module is disabled         0 = PWM1 module is disabled       0 = I2C1 module is disabled         0 = I2C1 module is disabled       0 = I2C1 module is enabled         0 = I2C1 module is disabled       0 = I2C1 module is disabled         0 = UART1 module is disabled       0 = UART1 module is disabled         0 = UART1 module is disabled       0 = UART1 module is disabled         0 = UART1 module is disabled       0 = UART1 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                     |                  |                        |                |                |           |                      |

| 1 = Timer3 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is enabled         bit 11       T1MD: Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = Timer1 module is disabled         0 = Timer1 module is enabled         0 = Timer1 module is disabled         0 = Timer1 module is enabled         0 = Timer1 module is enabled         0 = Timer1 module is disabled         0 = Timer1 module is enabled         0 = Timer1 module is disabled         0 = PWM1MD: PWM1 Module Disable bit         1 = PVWM1 module is enabled         0 = PWM1 module is enabled         0 = PWM1 module is enabled         0 = VATI module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled         0 = UART1 module is enabled         0 = UART1 modu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | h:: 40              |                     |                  |                        |                |                |           |                      |

| 0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is enabled         bit 11       T1MD: Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWM1 MD: PWM1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module is disabled         0 = I2C1 module Disable bit         1 = UART1 Module Disable bit         1 = UART1 module is disabled         0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DIT 13              |                     |                  |                        |                |                |           |                      |

| bit 12 <b>T2MD</b> : Timer2 Module Disable bit         1 = Timer2 module is disabled       0 = Timer2 module is enabled         bit 11 <b>T1MD</b> : Timer1 Module Disable bit         1 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is enabled       0 = Timer1 module is disabled         0 = Timer1 module is enabled       0 = Timer1 module is enabled         bit 10 <b>Unimplemented:</b> Read as '0'         bit 3 <b>PWM1MD</b> : PWM1 Module Disable bit         1 = PWM1 module is enabled       0 = PWM1 module is enabled         bit 4 <b>Unimplemented:</b> Read as '0'         bit 5 <b>Unimplemented:</b> Read as '0'         bit 6 <b>Unimplemented:</b> Read as '0'         bit 7 <b>I2C1MD</b> : I2C1 Module Disable bit         1 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 6 <b>Unimplemented:</b> Read as '0'         bit 5 <b>U1MD</b> : UART1 Module Disable bit         1 = UART1 module is disabled       0 = UART1 module is enabled         bit 4 <b>Unimplemented:</b> Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |                     |                  |                        |                |                |           |                      |

| 1 = Timer2 module is disabled         0 = Timer2 module is enabled         bit 11       T1MD: Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = Timer1 module is enabled         bit 10       Unimplemented: Read as '0'         bit 9       PWM1MD: PWM1 Module Disable bit         1 = PWM1 module is disabled       0 = PWM1 module is disabled         0 = PWM1 module is disabled       0 = PWM1 module is enabled         bit 8       Unimplemented: Read as '0'         bit 7       I2C1 Module Disable bit         1 = I2C1 module is disabled       0 = I2C1 module is disabled         0 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 6       Unimplemented: Read as '0'         bit 5       U1MD: UART1 Module Disable bit         1 = UART1 module is disabled       0 = UART1 module is enabled         0 = UART1 module is enabled       0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 12              | T2MD: Time          | r2 Module Disa   | ble bit                |                |                |           |                      |

| bit 11 <b>T1MD:</b> Timer1 Module Disable bit<br>$1 = Timer1$ module is disabled<br>$0 = Timer1$ module is enabledbit 10 <b>Unimplemented:</b> Read as '0'bit 9 <b>PWM1MD:</b> PWM1 Module Disable bit<br>$1 = PWM1$ module is disabled<br>$0 = PWM1$ module is enabledbit 8 <b>Unimplemented:</b> Read as '0'bit 7 <b>I2C1MD:</b> I2C1 Module Disable bit<br>$1 = I2C1$ module is disabled<br>$0 = I2C1$ module is enabledbit 6 <b>Unimplemented:</b> Read as '0'bit 5 <b>U1MD:</b> UART1 Module Disable bit<br>$1 = UART1$ module is disabled<br>$0 = UART1$ module is disabled<br>bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | 1 = Timer2 n        | nodule is disabl | ed                     |                |                |           |                      |

| 1 = Timer1 module is disabled         0 = Timer1 module is enabled         0 = Timer1 module is enabled         0 = Timer1 module is enabled         0 = PWM1MD: PWM1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is enabled         0 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = UART1 Module Disable bit         1 = UART1 module is disabled         0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     | 0 = Timer2 n        | nodule is enable | ed                     |                |                |           |                      |

| 0 = Timer1 module is enabled         bit 10       Unimplemented: Read as '0'         bit 9       PWM1MD: PWM1 Module Disable bit         1 = PWM1 module is disabled       0 = PWM1 module is disabled         0 = PWM1 module is enabled       0 = PWM1 module is enabled         bit 8       Unimplemented: Read as '0'         bit 7       I2C1MD: I2C1 Module Disable bit         1 = I2C1 module is disabled       0 = I2C1 module is enabled         0 = I2C1 module is enabled       0 = I2C1 module is enabled         bit 6       Unimplemented: Read as '0'         bit 5       U1MD: UART1 Module Disable bit         1 = UART1 module is disabled       0 = UART1 module is enabled         bit 4       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 11              | T1MD: Time          | r1 Module Disa   | ble bit                |                |                |           |                      |