Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 13                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 18-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp101-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

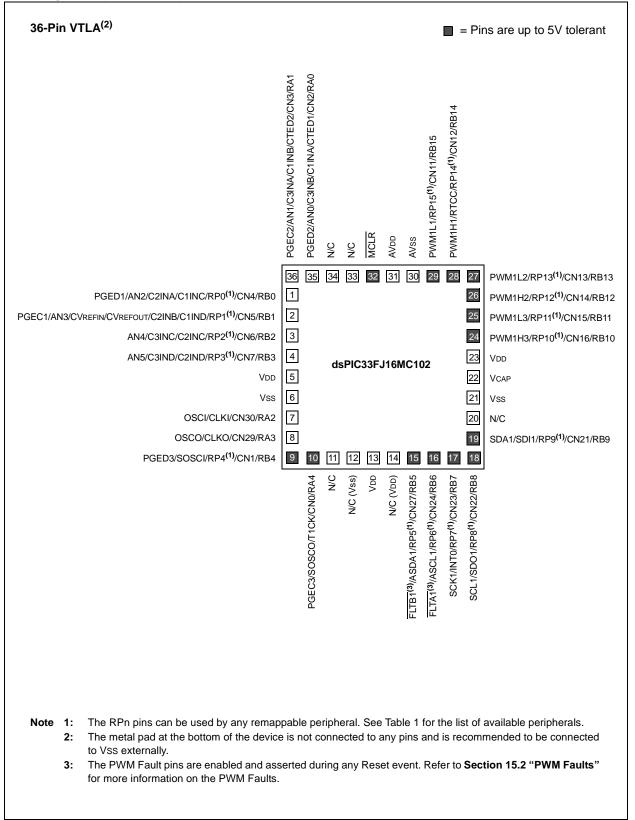

# Pin Diagrams (Continued)

# Referenced Sources

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the primary reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33FJ16MC102 product page of the Microchip Web site (www.microchip.com). In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "CPU" (DS70204)

- "Data Memory" (DS70202)

- "Program Memory" (DS70203)

- "Flash Programming" (DS70191)

- "Reset" (DS70192)

- "Watchdog Timer and Power-Saving Modes" (DS70196)

- "Timers" (DS70205)

- "Input Capture" (DS70198)

- "Output Compare" (DS70209)

- "Motor Control PWM" (DS70187)

- "Analog-to-Digital Converter (ADC)" (DS70183)

- "UART" (DS70188)

- "Serial Peripheral Interface (SPI)" (DS70206)

- "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- "CodeGuard Security" (DS70199)

- "Programming and Diagnostics" (DS70207)

- "Device Configuration" (DS70194)

- "I/O Ports with Peripheral Pin Select (PPS)" (DS70190)

- "Real-Time Clock and Calendar (RTCC)" (DS70301)

- "Introduction (Part VI)" (DS70655)

- "Oscillator (Part VI)" (DS70644)

- "Interrupts (Part VI)" (DS70633)

- "Comparator with Blanking" (DS70647)

- "Charge Time Measurement Unit (CTMU)" (DS70635)

NOTES:

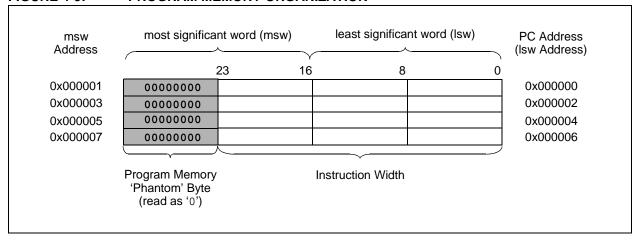

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-3).

Program memory addresses are always word-aligned on the lower word and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

# 4.1.2 INTERRUPT AND TRAP VECTORS

All of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices also have two Interrupt Vector Tables (IVTs), located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the Interrupt Vector Tables is provided in **Section 7.1 "Interrupt Vector Table"**.

#### FIGURE 4-3: PROGRAM MEMORY ORGANIZATION

# TABLE 4-12: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|------------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       | _      |         | _      |        |        | _      | _     |       |       |            | I2C1 Recei   | ve Register  |       |       |       | 0000          |

| I2C1TRN  | 0202        | _       | _      | _       | —      | _      | _      | _      | _     |       |       |            | I2C1 Trans   | mit Register | •     |       |       | 00FF          |

| I2C1BRG  | 0204        | _       | _      | _       | —      | _      | _      | _      |       |       |       | Baud Ra    | te Generato  | r Register   |       |       |       | 0000          |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT      | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D_A        | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       |        | _       | _      | _      | _      |        |       |       |       | I2C1 Addre | ess Register |              |       |       |       | 0000          |

| I2C1MSK  | 020C        | —       | _      | _       | _      | _      |        |        |       |       | 120   | C1 Address | Mask Regis   | ter          |       |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-13: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6    | Bit 5 | Bit 4      | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|-------------------------------|----------|--------|--------|--------|-------|-------|----------|----------|-------|------------|---------|--------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | _                             | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD | URXINV     | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _                             | -        | _      | _      | _      |       |       |          |          | UART1 | Transmit R | egister |        |        |       | xxxx          |

| U1RXREG  | 0226        | _        | _                             | -        | _      | _      | _      |       |       |          |          | UART  | Receive R  | egister |        |        |       | 0000          |

| U1BRG    | 0228        |          | Baud Rate Generator Prescaler |          |        |        |        |       |       | 0000     |          |       |            |         |        |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: SPI1 REGISTER MAP

|          |             | •••••• |        |         |        |        |        |            |            |              | -        |       |       |       |       | -      |        |               |

|----------|-------------|--------|--------|---------|--------|--------|--------|------------|------------|--------------|----------|-------|-------|-------|-------|--------|--------|---------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8      | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

| SPI1STAT | 0240        | SPIEN  | _      | SPISIDL | _      | _      | _      |            |            |              | SPIROV   | _     | _     | _     |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242        | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE        | SSEN         | CKP      | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000          |

| SPI1CON2 | 0244        | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _      | _          | _          | _            | _        | _     |       | -     | _     | FRMDLY | _      | 0000          |

| SPI1BUF  | 0248        |        |        |         |        |        |        | SPI1 Trans | mit and Re | ceive Buffer | Register |       |       |       |       |        |        | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

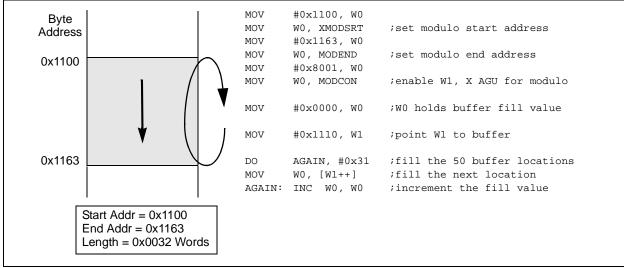

# 4.4 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the circular buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

### 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear). The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

# 4.4.2 W ADDRESS REGISTER SELECTION

- The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select which registers will operate with Modulo Addressing.

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled.

- If YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

# FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

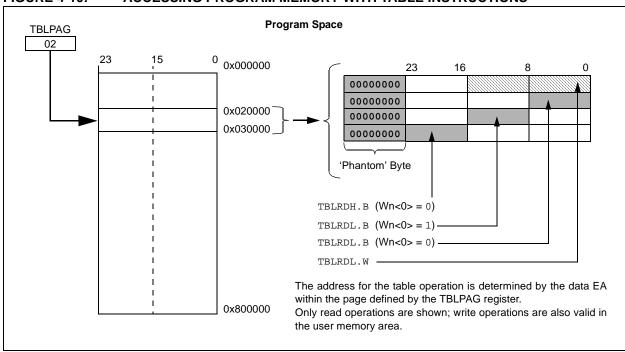

### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

#### FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| REGISTER     | (8-3: 050  | IUN: FRC 05                                              | GILLATOR    | IUNING REG       | ISIEK            |                 |       |  |

|--------------|------------|----------------------------------------------------------|-------------|------------------|------------------|-----------------|-------|--|

| U-0          | U-0        | U-0                                                      | U-0         | U-0              | U-0              | U-0             | U-0   |  |

| _            | _          | —                                                        | _           | _                | —                | —               | _     |  |

| bit 15       | ·          |                                                          |             |                  |                  | ·               | bit   |  |

|              |            |                                                          |             |                  |                  |                 |       |  |

| U-0          | U-0        | R/W-0                                                    | R/W-0       | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |

| _            | — TUN<5:0> |                                                          |             |                  |                  |                 |       |  |

| bit 7        |            |                                                          |             |                  |                  |                 | bit ( |  |

|              |            |                                                          |             |                  |                  |                 |       |  |

| Legend:      |            |                                                          |             |                  |                  |                 |       |  |

| R = Readab   | ole bit    | W = Writable                                             | bit         | U = Unimpler     | mented bit, read | d as '0'        |       |  |

| -n = Value a | at POR     | '1' = Bit is set                                         |             | '0' = Bit is cle | ared             | x = Bit is unkı | nown  |  |

|              |            |                                                          |             |                  |                  |                 |       |  |

| bit 15-6     | Unimpleme  | ented: Read as '                                         | 0'          |                  |                  |                 |       |  |

| bit 5-0      | TUN<5:0>:  | FRC Oscillator T                                         | uning bits  |                  |                  |                 |       |  |

|              |            | Aaximum frequer<br>Center frequency                      |             |                  | 77 MHz)          |                 |       |  |

|              | •          |                                                          |             |                  |                  |                 |       |  |

|              | •          |                                                          |             |                  |                  |                 |       |  |

|              | •          |                                                          |             |                  |                  |                 |       |  |

|              | 000000 = 0 | Center frequency<br>Center frequency<br>Center frequency | (7.37 MHz n | ominal)          |                  |                 |       |  |

|              | •          |                                                          |             |                  |                  |                 |       |  |

# REGISTER 8-3: OSCTUN: FRC OSCILLATOR TUNING REGISTER

• 100001 = Center frequency – 1.453% (7.263 MHz) 100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

•

# 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70196) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. Devices can manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

# 9.1 Clock Frequency and Clock Switching

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC<2:0> bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration**".

# 9.2 Instruction-Based Power-Saving Modes

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices have two special powersaving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

# 9.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device will wake-up from Sleep mode on any of the these events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE; Put the device into SLEEP modePWRSAV #IDLE\_MODE; Put the device into IDLE mode

### 10.4.2.2 Output Mapping

In contrast to the inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 5-bit fields, with each set associated with one RPn pin (see Register 10-11 through Register 10-23). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-2 and Figure 10-3).

The list of peripherals for output mapping also includes a null value of '00000' because of the mapping technique. This permits any given pin to remain unconnected from the output of any of the pin selectable peripherals.

#### **FIGURE 10-3:** MULTIPLEXING OF **REMAPPABLE OUTPUT** FOR RPn RPnR<4:0> Default 0 U1TX Output Enable 3 U1RTS Output Enable 4 Output Enable • • • OC2 Output Enable 19

Default

U1TX Output

OC2 Output

U1RTS Output

0

3

4

•

•

19

Output Data

$\mathbf{X}$

RPn

# TABLE 10-2: OUTPUT SELECTION FOR REMAPPABLE PIN (RPn)

| ••••••••  |                                                                                                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RPnR<4:0> | Output Name                                                                                                                                                         |

| 00000     | RPn tied to Default Port Pin                                                                                                                                        |

| 00001     | RPn tied to Comparator 1 Output                                                                                                                                     |

| 00010     | RPn tied to Comparator 2 Output                                                                                                                                     |

| 00011     | RPn tied to UART1 Transmit                                                                                                                                          |

| 00100     | RPn tied to UART1 Ready-to-Send                                                                                                                                     |

| 01000     | RPn tied to SPI Clock <sup>(1)</sup>                                                                                                                                |

| 00111     | RPn tied to SPI Data Output <sup>(1)</sup>                                                                                                                          |

| 01001     | RPn tied to SPI1 Slave Select Output <sup>(1)</sup>                                                                                                                 |

| 10010     | RPn tied to Output Compare 1                                                                                                                                        |

| 10011     | RPn tied to Output Compare 2                                                                                                                                        |

| 11101     | RPn tied to CTMU Pulse Output                                                                                                                                       |

| 11110     | RPn tied to Comparator 3 Output                                                                                                                                     |

|           | RPnR<4:0>         00000         00001         00010         00011         00100         01000         01001         01001         10010         10011         11011 |

**Note 1:** This function is available in dsPIC33FJ32(GP/MC)10X devices only.

| REGISTER                                                     | 10-9: RPINE                                            | 20: PERIPH                                    | ERAL PIN S                     | ELECT INPU                     | TREGISTER             | 20                      |                       |  |  |  |

|--------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------|--------------------------------|--------------------------------|-----------------------|-------------------------|-----------------------|--|--|--|

| U-0                                                          | U-0                                                    | U-0                                           | R/W-1                          | R/W-1                          | R/W-1                 | R/W-1                   | R/W-1                 |  |  |  |

| —                                                            | —                                                      | —                                             | SCK1R4 <sup>(1)</sup>          | SCK1R3 <sup>(1)</sup>          | SCK1R2 <sup>(1)</sup> | SCK1R1 <sup>(1)</sup>   | SCK1R0 <sup>(1)</sup> |  |  |  |

| bit 15                                                       |                                                        |                                               |                                |                                |                       |                         | bit 8                 |  |  |  |

|                                                              |                                                        |                                               |                                |                                |                       |                         |                       |  |  |  |

| U-0                                                          | U-0                                                    | U-0                                           | R/W-1<br>SDI1R4 <sup>(1)</sup> | R/W-1<br>SDI1R3 <sup>(1)</sup> | R/W-1                 | R/W-1                   | R/W-1                 |  |  |  |

|                                                              |                                                        |                                               | SDI1R2 <sup>(1)</sup>          | SDI1R1 <sup>(1)</sup>          | SDI1R0 <sup>(1)</sup> |                         |                       |  |  |  |

| bit 7                                                        |                                                        |                                               |                                |                                |                       |                         | bit 0                 |  |  |  |

|                                                              |                                                        |                                               |                                |                                |                       |                         |                       |  |  |  |

| Legend:                                                      | -                                                      |                                               |                                |                                |                       |                         |                       |  |  |  |

| R = Readable bit 	 W = Writable bit 	 U = Unimplemented bit, |                                                        |                                               |                                |                                |                       |                         |                       |  |  |  |

| -n = Value at                                                | t POR                                                  | '1' = Bit is set                              |                                | '0' = Bit is cle               | ared                  | x = Bit is unkr         | IOWN                  |  |  |  |

| 1 1 4 5 4 0                                                  |                                                        |                                               | o.!                            |                                |                       |                         |                       |  |  |  |

| bit 15-13                                                    | -                                                      | ted: Read as '                                |                                |                                | <b>.</b>              |                         |                       |  |  |  |

| bit 12-8                                                     |                                                        |                                               | Clock Input (S                 | CK1IN) to the                  | Corresponding         | RPn Pin bits            |                       |  |  |  |

|                                                              |                                                        | 11111 = Input tied to Vss<br>11110 = Reserved |                                |                                |                       |                         |                       |  |  |  |

|                                                              | 11110 = Res                                            | 11110 = Reserved                              |                                |                                |                       |                         |                       |  |  |  |

|                                                              |                                                        |                                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              |                                                        |                                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              | 11010 = Res                                            |                                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              | 11001 <b>= I</b> npu                                   | ut tied to RP25                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              | •                                                      |                                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              | •                                                      |                                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              | 00001 = Inpu                                           | ut tied to RP1                                |                                |                                |                       |                         |                       |  |  |  |

|                                                              | 00000 = Inpu                                           |                                               |                                |                                |                       |                         |                       |  |  |  |

| bit 7-5                                                      | Unimplemen                                             | ted: Read as '                                | 0'                             |                                |                       |                         |                       |  |  |  |

| bit 4-0                                                      | SDI1R<4:0>:                                            | Assign SPI1 E                                 | Data Input (SD                 | 11) to the Corre               | esponding RPn         | Pin bits <sup>(1)</sup> |                       |  |  |  |

|                                                              | 11111 <b>= I</b> npu                                   |                                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              | 11110 <b>= Res</b>                                     | erved                                         |                                |                                |                       |                         |                       |  |  |  |

|                                                              | •                                                      |                                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              | •                                                      |                                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              | 11010 = Res                                            | erved                                         |                                |                                |                       |                         |                       |  |  |  |

|                                                              |                                                        | ut tied to RP25                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              |                                                        |                                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              |                                                        |                                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              | 00001 – Inni                                           | it tied to RP1                                |                                |                                |                       |                         |                       |  |  |  |

|                                                              | 00001 = Input tied to RP1<br>00000 = Input tied to RP0 |                                               |                                |                                |                       |                         |                       |  |  |  |

|                                                              |                                                        | •                                             |                                |                                |                       |                         |                       |  |  |  |

# REGISTER 10-9: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

|                                    |                    |                 | _                                      |                  |                |                 |       |  |  |  |

|------------------------------------|--------------------|-----------------|----------------------------------------|------------------|----------------|-----------------|-------|--|--|--|

| U-0                                | U-0                | U-0             | U-0                                    | U-0              | U-0            | U-0             | U-0   |  |  |  |

| —                                  | —                  | —               | —                                      | —                | —              | —               | _     |  |  |  |

| bit 15                             |                    |                 |                                        |                  |                |                 | bit 8 |  |  |  |

|                                    |                    |                 |                                        |                  |                |                 |       |  |  |  |

| U-0                                | U-0                | U-0             | R/W-1                                  | R/W-1            | R/W-1          | R/W-1           | R/W-1 |  |  |  |

| _                                  |                    | —               | SS1R4                                  | SS1R3            | SS1R2          | SS1R1           | SS1R0 |  |  |  |

| bit 7                              |                    |                 |                                        |                  |                |                 | bit 0 |  |  |  |

|                                    |                    |                 |                                        |                  |                |                 |       |  |  |  |

| Legend:                            |                    |                 |                                        |                  |                |                 |       |  |  |  |

| R = Readable bit W = Writable      |                    |                 | bit U = Unimplemented bit, read as '0' |                  |                |                 |       |  |  |  |

| -n = Value at POR '1' = Bit is set |                    |                 | t                                      | '0' = Bit is cle | eared          | x = Bit is unkr | nown  |  |  |  |

|                                    |                    |                 |                                        |                  |                |                 |       |  |  |  |

| bit 15-5                           | Unimplemer         | nted: Read as ' | 0'                                     |                  |                |                 |       |  |  |  |

| bit 4-0                            | SS1R<4:0>:         | Assign SPI1 S   | lave Select In                         | put (SS1IN) to   | the Correspond | ing RPn Pin bit | S     |  |  |  |

|                                    |                    | ut tied to Vss  |                                        |                  |                |                 |       |  |  |  |

|                                    | 11110 <b>= Res</b> | served          |                                        |                  |                |                 |       |  |  |  |

|                                    | :                  |                 |                                        |                  |                |                 |       |  |  |  |

|                                    |                    |                 |                                        |                  |                |                 |       |  |  |  |

|                                    | 11010 <b>= Res</b> |                 |                                        |                  |                |                 |       |  |  |  |

|                                    | 11001 <b>= Inp</b> | ut tied to RP25 |                                        |                  |                |                 |       |  |  |  |

|                                    |                    |                 |                                        |                  |                |                 |       |  |  |  |

|                                    |                    |                 |                                        |                  |                |                 |       |  |  |  |

|                                    |                    | ut tied to RP1  |                                        |                  |                |                 |       |  |  |  |

|                                    | 00000 = Inpr       | ut tied to RP0  |                                        |                  |                |                 |       |  |  |  |

|                                    |                    |                 |                                        |                  |                |                 |       |  |  |  |

### REGISTER 10-10: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0                                | U-0   | U-0          | U-0   | U-0                                     | U-0             | R/W-0    | R/W-0 |  |  |

|------------------------------------|-------|--------------|-------|-----------------------------------------|-----------------|----------|-------|--|--|

|                                    | —     | _            |       | —                                       | —               | AMSK     | <9:8> |  |  |

| bit 15                             |       |              |       |                                         |                 |          | bit 8 |  |  |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0 | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |  |

|                                    |       |              | AMS   | K<7:0>                                  |                 |          |       |  |  |

| bit 7                              |       |              |       |                                         |                 |          | bit 0 |  |  |

|                                    |       |              |       |                                         |                 |          |       |  |  |

| Legend:                            |       |              |       |                                         |                 |          |       |  |  |

| R = Readable                       | bit   | W = Writable | bit   | U = Unimplen                            | nented bit, rea | d as '0' |       |  |  |

| -n = Value at POR '1' = Bit is set |       |              |       | '0' = Bit is cleared x = Bit is unknown |                 |          |       |  |  |

### REGISTER 17-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Mask for Address Bit x Select bits

1 = Enables masking for Bit x of incoming message address; bit match not required in this position

0 = Disables masking for Bit x; bit match required in this position

# 18.1 UART Helpful Tips

- In multi-node, direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

# 18.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en554109          |

### 18.2.1 KEY RESOURCES

- "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33/PIC24 Family Reference Manual"* sections

- Development Tools

| DC CHARACI       | TERISTICS                   |            | (unless oth | perating Condition<br>erwise stated)<br>mperature -40°C<br>-40°C |        |                             |  |  |  |  |

|------------------|-----------------------------|------------|-------------|------------------------------------------------------------------|--------|-----------------------------|--|--|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup>      | Max        | Units       | Units Conditions                                                 |        |                             |  |  |  |  |

| Operating Cur    | rent (IDD) <sup>(2)</sup> – | dsPIC33FJ1 | 6(GP/MC)10X | Devices                                                          |        |                             |  |  |  |  |

| DC20d            | 0.7                         | 1.7        | mA          | -40°C                                                            |        |                             |  |  |  |  |

| DC20a            | 0.7                         | 1.7        | mA          | +25°C                                                            | - 3.3V | LPRC                        |  |  |  |  |

| DC20b            | 1.0                         | 1.7        | mA          | +85°C                                                            | 3.3V   | (32.768 kHz) <sup>(3)</sup> |  |  |  |  |

| DC20c            | 1.3                         | 1.7        | mA          | +125°C                                                           |        |                             |  |  |  |  |

| DC21d            | 1.9                         | 2.6        | mA          | -40°C                                                            |        |                             |  |  |  |  |

| DC21a            | 1.9                         | 2.6        | mA          | +25°C                                                            | - 3.3V | 1 MIPS <sup>(3)</sup>       |  |  |  |  |

| DC21b            | 1.9                         | 2.6        | mA          | +85°C                                                            | - 3.3V | T MIPS(*)                   |  |  |  |  |

| DC21c            | 2.0                         | 2.6        | mA          | +125°C                                                           |        |                             |  |  |  |  |

| DC22d            | 6.5                         | 8.5        | mA          | -40°C                                                            |        |                             |  |  |  |  |

| DC22a            | 6.5                         | 8.5        | mA          | +25°C                                                            | - 3.3V | 4 MIPS <sup>(3)</sup>       |  |  |  |  |

| DC22b            | 6.5                         | 8.5        | mA          | +85°C                                                            | 3.3V   | 4 1011250                   |  |  |  |  |

| DC22c            | 6.5                         | 8.5        | mA          | +125°C                                                           |        |                             |  |  |  |  |

| DC23d            | 12.2                        | 16         | mA          | -40°C                                                            |        |                             |  |  |  |  |

| DC23a            | 12.2                        | 16         | mA          | +25°C                                                            | 2.21/  | 10 MIPS <sup>(3)</sup>      |  |  |  |  |

| DC23b            | 12.2                        | 16         | mA          | +85°C                                                            | - 3.3V | 10 MIPS**                   |  |  |  |  |

| DC23c            | 12.2                        | 16         | mA          | +125°C                                                           | ]      |                             |  |  |  |  |

| DC24d            | 16                          | 21         | mA          | -40°C                                                            |        |                             |  |  |  |  |

| DC24a            | 16                          | 21         | mA          | +25°C                                                            | - 3.3V | 16 MIPS                     |  |  |  |  |

| DC24b            | 16                          | 21         | mA          | +85°C                                                            | 3.3V   | 10 101173                   |  |  |  |  |

| DC24c            | 16                          | 21         | mA          | +125°C                                                           | ]      |                             |  |  |  |  |

#### TABLE 26-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

- Oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (PMDx bits are all zeroed)

- CPU executing while(1) statement

- 3: These parameters are characterized, but not tested in manufacturing.

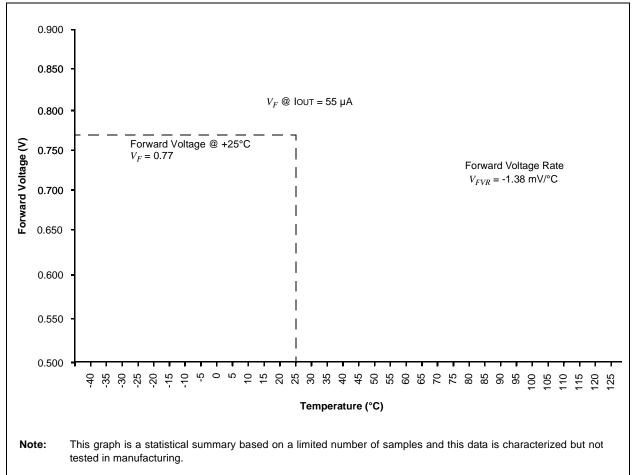

#### FIGURE 26-33: FORWARD VOLTAGE VERSUS TEMPERATURE

# TABLE A-3: MAJOR SECTION UPDATES (CONTINUED)

| Section Name             | Update Description                                                                                                       |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Section 26.0 "Electrical | Updated the Absolute Maximum Ratings.                                                                                    |

| Characteristics"         | Updated TABLE 26-3: Thermal Packaging Characteristics.                                                                   |

|                          | Updated TABLE 26-6: DC Characteristics: Operating Current (Idd).                                                         |

|                          | Updated TABLE 26-7: DC Characteristics: Idle Current (lidle).                                                            |

|                          | Updated TABLE 26-8: DC Characteristics: Power-Down Current (Ipd).                                                        |

|                          | Updated TABLE 26-9: DC Characteristics: Doze Current (Idoze).                                                            |

|                          | Updated TABLE 26-10: DC Characteristics: I/O Pin Input Specifications.                                                   |

|                          | Replaced all SPI specifications and figures (see Table 26-29 through Table 26-44 and Figure 26-11 through Figure 26-26). |

| Section 28.0 "Packaging  | Added the following Package Marking Information and Package Drawings:                                                    |

| Information"             | 44-Lead TQFP                                                                                                             |

|                          | • 44-Lead QFN                                                                                                            |

|                          | <ul> <li>44-Lead VTLA (referred to as TLA in the package drawings)</li> </ul>                                            |

| DC Characteristics                          | <br>282 |

|---------------------------------------------|---------|

| Brown-out Reset (BOR)                       |         |

| Doze Current (IDOZE)                        |         |

| High Temperature                            |         |

| I/O Pin Input Specifications                |         |

| I/O Pin Output Specifications               |         |

| Idle Current (IIDLE)                        |         |

| Operating Current (IDD)                     |         |

| Operating MIPS vs. Voltage                  |         |

| Power-Down Current (IPD)                    |         |

| Program Memory                              |         |

| Temperature and Voltage Specifications      |         |

| Thermal Operating Conditions                |         |

| Thermal Packaging                           |         |

| Development Support                         |         |

| Assembler                                   |         |

| MPASM Assembler                             | <br>278 |

| C Compilers                                 |         |

| MPLAB XC                                    | <br>278 |

| Demonstration/Development Boards            | <br>280 |

| Evaluation and Starter Kits                 |         |

| MPLAB Assembler, Linker, Librarian          |         |

| MPLAB ICD 3 In-Circuit Debugger System      | <br>279 |

| MPLAB PM3 Device Programmer                 | <br>279 |

| MPLAB REAL ICE In-Circuit Emulator System   |         |

| MPLAB X Integrated Development              |         |

| Environment Software                        | <br>277 |

| MPLINK Object Linker/MPLIB Object Librarian | <br>278 |

| PICkit 3 In-Circuit Debugger/Programmer     | <br>279 |

| Software Simulator (MPLAB X SIM)            | <br>279 |

| Third-Party Development Tools               |         |

| Doze Mode                                   | <br>134 |

| dsPIC33FJ16(GP/MC)101/102                   |         |

| Device Features                             | <br>2   |

| dsPIC33FJ32(GP/MC)101/102/104               |         |

| Device Features                             | <br>3   |

| F                                           |         |

| -                                           |         |

| Electrical Characteristics                  | <br>281 |

| 126 |

|-----|

|     |

|     |

|     |

|     |

|     |

|     |

#### F

| Flash Program Memory  |  |

|-----------------------|--|

| Control Registers     |  |

| Operations            |  |

| Programming Algorithm |  |

| RTSP Operation        |  |

| Table Instructions    |  |

|                       |  |

# G

| Getting Started with 16-Bit DSCs        | 33 |

|-----------------------------------------|----|

| Analog and Digital Pins Configuration   |    |

| During ICSP                             | 36 |

| Connection Requirements                 | 33 |

| Decoupling Capacitors                   | 33 |

| External Oscillator Pins                | 35 |

| ICSP Pins                               | 35 |

| Master Clear (MCLR) Pin                 | 34 |

| Oscillator Value Conditions on Start-up | 36 |

| Unused I/Os                             | 36 |

# Н

| High-Temperature Electrical Characteristics            |

|--------------------------------------------------------|

|                                                        |

| VO Dorto 120                                           |

| I/O Ports                                              |

| Configuring Analog Port Pins                           |

| Open-Drain Configuration                               |

| Parallel I/O (PIO)                                     |

| Write/Read Timing 141                                  |

| l <sup>2</sup> C                                       |

| Control Registers                                      |

| Operating Modes                                        |

| Registers 203                                          |

| In-Circuit Debugger268                                 |

| In-Circuit Serial Programming (ICSP)                   |

| Input Capture 175                                      |

| Control Register 176                                   |

| Input Change Notification (ICN)141                     |

| Instruction Addressing Modes73                         |

| File Register Instructions 73                          |

| Fundamental Modes Supported74                          |

| MAC Instructions74                                     |

| MCU Instructions73                                     |

| Move and Accumulator Instructions74                    |

| Other Instructions74                                   |

| Instruction Set                                        |

|                                                        |

| Summary                                                |

| Overview                                               |

| Symbols Used in Opcode Descriptions                    |

| Instruction-Based Power-Saving Modes                   |

| Idle                                                   |

| Sleep                                                  |

| Internet Address                                       |

| Interrupt Controller                                   |

| Interrupt Registers                                    |

| IECx                                                   |

| IFSx                                                   |

| INTCON1                                                |

| INTCON2                                                |

| INTTREG                                                |

| IPCx                                                   |

| Interrupt Setup Procedures                             |

| Initialization                                         |

| Interrupt Disable                                      |

| Interrupt Disable                                      |

| Trap Service Routine (TSR)                             |

|                                                        |

| Interrupt Vectors                                      |

| Reset Sequence                                         |

| Interrupt Vector Table (IVT)                           |

| Interrupts Coincident with Power Save Instructions 134 |

| L                                                      |

|                                                        |

| LPRC Oscillator                                        |

| Use with WDT267                                        |

| Μ                                                      |

|                                                        |

| Memory Organization                                    |

| Microchip Internet Web Site                            |

|                                                        |

| Momory organization          |     |

|------------------------------|-----|

| Microchip Internet Web Site  | 387 |

| Modulo Addressing            | 75  |

| Applicability                |     |

| Operation Example            |     |

| Start and End Address        | 75  |

| W Address Register Selection | 75  |

|                              |     |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2014, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-62077-845-6

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mnufacture of development systems is ISO 9001:2000 certified.

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Pforzheim Tel: 49-7231-424750

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

10/28/13