Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betails                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 13                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 18-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp101t-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# DS70000652F-page 66

#### TABLE 4-18: CTMU REGISTER MAP

| F | ile Name       | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

|---|----------------|-------------|---------|---------|----------|----------|----------|----------|----------|----------|---------|---------|----------|----------|----------|----------|-------|-------|---------------|

| C | FMUCON1        | 033A        | CTMUEN  | _       | CTMUSIDL | TGEN     | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | _       |          | -        | _        | -        | _     | _     | 0000          |

| C | FMUCON2        | 033C        | EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 |       |       | 0000          |

| C | <b>FMUICON</b> | 033E        | ITRIM5  | ITRIM4  | ITRIM3   | ITRIM2   | ITRIM1   | ITRIM0   | IRNG1    | IRNG0    | —       | —       | -        |          | _        |          |       | -     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-19: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File Name | SFR<br>Addr | Bit 15 | Bit 14                                             | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9    | Bit 8    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------------|--------|----------------------------------------------------|---------|---------|---------|--------|----------|----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ALRMVAL   | 0620        |        | Alarm Value Register Window based on ALRMPTR<1:0>  |         |         |         |        |          |          |       |       |       |       | xxxx  |       |       |       |               |

| ALCFGRPT  | 0622        | ALRMEN | CHIME                                              | AMASK3  | AMASK2  | AMASK1  | AMASK0 | ALRMPTR1 | ALRMPTR0 | ARPT7 | ARPT6 | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | 0000          |

| RTCVAL    | 0624        |        | RTCC Value Register Window based on RTCPTR<1:0> x: |         |         |         |        |          |          |       |       |       | xxxx  |       |       |       |       |               |

| RCFGCAL   | 0626        | RTCEN  | —                                                  | RTCWREN | RTCSYNC | HALFSEC | RTCOE  | RTCPTR1  | RTCPTR0  | CAL7  | CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-20: PAD CONFIGURATION REGISTER MAP

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|-----------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------|-------|---------------|

| PADCFG1   | 02FC        | _      |        |        |        | _      | _      | _     | -     | _     |       | —     |       |       | _     | RTSECSEL | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| bit 7                |                      |                      |       |       |       |       | bit 0 |

|----------------------|----------------------|----------------------|-------|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | Ν     | OV    | Z     | С     |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| bit 15               |                      |                      |       |       |       |       | bit 8 |

| OA                   | OB                   | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| R-0                  | R-0                  | R/C-0                | R/C-0 | R-0   | R/C-0 | R-0   | R/W-0 |

#### **REGISTER 7-1:** SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

#### REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R-0 | R-0 | R-0   |

|--------|-----|-----|-------|-------|-----|-----|-------|

| —      | —   | —   | US    | EDT   | DL2 | DL1 | DL0   |

| bit 15 |     |     |       |       |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-------|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | PSV   | RND   | IF    |

| bit 7 |       |       |        |                     |       |       | bit 0 |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

bit 3 **IPL3:** CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| U-0          | R/W-1                                                                 | R/W-0                   | R/W-0                   | U-0                        | R/W-1            | R/W-0           | R/W-0  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------|-------------------------|-------------------------|----------------------------|------------------|-----------------|--------|--|--|--|--|--|

| —            | FLTA1IP2 <sup>(1)</sup>                                               | FLTA1IP1 <sup>(1)</sup> | FLTA1IP0 <sup>(1)</sup> | —                          | RTCIP2           | RTCIP1          | RTCIP0 |  |  |  |  |  |

| bit 15       |                                                                       |                         |                         |                            |                  |                 | bit 8  |  |  |  |  |  |

|              |                                                                       |                         |                         |                            |                  |                 |        |  |  |  |  |  |

| U-0          | U-0                                                                   | U-0                     | U-0                     | U-0                        | U-0              | U-0             | U-0    |  |  |  |  |  |

|              |                                                                       | —                       | —                       |                            |                  |                 | —      |  |  |  |  |  |

| bit 7        |                                                                       |                         |                         |                            |                  |                 | bit C  |  |  |  |  |  |

|              |                                                                       |                         |                         |                            |                  |                 |        |  |  |  |  |  |

| Legend:      |                                                                       |                         |                         |                            |                  |                 |        |  |  |  |  |  |

| R = Readab   | le bit                                                                | W = Writable            | bit                     | U = Unimpler               | mented bit, read | d as '0'        |        |  |  |  |  |  |

| -n = Value a | t POR                                                                 | '1' = Bit is set        |                         | '0' = Bit is cle           | ared             | x = Bit is unkr | nown   |  |  |  |  |  |

|              |                                                                       |                         |                         |                            |                  |                 |        |  |  |  |  |  |

| bit 15       | Unimplemented: Read as '0'                                            |                         |                         |                            |                  |                 |        |  |  |  |  |  |

| bit 14-12    | FLTA1IP<2:0                                                           | >: PWM1 Faul            | A Interrupt Pr          | iority bits <sup>(1)</sup> |                  |                 |        |  |  |  |  |  |

|              | <pre>111 = Interrupt is Priority 7 (highest priority interrupt)</pre> |                         |                         |                            |                  |                 |        |  |  |  |  |  |

|              | •                                                                     |                         |                         |                            |                  |                 |        |  |  |  |  |  |

|              | •                                                                     |                         |                         |                            |                  |                 |        |  |  |  |  |  |

|              | 001 = Interrup                                                        |                         |                         |                            |                  |                 |        |  |  |  |  |  |

|              | 000 = Interrup                                                        | ot source is dis        | abled                   |                            |                  |                 |        |  |  |  |  |  |

| bit 11       | Unimplemen                                                            | ted: Read as '          | 0'                      |                            |                  |                 |        |  |  |  |  |  |

| bit 10-8     | RTCIP<2:0>:                                                           | RTCC Interrup           | ot Priority bits        |                            |                  |                 |        |  |  |  |  |  |

|              | 111 = Interrur                                                        | ot is Priority 7 (      | highest priority        | / interrupt)               |                  |                 |        |  |  |  |  |  |

|              |                                                                       | •                       |                         |                            |                  |                 |        |  |  |  |  |  |

|              | •                                                                     |                         |                         |                            |                  |                 |        |  |  |  |  |  |

|              | •                                                                     |                         |                         |                            |                  |                 |        |  |  |  |  |  |

|              | •<br>•<br>001 = Interrup                                              | ot is Priority 1        |                         |                            |                  |                 |        |  |  |  |  |  |

|              | •<br>•<br>001 = Interrup                                              |                         | abled                   |                            |                  |                 |        |  |  |  |  |  |

#### REGISTER 7-25: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

#### REGISTER 9-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

bit 3 SPI1MD: SPI1 Module Disable bit 1 = SPI1 module is disabled 0 = SPI1 module is enabled

#### bit 2-1 Unimplemented: Read as '0'

- bit 0 AD1MD: ADC1 Module Disable bit<sup>(2)</sup>

- 1 = ADC1 module is disabled

- 0 = ADC1 module is enabled

- **Note 1:** These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

- 2: PCFGx bits have no effect if the ADC module is disabled by setting this bit. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

#### REGISTER 9-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-------|-------|-------|

| —      | —   | —   | —   | —   | IC3MD | IC2MD | IC1MD |

| bit 15 |     |     |     |     |       |       | bit 8 |

|        |     |     |     |     |       |       |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0   | R/W-0 | R/W-0 |

| —      | —   | —   | —   | —   | —     | OC2MD | OC1MD |

| bit 7  |     |     | •   |     |       |       | bit 0 |

|        |     |     |     |     |       |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                 |

|-----------|------------------------------------------------------------|

| bit 10    | IC3MD: Input Capture 3 Module Disable bit                  |

|           | 1 = Input Capture 3 module is disabled                     |

|           | 0 = Input Capture 3 module is enabled                      |

| bit 9     | IC2MD: Input Capture 2 Module Disable bit                  |

|           | 1 = Input Capture 2 module is disabled                     |

|           | 0 = Input Capture 2 module is enabled                      |

| bit 8     | IC1MD: Input Capture 1 Module Disable bit                  |

|           | <ol> <li>I = Input Capture 1 module is disabled</li> </ol> |

|           | 0 = Input Capture 1 module is enabled                      |

| bit 7-2   | Unimplemented: Read as '0'                                 |

| bit 1     | OC2MD: Output Compare 2 Module Disable bit                 |

|           | 1 = Output Compare 2 module is disabled                    |

|           | 0 = Output Compare 2 module is enabled                     |

| bit 0     | OC1MD: Output Compare 1 Module Disable bit                 |

|           | 1 = Output Compare 1 module is disabled                    |

|           | 0 = Output Compare 1 module is enabled                     |

|           |                                                            |

#### 10.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See "**Pin Diagrams**" for the available pins and their functionality.

#### 10.2 Configuring Analog Port Pins

The AD1PCFGL and TRISx registers control the operation of the Analog-to-Digital port pins. The port pins that are to function as analog inputs must have their corresponding TRISx bit set (input). If the TRISx bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The AD1PCFGL register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORTx register is read, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 10.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP. A demonstration is shown in Example 10-1.

#### **10.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 21 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a Change-of-State.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

Note: Pull-ups on Input Change Notification pins should always be disabled when the port pin is configured as a digital output.

|      | LL 10-1.   |                                   |

|------|------------|-----------------------------------|

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> as inputs |

| MOV  | W0, TRISBB | ; and PORTB<7:0> as outputs       |

| NOP  |            | ; Delay 1 cycle                   |

| btss | PORTB, #13 | ; Next Instruction                |

|      |            |                                   |

EXAMPLE 10-1: PORT WRITE/READ EXAMPLE

| U-0          | U-0          | U-0              | U-0            | U-0                                      | U-0              | U-0          | U-0    |  |

|--------------|--------------|------------------|----------------|------------------------------------------|------------------|--------------|--------|--|

| _            | _            | —                |                |                                          | —                |              | —      |  |

| bit 15       | ·            | •                |                |                                          |                  |              | bit 8  |  |

|              |              |                  |                |                                          |                  |              |        |  |

| U-0          | U-0          | U-0              | R/W-1          | R/W-1                                    | R/W-1            | R/W-1        | R/W-1  |  |

| _            | —            | —                | OCFAR4         | OCFAR3                                   | OCFAR2           | OCFAR1       | OCFAR0 |  |

| bit 7        | ·            |                  | •              |                                          |                  |              | bit 0  |  |

|              |              |                  |                |                                          |                  |              |        |  |

| Legend:      |              |                  |                |                                          |                  |              |        |  |

| R = Readab   | ole bit      | W = Writable     | bit            | U = Unimpler                             | mented bit, read | l as '0'     |        |  |

| -n = Value a | at POR       | '1' = Bit is set |                | 0' = Bit is cleared $x = Bit is unknown$ |                  |              |        |  |

|              |              |                  |                |                                          |                  |              |        |  |

| bit 15-5     | Unimplemen   | ted: Read as '   | 0'             |                                          |                  |              |        |  |

| bit 4-0      | OCFAR<4:0>   | : Assign Outpu   | ut Capture A ( | OCFA) to the 0                           | Corresponding F  | RPn Pin bits |        |  |

|              | 11111 = Inpu | t tied to Vss    |                |                                          |                  |              |        |  |

|              | 11110 = Res  | erved            |                |                                          |                  |              |        |  |

|              | •            |                  |                |                                          |                  |              |        |  |

|              |              |                  |                |                                          |                  |              |        |  |

#### REGISTER 10-7: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

11010 = Reserved 11001 = Input tied to RP25

00001 = Input tied to RP1 00000 = Input tied to RP0

.

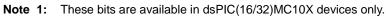

FIGURE 17-1:  $I^2C^{TM}$  BLOCK DIAGRAM (x = 1)

#### 18.3 UART Control Registers

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0                             | R/W-0                                  | R/W-0               | R/W-0            | U-0              | R/W-0                                         | R/W-0         |  |  |  |

|-----------------------|---------------------------------|----------------------------------------|---------------------|------------------|------------------|-----------------------------------------------|---------------|--|--|--|

| UARTEN <sup>(1)</sup> |                                 | USIDL                                  | IREN <sup>(2)</sup> | RTSMD            |                  | UEN1                                          | UEN0          |  |  |  |

| bit 15                |                                 |                                        |                     |                  |                  |                                               | bit 8         |  |  |  |

|                       |                                 |                                        |                     |                  |                  |                                               |               |  |  |  |

| R/W-0, HC             | R/W-0                           | R/W-0, HC                              | R/W-0               | R/W-0            | R/W-0            | R/W-0                                         | R/W-0         |  |  |  |

| WAKE                  | LPBACK                          | ABAUD                                  | URXINV              | BRGH             | PDSEL1           | PDSEL0                                        | STSEL         |  |  |  |

| bit 7                 |                                 |                                        |                     |                  |                  |                                               | bit           |  |  |  |

| Legend:               |                                 | HC = Hardwa                            | re Clearable b      | nit              |                  |                                               |               |  |  |  |

| R = Readable          | hit                             | W = Writable                           |                     |                  | mented bit, read | 1 as '0'                                      |               |  |  |  |

| -n = Value at F       |                                 | '1' = Bit is set                       |                     | '0' = Bit is cle |                  | x = Bit is unkn                               | own           |  |  |  |

|                       |                                 | 1 - Dit 13 300                         |                     |                  |                  |                                               | 00011         |  |  |  |

| bit 15                | UARTEN: UA                      | RTx Enable bi                          | t(1)                |                  |                  |                                               |               |  |  |  |

|                       |                                 |                                        |                     | e controlled by  | UARTx as defi    | ned by the UEN                                | l<1:0> bits   |  |  |  |

|                       | 0 = UARTx is                    |                                        |                     |                  |                  | JARTx power co                                |               |  |  |  |

|                       | minimal                         |                                        |                     |                  |                  |                                               |               |  |  |  |

| bit 14                | •                               | ted: Read as '                         |                     |                  |                  |                                               |               |  |  |  |

| bit 13                |                                 | Tx Stop in Idle                        |                     |                  |                  |                                               |               |  |  |  |

|                       |                                 | nues module op<br>s module oper        |                     |                  | Idle mode        |                                               |               |  |  |  |

| bit 12                |                                 | Encoder and D                          |                     |                  |                  |                                               |               |  |  |  |

| DIL 12                |                                 | oder and deco                          |                     |                  |                  |                                               |               |  |  |  |

|                       |                                 | oder and deco                          |                     |                  |                  |                                               |               |  |  |  |

| bit 11                | RTSMD: UAF                      | RTx Mode Sele                          | ction for UxR1      | S Pin bit        |                  |                                               |               |  |  |  |

|                       |                                 | oin is in Simple:<br>Sin is in Flow Co |                     |                  |                  |                                               |               |  |  |  |

| bit 10                | -                               | ted: Read as '                         |                     |                  |                  |                                               |               |  |  |  |

| bit 9-8               | UEN<1:0>: UARTx Pin Enable bits |                                        |                     |                  |                  |                                               |               |  |  |  |

|                       |                                 |                                        |                     |                  |                  | controlled by po                              | ort latches   |  |  |  |

|                       |                                 | JxRX, UxCTS a                          |                     |                  |                  | s controlled by p                             | ort latches   |  |  |  |

|                       |                                 |                                        |                     |                  |                  | /BCLK pins are                                |               |  |  |  |

|                       | port latc                       |                                        |                     |                  |                  | , <b>-                                   </b> |               |  |  |  |

| bit 7                 | WAKE: Wake                      | -up on Start bi                        | t Detect During     | g Sleep Mode     | Enable bit       |                                               |               |  |  |  |

|                       |                                 |                                        |                     | RX pin; interru  | pt is generated  | on falling edge,                              | bit is cleare |  |  |  |

|                       |                                 | are on following                       | g rising edge       |                  |                  |                                               |               |  |  |  |

|                       |                                 | -up is enabled                         |                     | 1.52             |                  |                                               |               |  |  |  |

| bit 6                 |                                 | RTx Loopback                           |                     | Dit              |                  |                                               |               |  |  |  |

|                       |                                 | Loopback mod<br>k mode is disal        |                     |                  |                  |                                               |               |  |  |  |

| bit 5                 | -                               | p-Baud Enable                          |                     |                  |                  |                                               |               |  |  |  |

| ~                     |                                 |                                        |                     | he next charac   | ter – reauires r | eception of a Sy                              | nc field (55h |  |  |  |

|                       |                                 | her data; clear                        |                     |                  |                  |                                               |               |  |  |  |

|                       |                                 | e measuremen                           |                     |                  |                  |                                               |               |  |  |  |

| Note 1: Ref           | er to "UART" (                  | DS70188) in th                         | ne "dsPIC33/F       | PIC24 Family F   | Reference Manu   | al" for information                           | on on         |  |  |  |

|                       | bling the UART                  |                                        |                     |                  |                  |                                               |               |  |  |  |

|                       | e foaturo ie ava                |                                        |                     | -                |                  |                                               |               |  |  |  |

2: This feature is available for 16x BRG mode (BRGH = 0) only.

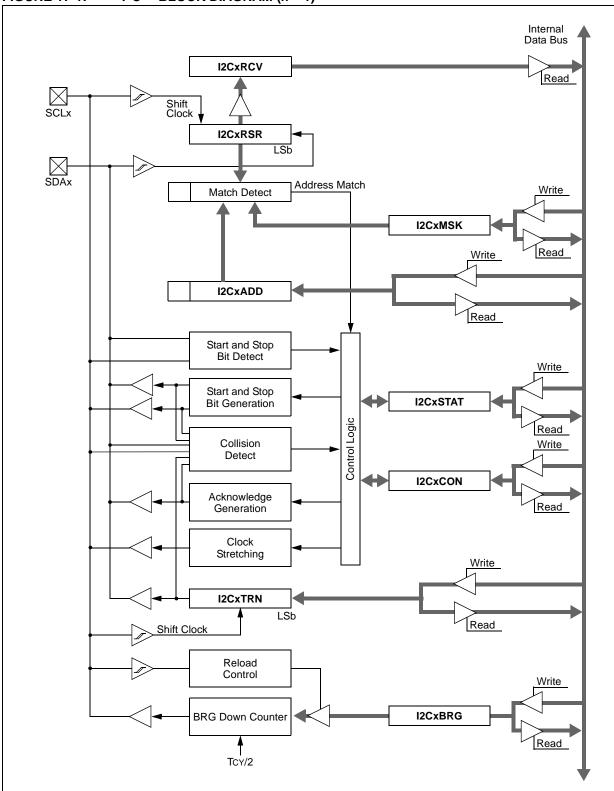

#### FIGURE 20-4: DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

| REGISTER      | 20-2: CMxC                   | ON: COMPA                                                 | RATOR x CO                    | ONTROL REG        | GISTER          |                                      |                |  |  |  |  |

|---------------|------------------------------|-----------------------------------------------------------|-------------------------------|-------------------|-----------------|--------------------------------------|----------------|--|--|--|--|

| R/W-0         | R/W-0                        | R/W-0                                                     | U-0                           | U-0               | U-0             | R/W-0                                | R/W-0          |  |  |  |  |

| CON           | COE                          | CPOL                                                      | _                             | _                 | _               | CEVT                                 | COUT           |  |  |  |  |

| bit 15        |                              |                                                           |                               |                   |                 |                                      | bit 8          |  |  |  |  |

| R/W-0         | R/W-0                        | U-0                                                       | R/W-0                         | U-0               | U-0             | R/W-0                                | R/W-0          |  |  |  |  |

| EVPOL1        | EVPOL0                       | 0-0                                                       | CREF                          |                   |                 | CCH1                                 | CCH0           |  |  |  |  |

| bit 7         | LVIOLO                       |                                                           | GIVEI                         |                   |                 | Com                                  | bit C          |  |  |  |  |

|               |                              |                                                           |                               |                   |                 |                                      |                |  |  |  |  |

| Legend:       |                              |                                                           |                               |                   |                 |                                      |                |  |  |  |  |

| R = Readable  |                              | W = Writable                                              |                               | -                 | nented bit, rea |                                      |                |  |  |  |  |

| -n = Value at | POR                          | '1' = Bit is se                                           | t                             | '0' = Bit is clea | ared            | x = Bit is unkr                      | iown           |  |  |  |  |

| bit 15        | CON: Compa                   | arator x Enable                                           | bit                           |                   |                 |                                      |                |  |  |  |  |

|               | =                            | tor x is enable                                           |                               |                   |                 |                                      |                |  |  |  |  |

|               |                              | tor x is disable                                          |                               |                   |                 |                                      |                |  |  |  |  |

| bit 14        | COE: Compa                   | arator x Output                                           | Enable bit                    |                   |                 |                                      |                |  |  |  |  |

|               |                              | tor output is pr<br>tor output is in                      | esent on the C<br>ternal only | xOUT pin          |                 |                                      |                |  |  |  |  |

| bit 13        | CPOL: Comp                   | parator x Outpu                                           | it Polarity Sele              | ct bit            |                 |                                      |                |  |  |  |  |

|               |                              | tor x output is tor x output is                           |                               |                   |                 |                                      |                |  |  |  |  |

| bit 12-10     | Unimplemen                   | ted: Read as                                              | 0'                            |                   |                 |                                      |                |  |  |  |  |

| bit 9         | CEVT: Comparator x Event bit |                                                           |                               |                   |                 |                                      |                |  |  |  |  |

|               | interrupts                   | ator x event ac<br>s until the bit is<br>ator x event dic | cleared                       | POL<1:0> set      | ings occurred   | ; disables future                    | e triggers and |  |  |  |  |

| bit 8         | COUT: Comp                   | parator x Outpu                                           | ıt bit                        |                   |                 |                                      |                |  |  |  |  |

|               | 1 = VIN+ > VI                |                                                           | ted polarity):                |                   |                 |                                      |                |  |  |  |  |

|               | 0 = VIN+ < VI                |                                                           |                               |                   |                 |                                      |                |  |  |  |  |

|               |                              | When CPOL = 1 (inverted polarity):<br>1 = VIN+ < VIN-     |                               |                   |                 |                                      |                |  |  |  |  |

|               | 0 = VIN + > VI               |                                                           |                               |                   |                 |                                      |                |  |  |  |  |

| bit 7-6       | EVPOL<1:0>                   | . Trigger/Ever                                            | t/Interrupt Pola              | arity Select bits |                 |                                      |                |  |  |  |  |

|               | 10 = Trigger/                |                                                           | is generated                  |                   |                 | ator output (whil<br>tion of the pol |                |  |  |  |  |

|               | If $CPOL = 1$ (              | (inverted polari                                          |                               | 1421.14           |                 |                                      |                |  |  |  |  |

|               | •                            | (non-inverted p                                           | •                             | արտ.              |                 |                                      |                |  |  |  |  |

|               |                              |                                                           | comparator ou                 | ıtput.            |                 |                                      |                |  |  |  |  |

|               |                              | event/interrupt/<br>ator output (wh                       |                               | only on low-      | to-high transi  | tion of the pol                      | arity selected |  |  |  |  |

|               |                              | (inverted polari<br>ransition of the                      | t <u>y):</u><br>comparator οι | itput.            |                 |                                      |                |  |  |  |  |

|               | -                            | (non-inverted p                                           | -                             |                   |                 |                                      |                |  |  |  |  |

|               | Low-to-high t                | ransition of the                                          | comparator o                  | -                 |                 |                                      |                |  |  |  |  |

|               | 00 = Trigger/                | event/interrupt                                           | generation is o               | disabled          |                 |                                      |                |  |  |  |  |

|               |                              | ted: Read as                                              |                               |                   |                 |                                      |                |  |  |  |  |

#### CIETED 20 2 CMACONI COMPADATOD A CONTROL DECISTED

|                 | REGI                                       | STER                                                   |                                        | X WASK GA        | ATING CONTI                            | ROL             |       |  |  |

|-----------------|--------------------------------------------|--------------------------------------------------------|----------------------------------------|------------------|----------------------------------------|-----------------|-------|--|--|

| R/W-0           | U-0                                        | R/W-0                                                  | R/W-0                                  | R/W-0            | R/W-0                                  | R/W-0           | R/W-0 |  |  |

| HLMS            |                                            | OCEN                                                   | OCNEN                                  | OBEN             | OBNEN                                  | OAEN            | OANEN |  |  |

| bit 15          |                                            |                                                        |                                        |                  |                                        |                 | bit 8 |  |  |

| R/W-0           | R/W-0                                      | R/W-0                                                  | R/W-0                                  | R/W-0            | R/W-0                                  | R/W-0           | R/W-0 |  |  |

| NAGS            | PAGS                                       | ACEN                                                   | ACNEN                                  | ABEN             | ABNEN                                  | AAEN            | AANEN |  |  |

| bit 7           |                                            |                                                        |                                        |                  |                                        |                 | bit 0 |  |  |

| Legend:         |                                            |                                                        |                                        |                  |                                        |                 |       |  |  |

| R = Readable b  | oit                                        | W = Writable                                           | bit                                    | U = Unimple      | mented bit, read                       | d as '0'        |       |  |  |

| -n = Value at P | OR                                         | '1' = Bit is se                                        | t                                      | '0' = Bit is cle | eared                                  | x = Bit is unki | nown  |  |  |

| bit 15          | 1 = The mas<br>0 = The mas                 | king (blanking)                                        | function will pro<br>function will pro | event any asse   | erted ('0') compa<br>erted ('1') compa |                 |       |  |  |

| bit 14          | -                                          | nted: Read as                                          |                                        | L :4             |                                        |                 |       |  |  |

| bit 13          | 1 = MCI is c                               | Gate C Input In<br>connected to OF<br>not connected to | R gate                                 | DIT              |                                        |                 |       |  |  |

| bit 12          | OCNEN: OR Gate C Input Inverted Enable bit |                                                        |                                        |                  |                                        |                 |       |  |  |

|                 |                                            | MCI is connec<br>MCI is not con                        |                                        |                  |                                        |                 |       |  |  |

| bit 11          | OBEN: OR                                   | BEN: OR Gate B Input Inverted Enable bit               |                                        |                  |                                        |                 |       |  |  |

|                 |                                            | onnected to OF<br>ot connected to                      |                                        |                  |                                        |                 |       |  |  |

| bit 10          |                                            | R Gate B Input                                         |                                        |                  |                                        |                 |       |  |  |

|                 |                                            | MBI is connect<br>MBI is not con                       |                                        |                  |                                        |                 |       |  |  |

| bit 9           | OAEN: OR                                   | Gate A Input Er                                        | nable bit                              |                  |                                        |                 |       |  |  |

|                 |                                            | onnected to OF<br>ot connected to                      |                                        |                  |                                        |                 |       |  |  |

| bit 8           | OANEN: OF                                  | R Gate A Input                                         | Inverted Enabl                         | e bit            |                                        |                 |       |  |  |

|                 |                                            | MAI is connect<br>MAI is not con                       | •                                      |                  |                                        |                 |       |  |  |

| bit 7           | 1 = Inverted                               | ative AND Gate<br>ANDI is conne<br>ANDI is not co      | cted to OR gat                         | te               |                                        |                 |       |  |  |

| bit 6           | 1 = ANDI is                                | tive AND Gate<br>connected to C<br>not connected       | R gate                                 |                  |                                        |                 |       |  |  |

| bit 5           | ACEN: AND<br>1 = MCI is c                  | O Gate A1 C Inp<br>connected to AN                     | out Inverted En                        | able bit         |                                        |                 |       |  |  |

|                 |                                            | of connected 1-                                        |                                        |                  |                                        |                 |       |  |  |

| bit 4           |                                            | ot connected to                                        | -                                      | nabla kit        |                                        |                 |       |  |  |

#### DECISTED 20-4. CMVMSKCON- COMPADATOR V MASK GATING CONTROL

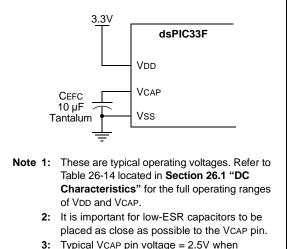

#### 23.2 On-Chip Voltage Regulator

All of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 23-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 26-14 located in **Section 26.1** "**DC Characteristics**".

| Note: | It is important for low-ESR capacitors to be |

|-------|----------------------------------------------|

|       | placed as close as possible to the VCAP pin. |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 23-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

**3:** Typical VCAP pin voltage = 2.5V when VDD  $\ge$  VDDMIN.

#### 23.3 BOR: Brown-out Reset

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an Oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

# TABLE 26-35:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ16(GP/MC)10X

| AC CH        | ARACTERIS             | TICS                                                         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                                      |  |

|--------------|-----------------------|--------------------------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions                           |  |

| SP70         | TscP                  | Maximum SCKx Input Frequency                                 | _                                                     |                    | 15  | MHz   | See Note 3                           |  |

| SP72         | TscF                  | SCKx Input Fall Time                                         | —                                                     |                    |     | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP73         | TscR                  | SCKx Input Rise Time                                         | —                                                     |                    |     | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                   | _                                                     |                    | _   | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                   | _                                                     |                    | _   | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                     | 6                  | 20  | ns    |                                      |  |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                    | _                  | _   | ns    |                                      |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                    | _                  | _   | ns    |                                      |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                    | _                  | _   | ns    |                                      |  |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                   | —                  | _   | ns    |                                      |  |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10                                                    | —                  | 50  | ns    | See Note 4                           |  |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 Tcy + 40                                          | _                  |     | ns    | See Note 4                           |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCKx clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

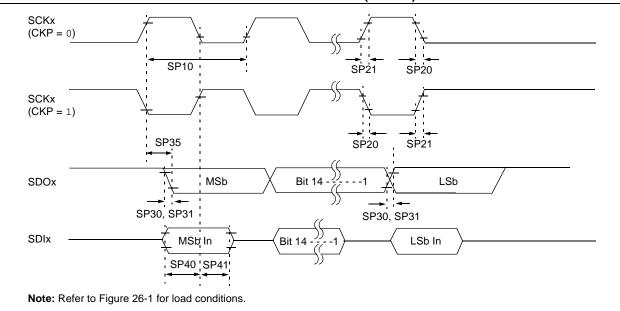

#### FIGURE 26-22: SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS FOR dsPIC33FJ32(GP/MC)10X

# TABLE 26-40:SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ32(GP/MC)10X

| AC CHA       |                       | Standard<br>(unless of<br>Operating           | otherwise | <b>stated)</b><br>ture -40 | °C ≤ Ta ≤ | V to 3.6V<br>+85°C for Industrial<br>+125°C for Extended |                                       |

|--------------|-----------------------|-----------------------------------------------|-----------|----------------------------|-----------|----------------------------------------------------------|---------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                 | Min       | Тур <sup>(2)</sup>         | Max       | Units                                                    | Conditions                            |

| SP10         | TscP                  | Maximum SCKx Frequency                        |           | _                          | 9         | MHz                                                      | -40°C to +125°C,<br>see <b>Note 3</b> |

| SP20         | TscF                  | SCKx Output Fall Time                         | _         | —                          | _         | ns                                                       | See Parameter DO32 and Note 4         |

| SP21         | TscR                  | SCKx Output Rise Time                         | _         | —                          | _         | ns                                                       | See Parameter DO31 and <b>Note 4</b>  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                    | _         | —                          | _         | ns                                                       | See Parameter DO32 and Note 4         |

| SP31         | TdoR                  | SDOx Data Output Rise Time                    | _         | —                          | _         | ns                                                       | See Parameter DO31 and Note 4         |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge     | _         | 6                          | 20        | ns                                                       |                                       |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge  | 30        |                            |           | ns                                                       |                                       |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30        | —                          | —         | ns                                                       |                                       |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30        |                            |           | ns                                                       |                                       |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

| AC CH        | ARACTER | RISTICS          |                           | Standard Operatin<br>(unless otherwise<br>Operating temperat | <b>stated)</b><br>ure -40 | °C ≤ Ta ≤ | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------|---------|------------------|---------------------------|--------------------------------------------------------------|---------------------------|-----------|-----------------------------------------------------------------|

| Param<br>No. | Symbol  | Charac           | teristic                  | Min <sup>(1)</sup> Max                                       |                           | Units     | Conditions                                                      |

| IM10         | TLO:SCL | Clock Low Time   | 100 kHz mode              | Tcy/2 (BRG + 1)                                              |                           | μS        |                                                                 |

|              |         |                  | 400 kHz mode              | Tcy/2 (BRG + 1)                                              |                           | μS        |                                                                 |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                              |                           | μS        |                                                                 |

| IM11         | THI:SCL | Clock High Time  | 100 kHz mode              | Tcy/2 (BRG + 1)                                              |                           | μS        |                                                                 |

|              |         |                  | 400 kHz mode              | Tcy/2 (BRG + 1)                                              |                           | μS        |                                                                 |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                              |                           | μS        |                                                                 |

| IM20         | TF:SCL  | SDAx and SCLx    | 100 kHz mode              |                                                              | 300                       | ns        | CB is specified to be                                           |

|              |         | Fall Time        | 400 kHz mode              | 20 + 0.1 Св                                                  | 300                       | ns        | from 10 to 400 pF                                               |

|              |         |                  | 1 MHz mode <sup>(2)</sup> |                                                              | 100                       | ns        |                                                                 |

| IM21         | TR:SCL  | SDAx and SCLx    | 100 kHz mode              | _                                                            | 1000                      | ns        | CB is specified to be                                           |

|              |         | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                                  | 300                       | ns        | from 10 to 400 pF                                               |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | —                                                            | 300                       | ns        | 1                                                               |

| IM25         | TSU:DAT | Data Input       | 100 kHz mode              | 250                                                          | _                         | ns        |                                                                 |

|              |         | Setup Time       | 400 kHz mode              | 100                                                          |                           | ns        | -                                                               |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 40                                                           |                           | ns        | 1                                                               |

| IM26         | THD:DAT | Data Input       | 100 kHz mode              | 0                                                            |                           | μS        |                                                                 |

|              |         | Hold Time        | 400 kHz mode              | 0                                                            | 0.9                       | μS        |                                                                 |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 0.2                                                          |                           | μS        | -                                                               |

| IM30         | TSU:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 1)                                              |                           | μS        | Only relevant for                                               |

|              |         | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 1)                                              | _                         | μS        | Repeated Start                                                  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                              |                           | μS        | condition                                                       |

| IM31         | THD:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 1)                                              | _                         | μS        | After this period the first                                     |

|              |         | Hold Time        | 400 kHz mode              | Tcy/2 (BRG + 1)                                              |                           | μS        | clock pulse is generated                                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                              |                           | μS        | 1                                                               |

| IM33         | TSU:STO | Stop Condition   | 100 kHz mode              | Tcy/2 (BRG + 1)                                              |                           | μS        |                                                                 |

|              |         | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 1)                                              |                           | μS        | -                                                               |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                              |                           | μS        | 1                                                               |

| IM34         | THD:STO | Stop Condition   | 100 kHz mode              | Tcy/2 (BRG + 1)                                              |                           | ns        |                                                                 |

|              |         | Hold Time        | 400 kHz mode              | Tcy/2 (BRG + 1)                                              |                           | ns        |                                                                 |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                              |                           | ns        |                                                                 |

| IM40         | TAA:SCL | Output Valid     | 100 kHz mode              | —                                                            | 3500                      | ns        |                                                                 |

|              |         | from Clock       | 400 kHz mode              | —                                                            | 1000                      | ns        |                                                                 |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                            | 400                       | ns        |                                                                 |

| IM45         | TBF:SDA | Bus Free Time    | 100 kHz mode              | 4.7                                                          |                           | μS        | Time the bus must be                                            |

| -            | _       |                  | 400 kHz mode              | 1.3                                                          |                           | μS        | free before a new                                               |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 0.5                                                          | _                         | μs        | transmission can start                                          |

| IM50         | Св      | Bus Capacitive L |                           |                                                              | 400                       | pF        |                                                                 |

| IM51         | TPGD    | Pulse Gobbler De |                           | 65                                                           | 390                       | ns        | See Note 3                                                      |

#### TABLE 26-45: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

Note 1: BRG is the value of the I<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70195) in the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site for the latest "dsPIC33/PIC24 Family Reference Manual" sections.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** Typical value for this parameter is 130 ns.

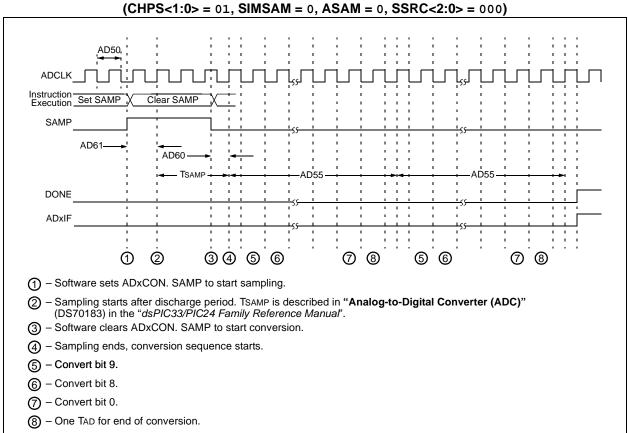

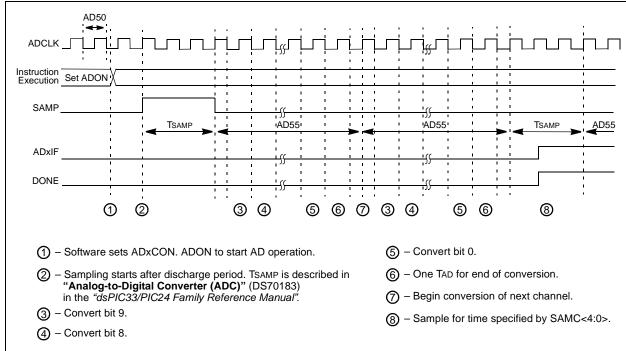

#### FIGURE 26-31: ADC CONVERSION TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000

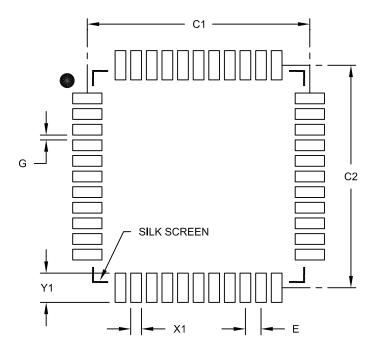

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                          | Ν      | /ILLIMETER | S     |      |  |

|--------------------------|--------|------------|-------|------|--|

| Dimension                | Limits | MIN        | NOM   | MAX  |  |

| Contact Pitch            | E      | 0.80 BSC   |       |      |  |

| Contact Pad Spacing      | C1     |            | 11.40 |      |  |

| Contact Pad Spacing      | C2     |            | 11.40 |      |  |

| Contact Pad Width (X44)  | X1     |            |       | 0.55 |  |

| Contact Pad Length (X44) | Y1     |            |       | 1.50 |  |

| Distance Between Pads    | G      | 0.25       |       |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

#### APPENDIX A: REVISION HISTORY

#### **Revision A (January 2011)**

This is the initial released version of the document.

#### **Revision B (February 2011)**

All major changes are referenced by their respective section in Table A-1.

In addition, minor text and formatting changes were incorporated throughout the document.

| TABLE A-1: | MAJOR SECTION UPDATE | S |

|------------|----------------------|---|

|            |                      |   |

| Section Name                                                          | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|