Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 13                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | - ·                                                                              |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 18-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp101t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

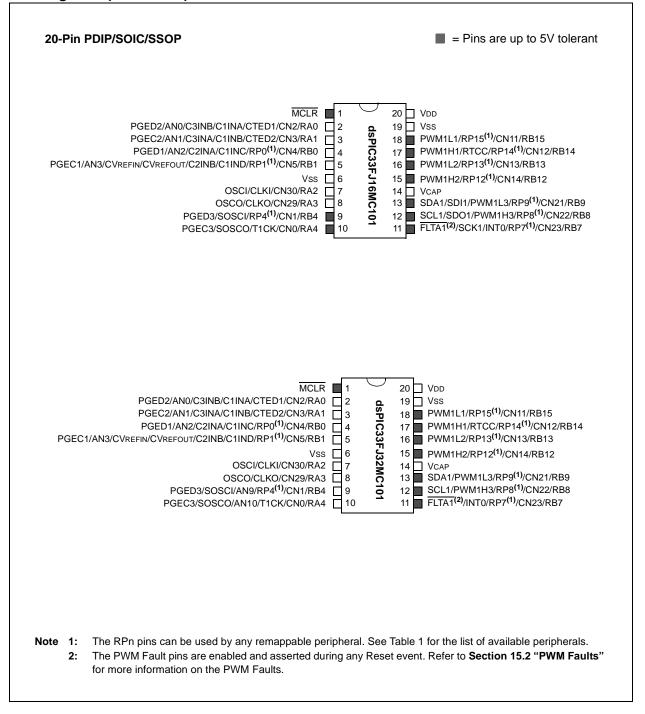

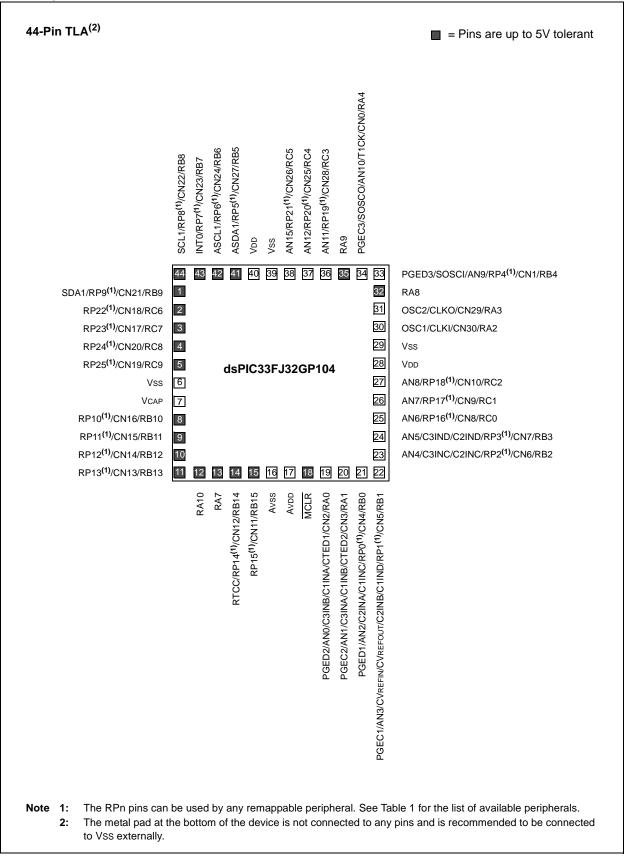

#### Pin Diagrams (Continued)

#### Pin Diagrams (Continued)

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz < FIN < 8 MHz (for MSPLL mode) or 3 MHz < FIN < 8 MHz (for ECPLL mode) to comply with device PLL start-up conditions. HSPLL mode is not supported. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The fixed PLL settings of 4x after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can enable the PLL and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

#### 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator is selected as a debugger, it automatically initializes all of the Analog-to-Digital input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in the register that correspond to the Analog-to-Digital pins that are initialized by MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain Analog-to-Digital pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all Analog-to-Digital pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

#### 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternately, connect a 1k to 10k resistor between Vss and unused pins.

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts are disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                                                                       |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | 1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                  |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of a magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                                                       |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                     |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                                    |

| Note 1: | This bit can be read or cleared (not set).                                                                                                                                                                                                                                                                                                                                                                                                 |

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

| U-0             | U-0                            | U-0                                   | R/W-0           | R/W-0               | R-0              | R-0              | R-0   |

|-----------------|--------------------------------|---------------------------------------|-----------------|---------------------|------------------|------------------|-------|

| —               | —                              | _                                     | US              | EDT <sup>(1)</sup>  | DL2              | DL1              | DL0   |

| bit 15          |                                |                                       |                 |                     |                  |                  | bit   |

| R/W-0           | R/W-0                          | R/W-1                                 | R/W-0           | R/C-0               | R/W-0            | R/W-0            | R/W-0 |

| SATA            | SATB                           | SATDW                                 | ACCSAT          | IPL3 <sup>(2)</sup> | PSV              | R/W-0            | IF    |

| bit 7           | SAID                           | SAIDW                                 | ACCOAT          | IF L3. 7            | F3V              | RND              | bit   |

|                 |                                |                                       |                 |                     |                  |                  | Dit   |

| Legend:         |                                | C = Clearable                         | e bit           |                     |                  |                  |       |

| R = Readabl     | e bit                          | W = Writable                          | bit             | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is cle | ared                           | 'x = Bit is unk                       | nown            | U = Unimple         | mented bit, read | d as '0'         |       |

| bit 15-13       | Unimplemen                     | ted: Read as '                        | 0'              |                     |                  |                  |       |

| bit 12          | -                              | tiply Unsigned                        |                 | ol bit              |                  |                  |       |

|                 |                                | ne multiplies a                       | •               |                     |                  |                  |       |

|                 | 0 = DSP engi                   | ne multiplies a                       | ire signed      |                     |                  |                  |       |

| bit 11          |                                | Loop Termina                          |                 |                     |                  |                  |       |

|                 | 1 = Terminate<br>0 = No effect | es executing Do                       | o loop at the e | nd of current lo    | oop iteration    |                  |       |

| bit 10-8        | DL<2:0>: DO                    | Loop Nesting                          | Level Status b  | its                 |                  |                  |       |

|                 | 111 <b>= 7</b> DO <b>lo</b>    | ops are active                        |                 |                     |                  |                  |       |

|                 | •                              |                                       |                 |                     |                  |                  |       |

|                 | •<br>001 = 1 DO lo             | on is activo                          |                 |                     |                  |                  |       |

|                 |                                | ops are active                        |                 |                     |                  |                  |       |

| bit 7           | SATA: ACCA                     | Saturation En                         | able bit        |                     |                  |                  |       |

|                 |                                | itor A saturatio                      |                 |                     |                  |                  |       |

|                 |                                | itor A saturatio                      |                 |                     |                  |                  |       |

| bit 6           |                                | Saturation En                         |                 |                     |                  |                  |       |

|                 |                                | tor B saturatio                       |                 |                     |                  |                  |       |

| bit 5           |                                |                                       |                 | ine Saturation      | Enable bit       |                  |       |

|                 |                                | ce write satura                       |                 |                     |                  |                  |       |

|                 |                                | ce write satura                       |                 |                     |                  |                  |       |

| bit 4           | ACCSAT: Acc                    | cumulator Satu                        | uration Mode S  | Select bit          |                  |                  |       |

|                 |                                | ration (super s                       |                 |                     |                  |                  |       |

| L:1 0           |                                | ration (normal                        | ,               | ··· (2)             |                  |                  |       |

| bit 3           |                                | terrupt Priority<br>rrupt Priority Le |                 |                     |                  |                  |       |

|                 |                                | rupt Priority Le                      | •               |                     |                  |                  |       |

| bit 2           |                                |                                       |                 | ace Enable bit      |                  |                  |       |

|                 |                                | space is visible                      |                 |                     |                  |                  |       |

|                 | -                              | space is not vi                       |                 | pace                |                  |                  |       |

| bit 1           |                                | ng Mode Sele                          |                 |                     |                  |                  |       |

|                 |                                | onventional) ro<br>(convergent)       |                 |                     |                  |                  |       |

| bit 0           | IF: Integer or                 | Fractional Mul                        | tiplier Mode S  | elect bit           |                  |                  |       |

|                 | -                              |                                       |                 | iply operations     |                  |                  |       |

|                 | 0 = Fractional                 | l mode is enab                        | led for DSP m   | nultiply operation  | ons              |                  |       |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

The SAC and SAC.R instructions store either a truncated (SAC), or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see **Section 3.6.3.2 "Data Space Write Saturation**"). For the MAC class of instructions, the accumulator writeback operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

#### 3.6.3.2 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly:

- For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF.

- For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000.

The MSb of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

#### 3.6.4 BARREL SHIFTER

The barrel shifter can perform up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts, in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between Bit Positions 16 and 31 for right shifts, and between Bit Positions 0 and 16 for left shifts.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed, but the contents of the register remain unchanged.

#### 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWM<3:0> bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the bit-reversed address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

**Note:** All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XB<14:0> value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing should not be enabled together. If an application attempts to do so, Bit-Reversed Addressing will assume priority when active. For the X WAGU and Y AGU, Modulo Addressing will be disabled. However, Modulo Addressing will continue to function in the X RAGU.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70191) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows a device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows users to manufacture boards with unprogrammed devices and then program the Digital Signal Controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data in a single program memory word and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes).

#### 5.1 Table Instructions and Flash Programming

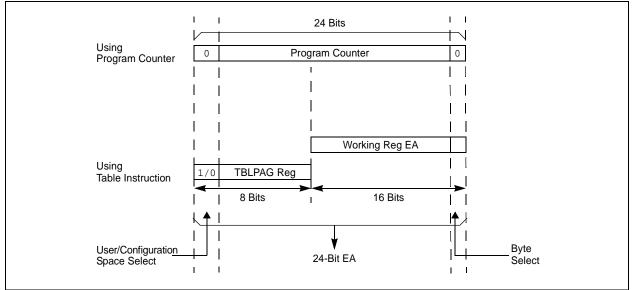

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space, from the data memory, while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1:

: ADDRESSING FOR TABLE REGISTERS

#### FIGURE 7-1: dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 INTERRUPT VECTOR TABLE

| 1                                 |                                            | 7                    |                                                        |

|-----------------------------------|--------------------------------------------|----------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction                   | 0x000000             |                                                        |

|                                   | Reset – GOTO Address                       | 0x000002             |                                                        |

|                                   | Reserved                                   | 0x000004             |                                                        |

|                                   | Oscillator Fail Trap Vector                | _                    |                                                        |

|                                   | Address Error Trap Vector                  | _                    |                                                        |

|                                   | Stack Error Trap Vector                    | _                    |                                                        |

|                                   | Math Error Trap Vector                     | _                    |                                                        |

|                                   | Reserved                                   | -                    |                                                        |

|                                   | Reserved                                   | _                    |                                                        |

|                                   | Reserved<br>Interrupt Vector 0             | 0x000014             |                                                        |

|                                   | Interrupt Vector 1                         | 0,000014             |                                                        |

|                                   |                                            | -                    |                                                        |

|                                   | ~                                          |                      |                                                        |

|                                   | ~                                          | _                    |                                                        |

|                                   | Interrupt Vector 52                        | 0x00007C             | (4)                                                    |

|                                   | Interrupt Vector 53                        | 0x00007E             | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ity                               | Interrupt Vector 54                        | 0x000080             |                                                        |

| iori                              | ~                                          |                      |                                                        |

| ā                                 | ~                                          |                      |                                                        |

| der                               | ~                                          |                      |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 116                       | 0x0000FC             |                                                        |

| ra                                | Interrupt Vector 117                       | 0x0000FE             |                                                        |

| atu                               | Reserved                                   | 0x000100             |                                                        |

| Z                                 | Reserved                                   | 0x000102             |                                                        |

| sing                              | Reserved                                   |                      |                                                        |

| eas                               | Oscillator Fail Trap Vector                |                      |                                                        |

| ecr                               | Address Error Trap Vector                  |                      |                                                        |

| ă                                 | Stack Error Trap Vector                    |                      |                                                        |

|                                   | Math Error Trap Vector                     |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Interrupt Vector 0                         | 0x000114             |                                                        |

|                                   | Interrupt Vector 1                         | _                    |                                                        |

|                                   | ~                                          | 4                    |                                                        |

|                                   | ~                                          | 4                    |                                                        |

|                                   | ~<br>Interrupt Vector 52                   | 0x000470             | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   |                                            | 0x00017C             |                                                        |

|                                   | Interrupt Vector 53<br>Interrupt Vector 54 | 0x00017E<br>0x000180 |                                                        |

|                                   | ~                                          | 0000180              |                                                        |

|                                   | ~                                          | -                    |                                                        |

|                                   | ~ ~                                        | _                    |                                                        |

|                                   | -<br>Interrupt Vector 116                  | -                    |                                                        |

|                                   | Interrupt Vector 117                       | 0x0001FE             |                                                        |

| *                                 | Start of Code                              | 0x000200             | L                                                      |

|                                   |                                            |                      |                                                        |

| Note 1: See                       | e Table 7-1 for the list of impleme        | ented interrupt v    | ectors.                                                |

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| U-0               | U-0                                                                                 | R/W-0                                                | U-0                                                                | U-0                                      | U-0 | U-0   | U-0                    |  |  |  |

|-------------------|-------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------|-----|-------|------------------------|--|--|--|

| —                 | —                                                                                   | CTMUIF                                               | —                                                                  | —                                        | —   | —     | -                      |  |  |  |

| bit 15            |                                                                                     |                                                      |                                                                    |                                          |     |       | bit 8                  |  |  |  |

|                   |                                                                                     |                                                      |                                                                    |                                          |     |       |                        |  |  |  |

| U-0               | U-0                                                                                 | U-0                                                  | U-0                                                                | U-0                                      | U-0 | R/W-0 | R/W-0                  |  |  |  |

|                   | —                                                                                   | —                                                    | —                                                                  |                                          |     | U1EIF | FLTB1IF <sup>(1)</sup> |  |  |  |

| bit 7             |                                                                                     |                                                      |                                                                    |                                          |     |       | bit 0                  |  |  |  |

| [                 |                                                                                     |                                                      |                                                                    |                                          |     |       |                        |  |  |  |

| Legend:           |                                                                                     |                                                      |                                                                    |                                          |     |       |                        |  |  |  |

| R = Readab        | le bit                                                                              | W = Writable                                         | bit                                                                | U = Unimplemented bit, read as '0'       |     |       |                        |  |  |  |

| -n = Value a      | t POR                                                                               | '1' = Bit is set                                     |                                                                    | 0' = Bit is cleared $x = Bit is unknown$ |     |       |                        |  |  |  |

|                   |                                                                                     |                                                      |                                                                    |                                          |     |       |                        |  |  |  |

| bit 15-14         | Unimplemen                                                                          | ted: Read as '                                       | o'                                                                 |                                          |     |       |                        |  |  |  |

| bit 13            | CTMUIF: CTM                                                                         | MU Interrupt Fla                                     | ag Status bit                                                      |                                          |     |       |                        |  |  |  |

|                   |                                                                                     | equest has occ                                       |                                                                    |                                          |     |       |                        |  |  |  |

|                   | 0 = Interrupt r                                                                     | equest has not                                       | occurred                                                           |                                          |     |       |                        |  |  |  |

|                   |                                                                                     |                                                      |                                                                    |                                          |     |       |                        |  |  |  |

| bit 12-2          | Unimplemen                                                                          | ted: Read as '                                       | כי                                                                 |                                          |     |       |                        |  |  |  |

| bit 12-2<br>bit 1 | -                                                                                   | t <b>ed:</b> Read as '(<br>1 Error Interru           |                                                                    | bit                                      |     |       |                        |  |  |  |

|                   | <b>U1EIF:</b> UART<br>1 = Interrupt r                                               | 1 Error Interrup                                     | ot Flag Status<br>curred                                           | bit                                      |     |       |                        |  |  |  |

|                   | <b>U1EIF:</b> UART<br>1 = Interrupt r<br>0 = Interrupt r                            | 1 Error Interrup<br>equest has occ<br>equest has not | ot Flag Status<br>curred<br>coccurred                              |                                          |     |       |                        |  |  |  |

|                   | <b>U1EIF:</b> UART<br>1 = Interrupt r<br>0 = Interrupt r                            | 1 Error Interrup                                     | ot Flag Status<br>curred<br>coccurred                              |                                          |     |       |                        |  |  |  |

| bit 1             | U1EIF: UART<br>1 = Interrupt r<br>0 = Interrupt r<br>FLTB1IF: PW<br>1 = Interrupt r | 1 Error Interrup<br>equest has occ<br>equest has not | ot Flag Status<br>curred<br>coccurred<br>errupt Flag Sta<br>curred |                                          |     |       |                        |  |  |  |

#### REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

Note 1: This bit is available in dsPIC(16/32)MC102/104 devices only.

#### **PMD Control Registers** 9.5

| R/W-0       U-0       R/W-0       U-0       R/W-0       U-0       R/W-0         I2C1MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0               | R/W-0               | R/W-0            | R/W-0                  | R/W-0          | U-0            | R/W-0     | U-0                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|------------------|------------------------|----------------|----------------|-----------|----------------------|

| R/W-0       U-0       R/W-0       U-0       R/W-0       U-0       R/W-0         I2C1MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | T5MD <sup>(1)</sup> | T4MD <sup>(1)</sup> | T3MD             | T2MD                   | T1MD           | _              | PWM1MD    | _                    |

| I2C1MD       -       U1MD       -       SPI1MD       -       AD1MDf2         bit 7       bit       -       bit       bit       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       nn = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is disabled       0 = Timer7 module is disabled         bit 14       T4MD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer7 module is disabled       0 = Timer7 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is enabled         bit 14       T4MD: Timer2 Module Disable bit       1 = Timer2 module is enabled       0 = Timer7 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled         bit 11       Timer1 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15              | •                   |                  | 1                      |                |                |           | bit                  |

| I2C1MD       -       U1MD       -       SPI1MD       -       AD1MDf2         bit 7       bit       -       bit       bit       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       nn = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is disabled       0 = Timer7 module is disabled         bit 14       T4MD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer7 module is disabled       0 = Timer7 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is enabled         bit 14       T4MD: Timer2 Module Disable bit       1 = Timer2 module is enabled       0 = Timer7 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled         bit 11       Timer1 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                     |                  |                        |                |                |           |                      |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 T5MD: Timer5 Module Disable bit <sup>(1)</sup><br>1 = Timer5 module is enabled<br>0 = Timer5 module is enabled<br>0 = Timer4 module is enabled<br>0 = Timer4 module is disabled<br>0 = Timer3 module is enabled<br>0 = Timer3 module is enabled<br>0 = Timer4 module Disable bit<br>1 = Timer2 Module Disable bit<br>1 = Timer2 Module Disable bit<br>1 = Timer2 module is disabled<br>0 = Timer4 module is enabled<br>0 = Timer7 module is enabled<br>0 = Timer7 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer1 module is disabled<br>0 = UART1 modul | R/W-0               | U-0                 | R/W-0            | U-0                    | R/W-0          | U-0            | U-0       | R/W-0                |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>in = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 T5MD: Timer5 Module Disable bit <sup>(1)</sup><br>1 = Timer5 module is disabled<br>0 = Timer5 module is disabled<br>0 = Timer4 module is disabled<br>0 = Timer4 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is enabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is enabled<br>0 = Timer2 module is enabled<br>0 = Timer1 module is disabled<br>0 = Timer1 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is enabled<br>0 = Timer4 module is disabled<br>0 = UXM11 module is disabled<br>0 = UXM11 module is disabled<br>0 = UART1 module is disabled<br>0 = UART4 module i | I2C1MD              |                     | U1MD             |                        | SPI1MD         | _              | —         | AD1MD <sup>(2)</sup> |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         Dit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is enabled         0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 14       T4MD: Timer6 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is disabled         Dit 12       T2MD: Timer1 Module Disable bit       1 = Timer2 module is disabled       0 = Timer2 module is disabled         Dit 11       T1MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer4 module is disabled         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 10       Unimplemented: Read as '0'       0       0         Dit 7       I2C1MD: I2C1 Module Disable bit       1 = I2C1 module is disabled       0 = I2C1 module is disabled         Dit 7       I2C1MD: I2C1 Module Disable bit       1 = I2C1 module is disabled       0 = UART1 module Disable bit         Dit 6       Unimplemented: Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 7               |                     |                  |                        |                |                |           | bit                  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         Dit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is enabled         0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 14       T4MD: Timer6 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is disabled         Dit 12       T2MD: Timer1 Module Disable bit       1 = Timer2 module is disabled       0 = Timer2 module is disabled         Dit 11       T1MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer4 module is disabled         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 10       Unimplemented: Read as '0'       0       0         Dit 7       I2C1MD: I2C1 Module Disable bit       1 = I2C1 module is disabled       0 = I2C1 module is disabled         Dit 7       I2C1MD: I2C1 Module Disable bit       1 = I2C1 module is disabled       0 = UART1 module Disable bit         Dit 6       Unimplemented: Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Legend:             |                     |                  |                        |                |                |           |                      |

| m = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer5 module is disabled         bit 14       TAMD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer4 module is disabled       0 = Timer4 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer3 module is disabled       0 = Timer3 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer3 module is disabled       0 = Timer3 module is disabled         bit 12       T2MD: Timer2 Module Disable bit       1 = Timer3 module is disabled       0 = Timer3 module is disabled         bit 12       T2MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 11       T1MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 10       Unimplemented: Read as '0'       0       0       0         bit 8       Unimplemented: Read as '0'       0       1 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 7       I2C1MD: I2C1 Module Disable bit       1 = I2C1 module is disabled       0 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 6       Unimplemented: Read as '0'       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                   | le bit              | W = Writable     | bit                    | U = Unimplem   | ented bit, rea | ad as '0' |                      |

| bit 15       T5MD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled         0 = Timer5 module is disabled         1 = Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer4 module is disabled         0 = Timer4 module is disabled         0 = Timer4 module is disabled         0 = Timer3 module is disabled         0 = Timer3 module is disabled         0 = Timer3 module is enabled         0 = Timer3 module is disabled         0 = Timer1 module Disable bit         1 = Timer1 module is disabled         0 = WM1MD: PVM1 Module Disable bit         1 = PWM1 module is disabled         0 = PVWM1 module is disabled         0 = PVW1 module is disabled         0 = VIM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -n = Value a        | t POR               | '1' = Bit is set | t                      | •              |                |           | nown                 |

| 1 = Timer5 module is disabled         0 = Timer5 module is enabled         0 = Timer4 Module Disable bit         1 = Timer4 module is enabled         0 = Timer4 module is enabled         0 = Timer3 module is enabled         0 = Timer3 module is disable bit         1 = Timer3 module is disabled         0 = Timer2 module is enabled         0 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 module is disabled         0 = PWM1 MD: PWM1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is enabled         0 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module Disable bit         1 = UART1 module is disabled         0 = UART1 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                     |                  |                        |                |                |           |                      |

| 0 = Timer5 module is enabled         bit 14       T4MD: Timer4 Module Disable bit         1 = Timer4 module is disabled         0 = Timer3 Module Disable bit         1 = Timer3 module is enabled         0 = Timer4 module is disabled         0 = Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer2 module is enabled         0 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWM1 module is disabled         0 = I2C1 Module Disable bit         1 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 15              | T5MD: Time          | r5 Module Disa   | ble bit <sup>(1)</sup> |                |                |           |                      |

| bit 14       T4MD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer4 module is disabled         0 = Timer4 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 module is disabled         0 = PWM1 module is disabled         0 = I2C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled <t< td=""><td></td><td>1 = Timer5 n</td><td>nodule is disabl</td><td>ed</td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     | 1 = Timer5 n        | nodule is disabl | ed                     |                |                |           |                      |

| 1 = Timer4 module is disabled         0 = Timer4 module is enabled         0 = Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer3 module is enabled         0 = Timer3 module is enabled         0 = Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer2 module is enabled         0 = Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWM1 module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module Disable bit         1 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled         0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     | 0 <b>= Timer5 n</b> | nodule is enable | ed                     |                |                |           |                      |

| 0 = Timer4 module is enabled         bit 13       T3MD: Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is enabled         0 = Timer3 module is enabled         0 = Timer2 module is enabled         0 = Timer2 module is enabled         0 = Timer1 module is disabled         0 = PWM1MD: PVW1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PUM1 module is disabled         0 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled         0 = UART1 module is enabled         0 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14              |                     |                  |                        |                |                |           |                      |