Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp102-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

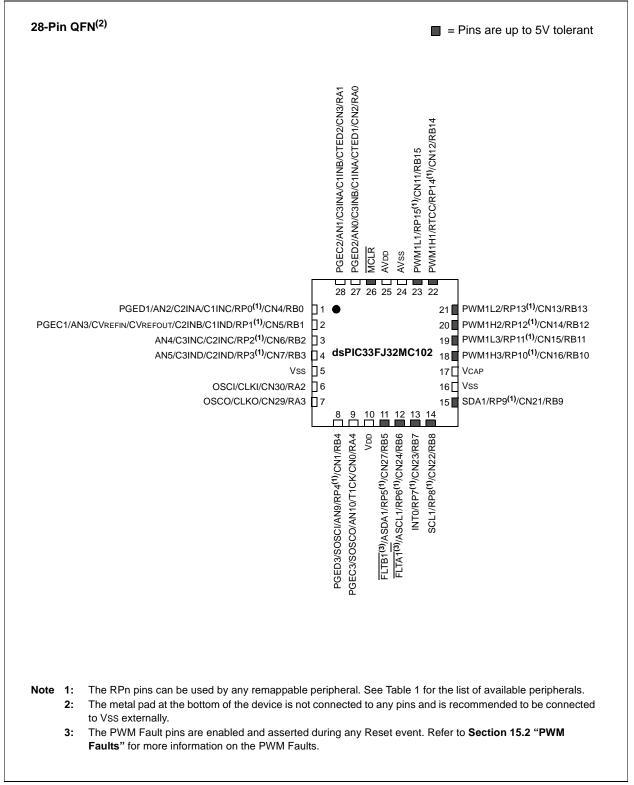

### Pin Diagrams (Continued)

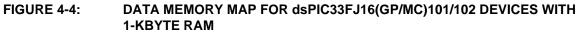

### 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY. N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All Effective Addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, although the implemented memory locations vary by device.

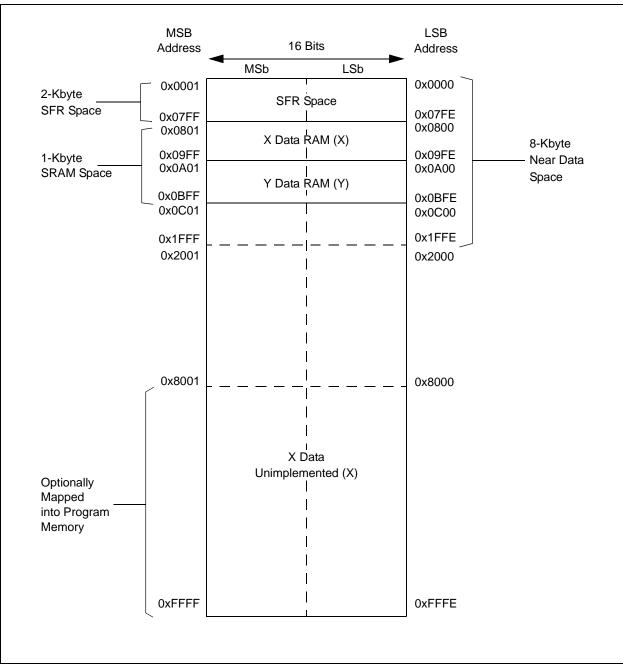

- 2. BOR: The on-chip voltage regulator has a BOR circuit that keeps the device in Reset until VDD crosses the VBOR threshold and the delay, TBOR, has elapsed. The delay, TBOR, ensures the voltage regulator output becomes stable.

- 3. **PWRT Timer:** The Power-up Timer continues to hold the processor in Reset for a specific period of time (TPWRT) after a BOR. The delay, TPWRT, ensures that the system power supplies have stabilized at the appropriate level for full-speed operation. After the delay, TPWRT, has elapsed, the SYSRST becomes inactive, which in turn, enables the selected oscillator to start generating clock cycles.

- 4. Oscillator Delay: The total delay for the clock to be ready for various clock source selections is given in Table 6-1. Refer to Section 8.0 "Oscillator Configuration" for more information.

- 5. When the oscillator clock is ready, the processor begins execution from location, 0x000000. The user application programs a GOTO instruction at the Reset address, which redirects program execution to the appropriate start-up routine.

- 6. The Fail-Safe Clock Monitor (FSCM), if enabled, begins to monitor the system clock when the system clock is ready and the delay, TFSCM, has elapsed.

| Symbol | Parameter                        | Value          |

|--------|----------------------------------|----------------|

| VPOR   | POR Threshold                    | 1.8V nominal   |

| TPOR   | POR Extension Time               | 30 μs maximum  |

| VBOR   | BOR Threshold                    | 2.5V nominal   |

| TBOR   | BOR Extension Time               | 100 μs maximum |

| TPWRT  | Power-up Time<br>Delay           | 64 ms nominal  |

| TFSCM  | Fail-Safe Clock<br>Monitor Delay | 900 μs maximum |

| TABLE 6-2: | <b>OSCILLATOR PARAMETER</b> | 2S |

|------------|-----------------------------|----|

|            |                             | ς, |

| Note: | When the device exits the Reset condition<br>(begins normal operation), the device<br>operating parameters (voltage, frequency,<br>temperature, etc.) must be within their<br>operating ranges; otherwise, the device<br>may not function correctly. The user appli-<br>cation must ensure that the delay between<br>the time power is first applied, and the time<br>SYSRST becomes inactive, is long<br>enough to get all operating parameters |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | enough to get all operating parameters within specification.                                                                                                                                                                                                                                                                                                                                                                                     |

| REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 |                                                                                                |                                  |                   |                  |                  |                 |        |  |  |  |

|------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------|-------------------|------------------|------------------|-----------------|--------|--|--|--|

| U-0                                                  | U-0                                                                                            | R/W-0                            | R/W-0             | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |

| —                                                    | —                                                                                              | AD1IF                            | U1TXIF            | U1RXIF           | SPI1IF           | SPI1EIF         | T3IF   |  |  |  |

| pit 15                                               |                                                                                                |                                  |                   |                  |                  |                 | bi     |  |  |  |

| R/W-0                                                | R/W-0                                                                                          | R/W-0                            | U-0               | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |

| T2IF                                                 | OC2IF                                                                                          | IC2IF                            | _                 | T1IF             | OC1IF            | IC1IF           | INTOIF |  |  |  |

| bit 7                                                |                                                                                                |                                  |                   |                  |                  |                 | bi     |  |  |  |

|                                                      |                                                                                                |                                  |                   |                  |                  |                 |        |  |  |  |

| Legend:                                              | - h:4                                                                                          |                                  | h.:4              |                  |                  |                 |        |  |  |  |

| R = Readable<br>-n = Value at                        |                                                                                                | W = Writable<br>'1' = Bit is se  |                   | 0 = Unimplem     | nented bit, read |                 |        |  |  |  |

| -n = value at                                        | POR                                                                                            | I = DILIS SE                     | l                 |                  | areu             | x = Bit is unkn | own    |  |  |  |

| bit 15-14                                            | Unimplemen                                                                                     | ted: Read as                     | 'O'               |                  |                  |                 |        |  |  |  |

| bit 13                                               | AD1IF: ADC1                                                                                    | Conversion (                     | Complete Interi   | rupt Flag Status | s bit            |                 |        |  |  |  |

|                                                      |                                                                                                | request has or                   |                   |                  |                  |                 |        |  |  |  |

|                                                      | -                                                                                              | request has no                   |                   | <b>.</b>         |                  |                 |        |  |  |  |

| bit 12                                               |                                                                                                |                                  | er Interrupt Flag | g Status bit     |                  |                 |        |  |  |  |

|                                                      | •                                                                                              | request has or<br>request has no |                   |                  |                  |                 |        |  |  |  |

| bit 11                                               | -                                                                                              | -                                | nterrupt Flag S   | Status bit       |                  |                 |        |  |  |  |

|                                                      |                                                                                                | request has or                   |                   |                  |                  |                 |        |  |  |  |

|                                                      | •                                                                                              | request has no                   |                   |                  |                  |                 |        |  |  |  |

| bit 10                                               |                                                                                                | -                                | ot Flag Status k  | bit              |                  |                 |        |  |  |  |

|                                                      | •                                                                                              | request has oc<br>request has no |                   |                  |                  |                 |        |  |  |  |

| bit 9                                                | -                                                                                              | -                                | pt Flag Status    | bit              |                  |                 |        |  |  |  |

|                                                      |                                                                                                | request has or                   |                   |                  |                  |                 |        |  |  |  |

|                                                      | -                                                                                              | request has no                   |                   |                  |                  |                 |        |  |  |  |

| bit 8                                                |                                                                                                | Interrupt Flag                   |                   |                  |                  |                 |        |  |  |  |

|                                                      |                                                                                                | request has ou<br>request has no |                   |                  |                  |                 |        |  |  |  |

| bit 7                                                | •                                                                                              | Interrupt Flag                   |                   |                  |                  |                 |        |  |  |  |

|                                                      |                                                                                                | request has or                   |                   |                  |                  |                 |        |  |  |  |

|                                                      | 0 = Interrupt i                                                                                | request has no                   | ot occurred       |                  |                  |                 |        |  |  |  |

| bit 6                                                | -                                                                                              | -                                |                   | upt Flag Status  | bit              |                 |        |  |  |  |

|                                                      | •                                                                                              | request has or<br>request has no |                   |                  |                  |                 |        |  |  |  |

| bit 5                                                | -                                                                                              | -                                |                   | -lag Status bit  |                  |                 |        |  |  |  |

|                                                      | IC2IF: Input Capture Channel 2 Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                  |                   |                  |                  |                 |        |  |  |  |

|                                                      |                                                                                                | request has no                   |                   |                  |                  |                 |        |  |  |  |

| bit 4                                                | -                                                                                              | ted: Read as                     |                   |                  |                  |                 |        |  |  |  |

| bit 3                                                | T1IF: Timer1                                                                                   | Interrupt Flag                   | Status bit        |                  |                  |                 |        |  |  |  |

|                                                      |                                                                                                | request has or                   |                   |                  |                  |                 |        |  |  |  |

#### -. חוור - - -• •

### 10.4 Peripheral Pin Select (PPS)

Peripheral Pin Select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral Pin Select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

### 10.4.1 AVAILABLE PINS

The Peripheral Pin Select feature is used with a range of up to 16 pins. The number of available pins depends on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

### 10.4.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of Special Function Registers: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

### 10.4.2.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-10). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

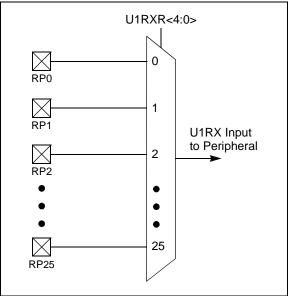

Figure 10-2 Illustrates remappable pin selection for U1RX input.

Note: For input mapping only, the Peripheral Pin Select (PPS) functionality does not have priority over the TRISx settings. Therefore, when configuring the RPx pin for input, the corresponding bit in the TRISx register must also be configured for input (i.e., set to '1').

### FIGURE 10-2: REMAPPABLE MUX INPUT FOR U1RX

# 12.3 Timer2/3 and Timer4/5 Control Registers

| _             |                                                                                        |                  |                |                  |                 |                 |       |  |  |  |

|---------------|----------------------------------------------------------------------------------------|------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|

| R/W-0         | U-0                                                                                    | R/W-0            | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |

| TON           |                                                                                        | TSIDL            | _              |                  | —               |                 | _     |  |  |  |

| bit 15        |                                                                                        |                  |                |                  |                 |                 | bit 8 |  |  |  |

|               |                                                                                        |                  |                |                  |                 |                 |       |  |  |  |

| U-0           | R/W-0                                                                                  | R/W-0            | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |

| _             | TGATE                                                                                  | TCKPS1           | TCKPS0         | T32              | —               | TCS             | —     |  |  |  |

| bit 7         |                                                                                        |                  |                |                  |                 |                 | bit C |  |  |  |

|               |                                                                                        |                  |                |                  |                 |                 |       |  |  |  |

| Legend:       |                                                                                        |                  |                |                  |                 |                 |       |  |  |  |

| R = Readabl   | e bit                                                                                  | W = Writable I   | oit            | U = Unimpler     | mented bit, rea | ad as '0'       |       |  |  |  |

| -n = Value at | POR                                                                                    | '1' = Bit is set |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |

|               |                                                                                        |                  |                |                  |                 |                 |       |  |  |  |

| bit 15        | TON: Timer2                                                                            | On bit           |                |                  |                 |                 |       |  |  |  |

|               | When T32 = 2                                                                           |                  |                |                  |                 |                 |       |  |  |  |

|               | 1 = Starts 32-                                                                         |                  |                |                  |                 |                 |       |  |  |  |

|               | 0 = Stops 32-                                                                          |                  |                |                  |                 |                 |       |  |  |  |

|               | $\frac{\text{When T32} = 0}{1 = \text{Starts 16}}$                                     |                  |                |                  |                 |                 |       |  |  |  |

|               | 0 = Stops 16-                                                                          |                  |                |                  |                 |                 |       |  |  |  |

| bit 14        | Unimplemen                                                                             | ted: Read as '   | )'             |                  |                 |                 |       |  |  |  |

| bit 13        | TSIDL: Timer                                                                           | 2 Stop in Idle M | lode bit       |                  |                 |                 |       |  |  |  |

|               |                                                                                        | ues module ope   |                |                  | lle mode        |                 |       |  |  |  |

|               |                                                                                        | s module opera   |                | de               |                 |                 |       |  |  |  |

| bit 12-7      | Unimplemen                                                                             | ted: Read as '0  | )'             |                  |                 |                 |       |  |  |  |

| bit 6         |                                                                                        | er2 Gated Time   | Accumulation   | Enable bit       |                 |                 |       |  |  |  |

|               | When TCS = 1:<br>This hit is imported                                                  |                  |                |                  |                 |                 |       |  |  |  |

|               | This bit is ignored.<br>When TCS = 0:                                                  |                  |                |                  |                 |                 |       |  |  |  |

|               | $\frac{\text{when } 1 \text{ CS} = 0}{1 \text{ = Gated time accumulation is enabled}}$ |                  |                |                  |                 |                 |       |  |  |  |

|               | 0 = Gated time accumulation is disabled                                                |                  |                |                  |                 |                 |       |  |  |  |

| bit 5-4       | TCKPS<1:0>                                                                             | : Timer2 Input   | Clock Prescale | e Select bits    |                 |                 |       |  |  |  |

|               | 11 <b>= 1:256</b>                                                                      |                  |                |                  |                 |                 |       |  |  |  |

|               | 10 = 1:64                                                                              |                  |                |                  |                 |                 |       |  |  |  |

|               | 01 = 1:8<br>00 = 1:1                                                                   |                  |                |                  |                 |                 |       |  |  |  |

| bit 3         |                                                                                        | imer Mode Sele   | ct bit         |                  |                 |                 |       |  |  |  |

| Sit 0         |                                                                                        | nd Timer3 form   |                | timer            |                 |                 |       |  |  |  |

|               |                                                                                        | nd Timer3 act a  |                |                  |                 |                 |       |  |  |  |

| bit 2         | Unimplemen                                                                             | ted: Read as '   | )'             |                  |                 |                 |       |  |  |  |

| bit 1         | TCS: Timer2                                                                            | Clock Source S   | elect bit      |                  |                 |                 |       |  |  |  |

|               |                                                                                        | clock from pin,  | Γ2CK (on the r | ising edge)      |                 |                 |       |  |  |  |

|               | 0 = Internal cl                                                                        |                  |                |                  |                 |                 |       |  |  |  |

| bit 0         | Unimplemen                                                                             | ted: Read as '0  | ) <b>'</b>     |                  |                 |                 |       |  |  |  |

### REGISTER 12-1: T2CON: TIMER2 CONTROL REGISTER

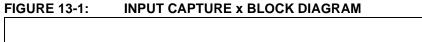

### 13.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70198) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices support up to three input capture channels. The input capture module captures the 16-bit value of the selected Time Base register when an event occurs on the ICx pin. The events that cause a capture event are listed below in three categories:

- 1. Simple Capture Event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- 2. Capture timer value on every edge (rising and falling).

- 3. Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values:

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Use of input capture to provide additional sources of external interrupts

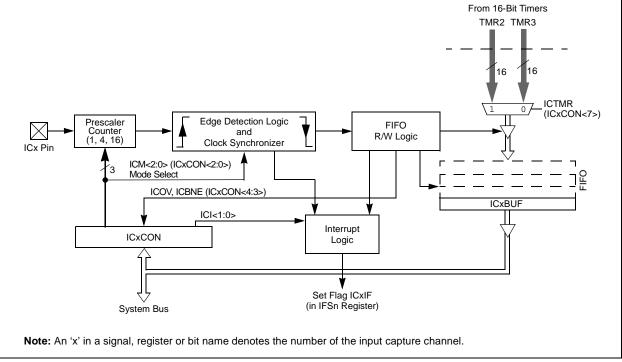

### 14.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70209) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The output compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Output Compare Control register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

The output compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault Protection

- PWM mode with Fault Protection

### FIGURE 14-1: OUTPUT COMPARE x MODULE BLOCK DIAGRAM

# EXAMPLE 15-1: ASSEMBLY CODE FOR WRITE-PROTECTED REGISTER UNLOCK AND FAULT CLEARING SEQUENCE

|                                                                             | lled high externally in order to clear and disable the Fault<br>register requires unlock sequence                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0x4321,w11 mov #0x0000,w0 mov w10, PWM1KEY mov w11, PWM1KEY</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of P1FLTACON register in w0<br/>; Write first unlock key to PWM1KEY register<br/>; Write second unlock key to PWM1KEY register<br/>; Write desired value to P1FLTACON register</pre> |

|                                                                             | lled high externally in order to clear and disable the Fault<br>register requires unlock sequence                                                                                                                                                                                                       |

| <pre>mov #0x4321,w11 mov #0x0000,w0 mov w10, PWM1KEY mov w11, PWM1KEY</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of P1FLTBCON register in w0<br/>; Write first unlock key to PWM1KEY register<br/>; Write second unlock key to PWM1KEY register<br/>; Write desired value to P1FLTBCON register</pre> |

| ; Enable all PWMs using<br>; Writing to PWM1CON1 r                          | g PWM1CON1 register<br>register requires unlock sequence                                                                                                                                                                                                                                                |

| <pre>mov #0x4321,w11 mov #0x0077,w0 mov w10, PWM1KEY mov w11, PWM1KEY</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of PWM1CON1 register in w0<br/>; Write first unlock key to PWM1KEY register<br/>; Write second unlock key to PWM1KEY register<br/>; Write desired value to PWM1CON1 register</pre>   |

# EXAMPLE 15-2: C CODE FOR WRITE-PROTECTED REGISTER UNLOCK AND FAULT CLEARING SEQUENCE

// FLTAl pin must be pulled high externally in order to clear and disable the Fault // Writing to PIFLTACON register requires unlock sequence // Use builtin function to write 0x0000 to PIFLTACON register \_\_builtin\_write\_PWMSFR(&PIFLTACON, 0x0000, &PWM1KEY); // FLTBl pin must be pulled high externally in order to clear and disable the Fault // Writing to PIFLTBCON register requires unlock sequence // Use builtin function to write 0x0000 to PIFLTBCON register \_\_builtin\_write\_PWMSFR(&PIFLTBCON, 0x0000, &PWM1KEY); // Enable all PWMs using PWM1CON1 register // Writing to PWM1CON1 register requires unlock sequence // Use builtin function to write 0x0077 to PWM1CON1 register \_\_builtin\_write\_PWMSFR(&PWM1CON1, 0x0077, &PWM1KEY);

| REGISTER            | 16-2: SPIXC                      | ON1: SPIx C                                   | ONTROL RE            | EGISTER 1                              |                      |                                       |                      |

|---------------------|----------------------------------|-----------------------------------------------|----------------------|----------------------------------------|----------------------|---------------------------------------|----------------------|

| U-0                 | U-0                              | U-0                                           | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                                 | R/W-0                |

| _                   | —                                | —                                             | DISSCK               | DISSDO                                 | MODE16               | SMP                                   | CKE <sup>(1)</sup>   |

| bit 15              |                                  |                                               |                      |                                        |                      |                                       | bit 8                |

| R/W-0               | R/W-0                            | R/W-0                                         | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                                 | R/W-0                |

| SSEN <sup>(2)</sup> | CKP                              | MSTEN                                         | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup>                   | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup>                  | PPRE0 <sup>(3)</sup> |

| bit 7               |                                  | 1                                             |                      | 1                                      |                      |                                       | bit (                |

| Legend:             |                                  |                                               |                      |                                        |                      |                                       |                      |

| R = Readab          | le bit                           | W = Writable                                  | bit                  | U = Unimplen                           | nented bit, read     | l as '0'                              |                      |

| -n = Value a        | t POR                            | '1' = Bit is set                              |                      | '0' = Bit is cle                       | ared                 | x = Bit is unkr                       | nown                 |

| bit 15-13           | Unimplemen                       | ted: Read as '                                | 0'                   |                                        |                      |                                       |                      |

| bit 12              | DISSCK: Disa                     | able SCKx pin                                 | bit (SPI Maste       | r modes only)                          |                      |                                       |                      |

|                     |                                  | PI clock is disa                              | •                    | tions as I/O                           |                      |                                       |                      |

|                     |                                  | PI clock is ena                               |                      |                                        |                      |                                       |                      |

| bit 11              |                                  | able SDOx pin                                 |                      |                                        |                      |                                       |                      |

|                     |                                  | is not used by is controlled b                |                      | oin functions as                       | s I/O                |                                       |                      |

| pit 10              | -                                | ord/Byte Comm                                 | -                    | ect bit                                |                      |                                       |                      |

|                     | 1 = Communi                      | cation is word-                               | wide (16 bits)       |                                        |                      |                                       |                      |

|                     | 0 = Communi                      | cation is byte-                               | wide (8 bits)        |                                        |                      |                                       |                      |

| bit 9               | SMP: SPIx D                      | ata Input Samp                                | ole Phase bit        |                                        |                      |                                       |                      |

|                     |                                  | <u>:</u><br>a sampled at er<br>a sampled at m |                      |                                        |                      |                                       |                      |

|                     | Slave mode:                      | -                                             |                      | n Slave mode.                          |                      |                                       |                      |

| bit 8               | CKE: Clock E                     | dge Select bit                                | (1)                  |                                        |                      |                                       |                      |

|                     |                                  |                                               |                      |                                        |                      | lle clock state (<br>ve clock state ( |                      |

| bit 7               | SSEN: SPIX S                     | Slave Select E                                | nable bit (Slav      | e mode) <sup>(2)</sup>                 |                      |                                       |                      |

|                     |                                  | s used for Slav<br>s not used by th           |                      | is controlled b                        | by port function     |                                       |                      |

| oit 6               | CKP: Clock F                     | Polarity Select I                             | oit                  |                                        |                      |                                       |                      |

|                     |                                  |                                               |                      | ve state is a lov<br>e state is a high |                      |                                       |                      |

| bit 5               | MSTEN: Mas                       | ter Mode Enab                                 | ole bit              |                                        |                      |                                       |                      |

|                     | 1 = Master m<br>0 = Slave mo     |                                               |                      |                                        |                      |                                       |                      |

|                     | he CKE bit is not<br>FRMEN = 1). | used in the Fra                               | amed SPI moo         | des. Program ti                        | his bit to '0' for   | the Framed SP                         | 'l modes             |

|                     | his bit must be cl               |                                               |                      |                                        |                      |                                       |                      |

| 3: D                | o not set both pri               | mary and seco                                 | ondary prescal       | ers to a value o                       | of 1:1.              |                                       |                      |

### REGISTER 16-2: SPIxCON1: SPIx CONTROL REGISTER 1

### 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

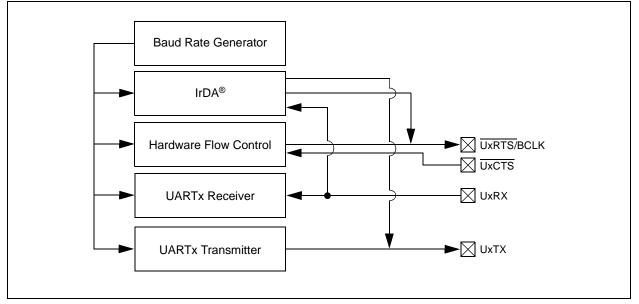

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 6 bps at 16x mode at 16 MIPS

- Baud Rates Ranging from 4 Mbps to 24.4 bps at 4x mode at 16 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- Transmit and Receive Interrupts

- A Separate Interrupt for all UART Error Conditions

- Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA® Support

A simplified block diagram of the UART module is shown in Figure 18-1. The UART module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

### FIGURE 18-1: UARTX SIMPLIFIED BLOCK DIAGRAM

| REGISTER                     | 19-4: ADICI                                                                                                                                                                  | 15123: ADC1                                                                         |                | ANNEL $1, 2,$    | SELECT RE        | GIJIER             |             |  |  |  |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------|------------------|------------------|--------------------|-------------|--|--|--|--|--|

| U-0                          | U-0                                                                                                                                                                          | U-0                                                                                 | U-0            | U-0              | R/W-0            | R/W-0              | R/W-0       |  |  |  |  |  |

| _                            | —                                                                                                                                                                            | —                                                                                   | —              | —                | CH123NB1         | CH123NB0           | CH123SB     |  |  |  |  |  |

| bit 15                       |                                                                                                                                                                              |                                                                                     |                |                  |                  |                    | bit 8       |  |  |  |  |  |

| U-0                          | U-0                                                                                                                                                                          | U-0                                                                                 | U-0            | U-0              | R/W-0            | R/W-0              | R/W-0       |  |  |  |  |  |

| -                            | _                                                                                                                                                                            | _                                                                                   | _              | _                | CH123NA1         | CH123NA0           | CH123SA     |  |  |  |  |  |

| bit 7                        |                                                                                                                                                                              |                                                                                     |                |                  | 0111201011       | 0111201010         | bit (       |  |  |  |  |  |

|                              |                                                                                                                                                                              |                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

| <b>Legend:</b><br>R = Readab | la hit                                                                                                                                                                       | W = Writable b                                                                      | 4              | LI – Unimplo     | mented bit, read | d oo 'O'           |             |  |  |  |  |  |

|                              |                                                                                                                                                                              |                                                                                     | L              | -                |                  |                    |             |  |  |  |  |  |

| -n = Value a                 | IT POR                                                                                                                                                                       | '1' = Bit is set                                                                    |                | '0' = Bit is cle | eared            | x = Bit is unkr    | nown        |  |  |  |  |  |

| bit 15-11                    | Unimplement                                                                                                                                                                  | ted: Read as '0'                                                                    |                |                  |                  |                    |             |  |  |  |  |  |

|                              | -                                                                                                                                                                            |                                                                                     |                |                  | er Comple D hit  | _                  |             |  |  |  |  |  |

| bit 10-9                     |                                                                                                                                                                              | <b>0&gt;:</b> Channel 1, 2                                                          | -              | -                | or Sample B bit  | S                  |             |  |  |  |  |  |

|                              |                                                                                                                                                                              | dsPIC33FJ16(GP/MC)101/102 Devices Only:                                             |                |                  |                  |                    |             |  |  |  |  |  |

|                              | 11 = Reserve                                                                                                                                                                 | 11 = Reserved                                                                       |                |                  |                  |                    |             |  |  |  |  |  |

|                              |                                                                                                                                                                              | u<br>I2, CH3 negative                                                               | a inpute are / |                  |                  |                    |             |  |  |  |  |  |

|                              |                                                                                                                                                                              | 2(GP/MC)101/10                                                                      | -              |                  |                  |                    |             |  |  |  |  |  |

|                              |                                                                                                                                                                              | ative input is AN                                                                   |                |                  |                  | utive input is not | t connected |  |  |  |  |  |

|                              | 10 = Reserve                                                                                                                                                                 |                                                                                     | is, criz nega  |                  | anto, ens nega   | live input is not  | Connecteu   |  |  |  |  |  |

|                              |                                                                                                                                                                              |                                                                                     | e inputs are A | AVss             |                  |                    |             |  |  |  |  |  |

|                              |                                                                                                                                                                              | CH1, CH2, CH3 negative inputs are AVss<br>C33FJ32(GP/MC)104 Devices Only:           |                |                  |                  |                    |             |  |  |  |  |  |

|                              |                                                                                                                                                                              | = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11 |                |                  |                  |                    |             |  |  |  |  |  |

|                              | 10 = CH1 negative input is ANS, CH2 negative input is AN7, CH3 negative input is AN8<br>10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8 |                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              | 0x = CH1, CH2, CH3 negative inputs are AVss                                                                                                                                  |                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

| bit 8                        | CH123SB: Ch                                                                                                                                                                  | nannel 1, 2, 3 Po                                                                   | sitive Input S | Select for Sam   | ple B bit        |                    |             |  |  |  |  |  |

|                              | dsPIC33FJXX(GP/MC)101 Devices Only:                                                                                                                                          |                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              | 1 = CH1 positive input is AN3, CH2 and CH3 positive inputs are not connected                                                                                                 |                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              | 0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2                                                                                          |                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              | All Other Devices:                                                                                                                                                           |                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              | 1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5                                                                                          |                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              | 0 = CH1 posit                                                                                                                                                                | ive input is AN0                                                                    | , CH2 positiv  | e input is AN1   | , CH3 positive i | nput is AN2        |             |  |  |  |  |  |

| bit 7-3                      | Unimplemen                                                                                                                                                                   | ted: Read as '0'                                                                    |                |                  |                  |                    |             |  |  |  |  |  |

| bit 2-1                      | CH123NA<1:                                                                                                                                                                   | <b>0&gt;:</b> Channel 1, 2                                                          | 2, 3 Negative  | Input Select f   | or Sample A bit  | S                  |             |  |  |  |  |  |

|                              |                                                                                                                                                                              | 10-9> for the ava                                                                   | -              | -                |                  |                    |             |  |  |  |  |  |

| bit 0                        |                                                                                                                                                                              | nannel 1, 2, 3 Po                                                                   |                | -                | nle A hit        |                    |             |  |  |  |  |  |

| UIL U                        |                                                                                                                                                                              |                                                                                     | •              |                  |                  |                    |             |  |  |  |  |  |

|                              | Relief to bit 8                                                                                                                                                              | for the available                                                                   | seuings.       |                  |                  |                    |             |  |  |  |  |  |

### REGISTER 19-4: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| DC CHARAC                                                               | TERISTICS              |                         | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |             |        |                                                |  |  |  |  |  |

|-------------------------------------------------------------------------|------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|------------------------------------------------|--|--|--|--|--|

| Parameter<br>No.                                                        | Typical <sup>(1)</sup> | Мах                     | Units                                                                                                                                                                                                                                                                              |             |        | Conditions                                     |  |  |  |  |  |

| Power-Down Current (IPD) <sup>(2)</sup> – dsPIC33FJ16(GP/MC)10X Devices |                        |                         |                                                                                                                                                                                                                                                                                    |             |        |                                                |  |  |  |  |  |

| DC60d                                                                   | 27                     | 250                     | μA                                                                                                                                                                                                                                                                                 | -40°C       |        |                                                |  |  |  |  |  |

| DC60a                                                                   | 32                     | 250                     | μA                                                                                                                                                                                                                                                                                 | +25°C       | 2.21/  | Base Power-Down Current <sup>(3,4)</sup>       |  |  |  |  |  |

| DC60b                                                                   | 43                     | 250                     | μA                                                                                                                                                                                                                                                                                 | +85°C       | - 3.3V | Base Power-Down Current                        |  |  |  |  |  |

| DC60c                                                                   | 150                    | 500                     | μA                                                                                                                                                                                                                                                                                 | +125°C      |        |                                                |  |  |  |  |  |

| DC61d                                                                   | 420                    | 600                     | μA                                                                                                                                                                                                                                                                                 | -40°C       |        |                                                |  |  |  |  |  |

| DC61a                                                                   | 420                    | 600                     | μA                                                                                                                                                                                                                                                                                 | +25°C       | 3.3∨   | Watchdog Timer Current: ∆IwDT <sup>(3,5)</sup> |  |  |  |  |  |

| DC61b                                                                   | 530                    | 750                     | μA                                                                                                                                                                                                                                                                                 | +85°C       | 3.3V   |                                                |  |  |  |  |  |

| DC61c                                                                   | 620                    | 900                     | μA                                                                                                                                                                                                                                                                                 | +125°C      |        |                                                |  |  |  |  |  |

| Power-Down                                                              | Current (IPD)          | <sup>(2)</sup> – dsPIC3 | 3FJ32(GP/M                                                                                                                                                                                                                                                                         | C)10X Devic | es     |                                                |  |  |  |  |  |

| DC60d                                                                   | 27                     | 250                     | μA                                                                                                                                                                                                                                                                                 | -40°C       |        |                                                |  |  |  |  |  |

| DC60a                                                                   | 32                     | 250                     | μA                                                                                                                                                                                                                                                                                 | +25°C       | 3.3V   | Base Power-Down Current <sup>(3,4)</sup>       |  |  |  |  |  |

| DC60b                                                                   | 43                     | 250                     | μA                                                                                                                                                                                                                                                                                 | +85°C       | 3.3V   | Base Power-Down Current                        |  |  |  |  |  |

| DC60c                                                                   | 150                    | 500                     | μA                                                                                                                                                                                                                                                                                 | +125°C      |        |                                                |  |  |  |  |  |

| DC61d                                                                   | 420                    | 600                     | μA                                                                                                                                                                                                                                                                                 | -40°C       |        |                                                |  |  |  |  |  |

| DC61a                                                                   | 420                    | 600                     | μA                                                                                                                                                                                                                                                                                 | +25°C       | 3.3∨   | Watchdog Timer Current: ∆IwDT <sup>(3,5)</sup> |  |  |  |  |  |

| DC61b                                                                   | 530                    | 750                     | μA                                                                                                                                                                                                                                                                                 | +85°C       | 3.3V   |                                                |  |  |  |  |  |

| DC61c                                                                   | 620                    | 900                     | μA                                                                                                                                                                                                                                                                                 | +125°C      |        |                                                |  |  |  |  |  |

### TABLE 26-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** Data in the Typical column is at 3.3V, +25°C unless otherwise stated.

2: IPD (Sleep) current is measured as follows:

- CPU core is off, oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- External Secondary Oscillator (SOSC) is disabled (i.e., SOSCO and SOSCI pins are configured as digital I/O inputs)

- · All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all ones)

- VREGS bit (RCON<8>) = 1 (i.e., core regulator is set to stand-by while the device is in Sleep mode)

- On applicable devices, RTCC is disabled, plus the VREGS bit (RCON<8>) = 1

- **3:** The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: These currents are measured on the device containing the most memory in this family.

- 5: These parameters are characterized, but not tested in manufacturing.

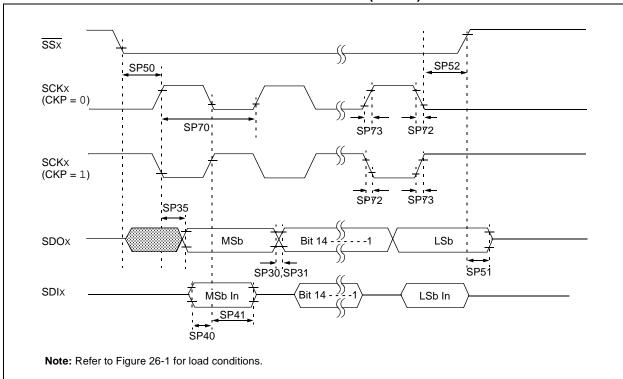

### FIGURE 26-17: SPIx SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ16(GP/MC)10X

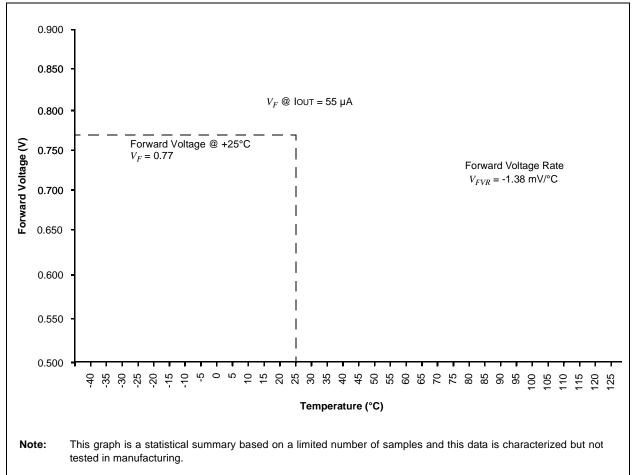

### FIGURE 26-33: FORWARD VOLTAGE VERSUS TEMPERATURE

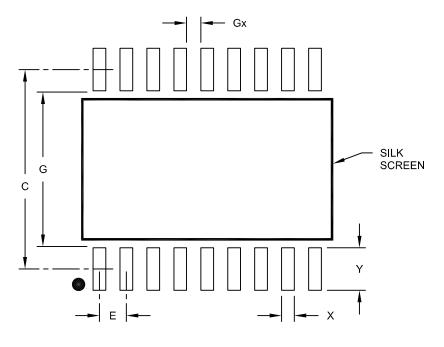

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

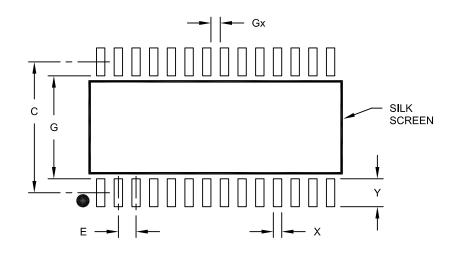

### RECOMMENDED LAND PATTERN

|                       | Units  | MILLIMETERS |      |      |  |

|-----------------------|--------|-------------|------|------|--|

| Dimension             | Limits | MIN         | NOM  | MAX  |  |

| Contact Pitch         | E      | 1.27 BSC    |      |      |  |

| Contact Pad Spacing   | С      |             | 9.40 |      |  |

| Contact Pad Width     | Х      |             |      | 0.60 |  |

| Contact Pad Length    | Y      |             |      | 2.00 |  |

| Distance Between Pads | Gx     | 0.67        |      |      |  |

| Distance Between Pads | G      | 7.40        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A

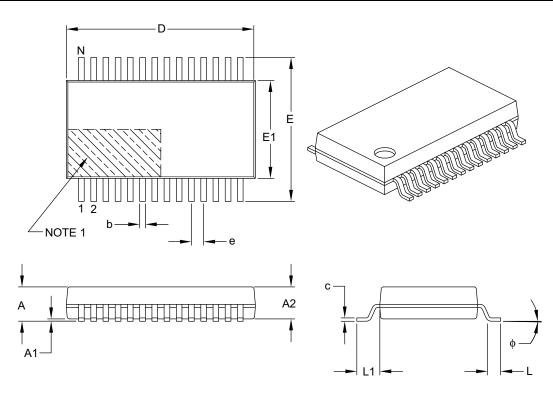

### 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     |          |          |       |  |

|--------------------------|-----------|----------|----------|-------|--|