Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

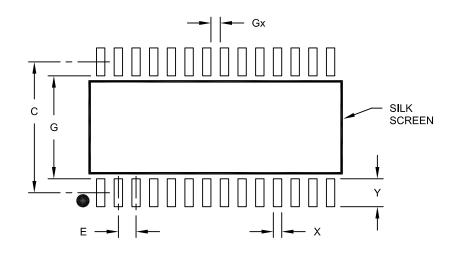

| Package / Case             | 36-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 36-VTLA (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp102-e-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 PRODUCT FAMILIES

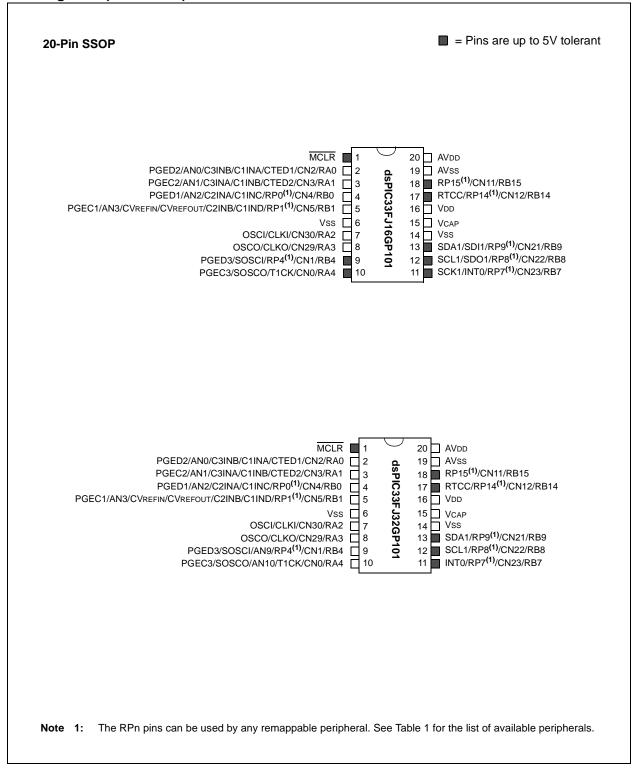

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. The following pages show their pinout diagrams.

|                  |      | rte)                  |              |                 | Rem                           | appa          | ble l          | Perip | herals                             | 5   | М                 |            | Ŋ                    |      |      |             |      |          |                                 |

|------------------|------|-----------------------|--------------|-----------------|-------------------------------|---------------|----------------|-------|------------------------------------|-----|-------------------|------------|----------------------|------|------|-------------|------|----------|---------------------------------|

| Device           | Pins | Program Flash (Kbyte) | RAM (Kbytes) | Remappable Pins | 16-bit Timer <sup>(1,2)</sup> | Input Capture | Output Compare | UART  | External Interrupts <sup>(3)</sup> | SPI | Motor Control PWM | PWM Faults | 10-Bit, 1.1 Msps ADC | RTCC | I²C™ | Comparators | CTMU | I/O Pins | Packages                        |

| dsPIC33FJ16GP101 | 18   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 13       | PDIP,<br>SOIC                   |

|                  | 20   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | SSOP                            |

| dsPIC33FJ16GP102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | _          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

| dsPIC33FJ16MC101 | 20   | 16                    | 1            | 10              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 1          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | PDIP,<br>SOIC,<br>SSOP          |

| dsPIC33FJ16MC102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

#### TABLE 1:dsPIC33FJ16(GP/MC)101/102 DEVICE FEATURES

**Note 1:** Two out of three timers are remappable.

2: One pair can be combined to create one 32-bit timer.

**3**: Two out of three interrupts are remappable.

#### Pin Diagrams (Continued)

© 2011-2014 Microchip Technology Inc.

#### TABLE 4-9: INPUT CAPTURE REGISTER MAP

| SFR<br>Addr | Bit 15                                       | Bit 14                             | Bit 13                                            | Bit 12                                                                                                                                                                                                       | Bit 11                                                                                                                                                                                                                                                                                                                                                                       | Bit 10                                                                                         | Bit 9                                                                                                         | Bit 8                                                                                                                       | Bit 7                                                                                                                                     | Bit 6                                                                                                                                                   | Bit 5                                                                                                                                                                 | Bit 4                                                                                                                                                                               | Bit 3                                                                                                                                                                                             | Bit 2                                                                                                                                                                                                           | Bit 1                                                                                                                                                                                                          | Bit 0                                                                                                                                                                                                                                       | All Resets                                                                                                                                                                                                                                                |

|-------------|----------------------------------------------|------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0140        |                                              |                                    |                                                   |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                |                                                                                                               | Input Cap                                                                                                                   | ture 1 Regis                                                                                                                              | ster                                                                                                                                                    |                                                                                                                                                                       |                                                                                                                                                                                     |                                                                                                                                                                                                   |                                                                                                                                                                                                                 |                                                                                                                                                                                                                |                                                                                                                                                                                                                                             | xxxx                                                                                                                                                                                                                                                      |

| 0142        | —                                            | —                                  | ICSIDL                                            | —                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                              | —                                                                                                             | —                                                                                                                           | ICTMR                                                                                                                                     | ICI1                                                                                                                                                    | ICI0                                                                                                                                                                  | ICOV                                                                                                                                                                                | ICBNE                                                                                                                                                                                             | ICM2                                                                                                                                                                                                            | ICM1                                                                                                                                                                                                           | ICM0                                                                                                                                                                                                                                        | 0000                                                                                                                                                                                                                                                      |

| 0144        |                                              |                                    |                                                   |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                |                                                                                                               | Input Cap                                                                                                                   | ture 2 Regis                                                                                                                              | ster                                                                                                                                                    |                                                                                                                                                                       |                                                                                                                                                                                     |                                                                                                                                                                                                   |                                                                                                                                                                                                                 |                                                                                                                                                                                                                |                                                                                                                                                                                                                                             | XXXX                                                                                                                                                                                                                                                      |

| 0146        | —                                            | —                                  | ICSIDL                                            | —                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                              | —                                                                                                             | —                                                                                                                           | ICTMR                                                                                                                                     | ICI1                                                                                                                                                    | ICI0                                                                                                                                                                  | ICOV                                                                                                                                                                                | ICBNE                                                                                                                                                                                             | ICM2                                                                                                                                                                                                            | ICM1                                                                                                                                                                                                           | ICM0                                                                                                                                                                                                                                        | 0000                                                                                                                                                                                                                                                      |

| 0148        |                                              |                                    |                                                   |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                |                                                                                                               | Input Cap                                                                                                                   | ture 3 Regis                                                                                                                              | ster                                                                                                                                                    |                                                                                                                                                                       |                                                                                                                                                                                     |                                                                                                                                                                                                   |                                                                                                                                                                                                                 |                                                                                                                                                                                                                |                                                                                                                                                                                                                                             | XXXX                                                                                                                                                                                                                                                      |

| 014A        |                                              | _                                  | ICSIDL                                            | _                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                              | _                                                                                                             |                                                                                                                             | ICTMR                                                                                                                                     | ICI1                                                                                                                                                    | ICI0                                                                                                                                                                  | ICOV                                                                                                                                                                                | ICBNE                                                                                                                                                                                             | ICM2                                                                                                                                                                                                            | ICM1                                                                                                                                                                                                           | ICM0                                                                                                                                                                                                                                        | 0000                                                                                                                                                                                                                                                      |

|             | Addr<br>0140<br>0142<br>0144<br>0146<br>0148 | Addr         Bit 15           0140 | Addr         Bit 15         Bit 14           0140 | Addr         Bit 15         Bit 14         Bit 13           0140          ICSIDL           0142          ICSIDL           0144          ICSIDL           0146          ICSIDL           0148          ICSIDL | Addr         Bit 15         Bit 14         Bit 13         Bit 12           0140         -         -         ICSIDL         -           0142         -         -         ICSIDL         -           0144         -         -         ICSIDL         -           0146         -         -         ICSIDL         -           0148         -         -         ICSIDL         - | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0           0140 |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-10: OUTPUT COMPARE REGISTER MAP

| SFR<br>Addr | Bit 15                                       | Bit 14                                                                                                                                           | Bit 13                                            | Bit 12                                                           | Bit 11                                                                                                                                                                                                                                                                                     | Bit 10                                                                                         | Bit 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Bit 8                                                                                                                       | Bit 7                                                                                                                                     | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit 5                                                                                                                     | Bit 4                                                                                                                               | Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bit 1                                                                                                                                                             | Bit 0                                                                                                                                                                                                                        | All<br>Resets                                                                            |

|-------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 0180        |                                              |                                                                                                                                                  |                                                   |                                                                  |                                                                                                                                                                                                                                                                                            |                                                                                                | Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | put Compar                                                                                                                  | e 1 Second                                                                                                                                | ary Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | r                                                                                                                         |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                   |                                                                                                                                                                                                                              | xxxx                                                                                     |

| 0182        |                                              | Output Compare 1 Register                                                                                                                        |                                                   |                                                                  |                                                                                                                                                                                                                                                                                            |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                             |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                           | XXXX                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                   |                                                                                                                                                                                                                              |                                                                                          |

| 0184        | —                                            | —                                                                                                                                                | OCSIDL                                            | —                                                                | —                                                                                                                                                                                                                                                                                          | —                                                                                              | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                                                                           | —                                                                                                                                         | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | —                                                                                                                         | OCFLT                                                                                                                               | OCTSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OCM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OCM1                                                                                                                                                              | OCM0                                                                                                                                                                                                                         | 0000                                                                                     |

| 0186        |                                              |                                                                                                                                                  |                                                   |                                                                  |                                                                                                                                                                                                                                                                                            |                                                                                                | Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | put Compar                                                                                                                  | e 2 Second                                                                                                                                | ary Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | r                                                                                                                         |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                   |                                                                                                                                                                                                                              | XXXX                                                                                     |

| 0188        |                                              |                                                                                                                                                  |                                                   |                                                                  |                                                                                                                                                                                                                                                                                            |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Output Co                                                                                                                   | ompare 2 Re                                                                                                                               | egister                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                           |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                   |                                                                                                                                                                                                                              | XXXX                                                                                     |

| 018A        | —                                            | —                                                                                                                                                | OCSIDL                                            | —                                                                | —                                                                                                                                                                                                                                                                                          | _                                                                                              | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                           | —                                                                                                                                         | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | —                                                                                                                         | OCFLT                                                                                                                               | OCTSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OCM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OCM1                                                                                                                                                              | OCM0                                                                                                                                                                                                                         | 0000                                                                                     |