Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

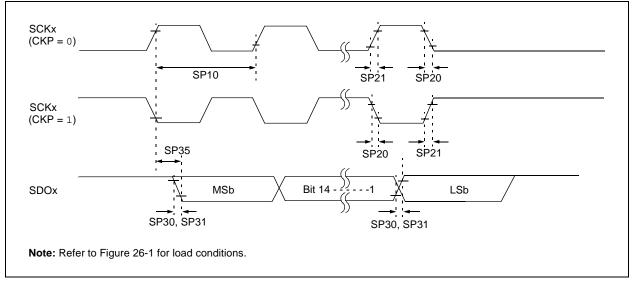

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp102-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest "dsPIC33/PIC24 Family Reference Manual" sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, if present on the device (regardless if ADC module is not used) (see Section 2.2 "Decoupling Capacitors")

- VCAP (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10V-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

The SAC and SAC.R instructions store either a truncated (SAC), or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see **Section 3.6.3.2 "Data Space Write Saturation**"). For the MAC class of instructions, the accumulator writeback operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

#### 3.6.3.2 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly:

- For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF.

- For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000.

The MSb of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

#### 3.6.4 BARREL SHIFTER

The barrel shifter can perform up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts, in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between Bit Positions 16 and 31 for right shifts, and between Bit Positions 0 and 16 for left shifts.

| TABLE | 4-26: | PERI | PHERAI | _ PIN S | ELECT | OUTPU | T REGIS | TER MA | P FOR o | IsPIC33 | 3FJ32(0 | SP/MC) <sup>2</sup> | 04 DE | /ICES |   |

|-------|-------|------|--------|---------|-------|-------|---------|--------|---------|---------|---------|---------------------|-------|-------|---|

|       |       |      |        |         |       |       |         |        |         |         |         |                     |       |       | т |

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| RPOR0        | 06C0        | _      | —      | —      |        |        | RP1R<4:0> | >     |       | —     | —     | —     |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR1        | 06C2        | -      |        | _      |        |        | RP3R<4:0> | >     |       | _     | _     | _     |       |       | RP2R<4:0>  |       |       | 0000          |

| RPOR2        | 06C4        | -      |        | _      |        |        | RP5R<4:0> | >     |       | _     | _     | _     |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3        | 06C6        | —      | _      | _      |        |        | RP7R<4:0> | >     |       | _     | _     | —     |       |       | RP6R<4:0>  |       |       | 0000          |

| RPOR4        | 06C8        | _      | _      | _      |        |        | RP9R<4:0> | >     |       | _     | _     | _     |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR5        | 06CA        | _      | _      | _      |        |        | RP11R<4:0 | >     |       | _     | _     | _     |       | F     | RP10R<4:0> |       |       | 0000          |

| RPOR6        | 06CC        | _      | _      | _      |        |        | RP13R<4:0 | >     |       | _     | _     | _     |       | F     | RP12R<4:0> |       |       | 0000          |

| RPOR7        | 06CE        | _      | _      | _      |        |        | RP15R<4:0 | >     |       | _     | _     | _     |       | F     | RP14R<4:0> |       |       | 0000          |

| RPOR8        | 06D0        | _      | _      | _      |        |        | RP17R<4:0 | >     |       | _     | _     | _     |       | F     | RP16R<4:0> |       |       | 0000          |

| RPOR9        | 06D2        | -      |        | _      |        |        | RP19R<4:0 | >     |       | _     | _     | _     |       | F     | RP18R<4:0> |       |       | 0000          |

| RPOR10       | 06D4        | _      | _      | _      |        |        | RP21R<4:0 | >     |       | _     | _     | _     |       | F     | RP20R<4:0> |       |       | 0000          |

| RPOR11       | 06D6        | _      | _      | _      |        |        | RP23R<4:0 | >     |       | _     | _     | _     |       | F     | RP22R<4:0> |       |       | 0000          |

| RPOR12       | 06D8        | _      | _      | -      |        |        | RP25R<4:0 | >     |       | _     | -     | —     |       | F     | RP24R<4:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-27: PORTA REGISTER MAP FOR dsPIC33FJ16(GP/MC)101/102 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-----------|------------|-------|-------|---------------|

| TRISA        | 02C0        | _      |        | _      |        | _      | _      | _     | _     | _     | _     | _     |       | -         | rrisa<4:0> |       |       | 001F          |

| PORTA        | 02C2        | —      | _      | _      | _      | _      | _      | _     | _     | -     | —     | _     |       |           | RA<4:0     |       |       | xxxx          |

| LATA         | 02C4        | —      | _      | _      | _      | _      | _      | _     | _     | -     | —     | _     |       |           | LATA<4:0   |       |       | xxxx          |

| ODCA         | 02C6        |        | _      | _      | _      | _      | _      | _     | _     | _     |       | _     | (     | ODCA<4:2> |            | _     | —     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-28: PORTA REGISTER MAP FOR dsPIC33FJ32(GP/MC)101/102 DEVICES

|     | File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|-----|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| Ī   | TRISA        | 02C0        | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |       | ٦     | rrisa<4:0> |       |       | 001F          |

| ſ   | PORTA        | 02C2        | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     |       |       | RA<4:0     |       |       | xxxx          |

| ſ   | LATA         | 02C4        | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     |       |       | LATA<4:0   |       |       | xxxx          |

| . [ | ODCA         | 02C6        | _      |        |        | —      |        | _      | _     | _     | _     | _     | _     |       | ODCA  | <3:2>      | _     | -     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-33: PORTB REGISTER MAP FOR dsPIC33FJ32GP101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|---------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        | TRISB< | :15:14> | —      |        |        | —      | -     | TRISB<9:7 | >     |       | —     | TRISB4 |       |       | TRISE | 3<1:0> | C393          |

| PORTB     | 02CA        | RB<1   | 5:14>   | _      | _      | _      | _      |       | RB<9:7>   |       | _     | _     | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        | LATB<  | 15:14>  | _      | _      | _      | _      |       | LATB<9:7> | >     | _     | _     | LATB4  | _     | _     | LATB  | <1:0>  | xxxx          |

| ODCB      | 02CE        | ODCB<  | :15:14> | _      | _      |        | _      | (     | ODCB<9:7  | >     | -     | _     | _      |       |       | -     |        | 0000          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-34: PORTB REGISTER MAP FOR dsPIC33FJ32MC101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|--------|---------|--------|--------|--------|-------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        |        | TRISB< | <15:12> |        | —      | _      | -     | TRISB<9:7 | >     | _     | —     | TRISB4 | _     | _     | TRISE | 3<1:0> | F393          |

| PORTB     | 02CA        |        | RB<1   | 5:12>   |        | _      | _      |       | RB<9:7>   |       | _     | —     | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        |        | LATB<  | 15:12>  |        | _      | _      |       | LATB<9:7> | •     | _     | —     | LATB4  | _     | _     | LATB  | <1:0>  | xxxx          |

| ODCB      | 02CE        |        | ODCB<  | <15:12> |        | _      | -      | (     | ODCB<9:7: | >     | _     | —     | _      | _     | _     | —     | _      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-35: PORTB REGISTER MAP FOR dsPIC33FJ32(GP/MC)102 AND dsPIC33FJ32(GP/MC)104 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|-----------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB        | 02C8        |        |        |        |        |        |           |       | TRISB< | :15:0> |       |       |       |       |       |       |       | FFFF          |

| PORTB        | 02CA        |        |        |        |        |        |           |       | RB<1   | 5:0>   |       |       |       |       |       |       |       | xxxx          |

| LATB         | 02CC        |        |        |        |        |        |           |       | LATB<  | 15:0>  |       |       |       |       |       |       |       | xxxx          |

| ODCB         | 02CE        |        |        |        |        | 0      | DCB<15:5> |       |        |        |       |       | -     | _     | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-36: PORTC REGISTER MAP FOR dsPIC33FJ32(GP/MC)104 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|-------|-------|-------|-------|---------------|

| TRISC        | 02D0        | —      | _      | _      | —      | _      | —      |       |       |        |       | TRISC | C<9:0> |       |       |       |       | FFFF          |

| PORTC        | 02D2        |        | _      | _      | —      | _      | _      |       |       |        |       | RC<   | :9:0>  |       |       |       |       | xxxx          |

| LATC         | 02D4        |        | _      | _      | —      | _      | _      |       |       |        |       | LATC  | <9:0>  |       |       |       |       | xxxx          |

| ODCC         | 02D6        | _      | _      | _      | —      | _      | —      |       | ODC   | C<9:6> |       |       | —      | _     | _     | —     |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| REGISTER 5            | 5-1: NVMCO                      | N: FLASH I               | MEMORY C                    | ONTROL RE             | GISTER                |                       |                       |

|-----------------------|---------------------------------|--------------------------|-----------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>            | R/W-0 <sup>(1)</sup>     | U-0                         | U-0                   | U-0                   | U-0                   | U-0                   |

| WR                    | WREN                            | WRERR                    |                             |                       | —                     |                       | _                     |

| bit 15                |                                 |                          |                             |                       |                       |                       | bit 8                 |

|                       | (4)                             |                          |                             | (4)                   | (4)                   | (4)                   | (4)                   |

| U-0                   | R/W-0 <sup>(1)</sup>            | U-0                      | U-0                         | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  |

|                       | ERASE                           | —                        | —                           | NVMOP3 <sup>(2)</sup> | NVMOP2 <sup>(2)</sup> | NVMOP1 <sup>(2)</sup> | NVMOP0 <sup>(2)</sup> |

| bit 7                 |                                 |                          |                             |                       |                       |                       | bit 0                 |

| Legend:               |                                 | SO = Settat              | ale Only hit                |                       |                       |                       |                       |

| R = Readable          | hit                             |                          |                             |                       | mantad hit raad       |                       |                       |

|                       |                                 | W = Writabl              |                             | -                     | nented bit, read      |                       |                       |

| -n = Value at I       | POR                             | '1' = Bit is s           | et                          | '0' = Bit is cle      | ared                  | x = Bit is unkr       | IOWN                  |

| bit 15                | WR: Write Con                   | trol bit <sup>(1)</sup>  |                             |                       |                       |                       |                       |

| 5                     |                                 |                          | v program or                | r erase operati       | on; the operatic      | on is self-timed      | and the bit is        |

|                       |                                 | hardware on              |                             | •                     |                       |                       |                       |

|                       | 0 = Program o                   |                          |                             |                       | e                     |                       |                       |

| bit 14                | WREN: Write E                   | nable bit <sup>(1)</sup> |                             |                       |                       |                       |                       |

|                       | 1 = Enables Fl                  |                          | erase operati               | ions                  |                       |                       |                       |

|                       | 0 = Inhibits Fla                |                          |                             |                       |                       |                       |                       |

| bit 13                | WRERR: Write                    | Sequence Er              | ror Flag bit <sup>(1)</sup> | )                     |                       |                       |                       |

|                       |                                 |                          | •                           |                       | rmination has oc      | curred (bit is se     | t automaticallv       |

|                       |                                 | attempt of the           |                             |                       |                       | (                     |                       |

|                       | 0 = The progra                  |                          |                             | pleted normally       | /                     |                       |                       |

| bit 12-7              | Unimplemente                    | ed: Read as 'd           | )'                          |                       |                       |                       |                       |

| bit 6                 | ERASE: Erase                    | /Program Ena             | ble bit <sup>(1)</sup>      |                       |                       |                       |                       |

|                       |                                 |                          |                             |                       | 3:0> on the nex       |                       |                       |

|                       |                                 |                          | -                           | Cified by NVINC       | P<3:0> on the         | next WR comm          | land                  |

| bit 5-4               | Unimplemente                    |                          |                             | (1.0)                 |                       |                       |                       |

| bit 3-0               | NVMOP<3:0>:                     | NVM Operati              | on Selection                | bits <sup>(1,2)</sup> |                       |                       |                       |

|                       | If ERASE = 1:                   | _                        |                             |                       |                       |                       |                       |

|                       | 1111 = No ope                   |                          | 4                           |                       |                       |                       |                       |

|                       | 1101 = Erase (<br>1100 = No ope | •                        | ient                        |                       |                       |                       |                       |

|                       | 0011 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 0010 = Memor                    |                          | operation                   |                       |                       |                       |                       |

|                       | 0001 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 0000 = No ope                   | ration                   |                             |                       |                       |                       |                       |

|                       | If ERASE = 0:                   |                          |                             |                       |                       |                       |                       |

|                       | 1111 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 1101 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 1100 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 0011 = Memor<br>0010 = No ope   |                          | in operation                |                       |                       |                       |                       |

|                       | 0001 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | 0000 = No ope                   |                          |                             |                       |                       |                       |                       |

|                       | -                               |                          |                             |                       |                       |                       |                       |

|                       | ese bits can only               |                          |                             |                       |                       |                       |                       |

|                       | other combination               |                          |                             | implemented.          | ECISTED               |                       |                       |

| REGISTER 5            | -2. IN VIVINE                   |                          |                             |                       | LOISIEK               |                       |                       |

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| U-0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| —   | —   |     |     | —   |     |     | _   |

© 2011-2014 Microchip Technology Inc.

| D / M A       | D 444 A                         | D.4.4. 0                            | DAMA            | DALLA             | DALLA           | DAMA            | D 44/ 6 |

|---------------|---------------------------------|-------------------------------------|-----------------|-------------------|-----------------|-----------------|---------|

| R/W-0         | R/W-0                           | R/W-0                               | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

| NSTDIS        | OVAERR                          | OVBERR                              | COVAERR         | COVBERR           | OVATE           | OVBTE           | COVTE   |

| bit 15        |                                 |                                     |                 |                   |                 |                 | bi      |

| R/W-0         | R/W-0                           | U-0                                 | R/W-0           | R/W-0             | R/W-0           | R/W-0           | U-0     |

| SFTACERR      |                                 | <u> </u>                            | MATHERR         | ADDRERR           | STKERR          | OSCFAIL         |         |

| bit 7         | BIVOLINI                        |                                     |                 | ABBRERR           | OTTLETT         | 00017112        | bi      |

|               |                                 |                                     |                 |                   |                 |                 |         |

| Legend:       |                                 |                                     |                 |                   |                 |                 |         |

| R = Readabl   | e bit                           | W = Writable                        | bit             | U = Unimplem      | ented bit, read | 1 as '0'        |         |

| -n = Value at | POR                             | '1' = Bit is set                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |

| 6:4 <i>7</i>  |                                 | www.unt.Nie.otie.ev.F               | Niachla hit     |                   |                 |                 |         |

| bit 15        |                                 | rrupt Nesting E<br>nesting is disat |                 |                   |                 |                 |         |

|               |                                 | nesting is cloat                    |                 |                   |                 |                 |         |

| bit 14        | -                               | cumulator A O                       |                 | lag bit           |                 |                 |         |

|               | 1 = Trap was                    | caused by ove                       | erflow of Accur | nulator A         |                 |                 |         |

|               | 0 = Trap was                    | not caused by                       | overflow of Ad  | ccumulator A      |                 |                 |         |

| bit 13        |                                 | cumulator B O                       | -               | -                 |                 |                 |         |

|               |                                 | caused by ove<br>not caused by      |                 |                   |                 |                 |         |

| bit 12        | -                               | -                                   |                 | Dverflow Trap F   | lag hit         |                 |         |

|               |                                 |                                     | •               | flow of Accumu    | •               |                 |         |

|               | •                               | •                                   | •               | overflow of Accu  |                 |                 |         |

| bit 11        | COVBERR: A                      | Accumulator B                       | Catastrophic C  | Overflow Trap F   | lag bit         |                 |         |

|               |                                 |                                     |                 | flow of Accumu    |                 |                 |         |

|               | -                               | -                                   | -               | overflow of Accu  | umulator B      |                 |         |

| bit 10        |                                 | Imulator A Ove                      |                 | able bit          |                 |                 |         |

|               | ⊥ = Trap over<br>0 = Trap is di | flow of Accum                       | ulator A        |                   |                 |                 |         |

| bit 9         |                                 | umulator B Ove                      | erflow Trap En  | able bit          |                 |                 |         |

|               |                                 | flow of Accum                       |                 |                   |                 |                 |         |

|               | 0 = Trap is di                  | sabled                              |                 |                   |                 |                 |         |

| bit 8         | COVTE: Cata                     | astrophic Overf                     | low Trap Enab   | ole bit           |                 |                 |         |

|               |                                 |                                     | erflow of Accur | mulator A or B i  | s enabled       |                 |         |

| hit 7         | 0 = Trap is dis                 | sabled<br>Shift Accumula            | tor Error State | ia hit            |                 |                 |         |

| bit 7         |                                 |                                     |                 | llid accumulator  | chift           |                 |         |

|               |                                 |                                     |                 | invalid accumul   |                 |                 |         |

| bit 6         |                                 | ithmetic Error :                    | -               |                   |                 |                 |         |

|               |                                 | or trap was cau                     | -               | -                 |                 |                 |         |

|               |                                 | r trap was not                      | -               | ivide-by-zero     |                 |                 |         |

| bit 5         | •                               | ted: Read as '                      |                 |                   |                 |                 |         |

| bit 4         | MATHERR: A                      | Arithmetic Error                    | Status bit      |                   |                 |                 |         |

|               | 1 14-41                         | or trap has occu                    | una al          |                   |                 |                 |         |

#### INTOONA, INTERDURT CONTROL DECISTER A

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

|                    | U-0                                                                     | U-0                                                                                                     | R/W-1           | R/W-1            | R/W-1            | R/W-1           | R/W-1           |  |  |  |

|--------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|-----------------|--|--|--|

| —                  | —                                                                       | —                                                                                                       | T3CKR4          | T3CKR3           | T3CKR2           | T3CKR1          | T3CKR0          |  |  |  |

| bit 15             |                                                                         |                                                                                                         |                 |                  |                  |                 | bit 8           |  |  |  |

|                    |                                                                         |                                                                                                         |                 |                  |                  |                 |                 |  |  |  |

| U-0                | U-0                                                                     | U-0                                                                                                     | R/W-1<br>T2CKR4 | R/W-1<br>T2CKR3  | R/W-1<br>T2CKR2  | R/W-1<br>T2CKR1 | R/W-1<br>T2CKR0 |  |  |  |

| bit 7              |                                                                         |                                                                                                         | 1201411         | 1201410          | 1201112          |                 | bit (           |  |  |  |

|                    |                                                                         |                                                                                                         |                 |                  |                  |                 |                 |  |  |  |

| Legend:            |                                                                         |                                                                                                         |                 |                  |                  |                 |                 |  |  |  |

| R = Readab         | le bit                                                                  | W = Writable                                                                                            | bit             | U = Unimpler     | mented bit, read | d as '0'        |                 |  |  |  |

| -n = Value a       | t POR                                                                   | '1' = Bit is se                                                                                         | t               | '0' = Bit is cle | ared             | x = Bit is unkr | iown            |  |  |  |

|                    |                                                                         |                                                                                                         | ( - <b>1</b>    |                  |                  |                 |                 |  |  |  |

| bit 15-13          | -                                                                       | ted: Read as                                                                                            |                 |                  |                  |                 |                 |  |  |  |

| bit 12-8           |                                                                         | -                                                                                                       | r3 External Clo | ck (T3CK) to t   | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |

|                    | 11111 = Inpu                                                            |                                                                                                         |                 |                  |                  |                 |                 |  |  |  |

|                    | 11110 = Res                                                             | erved                                                                                                   |                 |                  |                  |                 |                 |  |  |  |

|                    | •                                                                       |                                                                                                         |                 |                  |                  |                 |                 |  |  |  |

|                    | •                                                                       |                                                                                                         |                 |                  |                  |                 |                 |  |  |  |

|                    | 11010 = Reserved                                                        |                                                                                                         |                 |                  |                  |                 |                 |  |  |  |

|                    | 11001 = Inpu                                                            | t tied to RP25                                                                                          |                 |                  |                  |                 |                 |  |  |  |

|                    |                                                                         |                                                                                                         |                 |                  |                  |                 |                 |  |  |  |

|                    |                                                                         |                                                                                                         |                 |                  |                  |                 |                 |  |  |  |

|                    |                                                                         |                                                                                                         |                 |                  |                  |                 |                 |  |  |  |

|                    | •                                                                       |                                                                                                         |                 |                  |                  |                 |                 |  |  |  |

|                    | 00001 = Inpu                                                            |                                                                                                         |                 |                  |                  |                 |                 |  |  |  |

|                    | 00000 = Inpu                                                            | t tied to RP0                                                                                           |                 |                  |                  |                 |                 |  |  |  |

| bit 7-5            | 00000 = Inpu<br>Unimplemen                                              | t tied to RP0<br>ted: Read as                                                                           |                 |                  |                  |                 |                 |  |  |  |

| bit 7-5<br>bit 4-0 | 00000 = Inpu<br>Unimplemen                                              | t tied to RP0<br>ted: Read as                                                                           |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu                | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Time<br>It tied to Vss                                |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 3               |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0>                                | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Time<br>It tied to Vss                                |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu                | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Time<br>It tied to Vss                                |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu                | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Time<br>It tied to Vss                                |                 | ck (T2CK) to ti  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                             |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                             | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 3               |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                             | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                             | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 3               |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                             | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved<br>erved<br>It tied to RP25 | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |

#### REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| REGISTER      | 10-9: RPINE                 | 20: PERIPH                | ERAL PIN S            | ELECT INPU            | TREGISTER             | 20                      |                       |  |  |  |

|---------------|-----------------------------|---------------------------|-----------------------|-----------------------|-----------------------|-------------------------|-----------------------|--|--|--|

| U-0           | U-0                         | U-0                       | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                   | R/W-1                 |  |  |  |

| —             | —                           | —                         | SCK1R4 <sup>(1)</sup> | SCK1R3 <sup>(1)</sup> | SCK1R2 <sup>(1)</sup> | SCK1R1 <sup>(1)</sup>   | SCK1R0 <sup>(1)</sup> |  |  |  |

| bit 15        |                             |                           |                       |                       |                       |                         | bit 8                 |  |  |  |

|               |                             |                           |                       |                       |                       |                         |                       |  |  |  |

| U-0           | U-0                         | U-0                       | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                   | R/W-1                 |  |  |  |

|               |                             |                           | SDI1R4 <sup>(1)</sup> | SDI1R3 <sup>(1)</sup> | SDI1R2 <sup>(1)</sup> | SDI1R1 <sup>(1)</sup>   | SDI1R0 <sup>(1)</sup> |  |  |  |

| bit 7         |                             |                           |                       |                       |                       |                         | bit 0                 |  |  |  |

|               |                             |                           |                       |                       |                       |                         |                       |  |  |  |

| Legend:       |                             |                           |                       |                       |                       |                         |                       |  |  |  |

| R = Readabl   |                             | W = Writable              |                       | -                     | nented bit, read      |                         |                       |  |  |  |

| -n = Value at | t POR                       | '1' = Bit is set          |                       | '0' = Bit is cle      | ared                  | x = Bit is unkr         | IOWN                  |  |  |  |

| 1 1 4 5 4 0   |                             |                           | o.!                   |                       |                       |                         |                       |  |  |  |

| bit 15-13     | -                           | ted: Read as '            |                       |                       | <b>.</b>              |                         |                       |  |  |  |

| bit 12-8      |                             |                           | Clock Input (S        | CK1IN) to the         | Corresponding         | RPn Pin bits            |                       |  |  |  |

|               | 11111 = Inpu<br>11110 = Res |                           |                       |                       |                       |                         |                       |  |  |  |

|               | 11110 = Res                 | erved                     |                       |                       |                       |                         |                       |  |  |  |

|               |                             |                           |                       |                       |                       |                         |                       |  |  |  |

|               |                             |                           |                       |                       |                       |                         |                       |  |  |  |

|               | 11010 = Res                 |                           |                       |                       |                       |                         |                       |  |  |  |

|               | 11001 <b>= I</b> npu        | ut tied to RP25           |                       |                       |                       |                         |                       |  |  |  |

|               | •                           |                           |                       |                       |                       |                         |                       |  |  |  |

|               | •                           |                           |                       |                       |                       |                         |                       |  |  |  |

|               | 00001 = Inpu                | ut tied to RP1            |                       |                       |                       |                         |                       |  |  |  |

|               |                             | 00000 = Input tied to RP0 |                       |                       |                       |                         |                       |  |  |  |

| bit 7-5       | Unimplemen                  | ted: Read as '            | 0'                    |                       |                       |                         |                       |  |  |  |

| bit 4-0       | SDI1R<4:0>:                 | Assign SPI1 E             | Data Input (SD        | 11) to the Corre      | esponding RPn         | Pin bits <sup>(1)</sup> |                       |  |  |  |

|               | 11111 <b>= I</b> npu        |                           |                       |                       |                       |                         |                       |  |  |  |

|               | 11110 <b>= Res</b>          | erved                     |                       |                       |                       |                         |                       |  |  |  |

|               | •                           |                           |                       |                       |                       |                         |                       |  |  |  |

|               |                             |                           |                       |                       |                       |                         |                       |  |  |  |

|               | 11010 = Reserved            |                           |                       |                       |                       |                         |                       |  |  |  |

|               |                             | ut tied to RP25           |                       |                       |                       |                         |                       |  |  |  |

|               |                             |                           |                       |                       |                       |                         |                       |  |  |  |

|               |                             |                           |                       |                       |                       |                         |                       |  |  |  |

|               | 00001 = Inpu                | it tied to RP1            |                       |                       |                       |                         |                       |  |  |  |

|               | 000001 = Inpu               |                           |                       |                       |                       |                         |                       |  |  |  |

|               |                             | •                         |                       |                       |                       |                         |                       |  |  |  |

#### REGISTER 10-9: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| REGISTER                         | 12-3: T4CO                                                                                         | N: TIMER4 C                                                                                        | ONTROL RI      | EGISTER <sup>(1)</sup> |                 |                 |      |  |  |  |

|----------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------|------------------------|-----------------|-----------------|------|--|--|--|

| R/W-0                            | U-0                                                                                                | R/W-0                                                                                              | U-0            | U-0                    | U-0             | U-0             | U-0  |  |  |  |

| TON                              | —                                                                                                  | TSIDL                                                                                              | —              | —                      | —               | —               | —    |  |  |  |

| bit 15                           |                                                                                                    |                                                                                                    |                |                        |                 |                 | bita |  |  |  |

| U-0                              | R/W-0                                                                                              | R/W-0                                                                                              | R/W-0          | R/W-0                  | U-0             | R/W-0           | U-0  |  |  |  |

| _                                | TGATE                                                                                              | TCKPS1                                                                                             | TCKPS0         | T32                    | _               | TCS             | _    |  |  |  |

| bit 7                            |                                                                                                    |                                                                                                    |                |                        |                 |                 | bit  |  |  |  |

|                                  |                                                                                                    |                                                                                                    |                |                        |                 |                 |      |  |  |  |

| Legend:<br>R = Readab            | le hit                                                                                             | W = Writable                                                                                       | hit            | II – Unimpler          | mented bit, rea | nd as 'O'       |      |  |  |  |

| -n = Value a                     |                                                                                                    | '1' = Bit is set                                                                                   |                | '0' = Bit is cle       |                 | x = Bit is unkn | own  |  |  |  |

|                                  |                                                                                                    |                                                                                                    |                |                        |                 |                 |      |  |  |  |

| bit 15                           | TON: Timer4                                                                                        |                                                                                                    |                |                        |                 |                 |      |  |  |  |

|                                  | $\frac{\text{When T32}}{1 = \text{Starts 32}}$                                                     |                                                                                                    |                |                        |                 |                 |      |  |  |  |

|                                  | 1 = Starts 32 - 0 = Stops 32 - 0 = Stops 32 - 0 = Stops 32 - 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 |                                                                                                    |                |                        |                 |                 |      |  |  |  |

|                                  | When T32 =                                                                                         |                                                                                                    |                |                        |                 |                 |      |  |  |  |

|                                  | 1 = Starts 16-                                                                                     |                                                                                                    |                |                        |                 |                 |      |  |  |  |

|                                  | 0 = Stops 16-                                                                                      | bit Timer4                                                                                         |                |                        |                 |                 |      |  |  |  |

| bit 14                           | Unimplemen                                                                                         | Unimplemented: Read as '0'                                                                         |                |                        |                 |                 |      |  |  |  |

| bit 13                           | TSIDL: Timer4 Stop in Idle Mode bit                                                                |                                                                                                    |                |                        |                 |                 |      |  |  |  |

|                                  |                                                                                                    | ues module op<br>s module opera                                                                    |                | device enters l<br>ode | ldle mode       |                 |      |  |  |  |

| bit 12-7                         | Unimplemen                                                                                         | ted: Read as '                                                                                     | 0'             |                        |                 |                 |      |  |  |  |

| bit 6                            | TGATE: Time                                                                                        | er4 Gated Time                                                                                     | e Accumulation | n Enable bit           |                 |                 |      |  |  |  |

|                                  | When TCS =                                                                                         |                                                                                                    |                |                        |                 |                 |      |  |  |  |

|                                  | This bit is ign                                                                                    |                                                                                                    |                |                        |                 |                 |      |  |  |  |

|                                  | <u>When TCS =</u><br>1 = Cotod time                                                                | <u>0:</u><br>ne accumulatio                                                                        | n in anablad   |                        |                 |                 |      |  |  |  |

|                                  |                                                                                                    | ne accumulatio                                                                                     |                |                        |                 |                 |      |  |  |  |

| bit 5-4                          |                                                                                                    | : Timer4 Input                                                                                     |                | le Select bits         |                 |                 |      |  |  |  |

|                                  | 11 = 1:256                                                                                         | · · · · · · · · · · · · · · · · · · ·                                                              | 0.000.00000    |                        |                 |                 |      |  |  |  |

|                                  | 10 <b>= 1:64</b>                                                                                   |                                                                                                    |                |                        |                 |                 |      |  |  |  |

|                                  | 01 = 1:8                                                                                           | 01 = 1:8                                                                                           |                |                        |                 |                 |      |  |  |  |

|                                  | 00 = 1:1                                                                                           |                                                                                                    |                |                        |                 |                 |      |  |  |  |

| bit 3                            |                                                                                                    | T32: 32-Bit Timer Mode Select bit                                                                  |                |                        |                 |                 |      |  |  |  |

|                                  |                                                                                                    | 1 = Timer4 and Timer5 form a single 32-bit timer<br>0 = Timer4 and Timer5 act as two 16-bit timers |                |                        |                 |                 |      |  |  |  |

| bit 2 Unimplemented: Read as '0' |                                                                                                    |                                                                                                    |                |                        |                 |                 |      |  |  |  |

| bit 1                            | -                                                                                                  | Clock Source                                                                                       |                |                        |                 |                 |      |  |  |  |

|                                  |                                                                                                    | clock from pin,                                                                                    |                | rising edge)           |                 |                 |      |  |  |  |

|                                  | 0 = Internal c                                                                                     |                                                                                                    |                | nonig ougo)            |                 |                 |      |  |  |  |

| bit 0                            | Unimplemen                                                                                         | ted: Read as '                                                                                     | 0'             |                        |                 |                 |      |  |  |  |

| Note 1: ⊤                        | his register is ava                                                                                | ailable in dsPIC                                                                                   | C33FJ32(GP/N   | MC)10X device          | s only.         |                 |      |  |  |  |

|                                  | -                                                                                                  |                                                                                                    | `              |                        | -               |                 |      |  |  |  |

## REGISTER 12-3: T4CON: TIMER4 CONTROL REGISTER<sup>(1)</sup>

| R/W-0                      | R/W-0                                                                                                       | R/W-0                                                                                                      | U-0                                                                                              | U-0               | U-0              | U-0                | U-0   |

|----------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------|------------------|--------------------|-------|

| FRMEN                      | SPIFSD                                                                                                      | FRMPOL                                                                                                     |                                                                                                  | —                 |                  | —                  | _     |

| bit 15                     |                                                                                                             |                                                                                                            |                                                                                                  |                   |                  |                    | bit 8 |

| U-0                        | U-0                                                                                                         | U-0                                                                                                        | U-0                                                                                              | U-0               | U-0              | R/W-0              | U-0   |

| 0-0                        | 0-0                                                                                                         | 0-0                                                                                                        | 0-0                                                                                              | 0-0               | 0-0              | FRMDLY             | 0-0   |

| <br>bit 7                  |                                                                                                             |                                                                                                            |                                                                                                  |                   |                  | TRIMDET            | bit ( |

|                            |                                                                                                             |                                                                                                            |                                                                                                  |                   |                  |                    |       |

| Legend:                    |                                                                                                             |                                                                                                            |                                                                                                  |                   |                  |                    |       |

| R = Readable               | e bit                                                                                                       | W = Writable                                                                                               | bit                                                                                              | U = Unimplen      | nented bit, read | l as '0'           |       |

| -n = Value at              | POR                                                                                                         | '1' = Bit is set                                                                                           |                                                                                                  | '0' = Bit is clea | ared             | x = Bit is unknown |       |

| bit 15<br>bit 14<br>bit 13 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy | Plx support is<br>me Sync Pulse<br>rnc pulse input<br>rnc pulse outpu<br>ame Sync Puls<br>rnc pulse is act | enabled (SSx<br>disabled<br>Direction Cor<br>(slave)<br>t (master)<br>e Polarity bit<br>ive-high |                   | Frame Sync pu    | ulse input/output  | )     |

| bit 12-2<br>bit 1          | Unimplemen<br>FRMDLY: Fra<br>1 = Frame Sy                                                                   | rnc pulse is act<br>ted: Read as '<br>ame Sync Pulse<br>rnc pulse coinc<br>rnc pulse prece                 | 0'<br>e Edge Select<br>ides with first                                                           | bit clock         |                  |                    |       |

| bit 0                      | -                                                                                                           |                                                                                                            |                                                                                                  | to '1' by the us  | er application   |                    |       |