Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

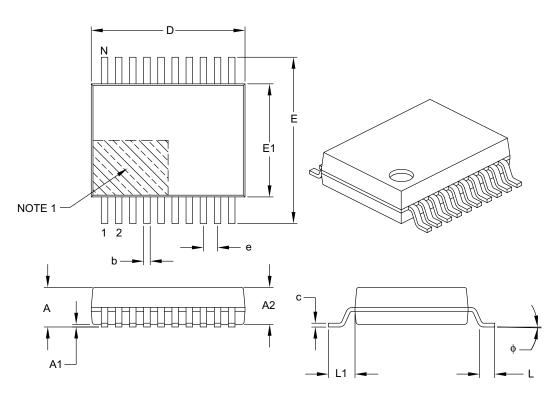

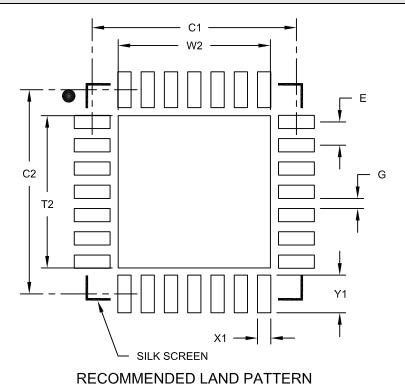

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 36-VTLA (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp102-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

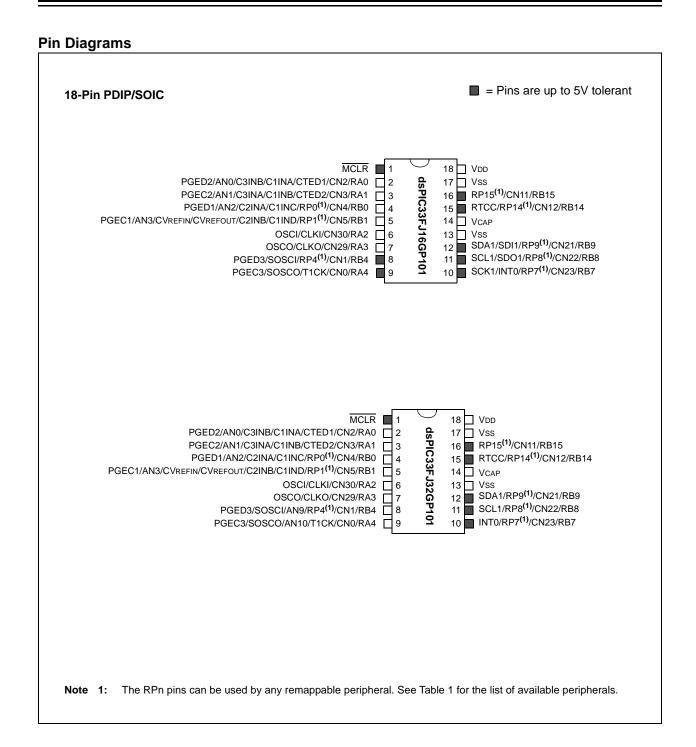

#### dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. The following pages show their pinout diagrams.

|                  |      | rte)                  |              |                 | Rem                           | appa          | ble l          | Perip | herals                             | 5   | М                 |            | Ŋ                    |      |      |             |      |          |                                 |

|------------------|------|-----------------------|--------------|-----------------|-------------------------------|---------------|----------------|-------|------------------------------------|-----|-------------------|------------|----------------------|------|------|-------------|------|----------|---------------------------------|

| Device           | Pins | Program Flash (Kbyte) | RAM (Kbytes) | Remappable Pins | 16-bit Timer <sup>(1,2)</sup> | Input Capture | Output Compare | UART  | External Interrupts <sup>(3)</sup> | SPI | Motor Control PWM | PWM Faults | 10-Bit, 1.1 Msps ADC | RTCC | I²C™ | Comparators | CTMU | I/O Pins | Packages                        |

| dsPIC33FJ16GP101 | 18   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 13       | PDIP,<br>SOIC                   |

|                  | 20   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | SSOP                            |

| dsPIC33FJ16GP102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | _          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

| dsPIC33FJ16MC101 | 20   | 16                    | 1            | 10              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 1          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | PDIP,<br>SOIC,<br>SSOP          |

| dsPIC33FJ16MC102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

#### TABLE 1:dsPIC33FJ16(GP/MC)101/102 DEVICE FEATURES

**Note 1:** Two out of three timers are remappable.

2: One pair can be combined to create one 32-bit timer.

**3**: Two out of three interrupts are remappable.

#### TABLE 4-12: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                        | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3       | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|------------------------------|-------|-------|-------|------------|-------------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       | _      |         | _      |        |        | _      | _                            |       |       |       | I2C1 Recei | ve Register |       |       |       | 0000          |

| I2C1TRN  | 0202        | _       | _      | _       | —      | _      | _      | _      | I2C1 Transmit Register       |       |       |       |            |             |       | 00FF  |       |               |

| I2C1BRG  | 0204        | _       | _      | _       | —      | _      | _      | _      | Baud Rate Generator Register |       |       |       |            |             |       | 0000  |       |               |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                         | GCEN  | STREN | ACKDT | ACKEN      | RCEN        | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                        | IWCOL | I2COV | D_A   | Р          | S           | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       |        | _       | _      | _      | _      |        | I2C1 Address Register        |       |       |       |            |             |       | 0000  |       |               |

| I2C1MSK  | 020C        | —       | _      | _       | _      | _      |        |        | I2C1 Address Mask Register   |       |       |       |            |             |       | 0000  |       |               |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-13: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6    | Bit 5 | Bit 4      | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|-------------------------------|----------|--------|--------|--------|-------|-------|----------|----------|-------|------------|---------|--------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | —                             | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD | URXINV     | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _                             | -        | _      | _      | _      |       |       |          |          | UART1 | Transmit R | egister |        |        |       | xxxx          |

| U1RXREG  | 0226        | _        | _                             | -        | _      | _      | _      |       |       |          |          | UART  | Receive R  | egister |        |        |       | 0000          |

| U1BRG    | 0228        |          | Baud Rate Generator Prescaler |          |        |        |        |       |       |          |          |       | 0000       |         |        |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: SPI1 REGISTER MAP

|          |             | •••••• |        |         |        |        |        |            |            |              | -        |       |       |       |       | -      |        |               |

|----------|-------------|--------|--------|---------|--------|--------|--------|------------|------------|--------------|----------|-------|-------|-------|-------|--------|--------|---------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8      | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

| SPI1STAT | 0240        | SPIEN  | _      | SPISIDL | _      | _      | _      |            |            |              | SPIROV   | _     | _     | _     |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242        | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE        | SSEN         | CKP      | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000          |

| SPI1CON2 | 0244        | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _      | _          | _          | _            | _        | _     |       | -     | _     | FRMDLY | _      | 0000          |

| SPI1BUF  | 0248        |        |        |         |        |        |        | SPI1 Trans | mit and Re | ceive Buffer | Register |       |       |       |       |        |        | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0                                                                  | U-0                | R/W-0            | U-0           | U-0                | U-0   | U-0             | U-0                    |  |  |  |

|----------------------------------------------------------------------|--------------------|------------------|---------------|--------------------|-------|-----------------|------------------------|--|--|--|

| —                                                                    |                    | CTMUIE           | —             | —                  | —     | —               | —                      |  |  |  |

| bit 15                                                               |                    |                  |               |                    |       |                 | bit 8                  |  |  |  |

|                                                                      |                    |                  |               |                    |       |                 |                        |  |  |  |

| U-0                                                                  | U-0                | U-0              | U-0           | U-0                | U-0   | R/W-0           | R/W-0                  |  |  |  |

|                                                                      |                    |                  | —             | —                  | —     | U1EIE           | FLTB1IE <sup>(1)</sup> |  |  |  |

| bit 7                                                                |                    |                  |               |                    |       |                 | bit 0                  |  |  |  |

|                                                                      |                    |                  |               |                    |       |                 |                        |  |  |  |

| Legend:                                                              |                    |                  |               |                    |       |                 |                        |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                    |                  |               |                    |       |                 |                        |  |  |  |

| -n = Value at P                                                      | OR                 | '1' = Bit is set |               | '0' = Bit is cle   | eared | x = Bit is unki | nown                   |  |  |  |

|                                                                      |                    |                  |               |                    |       |                 |                        |  |  |  |

| bit 15-14                                                            | Unimplemen         | ted: Read as '   | 0'            |                    |       |                 |                        |  |  |  |

| bit 13                                                               | CTMUIE: CTM        | MU Interrupt Er  | nable bit     |                    |       |                 |                        |  |  |  |

|                                                                      |                    | request is enab  |               |                    |       |                 |                        |  |  |  |

|                                                                      | -                  | request is not e |               |                    |       |                 |                        |  |  |  |

| bit 12-2                                                             | Unimplemen         | ted: Read as '   | 0'            |                    |       |                 |                        |  |  |  |

| bit 1                                                                | <b>U1EIE:</b> UART | 1 Error Interru  | pt Enable bit |                    |       |                 |                        |  |  |  |

|                                                                      |                    | request is enab  |               |                    |       |                 |                        |  |  |  |

|                                                                      | •                  | request is not e |               | <i>(</i> <b>)</b>  |       |                 |                        |  |  |  |

| bit 0                                                                |                    | /M1 Fault B Inte | -             | bit <sup>(1)</sup> |       |                 |                        |  |  |  |

|                                                                      | •                  | request has occ  |               |                    |       |                 |                        |  |  |  |

|                                                                      | 0 = Interrupt r    | request has not  | occurred      |                    |       |                 |                        |  |  |  |

| Note 1: This                                                         | bit is available   | e in dsPIC(16/3  | 2)MC102/104   | devices only.      |       |                 |                        |  |  |  |

#### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0     | U-0    | U-0    | U-0    | U-0 | U-0 | U-0 | U-0   |

|---------|--------|--------|--------|-----|-----|-----|-------|

| —       | —      | —      | —      | —   | —   | —   | —     |

| bit 15  |        |        |        |     |     |     | bit 8 |

|         |        |        |        |     |     |     |       |

| U-0     | R/W-1  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0   |

| —       | IC3IP2 | IC3IP1 | IC3IP0 | —   | —   | —   | —     |

| bit 7   |        |        |        |     |     |     | bit 0 |

|         |        |        |        |     |     |     |       |

| Legend: |        |        |        |     |     |     |       |

#### REGISTER 7-23: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

|     | iend: |

|-----|-------|

| LCC | ienu. |

|     |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                          |

|----------|---------------------------------------------------------------------|

| bit 6-4  | IC3IP<2:0>: External Interrupt 3 Priority bits                      |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt)          |

|          | •                                                                   |

|          | •                                                                   |

|          | •<br>001 - Interrupt in Priority 1                                  |

|          | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled |

|          |                                                                     |

| bit 3-0  | Unimplemented: Read as '0'                                          |

#### REGISTER 7-24: IPC14: INTERRUPT PRIORITY CONTROL REGISTER 14

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1                  | R/W-0                  | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|-------|------------------------|------------------------|------------------------|-----|-----|-----|-------|

| —     | PWM1IP2 <sup>(1)</sup> | PWM1IP1 <sup>(1)</sup> | PWM1IP0 <sup>(1)</sup> | -   | —   | —   | —     |

| bit 7 |                        |                        |                        |     |     |     | bit 0 |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

| bit 15-7 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 6-4  | PWM1IP<2:0>: PWM1 Interrupt Priority bits <sup>(1)</sup>   |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

| bit 3-0  | Unimplemented: Read as '0'                                 |

|          |                                                            |

Note 1: These bits are available in dsPIC(16/32)MC10X devices only.

| U-0           | U-0           | U-0                                  | U-0             | U-0                                | U-0 | U-0                | U-0   |

|---------------|---------------|--------------------------------------|-----------------|------------------------------------|-----|--------------------|-------|

| —             |               | _                                    | —               |                                    | —   |                    |       |

| bit 15        |               |                                      |                 |                                    |     |                    | bit 8 |

|               |               |                                      |                 |                                    |     |                    |       |

| U-0           | R/W-1         | R/W-0                                | R/W-0           | U-0                                | U-0 | U-0                | U-0   |

| —             | CTMUIP2       | CTMUIP1                              | CTMUIP0         | —                                  | —   | —                  | _     |

| bit 7         |               |                                      |                 |                                    |     |                    | bit 0 |

|               |               |                                      |                 |                                    |     |                    |       |

| Legend:       |               |                                      |                 |                                    |     |                    |       |

| R = Readabl   | e bit         | W = Writable bit                     |                 | U = Unimplemented bit, read as '0' |     |                    |       |

| -n = Value at | POR           | '1' = Bit is set                     |                 | '0' = Bit is cleared               |     | x = Bit is unknown |       |

|               |               |                                      |                 |                                    |     |                    |       |

| bit 15-7      | Unimplemen    | ted: Read as '                       | 0'              |                                    |     |                    |       |

| bit 6-4       | CTMUIP<2:0    | >: CTMU Interr                       | upt Priority bi | ts                                 |     |                    |       |

|               | 111 = Interru | pt is Priority 7 (                   | highest priorit | y interrupt)                       |     |                    |       |

|               | •             |                                      |                 |                                    |     |                    |       |

|               | •             |                                      |                 |                                    |     |                    |       |

|               | •             |                                      |                 |                                    |     |                    |       |

|               |               | pt is Priority 1<br>pt source is dis | abled           |                                    |     |                    |       |

| bit 3-0       | Unimplemen    | ted: Read as '                       | 0'              |                                    |     |                    |       |

|               |               |                                      |                 |                                    |     |                    |       |

#### REGISTER 7-27: IPC19: INTERRUPT PRIORITY CONTROL REGISTER 19

#### 9.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 9.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

#### 9.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

#### 9.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this may not be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the UART module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the UART module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 9.4 Peripheral Module Disable

The Peripheral Module Disable (PMDx) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMDx control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is enabled only if both the associated bit in the PMDx register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMDx register by default.

**Note:** If a PMDx bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMDx bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

## 10.4.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

#### 10.4.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |  |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                     |  |  |  |  |  |  |  |

|       | See MPLAB IDE Help for more information.                                                         |  |  |  |  |  |  |  |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

#### 10.4.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

#### 10.4.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

| U-0          | U-0                        | U-0              | R/W-0                                    | R/W-0          | R/W-0                    | R/W-0                   | R/W-0 |  |

|--------------|----------------------------|------------------|------------------------------------------|----------------|--------------------------|-------------------------|-------|--|

| —            | —                          | —                |                                          |                | RP21R<4:0> <sup>(1</sup> | )                       |       |  |

| bit 15       |                            |                  |                                          |                |                          |                         | bit 8 |  |

|              |                            |                  |                                          |                |                          |                         |       |  |

| U-0          | U-0                        | U-0              | R/W-0                                    | R/W-0          | R/W-0                    | R/W-0                   | R/W-0 |  |

| —            | —                          | —                |                                          |                | RP20R<4:0> <sup>(1</sup> | 1)                      |       |  |

| bit 7        |                            |                  |                                          |                |                          |                         | bit 0 |  |

|              |                            |                  |                                          |                |                          |                         |       |  |

| Legend:      |                            |                  |                                          |                |                          |                         |       |  |

| R = Readab   | le bit                     | W = Writable     | e bit U = Unimplemented bit, read as '0' |                |                          |                         |       |  |

| -n = Value a | t POR                      | '1' = Bit is set | '0' = Bit is cleared                     |                |                          | x = Bit is unknown      |       |  |

|              |                            |                  |                                          |                |                          |                         |       |  |

| bit 15-13    | Unimplemen                 | ted: Read as '   | 0'                                       |                |                          |                         |       |  |

| bit 12-8     | RP21R<4:0>                 | Peripheral Ou    | tput Function                            | is Assigned to | RP21 Output F            | Pin bits <sup>(1)</sup> |       |  |

|              | (see Table 10              | -2 for periphera | al function nur                          | mbers)         |                          |                         |       |  |

| bit 7-5      | Unimplemented: Read as '0' |                  |                                          |                |                          |                         |       |  |

| bit 4-0      | -                          |                  |                                          | is Assigned to | RP20 Output F            | Pin bits <sup>(1)</sup> |       |  |

|              |                            | -2 for periphera | -                                        | •              | 20 0 0 0 0 0 0 0 0       |                         |       |  |

|              |                            |                  |                                          | 110010/        |                          |                         |       |  |

#### REGISTER 10-21: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10

Note 1: These bits are available in dsPIC33FJ32(GP/MC)104 devices only.

#### REGISTER 10-22: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0           | U-0               | U-0              | R/W-0                                  | R/W-0                         | R/W-0                    | R/W-0                   | R/W-0 |  |

|---------------|-------------------|------------------|----------------------------------------|-------------------------------|--------------------------|-------------------------|-------|--|

| _             |                   | —                |                                        |                               | RP23R<4:0> <sup>(1</sup> | )                       |       |  |

| bit 15        | Ŀ                 |                  |                                        |                               |                          |                         | bit 8 |  |

|               |                   |                  |                                        |                               |                          |                         |       |  |

| U-0           | U-0               | U-0              | R/W-0                                  | R/W-0                         | R/W-0                    | R/W-0                   | R/W-0 |  |

| —             | —                 | —                |                                        |                               | RP22R<4:0> <sup>(1</sup> | )                       |       |  |

| bit 7         | ÷                 |                  |                                        |                               |                          |                         | bit 0 |  |

|               |                   |                  |                                        |                               |                          |                         |       |  |

| Legend:       |                   |                  |                                        |                               |                          |                         |       |  |

| R = Readab    | le bit            | W = Writable     | Dit U = Unimplemented bit, read as '0' |                               |                          |                         |       |  |

| -n = Value at | t POR             | '1' = Bit is set |                                        | 0' = Bit is cleared $x = Bit$ |                          |                         | nown  |  |

|               |                   |                  |                                        |                               |                          |                         |       |  |

| bit 15-13     | Unimplemen        | ted: Read as '   | 0'                                     |                               |                          |                         |       |  |

| bit 12-8      | RP23R<4:0>        | : Peripheral Ou  | tput Function                          | is Assigned to                | RP23 Output F            | Pin bits <sup>(1)</sup> |       |  |

|               | (see Table 10     | -2 for periphera | al function nu                         | mbers)                        |                          |                         |       |  |

| bit 7-5       | Unimplemen        | ted: Read as '   | 0'                                     |                               |                          |                         |       |  |

| bit 4-0       | RP22R<4:0>        | : Peripheral Ou  | tput Function                          | is Assigned to                | RP22 Output F            | Pin bits <sup>(1)</sup> |       |  |

|               |                   | -2 for periphera |                                        |                               |                          |                         |       |  |

| Note 1: ⊺     | hese bits are ava | ilable in dePIC  | 33E 132/CD/N                           | AC)104 devices                | only                     |                         |       |  |

|               | nese bits ale ava |                  | 551 552(GF/N                           |                               | only.                    |                         |       |  |

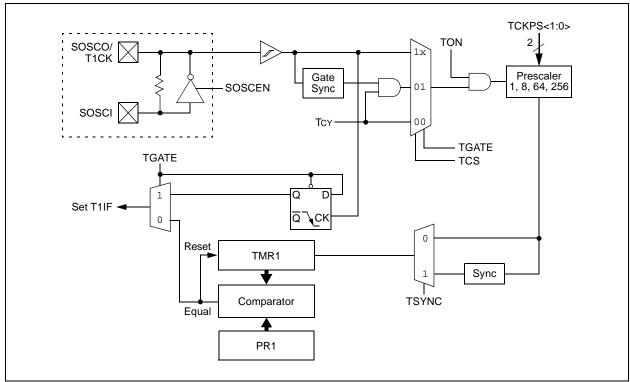

#### 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 11-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Load the timer value into the TMR1 register.

- 2. Load the timer period value into the PR1 register.

- 3. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 4. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 5. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

- 7. Set the TON bit (= 1) in the T1CON register.

#### FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

#### REGISTER 20-3: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT REGISTER (CONTINUED)

| <b>h</b> it 0 0 | CELCECA 200 - Mark A lanut Calast hits |

|-----------------|----------------------------------------|

| bit 3-0         | SELSRCA<3:0>: Mask A Input Select bits |

|                 | 1111 = Reserved                        |

|                 | 1110 = Reserved                        |

|                 | 1101 = Reserved                        |

|                 | 1100 = Reserved                        |

|                 | 1011 = Reserved                        |

|                 | 1010 = Reserved                        |

|                 | 1001 = Reserved                        |

|                 | 1000 = Reserved                        |

|                 | 0111 = Reserved                        |

|                 | 0110 = Reserved                        |

|                 | 0101 = PWM1H3                          |

|                 | 0100 = PWM1L3                          |

|                 | 0011 = PWM1H2                          |

|                 | 0010 = PWM1L2                          |

|                 | 0001 = PWM1H1                          |

|                 | 0000 = PWM1L1                          |

|                 |                                        |

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     |       | —     | —     | —     | —     | _     |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

YRONE3

YRONE2

YRONE1

YRONE0

#### REGISTER 21-4: RTCVAL (WHEN RTCPTR<1:0> = 11): RTCC YEAR VALUE REGISTER<sup>(1)</sup>

YRTEN0

| bit 7             |                  |                        |                              | bit 0 |  |

|-------------------|------------------|------------------------|------------------------------|-------|--|

|                   |                  |                        |                              |       |  |

| Legend:           |                  |                        |                              |       |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | implemented bit, read as '0' |       |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown           |       |  |

| bit 15-8 | Unimplemented: Read as '0'                                       |

|----------|------------------------------------------------------------------|

| bit 7-4  | YRTEN<3:0>: Binary Coded Decimal Value of Year's Tens Digit bits |

|          | Contains a value from 0 to 9.                                    |

| bit 3-0  | YRONE<3:0>: Binary Coded Decimal Value of Year's Ones Digit bits |

|          | Contains a value from 0 to 9.                                    |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

YRTEN1

YRTEN3

YRTEN2

#### **REGISTER 21-5: RTCVAL (WHEN RTCPTR<1:0> = 10): RTCC MONTH AND DAY VALUE REGISTER<sup>(1)</sup>**

| U-0    | U-0 | U-0 | R-x     | R-x     | R-x     | R-x     | R-x     |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                         |

|-----------|--------------------------------------------------------------------|

| bit 12    | MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit      |

|           | Contains a value of 0 or 1.                                        |

| bit 11-8  | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits |

|           | Contains a value from 0 to 9.                                      |

| bit 7-6   | Unimplemented: Read as '0'                                         |

| bit 5-4   | DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit bits   |

|           | Contains a value from 0 to 3.                                      |

| bit 3-0   | DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits   |

|           | Contains a value from 0 to 9.                                      |

|           |                                                                    |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

| Bit Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCP         | General Segment Code-Protect bit                                                                                                                                                                                                                                                                                                                                                                                    |

|             | <ul><li>1 = User program memory is not code-protected</li><li>0 = Code protection is enabled for the entire program memory space</li></ul>                                                                                                                                                                                                                                                                          |

| GWRP        | General Segment Write-Protect bit                                                                                                                                                                                                                                                                                                                                                                                   |

|             | <ul><li>1 = User program memory is not write-protected</li><li>0 = User program memory is write-protected</li></ul>                                                                                                                                                                                                                                                                                                 |

| IESO        | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Starts up device with FRC, then automatically switches to the user-selected oscillator source when ready</li> <li>0 = Starts up device with user-selected oscillator source</li> </ul>                                                                                                                                                               |

| PWMLOCK     | PWM Lock Enable bit                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | <ul><li>1 = Certain PWM registers may only be written after a key sequence</li><li>0 = PWM registers may be written without a key sequence</li></ul>                                                                                                                                                                                                                                                                |

| WDTWIN<1:0> | Watchdog Timer Window Select bits<br>11 = WDT window is 24% of WDT period<br>10 = WDT window is 37.5% of WDT period<br>01 = WDT window is 50% of WDT period<br>00 = WDT window is 75% of WDT period                                                                                                                                                                                                                 |

| FNOSC<2:0>  | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Reserved; do not use<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Secondary Oscillator (SOSC)<br>011 = Primary Oscillator with PLL module (MS + PLL, EC + PLL)<br>010 = Primary Oscillator (MS, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N and PLL module (FRCDIVN + PLL)<br>000 = Fast RC Oscillator (FRC) |

| FCKSM<1:0>  | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                   |

| IOL1WAY     | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                |

| OSCIOFNC    | OSC2 Pin Function bit (except in MS and HS modes)<br>1 = OSC2 is a clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                    |

| POSCMD<1:0> | Primary Oscillator Mode Select bits         11 = Primary Oscillator is disabled         10 = HS Crystal Oscillator mode (10 MHz-32 MHz)         01 = MS Crystal Oscillator mode (3 MHz-10 MHz)         00 = EC (External Clock) mode (DC-32 MHz)                                                                                                                                                                    |

| FWDTEN      | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled; clearing the SWDTEN bit in the RCON register will have no effect)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                          |

| WINDIS      | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                      |

#### TABLE 23-4: dsPIC33F CONFIGURATION BITS DESCRIPTION

| Base<br>Instr<br># | Assembly<br>Mnemonic |       | Assembly Syntax                | Description                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-------|--------------------------------|------------------------------------------|---------------|----------------|--------------------------|

| 1                  | ADD                  | ADD   | Acc                            | Add Accumulators                         | 1             | 1              | OA,OB,SA,SB              |

|                    |                      | ADD   | f                              | f = f + WREG                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | f,WREG                         | WREG = f + WREG                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | #lit10,Wn                      | Wd = lit10 + Wd                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,Ws,Wd                       | Wd = Wb + Ws                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,#lit5,Wd                    | Wd = Wb + lit5                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wso,#Slit4,Acc                 | 16-bit Signed Add to Accumulator         | 1             | 1              | OA,OB,SA,SB              |

| 2                  | ADDC                 | ADDC  | f                              | f = f + WREG + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | f,WREG                         | WREG = f + WREG + (C)                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | #lit10,Wn                      | Wd = Iit10 + Wd + (C)                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,Ws,Wd                       | Wd = Wb + Ws + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,#lit5,Wd                    | Wd = Wb + lit5 + (C)                     | 1             | 1              | C,DC,N,OV,Z              |

| 3                  | AND                  | AND   | f                              | f = f .AND. WREG                         | 1             | 1              | N,Z                      |

|                    |                      | AND   | f,WREG                         | WREG = f .AND. WREG                      | 1             | 1              | N,Z                      |

|                    |                      | AND   | #lit10,Wn                      | Wd = lit10 .AND. Wd                      | 1             | 1              | N,Z                      |

|                    |                      | AND   | Wb,Ws,Wd                       | Wd = Wb .AND. Ws                         | 1             | 1              | N,Z                      |

|                    |                      | AND   | Wb,#lit5,Wd                    | Wd = Wb .AND. lit5                       | 1             | 1              | N,Z                      |

| 4                  | ASR                  | ASR   | f                              | f = Arithmetic Right Shift f             | 1             | 1              | C,N,OV,Z                 |

| •                  | 11010                | ASR   | f,WREG                         | WREG = Arithmetic Right Shift f          | 1             | 1              | C,N,OV,Z                 |

|                    | ASR                  | Ws,Wd | Wd = Arithmetic Right Shift Ws | 1                                        | 1             | C,N,OV,Z       |                          |

|                    |                      | ASR   | Wb,Wns,Wnd                     | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1              | N,Z                      |

|                    |                      | ASR   | Wb,#lit5,Wnd                   | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1              | N,Z                      |

| 5                  | BCLR                 | BCLR  | f,#bit4                        | Bit Clear f                              | 1             | 1              | None                     |

| 0                  | DCDIC                | BCLR  | Ws,#bit4                       | Bit Clear Ws                             | 1             | 1              | None                     |

| 6                  | BRA                  | BRA   | C,Expr                         | Branch if Carry                          | 1             | 1 (2)          | None                     |

| 0                  | DIA                  | BRA   |                                | Branch if greater than or equal          | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | GE, Expr                       | Branch if unsigned greater than or equal | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | GEU, Expr                      | Branch if greater than                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | GT, Expr                       | Branch if unsigned greater than          | 1             | 1 (2)          | None                     |

|                    |                      |       | GTU, Expr                      | Branch if less than or equal             | 1             | . ,            | None                     |

|                    |                      | BRA   | LE, Expr                       |                                          |               | 1 (2)          |                          |

|                    |                      | BRA   | LEU, Expr                      | Branch if unsigned less than or equal    | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | LT, Expr                       | Branch if less than                      | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | LTU, Expr                      | Branch if unsigned less than             | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | N,Expr                         | Branch if Negative                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | NC,Expr                        | Branch if Not Carry                      | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | NN,Expr                        | Branch if Not Negative                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | NOV, Expr                      | Branch if Not Overflow                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | NZ,Expr                        | Branch if Not Zero                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | OA,Expr                        | Branch if Accumulator A overflow         | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | OB,Expr                        | Branch if Accumulator B overflow         | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | OV,Expr                        | Branch if Overflow                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | SA,Expr                        | Branch if Accumulator A saturated        | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | SB,Expr                        | Branch if Accumulator B saturated        | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | Expr                           | Branch Unconditionally                   | 1             | 2              | None                     |

|                    |                      | BRA   | Z,Expr                         | Branch if Zero                           | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | Wn                             | Computed Branch                          | 1             | 2              | None                     |

| 7                  | BSET                 | BSET  | f,#bit4                        | Bit Set f                                | 1             | 1              | None                     |

|                    |                      | BSET  | Ws,#bit4                       | Bit Set Ws                               | 1             | 1              | None                     |

| 8                  | BSW                  | BSW.C | Ws,Wb                          | Write C bit to Ws <wb></wb>              | 1             | 1              | None                     |

|                    | 1                    | BSW.Z | Ws,Wb                          | Write Z bit to Ws <wb></wb>              | 1             | 1              | None                     |

#### TABLE 24-2: INSTRUCTION SET OVERVIEW

#### 25.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 25.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 25.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 25.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 25.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

| DC CHARAC        | TERISTICS              |                          | (unless oth | <b>perating Co</b><br><b>nerwise state</b><br>emperature | <b>0V to 3.6V</b><br>≤ +85°C for Industrial<br>≤ +125°C for Extended |                                                |  |

|------------------|------------------------|--------------------------|-------------|----------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------|--|

| Parameter<br>No. | Typical <sup>(1)</sup> | Max                      | Units       |                                                          |                                                                      | Conditions                                     |  |

| Power-Down       | Current (IPD)          | <sup>(2)</sup> – dsPIC3  | 3FJ16(GP/M  | C)10X Devic                                              | es                                                                   |                                                |  |

| DC60d            | 27                     | 250                      | μA          | -40°C                                                    |                                                                      |                                                |  |

| DC60a            | 32                     | 250                      | μA          | +25°C                                                    | 3.3∨                                                                 | Base Power-Down Current <sup>(3,4)</sup>       |  |

| DC60b            | 43                     | 250                      | μA          | +85°C                                                    | 3.3V                                                                 | Base Power-Down Current                        |  |

| DC60c            | 150                    | 500                      | μA          | +125°C                                                   |                                                                      |                                                |  |

| DC61d            | 420                    | 600                      | μA          | -40°C                                                    |                                                                      |                                                |  |

| DC61a            | 420                    | 600                      | μA          | +25°C                                                    |                                                                      | Watchdog Timer Current: ∆IwDT <sup>(3,5)</sup> |  |

| DC61b            | 530                    | 750                      | μA          | +85°C                                                    | 3.3V                                                                 |                                                |  |

| DC61c            | 620                    | 900                      | μA          | +125°C                                                   |                                                                      |                                                |  |

| Power-Down       | Current (IPD)          | ( <sup>2)</sup> – dsPIC3 | 3FJ32(GP/M  | C)10X Devic                                              | es                                                                   |                                                |  |

| DC60d            | 27                     | 250                      | μA          | -40°C                                                    |                                                                      |                                                |  |

| DC60a            | 32                     | 250                      | μA          | +25°C                                                    | 3.3V                                                                 | Base Power-Down Current <sup>(3,4)</sup>       |  |

| DC60b            | 43                     | 250                      | μA          | +85°C                                                    | 3.3V                                                                 | base Fower-Down Current                        |  |

| DC60c            | 150                    | 500                      | μA          | +125°C                                                   |                                                                      |                                                |  |

| DC61d            | 420                    | 600                      | μA          | -40°C                                                    |                                                                      |                                                |  |

| DC61a            | 420                    | 600                      | μA          | +25°C                                                    |                                                                      | Watchdog Timer Current: ∆IwDT <sup>(3,5)</sup> |  |

| DC61b            | 530                    | 750                      | μA          | +85°C                                                    | 3.3V                                                                 |                                                |  |

| DC61c            | 620                    | 900                      | μA          | +125°C                                                   |                                                                      |                                                |  |

#### TABLE 26-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** Data in the Typical column is at 3.3V, +25°C unless otherwise stated.

2: IPD (Sleep) current is measured as follows:

- CPU core is off, oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- External Secondary Oscillator (SOSC) is disabled (i.e., SOSCO and SOSCI pins are configured as digital I/O inputs)

- · All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all ones)

- VREGS bit (RCON<8>) = 1 (i.e., core regulator is set to stand-by while the device is in Sleep mode)

- On applicable devices, RTCC is disabled, plus the VREGS bit (RCON<8>) = 1

- **3:** The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: These currents are measured on the device containing the most memory in this family.

- 5: These parameters are characterized, but not tested in manufacturing.

| DC CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |         |                    |         |         |                                                            |  |

|--------------------|--------|-----------------------------------------------------------------------|---------|--------------------|---------|---------|------------------------------------------------------------|--|

|                    | RAUIER | 131163                                                                | Operati | ng tempe           | erature |         | $\leq$ TA $\leq$ +85°C for Industrial                      |  |

|                    | 1      |                                                                       |         |                    |         | -40°C : | $\leq$ TA $\leq$ +125°C for Extended                       |  |

| Param<br>No.       | Symbol | Characteristic <sup>(3)</sup>                                         | Min     | Typ <sup>(1)</sup> | Max     | Units   | Conditions                                                 |  |

|                    |        | Program Flash Memory                                                  |         |                    |         |         |                                                            |  |

| D130a              | Eр     | Cell Endurance                                                        | 10,000  | —                  | —       | E/W     | -40°C to +125°C                                            |  |