Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp102t-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

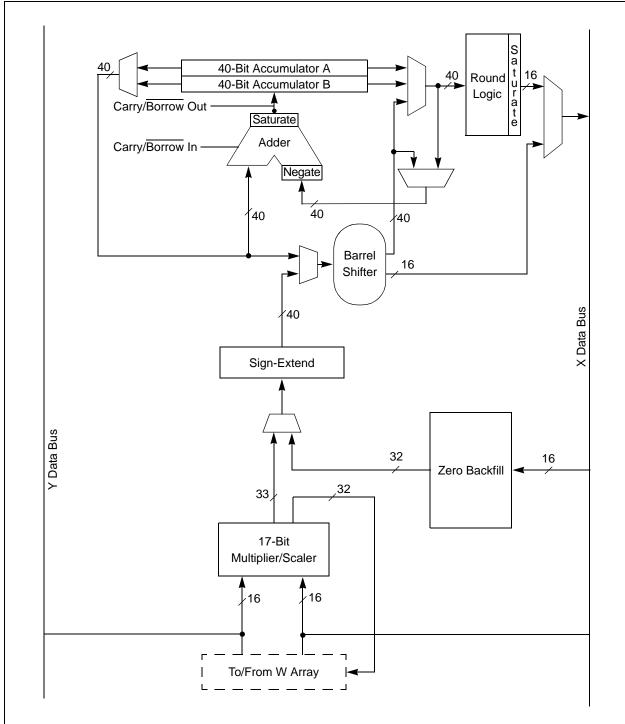

### FIGURE 3-3: DSP ENGINE BLOCK DIAGRAM

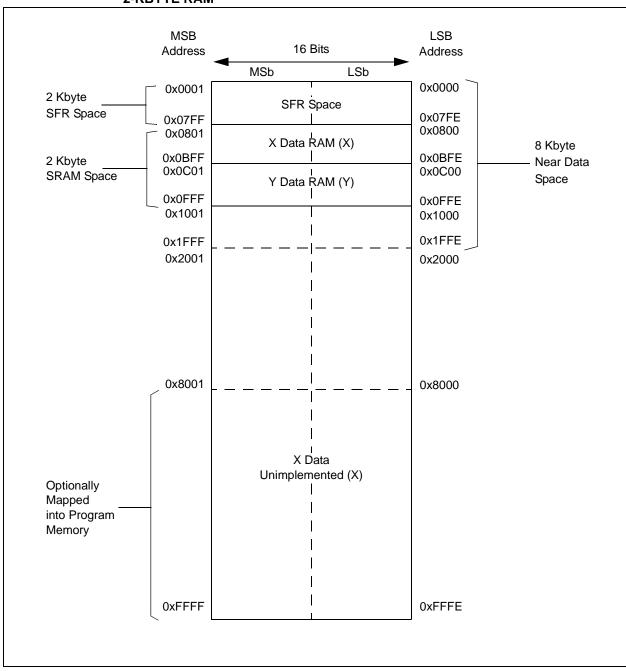

# FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJ32(GP/MC)101/102/104 DEVICES WITH 2-KBYTE RAM

#### 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY. N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All Effective Addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, although the implemented memory locations vary by device. NOTES:

### 6.3 POR

A POR circuit ensures the device is reset from poweron. The POR circuit is active until VDD crosses the VPOR threshold and the delay, TPOR, has elapsed. The delay, TPOR, ensures that the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to **Section 26.0** "**Electrical Characteristics**" for details.

The Power-on Reset (POR) status bit in the Reset Control (RCON<0>) register is set to indicate the Power-on Reset.

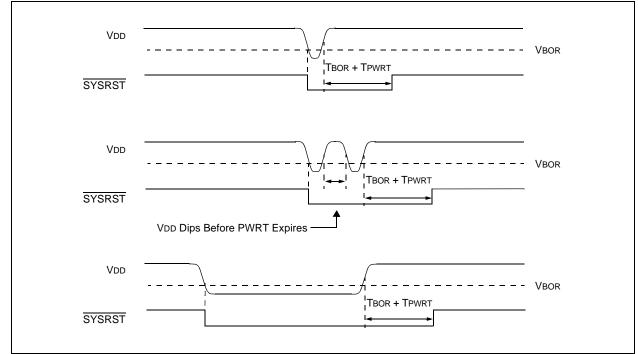

#### 6.4 BOR and PWRT

The on-chip regulator has a BOR circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses the VBOR threshold and the delay, TBOR, has elapsed. The delay, TBOR, ensures the voltage regulator output becomes stable.

The Brown-out Reset (BOR) status bit in the Reset Control (RCON<1>) register is set to indicate the Brown-out Reset.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The Power-up Timer (PWRT) provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

Refer to **Section 23.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The Reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point.

#### FIGURE 6-3: BROWN-OUT RESET SITUATIONS

| U-0                            | R/W-1                                                                                                                          | R/W-0                                | R/W-0             | U-0             | R/W-1             | R/W-0           | R/W-0          |  |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------|-----------------|-------------------|-----------------|----------------|--|--|--|--|--|

| —                              | U1RXIP2                                                                                                                        | U1RXIP1                              | U1RXIP0           | —               | SPI1IP2           | SPI1IP1         | SPI1IP0        |  |  |  |  |  |

| bit 15                         |                                                                                                                                |                                      |                   |                 |                   |                 | bit            |  |  |  |  |  |

|                                | D 444                                                                                                                          | DAMA                                 | DAMA              |                 | D 44/ 4           | DAMA            | DAMO           |  |  |  |  |  |

| U-0                            | R/W-1<br>SPI1EIP2                                                                                                              | R/W-0<br>SPI1EIP1                    | R/W-0<br>SPI1EIP0 | U-0             | R/W-1<br>T3IP2    | R/W-0<br>T3IP1  | R/W-0<br>T3IP0 |  |  |  |  |  |

| bit 7                          | OTTEN 2                                                                                                                        | OFFICIENT                            | OFFICIENT         |                 | 10112             | 1011 1          | bit            |  |  |  |  |  |

|                                |                                                                                                                                |                                      |                   |                 |                   |                 | _              |  |  |  |  |  |

| <b>Legend:</b><br>R = Readable | hit.                                                                                                                           |                                      | <b>b</b> :+       |                 | manted bit read   |                 |                |  |  |  |  |  |

|                                |                                                                                                                                | W = Writable                         |                   | -               | emented bit, read |                 |                |  |  |  |  |  |

| -n = Value at                  | POR                                                                                                                            | '1' = Bit is set                     |                   | '0' = Bit is cl | eared             | x = Bit is unkı | lown           |  |  |  |  |  |

| bit 15                         | Unimplemen                                                                                                                     | ted: Read as '                       | 0'                |                 |                   |                 |                |  |  |  |  |  |

| bit 14-12                      | -                                                                                                                              |                                      |                   | Priority bits   |                   |                 |                |  |  |  |  |  |

|                                | <b>U1RXIP&lt;2:0&gt;:</b> UART1 Receiver Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                |                                                                                                                                |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •<br>001 = Interrupt is Priority 1                                                                                             |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                |                                                                                                                                | pt is Friding 1<br>pt source is dis  | abled             |                 |                   |                 |                |  |  |  |  |  |

| bit 11                         |                                                                                                                                | -                                    |                   |                 |                   |                 |                |  |  |  |  |  |

| bit 10-8                       | Unimplemented: Read as '0'<br>SPI1IP<2:0>: SPI1 Event Interrupt Priority bits                                                  |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                     |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              | pt le 1 llell, j 1 l                 | (geet pe          | .,              |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                |                                                                                                                                |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                            |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

| bit 7                          |                                                                                                                                | ited: Read as '                      |                   |                 |                   |                 |                |  |  |  |  |  |

| bit 6-4                        | -                                                                                                                              |                                      |                   | ty hite         |                   |                 |                |  |  |  |  |  |

|                                | SPI1EIP<2:0>: SPI1 Error Interrupt Priority bits                                                                               |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul>                                                 |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                |                                                                                                                                |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | 001 = Interru                                                                                                                  | pt is Priority 1<br>pt source is dis | abled             |                 |                   |                 |                |  |  |  |  |  |

| bit 3                          |                                                                                                                                | ited: Read as '                      |                   |                 |                   |                 |                |  |  |  |  |  |

| bit 2-0                        | -                                                                                                                              | imer3 Interrupt                      |                   |                 |                   |                 |                |  |  |  |  |  |

| Dit 2-0                        |                                                                                                                                | pt is Priority 7                     | -                 | ty interrupt)   |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              | prist nonty /                        | (ingriest priorit | ly interrupt)   |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •<br>001 = Interrupt is Priority 1                                                                                             |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

### REGISTER 7-20: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|---------|-----|-----|-----|-----|---------|---------|---------|

|         |     | —   | _   | —   |         | —       | _       |

| bit 15  |     |     |     |     |         |         | bit 8   |

|         |     |     |     |     |         |         |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| —       | —   | —   | —   | —   | INT1IP2 | INT1IP1 | INT1IP0 |

| bit 7   |     |     |     |     |         |         | bit 0   |

|         |     |     |     |     |         |         |         |

| Logondi |     |     |     |     |         |         |         |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-3 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 2-0  | INT1IP<2:0>: External Interrupt 1 Priority bits            |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •<br>001 = Interrupt is Priority 1                         |

|          | 000 = Interrupt source is disabled                         |

#### REGISTER 7-21: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| U-0                                | R/W-1                | R/W-0                | R/W-0                                   | U-0                                | U-0 | U-0  | U-0   |

|------------------------------------|----------------------|----------------------|-----------------------------------------|------------------------------------|-----|------|-------|

| _                                  | T4IP2 <sup>(1)</sup> | T4IP1 <sup>(1)</sup> | T4IP0 <sup>(1)</sup>                    | —                                  | _   | _    | _     |

| bit 15                             |                      |                      |                                         |                                    |     |      | bit 8 |

|                                    |                      |                      |                                         |                                    |     |      |       |

| U-0                                | U-0                  | U-0                  | U-0                                     | U-0                                | U-0 | U-0  | U-0   |

| —                                  | —                    | —                    | —                                       | —                                  | —   | —    | —     |

| bit 7                              |                      |                      |                                         |                                    |     |      | bit 0 |

|                                    |                      |                      |                                         |                                    |     |      |       |

| Legend:                            |                      |                      |                                         |                                    |     |      |       |

| R = Readable I                     | bit                  | W = Writable         | bit                                     | U = Unimplemented bit, read as '0' |     |      |       |

| -n = Value at POR '1' = Bit is set |                      |                      | '0' = Bit is cleared x = Bit is unknown |                                    |     | nown |       |

|                                    |                      |                      |                                         |                                    |     |      |       |

| bit 15                             | Unimplemen           | ted: Read as '       | 0'                                      |                                    |     |      |       |

| bit 14-12 | T4IP<2:0>: Timer4 Interrupt Priority bits <sup>(1)</sup>   |

|-----------|------------------------------------------------------------|

|           | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|           | •                                                          |

|           | •                                                          |

|           | •                                                          |

|           | 001 = Interrupt is Priority 1                              |

|           | 000 = Interrupt source is disabled                         |

| bit 11-0  | Unimplemented: Read as '0'                                 |

|           |                                                            |

Note 1: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

#### **PMD Control Registers** 9.5

| R/W-0       U-0       R/W-0       U-0       R/W-0       U-0       R/W-0         I2C1MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0               | R/W-0               | R/W-0            | R/W-0                  | R/W-0          | U-0            | R/W-0     | U-0                  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|------------------|------------------------|----------------|----------------|-----------|----------------------|--|--|

| R/W-0       U-0       R/W-0       U-0       R/W-0       U-0       R/W-0         I2C1MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | T5MD <sup>(1)</sup> | T4MD <sup>(1)</sup> | T3MD             | T2MD                   | T1MD           | _              | PWM1MD    | _                    |  |  |

| I2C1MD       -       U1MD       -       SPI1MD       -       AD1MDf2         bit 7       bit       -       bit       bit       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       nn = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is disabled       0 = Timer7 module is disabled         bit 14       T4MD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer7 module is disabled       0 = Timer7 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is enabled         bit 14       T4MD: Timer2 Module Disable bit       1 = Timer2 module is enabled       0 = Timer7 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled         bit 11       Timer1 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15              | •                   |                  | 1                      |                |                |           | bit                  |  |  |

| I2C1MD       -       U1MD       -       SPI1MD       -       AD1MDf2         bit 7       bit       -       bit       bit       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       nn = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is disabled       0 = Timer7 module is disabled         bit 14       T4MD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer7 module is disabled       0 = Timer7 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is enabled         bit 14       T4MD: Timer2 Module Disable bit       1 = Timer2 module is enabled       0 = Timer7 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled         bit 11       Timer1 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                     |                  |                        |                |                |           |                      |  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 T5MD: Timer5 Module Disable bit <sup>(1)</sup><br>1 = Timer5 module is enabled<br>0 = Timer5 module is enabled<br>0 = Timer4 module is enabled<br>0 = Timer4 module is disabled<br>0 = Timer3 module is enabled<br>0 = Timer3 module is enabled<br>0 = Timer4 module Disable bit<br>1 = Timer2 Module Disable bit<br>1 = Timer2 Module Disable bit<br>1 = Timer2 module is disabled<br>0 = Timer4 module is enabled<br>0 = Timer7 module is enabled<br>0 = Timer7 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer1 module is disabled<br>0 = UART1 modul | R/W-0               | U-0                 | R/W-0            | U-0                    | R/W-0          | U-0            | U-0       | R/W-0                |  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>in = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 T5MD: Timer5 Module Disable bit <sup>(1)</sup><br>1 = Timer5 module is disabled<br>0 = Timer5 module is disabled<br>0 = Timer4 module is disabled<br>0 = Timer4 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is enabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is enabled<br>0 = Timer2 module is enabled<br>0 = Timer1 module is disabled<br>0 = Timer1 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is enabled<br>0 = Timer4 module is disabled<br>0 = UXM11 module is disabled<br>0 = UXM11 module is disabled<br>0 = UART1 module is disabled<br>0 = UART4 module i | I2C1MD              |                     | U1MD             |                        | SPI1MD         | _              | —         | AD1MD <sup>(2)</sup> |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         Dit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is enabled         0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 14       T4MD: Timer6 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is disabled         Dit 12       T2MD: Timer1 Module Disable bit       1 = Timer2 module is disabled       0 = Timer2 module is disabled         Dit 11       T1MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer4 module is disabled         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 11       T1MD: I2C1 Module Disable bit       1 = I2C1 module is disabled       0 = PWM1 module is disabled       0 = PWM1 module is disabled       0         Dit 10       Unimplemented: Read as '0'       0       0       0       0       0 <td>bit 7</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>bit</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 7               |                     |                  |                        |                |                |           | bit                  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         Dit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is enabled         0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 14       T4MD: Timer6 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is disabled         Dit 12       T2MD: Timer1 Module Disable bit       1 = Timer2 module is disabled       0 = Timer2 module is disabled         Dit 11       T1MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer4 module is disabled         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 11       T1MD: I2C1 Module Disable bit       1 = I2C1 module is disabled       0 = PWM1 module is disabled       0 = PWM1 module is disabled       0         Dit 10       Unimplemented: Read as '0'       0       0       0       0       0 <td>Legend:</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Legend:             |                     |                  |                        |                |                |           |                      |  |  |

| m = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer5 module is disabled         bit 14       TAMD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer4 module is disabled       0 = Timer4 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer3 module is disabled       0 = Timer3 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer3 module is disabled       0 = Timer3 module is disabled         bit 12       T2MD: Timer2 Module Disable bit       1 = Timer3 module is disabled       0 = Timer3 module is disabled         bit 12       T2MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 11       T1MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 10       Unimplemented: Read as '0'       0       0       0         bit 8       Unimplemented: Read as '0'       0       1 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 7       I2C1MD: I2C1 Module Disable bit       1 = I2C1 module is disabled       0 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 6       Unimplemented: Read as '0'       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                   | le bit              | W = Writable     | bit                    | U = Unimplem   | ented bit, rea | ad as '0' |                      |  |  |

| bit 15       T5MD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled         0 = Timer5 module is disabled         1 = Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer4 module is disabled         0 = Timer4 module is disabled         0 = Timer4 module is disabled         0 = Timer3 module is disabled         0 = Timer3 module is disabled         0 = Timer3 module is enabled         0 = Timer3 module is disabled         0 = Timer1 module Disable bit         1 = Timer1 module is disabled         0 = WM1MD: PVM1 Module Disable bit         1 = PWM1 module is disabled         0 = PVWM1 module is disabled         0 = PVW1 module is disabled         0 = VIM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -n = Value a        | t POR               | '1' = Bit is set | t                      | •              |                |           | nown                 |  |  |

| 1 = Timer5 module is disabled         0 = Timer5 module is enabled         0 = Timer4 Module Disable bit         1 = Timer4 module is enabled         0 = Timer4 module is enabled         0 = Timer3 module is enabled         0 = Timer3 module is disable bit         1 = Timer3 module is disabled         0 = Timer2 module is enabled         0 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 module is disabled         0 = PWM1 MD: PWM1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is enabled         0 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module Disable bit         1 = UART1 module is disabled         0 = UART1 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                     |                  |                        |                |                |           |                      |  |  |

| 0 = Timer5 module is enabled         bit 14       T4MD: Timer4 Module Disable bit         1 = Timer4 module is disabled         0 = Timer3 Module Disable bit         1 = Timer3 module is enabled         0 = Timer4 module is disabled         0 = Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer2 module is enabled         0 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWM1 module is disabled         0 = I2C1 Module Disable bit         1 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 15              | T5MD: Time          | r5 Module Disa   | ble bit <sup>(1)</sup> |                |                |           |                      |  |  |

| bit 14       T4MD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer4 module is disabled         0 = Timer4 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 module is disabled         0 = PWM1 module is disabled         0 = I2C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled <t< td=""><td></td><td>1 = Timer5 n</td><td>nodule is disabl</td><td>ed</td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     | 1 = Timer5 n        | nodule is disabl | ed                     |                |                |           |                      |  |  |

| 1 = Timer4 module is disabled         0 = Timer4 module is enabled         0 = Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer3 module is enabled         0 = Timer3 module is enabled         0 = Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer2 module is enabled         0 = Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWM1 module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module Disable bit         1 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled         0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     | 0 <b>= Timer5 n</b> | nodule is enable | ed                     |                |                |           |                      |  |  |

| 0 = Timer4 module is enabled         bit 13       T3MD: Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is enabled         0 = Timer3 module is enabled         0 = Timer2 module is enabled         0 = Timer2 module is enabled         0 = Timer1 module is disabled         0 = PWM1MD: PVW1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PUM1 module is disabled         0 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled         0 = UART1 module is enabled         0 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14              |                     |                  |                        |                |                |           |                      |  |  |

| bit 13       T3MD: Timer3 Module Disable bit         1 = Timer3 module is disabled       0 = Timer3 module is enabled         0 = Timer3 module is enabled       0 = Timer2 Module Disable bit         1 = Timer2 module is disabled       0 = Timer2 module is enabled         0 = Timer2 module is disabled       0 = Timer2 module is disabled         0 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is disabled       0 = PWM1 MD: PWM1 Module Disable bit         1 = PWM1 module is disabled       0 = PWM1 module is disabled         0 = PWM1 module is disabled       0 = PWM1 module is enabled         0 = PWM1 module is disabled       0 = PUM1 module is disabled         0 = PWM1 module is disabled       0 = I2C1 module is disabled         0 = I2C1 module is disabled       0 = I2C1 module is enabled         0 = I2C1 module is disabled       0 = I2C1 module is disabled         0 = UART1 module is disabled       0 = UART1 module is disabled         0 = UART1 module is disabled       0 = UART1 module is disabled         0 = UART1 module is disabled       0 = UART1 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                     |                  |                        |                |                |           |                      |  |  |

| 1 = Timer3 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is enabled         bit 11       T1MD: Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = Timer1 module is disabled         0 = Timer1 module is enabled         0 = Timer1 module is disabled         0 = Timer1 module is enabled         0 = Timer1 module is enabled         0 = Timer1 module is disabled         0 = Timer1 module is enabled         0 = Timer1 module is disabled         0 = PWM1MD: PWM1 Module Disable bit         1 = PVWM1 module is enabled         0 = PWM1 module is enabled         0 = PWM1 module is enabled         0 = VATI module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled         0 = UART1 module is enabled         0 = UART1 modu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | h:: 40              |                     |                  |                        |                |                |           |                      |  |  |

| 0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is enabled         bit 11       T1MD: Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWM1 MD: PWM1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module is disabled         0 = I2C1 module Disable bit         1 = UART1 Module Disable bit         1 = UART1 module is disabled         0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DIT 13              |                     |                  |                        |                |                |           |                      |  |  |

| bit 12 <b>T2MD</b> : Timer2 Module Disable bit         1 = Timer2 module is disabled       0 = Timer2 module is enabled         bit 11 <b>T1MD</b> : Timer1 Module Disable bit         1 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is enabled       0 = Timer1 module is disabled         0 = Timer1 module is enabled       0 = Timer1 module is enabled         bit 10 <b>Unimplemented:</b> Read as '0'         bit 3 <b>PWM1MD</b> : PWM1 Module Disable bit         1 = PWM1 module is enabled       0 = PWM1 module is enabled         bit 4 <b>Unimplemented:</b> Read as '0'         bit 5 <b>Unimplemented:</b> Read as '0'         bit 6 <b>Unimplemented:</b> Read as '0'         bit 7 <b>I2C1MD</b> : I2C1 Module Disable bit         1 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 6 <b>Unimplemented:</b> Read as '0'         bit 5 <b>U1MD</b> : UART1 Module Disable bit         1 = UART1 module is disabled       0 = UART1 module is enabled         bit 4 <b>Unimplemented:</b> Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |                     |                  |                        |                |                |           |                      |  |  |

| 1 = Timer2 module is disabled         0 = Timer2 module is enabled         bit 11       T1MD: Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = Timer1 module is enabled         bit 10       Unimplemented: Read as '0'         bit 9       PWM1MD: PWM1 Module Disable bit         1 = PWM1 module is disabled       0 = PWM1 module is disabled         0 = PWM1 module is disabled       0 = PWM1 module is enabled         bit 8       Unimplemented: Read as '0'         bit 7       I2C1 Module Disable bit         1 = I2C1 module is disabled       0 = I2C1 module is disabled         0 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 6       Unimplemented: Read as '0'         bit 5       U1MD: UART1 Module Disable bit         1 = UART1 module is disabled       0 = UART1 module is enabled         0 = UART1 module is enabled       0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 12              | T2MD: Time          | r2 Module Disa   | ble bit                |                |                |           |                      |  |  |

| bit 11 <b>T1MD:</b> Timer1 Module Disable bit<br>$1 = Timer1$ module is disabled<br>$0 = Timer1$ module is enabledbit 10 <b>Unimplemented:</b> Read as '0'bit 9 <b>PWM1MD:</b> PWM1 Module Disable bit<br>$1 = PWM1$ module is disabled<br>$0 = PWM1$ module is enabledbit 8 <b>Unimplemented:</b> Read as '0'bit 7 <b>I2C1MD:</b> I2C1 Module Disable bit<br>$1 = I2C1$ module is disabled<br>$0 = I2C1$ module is enabledbit 6 <b>Unimplemented:</b> Read as '0'bit 5 <b>U1MD:</b> UART1 Module Disable bit<br>$1 = UART1$ module is disabled<br>$0 = UART1$ module is disabled<br>bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | 1 = Timer2 n        | nodule is disabl | ed                     |                |                |           |                      |  |  |

| 1 = Timer1 module is disabled         0 = Timer1 module is enabled         0 = Timer1 module is enabled         0 = Timer1 module is enabled         0 = PWM1MD: PWM1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is enabled         0 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = UART1 Module Disable bit         1 = UART1 module is disabled         0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     | 0 = Timer2 n        | nodule is enable | ed                     |                |                |           |                      |  |  |

| 0 = Timer1 module is enabled         bit 10       Unimplemented: Read as '0'         bit 9       PWM1MD: PWM1 Module Disable bit         1 = PWM1 module is disabled       0 = PWM1 module is disabled         0 = PWM1 module is enabled       0 = PWM1 module is enabled         bit 8       Unimplemented: Read as '0'         bit 7       I2C1MD: I2C1 Module Disable bit         1 = I2C1 module is disabled       0 = I2C1 module is enabled         0 = I2C1 module is enabled       0 = I2C1 module is enabled         bit 6       Unimplemented: Read as '0'         bit 5       U1MD: UART1 Module Disable bit         1 = UART1 module is disabled       0 = UART1 module is enabled         bit 4       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 11              | T1MD: Time          | r1 Module Disa   | ble bit                |                |                |           |                      |  |  |

| bit 10       Unimplemented: Read as '0'         bit 9       PWM1MD: PWM1 Module Disable bit         1 = PWM1 module is disabled       0 = PWM1 module is enabled         bit 8       Unimplemented: Read as '0'         bit 7       I2C1MD: I2C1 Module Disable bit         1 = I2C1 module is disabled       0 = I2C1 module is disabled         0 = I2C1 module is enabled       0 = I2C1 module is enabled         bit 6       Unimplemented: Read as '0'         bit 5       U1MD: UART1 Module Disable bit         1 = UART1 module is disabled       0 = UART1 module is enabled         bit 4       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                     |                  |                        |                |                |           |                      |  |  |