Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp102t-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 PRODUCT FAMILIES

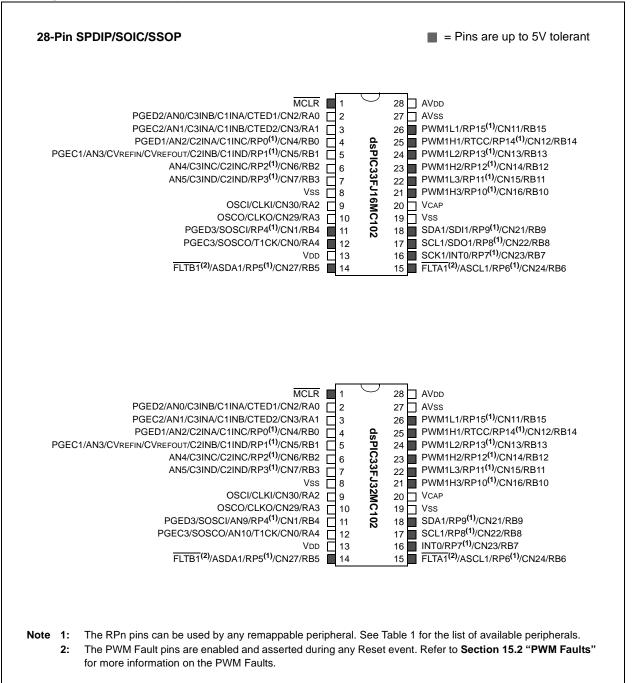

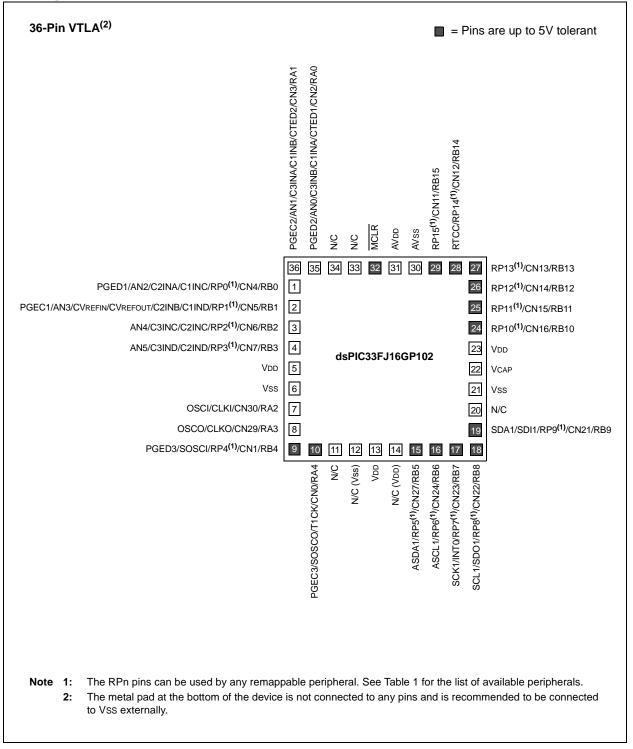

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. The following pages show their pinout diagrams.

|                  |      | rte)                  |              |                 | Rem                           | appa          | ble l          | Perip | herals                             | 5   | М                 |            | Ŋ                    |      |      |             |      |          |                                 |

|------------------|------|-----------------------|--------------|-----------------|-------------------------------|---------------|----------------|-------|------------------------------------|-----|-------------------|------------|----------------------|------|------|-------------|------|----------|---------------------------------|

| Device           | Pins | Program Flash (Kbyte) | RAM (Kbytes) | Remappable Pins | 16-bit Timer <sup>(1,2)</sup> | Input Capture | Output Compare | UART  | External Interrupts <sup>(3)</sup> | SPI | Motor Control PWM | PWM Faults | 10-Bit, 1.1 Msps ADC | RTCC | I²C™ | Comparators | CTMU | I/O Pins | Packages                        |

| dsPIC33FJ16GP101 | 18   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 13       | PDIP,<br>SOIC                   |

|                  | 20   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | SSOP                            |

| dsPIC33FJ16GP102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | _          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

| dsPIC33FJ16MC101 | 20   | 16                    | 1            | 10              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 1          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | PDIP,<br>SOIC,<br>SSOP          |

| dsPIC33FJ16MC102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

### TABLE 1:dsPIC33FJ16(GP/MC)101/102 DEVICE FEATURES

**Note 1:** Two out of three timers are remappable.

2: One pair can be combined to create one 32-bit timer.

**3**: Two out of three interrupts are remappable.

### **Pin Diagrams (Continued)**

### Pin Diagrams (Continued)

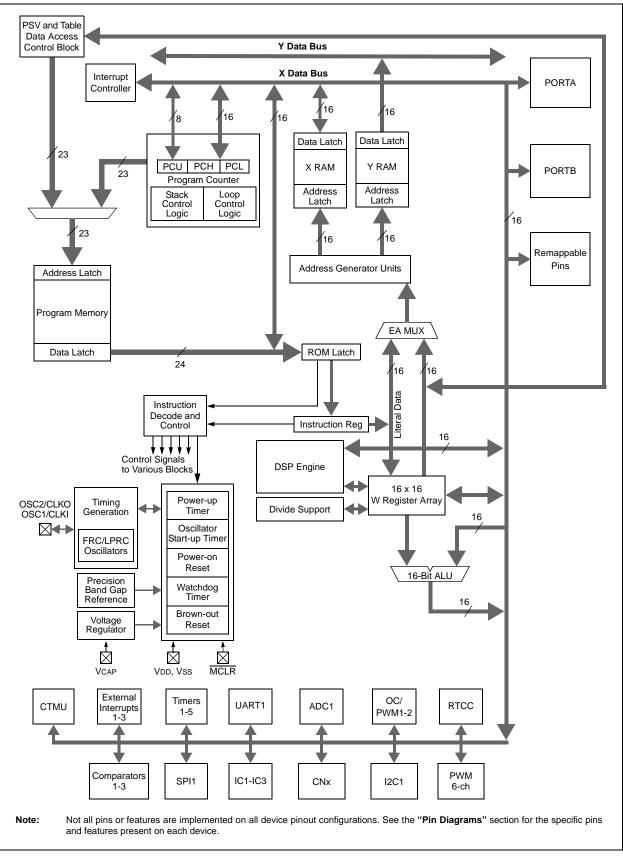

# FIGURE 1-1: dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 BLOCK DIAGRAM

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz < FIN < 8 MHz (for MSPLL mode) or 3 MHz < FIN < 8 MHz (for ECPLL mode) to comply with device PLL start-up conditions. HSPLL mode is not supported. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The fixed PLL settings of 4x after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can enable the PLL and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

### 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator is selected as a debugger, it automatically initializes all of the Analog-to-Digital input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in the register that correspond to the Analog-to-Digital pins that are initialized by MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain Analog-to-Digital pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all Analog-to-Digital pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternately, connect a 1k to 10k resistor between Vss and unused pins.

| U-0             | U-0                            | U-0                                   | R/W-0           | R/W-0               | R-0              | R-0              | R-0   |

|-----------------|--------------------------------|---------------------------------------|-----------------|---------------------|------------------|------------------|-------|

| —               | —                              | _                                     | US              | EDT <sup>(1)</sup>  | DL2              | DL1              | DL0   |

| bit 15          |                                |                                       |                 |                     |                  |                  | bit   |

| R/W-0           | R/W-0                          | R/W-1                                 | R/W-0           | R/C-0               | R/W-0            | R/W-0            | R/W-0 |

| SATA            | SATB                           | SATDW                                 | ACCSAT          | IPL3 <sup>(2)</sup> | PSV              | R/W-0            | IF    |

| bit 7           | SAID                           | SAIDW                                 | ACCOAT          | IF L3. 7            | F3V              | RND              | bit   |

|                 |                                |                                       |                 |                     |                  |                  | Dit   |

| Legend:         |                                | C = Clearable                         | e bit           |                     |                  |                  |       |

| R = Readabl     | e bit                          | W = Writable                          | bit             | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is cle | ared                           | 'x = Bit is unk                       | nown            | U = Unimple         | mented bit, read | d as '0'         |       |

| bit 15-13       | Unimplemen                     | ted: Read as '                        | 0'              |                     |                  |                  |       |

| bit 12          | -                              | tiply Unsigned                        |                 | ol bit              |                  |                  |       |

|                 |                                | ne multiplies a                       | •               |                     |                  |                  |       |

|                 | 0 = DSP engi                   | ne multiplies a                       | ire signed      |                     |                  |                  |       |

| bit 11          |                                | Loop Termina                          |                 |                     |                  |                  |       |

|                 | 1 = Terminate<br>0 = No effect | es executing Do                       | o loop at the e | nd of current lo    | oop iteration    |                  |       |

| bit 10-8        | DL<2:0>: DO                    | Loop Nesting                          | Level Status b  | its                 |                  |                  |       |

|                 | 111 <b>= 7</b> DO <b>lo</b>    | ops are active                        |                 |                     |                  |                  |       |

|                 | •                              |                                       |                 |                     |                  |                  |       |

|                 | •<br>001 = 1 DO lo             | on is activo                          |                 |                     |                  |                  |       |

|                 |                                | ops are active                        |                 |                     |                  |                  |       |

| bit 7           | SATA: ACCA                     | Saturation En                         | able bit        |                     |                  |                  |       |

|                 |                                | itor A saturatio                      |                 |                     |                  |                  |       |

|                 |                                | itor A saturatio                      |                 |                     |                  |                  |       |

| bit 6           |                                | Saturation En                         |                 |                     |                  |                  |       |

|                 |                                | tor B saturatio                       |                 |                     |                  |                  |       |

| bit 5           |                                |                                       |                 | ine Saturation      | Enable bit       |                  |       |

|                 |                                | ce write satura                       |                 |                     |                  |                  |       |

|                 |                                | ce write satura                       |                 |                     |                  |                  |       |

| bit 4           | ACCSAT: Acc                    | cumulator Satu                        | uration Mode S  | Select bit          |                  |                  |       |

|                 |                                | ration (super s                       |                 |                     |                  |                  |       |

| L:1 0           |                                | ration (normal                        | ,               | ··· (2)             |                  |                  |       |

| bit 3           |                                | terrupt Priority<br>rrupt Priority Le |                 |                     |                  |                  |       |

|                 |                                | rupt Priority Le                      | •               |                     |                  |                  |       |

| bit 2           |                                |                                       |                 | ace Enable bit      |                  |                  |       |

|                 |                                | space is visible                      |                 |                     |                  |                  |       |

|                 | -                              | space is not vi                       |                 | pace                |                  |                  |       |

| bit 1           |                                | ng Mode Sele                          |                 |                     |                  |                  |       |

|                 |                                | onventional) ro<br>(convergent)       |                 |                     |                  |                  |       |

| bit 0           | IF: Integer or                 | Fractional Mul                        | tiplier Mode S  | elect bit           |                  |                  |       |

|                 | -                              |                                       |                 | iply operations     |                  |                  |       |

|                 | 0 = Fractional                 | l mode is enab                        | led for DSP m   | nultiply operation  | ons              |                  |       |

### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## FIGURE 7-1: dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 INTERRUPT VECTOR TABLE

| 1                                 |                                            | 7                    |                                                        |

|-----------------------------------|--------------------------------------------|----------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction                   | 0x000000             |                                                        |

|                                   | Reset – GOTO Address                       | 0x000002             |                                                        |

|                                   | Reserved                                   | 0x000004             |                                                        |

|                                   | Oscillator Fail Trap Vector                | _                    |                                                        |

|                                   | Address Error Trap Vector                  | _                    |                                                        |

|                                   | Stack Error Trap Vector                    | _                    |                                                        |

|                                   | Math Error Trap Vector                     | _                    |                                                        |

|                                   | Reserved                                   | -                    |                                                        |

|                                   | Reserved                                   | _                    |                                                        |

|                                   | Reserved<br>Interrupt Vector 0             | 0x000014             |                                                        |

|                                   | Interrupt Vector 1                         | 0,000014             |                                                        |

|                                   |                                            | -                    |                                                        |

|                                   | ~                                          |                      |                                                        |

|                                   | ~                                          | _                    |                                                        |

|                                   | Interrupt Vector 52                        | 0x00007C             | (4)                                                    |

|                                   | Interrupt Vector 53                        | 0x00007E             | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ity                               | Interrupt Vector 54                        | 0x000080             |                                                        |

| iori                              | ~                                          |                      |                                                        |

| ā                                 | ~                                          |                      |                                                        |

| der                               | ~                                          |                      |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 116                       | 0x0000FC             |                                                        |

| ra                                | Interrupt Vector 117                       | 0x0000FE             |                                                        |

| atu                               | Reserved                                   | 0x000100             |                                                        |

| Z                                 | Reserved                                   | 0x000102             |                                                        |

| sing                              | Reserved                                   |                      |                                                        |

| eas                               | Oscillator Fail Trap Vector                |                      |                                                        |

| ecr                               | Address Error Trap Vector                  |                      |                                                        |

| ă                                 | Stack Error Trap Vector                    |                      |                                                        |

|                                   | Math Error Trap Vector                     |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Interrupt Vector 0                         | 0x000114             |                                                        |

|                                   | Interrupt Vector 1                         |                      |                                                        |

|                                   | ~                                          | 4                    |                                                        |

|                                   | ~                                          | 4                    |                                                        |

|                                   | ~<br>Interrupt Vector 52                   | 0x000470             | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   |                                            | 0x00017C             |                                                        |

|                                   | Interrupt Vector 53<br>Interrupt Vector 54 | 0x00017E<br>0x000180 |                                                        |

|                                   | ~                                          | 0000180              |                                                        |

|                                   | ~                                          | -                    |                                                        |

|                                   | ~                                          | _                    |                                                        |

|                                   | -<br>Interrupt Vector 116                  | -                    |                                                        |

|                                   | Interrupt Vector 117                       | 0x0001FE             |                                                        |

| *                                 | Start of Code                              | 0x000200             | L                                                      |

|                                   |                                            |                      |                                                        |

| Note 1: See                       | e Table 7-1 for the list of impleme        | ented interrupt v    | ectors.                                                |

| bit 7                |                      |                      |       |       |       |       | bit 0 |

|----------------------|----------------------|----------------------|-------|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | Ν     | OV    | Z     | С     |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| bit 15               |                      |                      |       |       |       |       | bit 8 |

| OA                   | OB                   | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| R-0                  | R-0                  | R/C-0                | R/C-0 | R-0   | R/C-0 | R-0   | R/W-0 |

### **REGISTER 7-1:** SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

### REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R-0 | R-0 | R-0   |

|--------|-----|-----|-------|-------|-----|-----|-------|

| —      | —   | —   | US    | EDT   | DL2 | DL1 | DL0   |

| bit 15 |     |     |       |       |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-------|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | PSV   | RND   | IF    |

| bit 7 |       |       |        |                     |       |       | bit 0 |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

bit 3 **IPL3:** CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| Input Name              | Function Name | Register | Configuration<br>Bits     |

|-------------------------|---------------|----------|---------------------------|

| External Interrupt 1    | INT1          | RPINR0   | INT1R<4:0>                |

| External Interrupt 2    | INT2          | RPINR1   | INT2R<4:0>                |

| Timer2 External Clock   | T2CK          | RPINR3   | T2CKR<4:0>                |

| Timer3 External Clock   | T3CK          | RPINR3   | T3CKR<4:0>                |

| Timer4 External Clock   | T4CK          | RPINR4   | T4CKR<4:0> <sup>(2)</sup> |

| Timer5 External Clock   | T5CK          | RPINR4   | T5CKR<4:0> <sup>(2)</sup> |

| Input Capture 1         | IC1           | RPINR7   | IC1R<4:0>                 |

| Input Capture 2         | IC2           | RPINR7   | IC2R<4:0>                 |

| Input Capture 3         | IC3           | RPINR8   | IC3R<4:0>                 |

| Output Compare Fault A  | OCFA          | RPINR11  | OCFAR<4:0>                |

| UART1 Receive           | U1RX          | RPINR18  | U1RXR<4:0>                |

| UART1 Clear-to-Send     | U1CTS         | RPINR18  | U1CTSR<4:0>               |

| SDI1 SPI Data Input 1   | SDI1          | RPINR20  | SDI1R<4:0> <sup>(2)</sup> |

| SCK1 SPI Clock Input 1  | SCK1          | RPINR20  | SCK1R<4:0> <sup>(2)</sup> |

| SPI1 Slave Select Input | SS1           | RPINR21  | SS1R<4:0> <sup>(2)</sup>  |

# TABLE 10-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)<sup>(1)</sup>

Note 1: Unless otherwise noted, all inputs use the Schmitt input buffers.

2: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

# 11.1 Timer1 Control Register

| R/W-0              | U-0                               | R/W-0                        | U-0           | U-0              | U-0              | U-0                | U-0   |  |  |  |  |

|--------------------|-----------------------------------|------------------------------|---------------|------------------|------------------|--------------------|-------|--|--|--|--|

| TON <sup>(1)</sup> | _                                 | TSIDL                        | —             | _                |                  | _                  | _     |  |  |  |  |

| bit 15             |                                   |                              |               | •                |                  |                    | bit 8 |  |  |  |  |

|                    |                                   |                              |               |                  |                  |                    |       |  |  |  |  |

| U-0                | R/W-0                             | R/W-0                        | R/W-0         | U-0              | R/W-0            | R/W-0              | U-0   |  |  |  |  |

| —                  | TGATE                             | TCKPS1                       | TCKPS0        |                  | TSYNC            | TCS <sup>(1)</sup> | —     |  |  |  |  |

| bit 7              |                                   |                              |               |                  |                  |                    | bit ( |  |  |  |  |

|                    |                                   |                              |               |                  |                  |                    |       |  |  |  |  |

| Legend:            |                                   |                              |               |                  |                  |                    |       |  |  |  |  |

| R = Readable       |                                   | W = Writable                 |               | -                | mented bit, read |                    |       |  |  |  |  |

| -n = Value at      | POR                               | '1' = Bit is set             |               | '0' = Bit is cle | ared             | x = Bit is unkno   | own   |  |  |  |  |

| bit 15             | TON: Timer1                       | On hit(1)                    |               |                  |                  |                    |       |  |  |  |  |

| DIL 15             | 1 = Starts 16-                    |                              |               |                  |                  |                    |       |  |  |  |  |

|                    | 0 = Stops 16-                     |                              |               |                  |                  |                    |       |  |  |  |  |

| bit 14             | Unimplemen                        | ted: Read as '               | 0'            |                  |                  |                    |       |  |  |  |  |

| bit 13             | TSIDL: Timer                      | 1 Stop in Idle               | Node bit      |                  |                  |                    |       |  |  |  |  |

|                    |                                   |                              |               | device enters I  | dle mode         |                    |       |  |  |  |  |

|                    |                                   | s module opera               |               | ode              |                  |                    |       |  |  |  |  |

| bit 12-7           | -                                 | ted: Read as '               |               |                  |                  |                    |       |  |  |  |  |

| bit 6              |                                   | er1 Gated Time               | Accumulation  | n Enable bit     |                  |                    |       |  |  |  |  |

|                    | When TCS =<br>This bit is ign     |                              |               |                  |                  |                    |       |  |  |  |  |

|                    | When TCS =                        |                              |               |                  |                  |                    |       |  |  |  |  |

|                    |                                   | e accumulatio                |               |                  |                  |                    |       |  |  |  |  |

|                    |                                   | e accumulatio                |               |                  |                  |                    |       |  |  |  |  |

| bit 5-4            |                                   | Timer1 Input (               | Clock Prescal | e Select bits    |                  |                    |       |  |  |  |  |

|                    | 11 = 1:256<br>10 = 1:64           |                              |               |                  |                  |                    |       |  |  |  |  |

|                    | 01 = 1:8                          |                              |               |                  |                  |                    |       |  |  |  |  |

|                    | 00 = 1:1                          |                              |               |                  |                  |                    |       |  |  |  |  |

| bit 3              | -                                 | ted: Read as '               |               |                  |                  |                    |       |  |  |  |  |

| bit 2              |                                   |                              | ock Input Syn | chronization Se  | elect bit        |                    |       |  |  |  |  |

|                    | <u>When TCS =</u><br>1 = Synchron | <u>1:</u><br>izes external c | lock input    |                  |                  |                    |       |  |  |  |  |

|                    |                                   | synchronize ex               |               | nput             |                  |                    |       |  |  |  |  |

|                    | When TCS =                        | •                            |               |                  |                  |                    |       |  |  |  |  |

|                    | This bit is ign                   |                              |               |                  |                  |                    |       |  |  |  |  |

| bit 1              |                                   | Clock Source                 |               |                  |                  |                    |       |  |  |  |  |

|                    |                                   | clock from pin,              | T1CK (on the  | rising edge)     |                  |                    |       |  |  |  |  |

|                    | 0 = Internal c                    |                              |               |                  |                  |                    |       |  |  |  |  |

| bit 0              | Unimplament                       | ted: Read as '               | o'            |                  |                  |                    |       |  |  |  |  |

## REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER

### 15.4 PWM Control Registers

#### R/W-0 U-0 R/W-0 U-0 U-0 U-0 U-0 U-0 PTEN PTSIDL bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 PTOPS3 PTOPS2 PTOPS1 PTOPS0 PTCKPS1 PTCKPS0 PTMOD1 PTMOD0 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 PTEN: PWMx Time Base Timer Enable bit 1 = PWMx time base is on 0 = PWMx time base is off bit 14 Unimplemented: Read as '0' bit 13 PTSIDL: PWMx Time Base Stop in Idle Mode bit 1 = PWMx time base halts in CPU Idle mode 0 = PWMx time base runs in CPU Idle mode bit 12-8 Unimplemented: Read as '0' bit 7-4 PTOPS<3:0>: PWMx Time Base Output Postscale Select bits 1111 = 1:16 postscale 0001 = 1:2 postscale 0000 = 1:1 postscale bit 3-2 PTCKPS<1:0>: PWMx Time Base Input Clock Prescale Select bits 11 = PWMx time base input clock period is 64 Tcy (1:64 prescale) 10 = PWMx time base input clock period is 16 Tcy (1:16 prescale) 01 = PWMx time base input clock period is 4 Tcy (1:4 prescale) 00 = PWMx time base input clock period is TCY (1:1 prescale) bit 1-0 PTMOD<1:0>: PWMx Time Base Mode Select bits 11 = PWMx time base operates in a Continuous Up/Down Count mode with interrupts for double **PWM updates** 10 = PWMx time base operates in a Continuous Up/Down Count mode 01 = PWMx time base operates in Single Pulse mode

#### REGISTER 15-1: PxTCON: PWMx TIME BASE CONTROL REGISTER

00 = PWMx time base operates in a Free-Running mode

### REGISTER 15-12: PxDC1: PWMx DUTY CYCLE 1 REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|

|                                   |       |                  | PDC   | 1<15:8>                            |       |                 |       |  |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|                                   |       |                  | PDC   | 1<7:0>                             |       |                 |       |  |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |  |

|                                   |       |                  |       |                                    |       |                 |       |  |

| Legend:                           |       |                  |       |                                    |       |                 |       |  |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at POR '1' = B         |       | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unki | nown  |  |

bit 15-0 PDC1<15:0>: PWMx Duty Cycle 1 Value bits

### REGISTER 15-13: PxDC2: PWMx DUTY CYCLE 2 REGISTER

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|

| PDC2<15:8> |       |       |       |       |       |       |       |  |

| bit 15 bit |       |       |       |       |       |       |       |  |

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|

| PDC2<7:0> |       |       |       |       |       |       |       |

| bit 7     |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 PDC2<15:0>: PWMx Duty Cycle 2 Value bits

### REGISTER 15-14: PxDC3: PWMx DUTY CYCLE 3 REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0  | R/W-0              | R/W-0 |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|--------|--------------------|-------|--|

|                                   |       |                  | PDC   | 3<15:8>                            |        |                    |       |  |

| bit 15                            |       |                  |       |                                    |        |                    | bit 8 |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0  | R/W-0              | R/W-0 |  |

| N/W-0                             | N/W-0 | N/ VV-U          |       |                                    | N/VV-0 | N/W-0              | N/W-0 |  |

|                                   |       |                  | PDC   | 3<7:0>                             |        |                    |       |  |

| bit 7                             |       |                  |       |                                    |        |                    | bit C |  |

| Legend:                           |       |                  |       |                                    |        |                    |       |  |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |        |                    |       |  |

| -n = Value at POR                 |       | '1' = Bit is set |       | '0' = Bit is cle                   | ared   | x = Bit is unknown |       |  |

bit 15-0 PDC3<15:0>: PWMx Duty Cycle 3 Value bits

| REGISTER                     | 19-4: ADICI                                                                         | 15123: ADC1                                                                                                                         |                | ANNEL $1, 2,$    | SELECT RE        | GIJIER             |             |  |  |  |  |  |

|------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|--------------------|-------------|--|--|--|--|--|

| U-0                          | U-0                                                                                 | U-0                                                                                                                                 | U-0            | U-0              | R/W-0            | R/W-0              | R/W-0       |  |  |  |  |  |

| _                            | —                                                                                   | —                                                                                                                                   | —              | —                | CH123NB1         | CH123NB0           | CH123SB     |  |  |  |  |  |

| bit 15                       |                                                                                     |                                                                                                                                     |                |                  |                  |                    | bit 8       |  |  |  |  |  |

| U-0                          | U-0                                                                                 | U-0                                                                                                                                 | U-0            | U-0              | R/W-0            | R/W-0              | R/W-0       |  |  |  |  |  |

| -                            | _                                                                                   | _                                                                                                                                   | _              | _                | CH123NA1         | CH123NA0           | CH123SA     |  |  |  |  |  |

| bit 7                        |                                                                                     |                                                                                                                                     |                |                  | 0111201011       | 0111201010         | bit (       |  |  |  |  |  |

|                              |                                                                                     |                                                                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

| <b>Legend:</b><br>R = Readab | la hit                                                                              | W = Writable b                                                                                                                      | 4              | LI – Unimplo     | mented bit, read | d oo 'O'           |             |  |  |  |  |  |

|                              |                                                                                     |                                                                                                                                     | L              | -                |                  |                    |             |  |  |  |  |  |

| -n = Value a                 | IT POR                                                                              | '1' = Bit is set                                                                                                                    |                | '0' = Bit is cle | eared            | x = Bit is unkr    | nown        |  |  |  |  |  |

| bit 15-11                    | Unimplement                                                                         | ted: Read as '0'                                                                                                                    |                |                  |                  |                    |             |  |  |  |  |  |

|                              | -                                                                                   |                                                                                                                                     |                |                  | er Comple D hit  | _                  |             |  |  |  |  |  |

| bit 10-9                     | CH123NB<1:0>: Channel 1, 2, 3 Negative Input Select for Sample B bits               |                                                                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              |                                                                                     | <u>dsPIC33FJ16(GP/MC)101/102 Devices Only:</u><br>11 = Reserved                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              |                                                                                     | 11 = Reserved                                                                                                                       |                |                  |                  |                    |             |  |  |  |  |  |

|                              | 0x = CH1, CH2, CH3 negative inputs are AVss                                         |                                                                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              | dsPIC33FJ32(GP/MC)101/102 Devices Only:                                             |                                                                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              |                                                                                     | ative input is AN                                                                                                                   |                |                  |                  | utive input is not | t connected |  |  |  |  |  |

|                              | 10 = Reserve                                                                        |                                                                                                                                     | is, criz nega  |                  | anto, ens nega   | live input is not  | Connecteu   |  |  |  |  |  |

|                              |                                                                                     | l2, CH3 negative                                                                                                                    | e inputs are A | AVss             |                  |                    |             |  |  |  |  |  |

|                              |                                                                                     | (GP/MC)104 De                                                                                                                       | -              |                  |                  |                    |             |  |  |  |  |  |

|                              |                                                                                     | ative input is AN                                                                                                                   |                |                  | N10 CH3 nega     | tive input is AN   | 111         |  |  |  |  |  |

|                              |                                                                                     |                                                                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              |                                                                                     | 10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8<br>0x = CH1, CH2, CH3 negative inputs are AVss |                |                  |                  |                    |             |  |  |  |  |  |

| bit 8                        | CH123SB: Ch                                                                         | <b>CH123SB:</b> Channel 1, 2, 3 Positive Input Select for Sample B bit                                                              |                |                  |                  |                    |             |  |  |  |  |  |

|                              | dsPIC33FJXX(GP/MC)101 Devices Only:                                                 |                                                                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              | 1 = CH1 positive input is AN3, CH2 and CH3 positive inputs are not connected        |                                                                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              | 0 = CH1 posit                                                                       | ive input is AN0                                                                                                                    | , CH2 positiv  | e input is AN1   | , CH3 positive i | nput is AN2        |             |  |  |  |  |  |

|                              | All Other Dev                                                                       | All Other Devices:                                                                                                                  |                |                  |                  |                    |             |  |  |  |  |  |

|                              | 1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5 |                                                                                                                                     |                |                  |                  |                    |             |  |  |  |  |  |

|                              | 0 = CH1 posit                                                                       | ive input is AN0                                                                                                                    | , CH2 positiv  | e input is AN1   | , CH3 positive i | nput is AN2        |             |  |  |  |  |  |

| bit 7-3                      | Unimplemen                                                                          | ted: Read as '0'                                                                                                                    |                |                  |                  |                    |             |  |  |  |  |  |

| bit 2-1                      | CH123NA<1:                                                                          | <b>0&gt;:</b> Channel 1, 2                                                                                                          | 2, 3 Negative  | Input Select f   | or Sample A bit  | S                  |             |  |  |  |  |  |

|                              |                                                                                     | 10-9> for the ava                                                                                                                   | -              | -                |                  |                    |             |  |  |  |  |  |

| bit 0                        |                                                                                     | nannel 1, 2, 3 Po                                                                                                                   |                | -                | nle A hit        |                    |             |  |  |  |  |  |

| UIL U                        |                                                                                     |                                                                                                                                     | •              |                  |                  |                    |             |  |  |  |  |  |

|                              | Relief to bit 8                                                                     | for the available                                                                                                                   | seuings.       |                  |                  |                    |             |  |  |  |  |  |

### REGISTER 19-4: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

### REGISTER 23-1: DEVID: DEVICE ID REGISTER

| R | R | R      | R                                 | R                                                                    | R                                                                                       | R                                                                                           |

|---|---|--------|-----------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|   |   | DEVID< | 23:16> <sup>(1)</sup>             |                                                                      |                                                                                         |                                                                                             |

|   |   |        |                                   |                                                                      |                                                                                         | bit 16                                                                                      |

| R | R | R      | R                                 | R                                                                    | R                                                                                       | R                                                                                           |

|   |   |        |                                   |                                                                      |                                                                                         |                                                                                             |

|   |   |        |                                   |                                                                      |                                                                                         | bit 8                                                                                       |

| R | R | R      | R                                 | R                                                                    | R                                                                                       | R                                                                                           |

|   |   | DEVID  | <7:0> <sup>(1)</sup>              |                                                                      |                                                                                         |                                                                                             |

|   |   |        |                                   |                                                                      |                                                                                         | bit 0                                                                                       |

|   | R | R R    | R R R<br>R R R<br>DEVID<<br>R R R | DEVID<23:16> <sup>(1)</sup><br>R R R R<br>DEVID<15:8> <sup>(1)</sup> | DEVID<23:16> <sup>(1)</sup><br>R R R R R R<br>DEVID<15:8> <sup>(1)</sup><br>R R R R R R | DEVID<23:16> <sup>(1)</sup><br>R R R R R R R<br>DEVID<15:8> <sup>(1)</sup><br>R R R R R R R |

Legend:

R = Read-Only bit

U = Unimplemented bit

bit 23-0 **DEIDV<23:0>:** Device Identifier bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33F Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70659) for the list of device ID values.

### REGISTER 23-2: DEVREV: DEVICE REVISION REGISTER

| R       | R                 | R                                  | R      | R                      | R          | R | R      |  |

|---------|-------------------|------------------------------------|--------|------------------------|------------|---|--------|--|

|         |                   |                                    | DEVREV | <23:16> <sup>(1)</sup> |            |   |        |  |

| bit 23  |                   |                                    |        |                        |            |   | bit 16 |  |

| R       | R                 |                                    | R      | R                      | R          |   |        |  |

| к       | ĸ                 | R                                  |        |                        | ĸ          | R | R      |  |

|         |                   |                                    | DEVREV | <15:8> <sup>(1)</sup>  |            |   |        |  |

| bit 15  |                   |                                    |        |                        |            |   | bit 8  |  |

| R       | R                 | R                                  | R      | R                      | R          | R | R      |  |

|         |                   |                                    | DEVRE\ | /<7:0> <sup>(1)</sup>  |            |   |        |  |

| bit 7   |                   |                                    |        |                        |            |   | bit 0  |  |

| Logondi | D. Dood only hit  |                                    |        |                        | nantad hit |   |        |  |

| Legena: | R = Read-only bit | ead-only bit U = Unimplemented bit |        |                        |            |   |        |  |

bit 23-0 DEVREV<23:0>: Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33F Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70659) for the list of device revision values.

# 25.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 25.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- Simultaneous debugging sessions

- File History and Bug Tracking:

- Local file history feature

- Built-in support for Bugzilla issue tracker

### 25.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 25.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

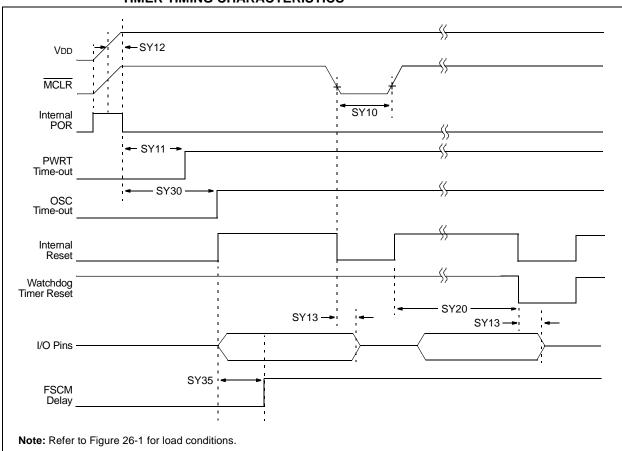

# FIGURE 26-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

# TABLE 26-21: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET TIMING REQUIREMENTS

| АС СН        | ARACTI | ERISTICS                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                                                                                      |  |

|--------------|--------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------------------------------------------------------|--|

| Param<br>No. | Symb   | Characteristic <sup>(1)</sup>                               | Min                                                                                                                                                                                                                                                                                 | Тур <sup>(2)</sup> | Max | Units | Conditions                                                                           |  |

| SY10         | TMCL   | MCLR Pulse Width (low)                                      | 2                                                                                                                                                                                                                                                                                   |                    | _   | μS    |                                                                                      |  |

| SY11         | TPWRT  | Power-up Timer Period                                       | _                                                                                                                                                                                                                                                                                   | 64                 | _   | ms    |                                                                                      |  |

| SY12         | TPOR   | Power-on Reset Delay                                        | 3                                                                                                                                                                                                                                                                                   | 10                 | 30  | μS    |                                                                                      |  |

| SY13         | Tioz   | I/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset |                                                                                                                                                                                                                                                                                     |                    | 1.2 | μS    |                                                                                      |  |

| SY20         | TWDT1  | Watchdog Timer Time-out<br>Period                           | —                                                                                                                                                                                                                                                                                   | —                  | —   | ms    | See Section 23.4 "Watchdog<br>Timer (WDT)" and LPRC<br>Parameter F21a (Table 26-19). |  |

| SY30         | Tost   | Oscillator Start-up Time                                    |                                                                                                                                                                                                                                                                                     | 1024 * Tosc        |     | _     | Tosc = OSC1 period                                                                   |  |

| SY35         | TFSCM  | Fail-Safe Clock Monitor Delay                               | _                                                                                                                                                                                                                                                                                   | 500                | 900 | μS    |                                                                                      |  |

Note 1: These parameters are characterized but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

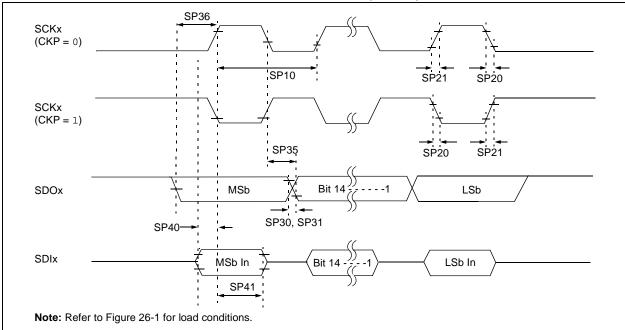

### FIGURE 26-21: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS FOR dsPIC33FJ32(GP/MC)10X

# TABLE 26-39:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ32(GP/MC)10X

| АС СНА       | RACTERIST             | ICS                                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                               |  |

|--------------|-----------------------|-----------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|-------------------------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                 | Min                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions                    |  |

| SP10         | TscP                  | Maximum SCKx Frequency                        | —                                                     | _                  | 9   | MHz   | See Note 3                    |  |

| SP20         | TscF                  | SCKx Output Fall Time                         | —                                                     | —                  | —   | ns    | See Parameter DO32 and Note 4 |  |

| SP21         | TscR                  | SCKx Output Rise Time                         | —                                                     | —                  | _   | ns    | See Parameter DO31 and Note 4 |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                    | —                                                     | —                  | _   | ns    | See Parameter DO32 and Note 4 |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                    | —                                                     | —                  | _   | ns    | See Parameter DO31 and Note 4 |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge     | —                                                     | 6                  | 20  | ns    |                               |  |

| SP36         | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                                    | —                  | _   | ns    |                               |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                                    | —                  | —   | ns    |                               |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30                                                    |                    | _   | ns    |                               |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

# TABLE 26-41:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ32(GP/MC)10X