Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

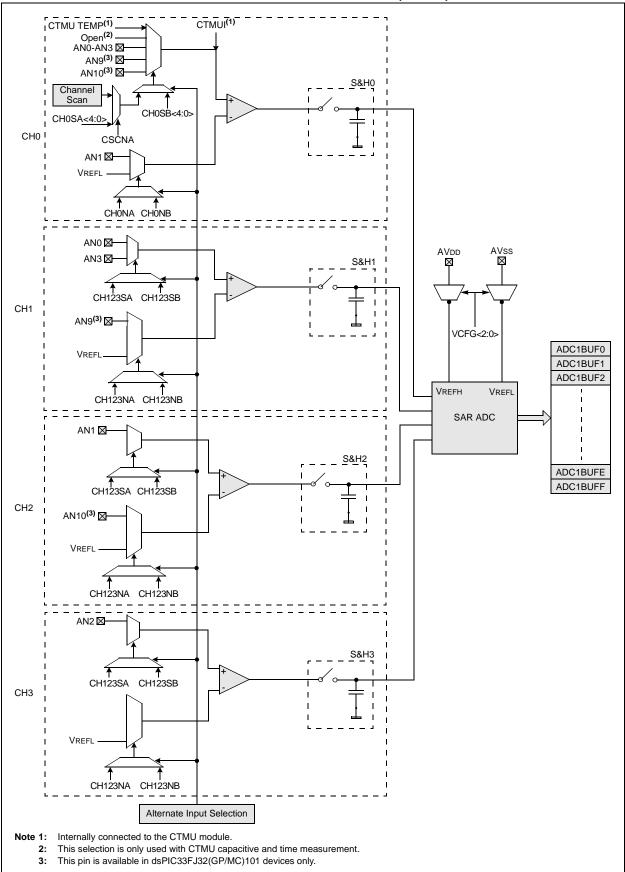

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

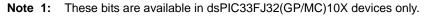

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 36-VTLA (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp102t-e-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest "dsPIC33/PIC24 Family Reference Manual" sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

### 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, if present on the device (regardless if ADC module is not used) (see Section 2.2 "Decoupling Capacitors")

- VCAP (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

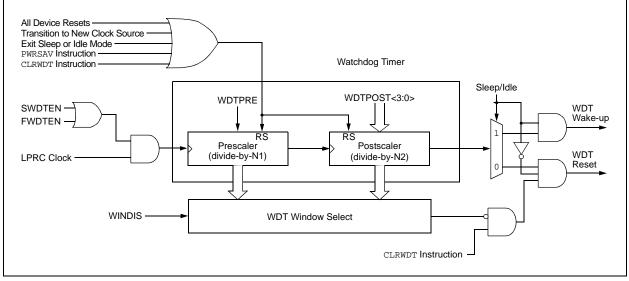

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10V-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

#### TABLE 4-33: PORTB REGISTER MAP FOR dsPIC33FJ32GP101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|---------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        | TRISB< | :15:14> | —      |        |        | —      | -     | TRISB<9:7 | >     |       | —     | TRISB4 |       |       | TRISE | 3<1:0> | C393          |

| PORTB     | 02CA        | RB<1   | 5:14>   | _      | _      | _      | —      |       | RB<9:7>   |       | _     | _     | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        | LATB<  | 15:14>  | _      | _      | _      | —      |       | LATB<9:7> | >     | _     | _     | LATB4  | _     | _     | LATB  | <1:0>  | xxxx          |

| ODCB      | 02CE        | ODCB<  | :15:14> | _      | _      |        | _      | (     | ODCB<9:7  | >     | -     | _     | _      |       |       | -     |        | 0000          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-34: PORTB REGISTER MAP FOR dsPIC33FJ32MC101 DEVICES

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------------|--------|--------|---------|--------|--------|--------|-------|-----------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISB     | 02C8        |        | TRISB< | <15:12> |        | —      | —      | -     | TRISB<9:7 | >     | _     | —     | TRISB4 | _     | _     | TRISE | 3<1:0> | F393          |

| PORTB     | 02CA        |        | RB<1   | 5:12>   |        | _      | _      |       | RB<9:7>   |       | _     | —     | RB4    | _     | _     | RB<   | :1:0>  | xxxx          |

| LATB      | 02CC        |        | LATB<  | 15:12>  |        | _      | _      |       | LATB<9:7> | •     | _     | —     | LATB4  | _     | _     | LATB  | <1:0>  | xxxx          |

| ODCB      | 02CE        |        | ODCB<  | <15:12> |        | _      | _      | (     | ODCB<9:7: | >     | _     | —     | _      | _     | _     | —     | _      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-35: PORTB REGISTER MAP FOR dsPIC33FJ32(GP/MC)102 AND dsPIC33FJ32(GP/MC)104 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|------------|--------|--------|--------|--------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB        | 02C8        |        |            |        |        |        |        |       | TRISB< | :15:0> |       |       |       |       |       |       |       | FFFF          |

| PORTB        | 02CA        |        |            |        |        |        |        |       | RB<1   | 5:0>   |       |       |       |       |       |       |       | xxxx          |

| LATB         | 02CC        |        |            |        |        |        |        |       | LATB<  | 15:0>  |       |       |       |       |       |       |       | xxxx          |

| ODCB         | 02CE        |        | ODCB<15:5> |        |        |        |        |       |        |        | 0000  |       |       |       |       |       |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-36: PORTC REGISTER MAP FOR dsPIC33FJ32(GP/MC)104 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|-------|-------|-------|-------|---------------|

| TRISC        | 02D0        | —      | _      | _      | —      | _      | —      |       |       |        |       | TRISC | C<9:0> |       |       |       |       | FFFF          |

| PORTC        | 02D2        |        | _      | _      | —      | _      | _      |       |       |        |       | RC<   | :9:0>  |       |       |       |       | xxxx          |

| LATC         | 02D4        |        | _      | _      | —      | _      | _      |       |       |        |       | LATC  | <9:0>  |       |       |       |       | xxxx          |

| ODCC         | 02D6        | _      | _      | _      | —      | _      | —      |       | ODC   | C<9:6> |       |       | —      | _     | _     | —     |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER                      | <i>i</i> -J. II 30. I | NTERRUPT                         |                   |                  |                  |                 |        |  |  |  |

|-------------------------------|-----------------------|----------------------------------|-------------------|------------------|------------------|-----------------|--------|--|--|--|

| U-0                           | U-0                   | R/W-0                            | R/W-0             | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |

| —                             | —                     | AD1IF                            | U1TXIF            | U1RXIF           | SPI1IF           | SPI1EIF         | T3IF   |  |  |  |

| oit 15                        |                       |                                  |                   |                  |                  |                 | bi     |  |  |  |

| R/W-0                         | R/W-0                 | R/W-0                            | U-0               | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |

| T2IF                          | OC2IF                 | IC2IF                            | _                 | T1IF             | OC1IF            | IC1IF           | INTOIF |  |  |  |

| bit 7                         |                       |                                  |                   |                  |                  |                 | bi     |  |  |  |

|                               |                       |                                  |                   |                  |                  |                 |        |  |  |  |

| Legend:                       | - h:4                 |                                  | h.:4              |                  |                  |                 |        |  |  |  |

| R = Readable<br>-n = Value at |                       | W = Writable<br>'1' = Bit is se  |                   | 0 = Unimplem     | nented bit, read |                 |        |  |  |  |

| -n = value at                 | POR                   | I = DILIS SE                     | l                 |                  | areu             | x = Bit is unkn | own    |  |  |  |

| bit 15-14                     | Unimplemen            | ted: Read as                     | 'O'               |                  |                  |                 |        |  |  |  |

| bit 13                        | AD1IF: ADC1           | Conversion (                     | Complete Interi   | rupt Flag Status | s bit            |                 |        |  |  |  |

|                               |                       | request has or                   |                   |                  |                  |                 |        |  |  |  |

|                               | -                     | request has no                   |                   | <b>.</b>         |                  |                 |        |  |  |  |

| bit 12                        |                       |                                  | er Interrupt Flag | g Status bit     |                  |                 |        |  |  |  |

|                               | •                     | request has oc<br>request has no |                   |                  |                  |                 |        |  |  |  |

| bit 11                        | -                     | -                                | nterrupt Flag S   | Status bit       |                  |                 |        |  |  |  |

|                               |                       | = Interrupt request has occurred |                   |                  |                  |                 |        |  |  |  |

|                               | •                     | request has no                   |                   |                  |                  |                 |        |  |  |  |

| bit 10                        |                       | -                                | ot Flag Status k  | bit              |                  |                 |        |  |  |  |

|                               | •                     | request has oc<br>request has no |                   |                  |                  |                 |        |  |  |  |

| bit 9                         | -                     | -                                | pt Flag Status    | bit              |                  |                 |        |  |  |  |

|                               |                       | request has or                   |                   |                  |                  |                 |        |  |  |  |

|                               | -                     | request has no                   |                   |                  |                  |                 |        |  |  |  |

| bit 8                         |                       | Interrupt Flag                   |                   |                  |                  |                 |        |  |  |  |

|                               |                       | request has or<br>request has no |                   |                  |                  |                 |        |  |  |  |

| bit 7                         | •                     | Interrupt Flag                   |                   |                  |                  |                 |        |  |  |  |

|                               |                       | request has oc                   |                   |                  |                  |                 |        |  |  |  |

|                               | 0 = Interrupt i       | request has no                   | ot occurred       |                  |                  |                 |        |  |  |  |

| bit 6                         | -                     | -                                |                   | upt Flag Status  | bit              |                 |        |  |  |  |

|                               | •                     | request has oc<br>request has no |                   |                  |                  |                 |        |  |  |  |

| bit 5                         | -                     | -                                | nel 2 Interrupt F | -lag Status bit  |                  |                 |        |  |  |  |

|                               | -                     | request has or                   | -                 | <u>.</u>         |                  |                 |        |  |  |  |

|                               |                       | request has no                   |                   |                  |                  |                 |        |  |  |  |

| bit 4                         | -                     | ted: Read as                     |                   |                  |                  |                 |        |  |  |  |

| bit 3                         | T1IF: Timer1          | Interrupt Flag                   | Status bit        |                  |                  |                 |        |  |  |  |

|                               |                       | request has or                   |                   |                  |                  |                 |        |  |  |  |

#### -. חוור - - -• •

| U-0                                  |                                                                                                                                             |                                                                                                                                                                                  |                                                                          |                                     | EGISTER 0        |                 |         |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------|------------------|-----------------|---------|

| 0-0                                  | R/W-1                                                                                                                                       | R/W-0                                                                                                                                                                            | R/W-0                                                                    | U-0                                 | R/W-1            | R/W-0           | R/W-0   |

| —                                    | T1IP2                                                                                                                                       | T1IP1                                                                                                                                                                            | T1IP0                                                                    |                                     | OC1IP2           | OC1IP1          | OC1IP0  |

| bit 15                               |                                                                                                                                             |                                                                                                                                                                                  |                                                                          |                                     |                  |                 | bit     |

| U-0                                  | R/W-1                                                                                                                                       | R/W-0                                                                                                                                                                            | R/W-0                                                                    | U-0                                 | R/W-1            | R/W-0           | R/W-0   |

| —                                    | IC1IP2                                                                                                                                      | IC1IP1                                                                                                                                                                           | IC1IP0                                                                   |                                     | INT0IP2          | INT0IP1         | INT0IP0 |

| bit 7                                |                                                                                                                                             |                                                                                                                                                                                  |                                                                          |                                     |                  |                 | bit     |

| Legend:                              |                                                                                                                                             |                                                                                                                                                                                  |                                                                          |                                     |                  |                 |         |

| R = Readabl                          | e bit                                                                                                                                       | W = Writable                                                                                                                                                                     | bit                                                                      | U = Unimple                         | mented bit, read | d as '0'        |         |

| -n = Value at                        | POR                                                                                                                                         | '1' = Bit is set                                                                                                                                                                 |                                                                          | '0' = Bit is cle                    | eared            | x = Bit is unkr | nown    |

|                                      |                                                                                                                                             |                                                                                                                                                                                  |                                                                          |                                     |                  |                 |         |

| bit 15                               | Unimplemen                                                                                                                                  | ted: Read as '                                                                                                                                                                   | 0'                                                                       |                                     |                  |                 |         |

| bit 14-12                            | -                                                                                                                                           | imer1 Interrupt                                                                                                                                                                  |                                                                          |                                     |                  |                 |         |

|                                      |                                                                                                                                             | pt is Priority 7 (                                                                                                                                                               | •                                                                        | itv interrupt)                      |                  |                 |         |

|                                      | •                                                                                                                                           |                                                                                                                                                                                  |                                                                          |                                     |                  |                 |         |

|                                      | •                                                                                                                                           |                                                                                                                                                                                  |                                                                          |                                     |                  |                 |         |

|                                      | •                                                                                                                                           |                                                                                                                                                                                  |                                                                          |                                     |                  |                 |         |

|                                      |                                                                                                                                             | pt is Priority 1<br>pt source is dis                                                                                                                                             | ablad                                                                    |                                     |                  |                 |         |

| L:1 4 4                              |                                                                                                                                             | -                                                                                                                                                                                |                                                                          |                                     |                  |                 |         |

| bit 11                               | -                                                                                                                                           | ted: Read as '                                                                                                                                                                   |                                                                          |                                     |                  |                 |         |

| bit 10-8                             |                                                                                                                                             | : Output Compa                                                                                                                                                                   |                                                                          | •                                   | ity bits         |                 |         |

|                                      |                                                                                                                                             | pt is Priority 7 (                                                                                                                                                               | nignest priori                                                           | ity interrupt)                      |                  |                 |         |

|                                      | •                                                                                                                                           |                                                                                                                                                                                  |                                                                          |                                     |                  |                 |         |

|                                      | •                                                                                                                                           |                                                                                                                                                                                  |                                                                          |                                     |                  |                 |         |

|                                      |                                                                                                                                             |                                                                                                                                                                                  |                                                                          |                                     |                  |                 |         |

|                                      |                                                                                                                                             | pt is Priority 1                                                                                                                                                                 |                                                                          |                                     |                  |                 |         |

|                                      | 000 = Interru                                                                                                                               | pt source is dis                                                                                                                                                                 |                                                                          |                                     |                  |                 |         |

| bit 7                                | 000 = Interru<br>Unimplemen                                                                                                                 | pt source is dis<br>nted: Read as '                                                                                                                                              | 0'                                                                       |                                     |                  |                 |         |

|                                      | 000 = Interru<br>Unimplemen                                                                                                                 | pt source is dis                                                                                                                                                                 | 0'                                                                       | errupt Priority b                   | vits             |                 |         |

|                                      | 000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                  | pt source is dis<br>nted: Read as '                                                                                                                                              | 0'<br>Channel 1 Inte                                                     |                                     | its              |                 |         |

|                                      | 000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                  | pt source is dis<br><b>ted:</b> Read as '<br>Input Capture (                                                                                                                     | 0'<br>Channel 1 Inte                                                     |                                     | its              |                 |         |

|                                      | 000 = Interru<br>Unimplemen<br>IC1IP<2:0>:                                                                                                  | pt source is dis<br><b>ted:</b> Read as '<br>Input Capture (                                                                                                                     | 0'<br>Channel 1 Inte                                                     |                                     | its              |                 |         |

|                                      | 000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>•<br>•                                                                       | pt source is dis<br><b>ited:</b> Read as '<br>Input Capture (<br>pt is Priority 7 (                                                                                              | 0'<br>Channel 1 Inte                                                     |                                     | its              |                 |         |

|                                      | 000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru                                                      | pt source is dis<br><b>ted:</b> Read as '<br>Input Capture (                                                                                                                     | 0'<br>Channel 1 Inte<br>highest priori                                   |                                     | vits             |                 |         |

| bit 6-4                              | 000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>•<br>001 = Interru<br>000 = Interru                                          | pt source is dis<br><b>ited:</b> Read as '<br>Input Capture (<br>pt is Priority 7 (<br>pt is Priority 1                                                                          | <sup>0'</sup><br>Channel 1 Inte<br>highest priori<br>abled               |                                     | its              |                 |         |

| bit 6-4<br>bit 3                     | 000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen                       | pt source is dis<br><b>ited:</b> Read as '<br>Input Capture (<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as '                            | <sup>0'</sup><br>Channel 1 Inte<br>highest priori<br>abled<br>0'         | ity interrupt)                      | its              |                 |         |

| bit 6-4<br>bit 3                     | 000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT0IP<2:0>        | pt source is dis<br><b>nted:</b> Read as '<br>Input Capture (<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                                      | 0'<br>Channel 1 Inte<br>highest priori<br>abled<br>0'<br>rupt 0 Priority | ity interrupt)<br><sup>r</sup> bits | vits             |                 |         |

| bit 6-4<br>bit 3                     | 000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT0IP<2:0>        | pt source is dis<br><b>ited:</b> Read as '<br>Input Capture (<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as '<br><b>:</b> External Inter | 0'<br>Channel 1 Inte<br>highest priori<br>abled<br>0'<br>rupt 0 Priority | ity interrupt)<br><sup>r</sup> bits | its              |                 |         |

| bit 7<br>bit 6-4<br>bit 3<br>bit 2-0 | 000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT0IP<2:0>        | pt source is dis<br><b>ited:</b> Read as '<br>Input Capture (<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as '<br><b>:</b> External Inter | 0'<br>Channel 1 Inte<br>highest priori<br>abled<br>0'<br>rupt 0 Priority | ity interrupt)<br><sup>r</sup> bits | its              |                 |         |

| bit 6-4<br>bit 3                     | 000 = Interru<br>Unimplemen<br>IC1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT0IP<2:0><br>111 = Interru | pt source is dis<br><b>ited:</b> Read as '<br>Input Capture (<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as '<br><b>:</b> External Inter | 0'<br>Channel 1 Inte<br>highest priori<br>abled<br>0'<br>rupt 0 Priority | ity interrupt)<br><sup>r</sup> bits | vits             |                 |         |

### REGISTER 7-15: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| REGISTER      | 10-9: RPINE                 | 20: PERIPH       | ERAL PIN S            | ELECT INPU            | TREGISTER             | 20                      |                       |

|---------------|-----------------------------|------------------|-----------------------|-----------------------|-----------------------|-------------------------|-----------------------|

| U-0           | U-0                         | U-0              | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                   | R/W-1                 |

| —             | —                           | —                | SCK1R4 <sup>(1)</sup> | SCK1R3 <sup>(1)</sup> | SCK1R2 <sup>(1)</sup> | SCK1R1 <sup>(1)</sup>   | SCK1R0 <sup>(1)</sup> |

| bit 15        |                             |                  |                       |                       |                       |                         | bit 8                 |

|               |                             |                  |                       |                       |                       |                         |                       |

| U-0           | U-0                         | U-0              | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                   | R/W-1                 |

|               |                             |                  | SDI1R4 <sup>(1)</sup> | SDI1R3 <sup>(1)</sup> | SDI1R2 <sup>(1)</sup> | SDI1R1 <sup>(1)</sup>   | SDI1R0 <sup>(1)</sup> |

| bit 7         |                             |                  |                       |                       |                       |                         | bit 0                 |

|               |                             |                  |                       |                       |                       |                         |                       |

| Legend:       |                             |                  |                       |                       |                       |                         |                       |

| R = Readabl   |                             | W = Writable     |                       | -                     | nented bit, read      |                         |                       |

| -n = Value at | t POR                       | '1' = Bit is set |                       | '0' = Bit is cle      | ared                  | x = Bit is unkr         | IOWN                  |

| 1 1 4 5 4 0   |                             |                  | o.!                   |                       |                       |                         |                       |

| bit 15-13     | -                           | ted: Read as '   |                       |                       | <b>.</b>              |                         |                       |

| bit 12-8      |                             |                  | Clock Input (S        | CK1IN) to the         | Corresponding         | RPn Pin bits            |                       |

|               | 11111 = Inpu<br>11110 = Res |                  |                       |                       |                       |                         |                       |

|               | 11110 = Res                 | erved            |                       |                       |                       |                         |                       |

|               |                             |                  |                       |                       |                       |                         |                       |

|               |                             |                  |                       |                       |                       |                         |                       |

|               | 11010 = Res                 |                  |                       |                       |                       |                         |                       |

|               | 11001 <b>= I</b> npu        | ut tied to RP25  |                       |                       |                       |                         |                       |

|               | •                           |                  |                       |                       |                       |                         |                       |

|               | •                           |                  |                       |                       |                       |                         |                       |

|               | 00001 = Inpu                | ut tied to RP1   |                       |                       |                       |                         |                       |

|               | 00000 = Inpu                |                  |                       |                       |                       |                         |                       |

| bit 7-5       | Unimplemen                  | ted: Read as '   | 0'                    |                       |                       |                         |                       |

| bit 4-0       | SDI1R<4:0>:                 | Assign SPI1 E    | Data Input (SD        | 11) to the Corre      | esponding RPn         | Pin bits <sup>(1)</sup> |                       |

|               | 11111 <b>= I</b> npu        |                  |                       |                       |                       |                         |                       |

|               | 11110 <b>= Res</b>          | erved            |                       |                       |                       |                         |                       |

|               | •                           |                  |                       |                       |                       |                         |                       |

|               | •                           |                  |                       |                       |                       |                         |                       |

|               | 11010 = Res                 | erved            |                       |                       |                       |                         |                       |

|               |                             | ut tied to RP25  |                       |                       |                       |                         |                       |

|               |                             |                  |                       |                       |                       |                         |                       |

|               |                             |                  |                       |                       |                       |                         |                       |

|               | 00001 = Inpu                | it tied to RP1   |                       |                       |                       |                         |                       |

|               | 000001 = Inpu               |                  |                       |                       |                       |                         |                       |

|               |                             | •                |                       |                       |                       |                         |                       |

#### REGISTER 10-9: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| U-0           | U-0          | U-0                                                                                                   | U-0         | U-0               | U-0              | U-0             | U-0   |  |  |  |

|---------------|--------------|-------------------------------------------------------------------------------------------------------|-------------|-------------------|------------------|-----------------|-------|--|--|--|

| _             | —            | —                                                                                                     |             | —                 | _                |                 | —     |  |  |  |

| bit 15        |              |                                                                                                       |             |                   |                  |                 | bit 8 |  |  |  |

|               |              |                                                                                                       |             |                   |                  |                 |       |  |  |  |

| U-0           | U-0          | R/W-0                                                                                                 | R/W-0       | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |

| —             | —            | DTS3A                                                                                                 | DTS3I       | DTS2A             | DTS2I            | DTS1A           | DTS1I |  |  |  |

| bit 7         |              |                                                                                                       |             |                   |                  |                 | bit ( |  |  |  |

|               |              |                                                                                                       |             |                   |                  |                 |       |  |  |  |

| Legend:       |              |                                                                                                       | L :4        |                   |                  |                 |       |  |  |  |

| R = Readab    |              | W = Writable                                                                                          |             | •                 | nented bit, read |                 |       |  |  |  |

| -n = Value a  | at POR       | '1' = Bit is set                                                                                      |             | '0' = Bit is clea | ared             | x = Bit is unkr | IOWN  |  |  |  |

| bit 15-6      | Unimplement  | ted: Read as '                                                                                        | o'          |                   |                  |                 |       |  |  |  |

| bit 5         | •            |                                                                                                       |             | nal Going Activ   | o hit            |                 |       |  |  |  |

| DIT D         |              | e provided fron                                                                                       | Ũ           | nai Going Activ   |                  |                 |       |  |  |  |

|               |              | provided from                                                                                         |             |                   |                  |                 |       |  |  |  |

| bit 4         | DTS3I: Dead- | Time Select fo                                                                                        | r PWM3 Sign | al Going Inactiv  | ve bit           |                 |       |  |  |  |

|               |              | e provided fron                                                                                       |             |                   |                  |                 |       |  |  |  |

|               |              | e provided fron                                                                                       |             |                   |                  |                 |       |  |  |  |

| bit 3         |              |                                                                                                       | •           | nal Going Activ   | e bit            |                 |       |  |  |  |

|               |              | e provided fron                                                                                       |             |                   |                  |                 |       |  |  |  |

| <b>h</b> :+ 0 |              | e provided fron                                                                                       |             |                   | e hit            |                 |       |  |  |  |

| bit 2         |              | e provided fron                                                                                       | •           | al Going Inactiv  | e dit            |                 |       |  |  |  |

|               |              | e provided from                                                                                       |             |                   |                  |                 |       |  |  |  |

| bit 1         |              | -                                                                                                     |             | nal Going Activ   | e bit            |                 |       |  |  |  |

|               |              | <b>DTS1A:</b> Dead-Time Select for PWM1 Signal Going Active bit<br>1 = Dead time provided from Unit B |             |                   |                  |                 |       |  |  |  |

|               |              | e provided fron                                                                                       |             |                   |                  |                 |       |  |  |  |

| bit 0         | DTS1I: Dead- | Time Select for                                                                                       | r PWM1 Sign | al Going Inactiv  | ve bit           |                 |       |  |  |  |

|               |              | e provided fron                                                                                       | n Unit B    |                   |                  |                 |       |  |  |  |

|               |              | e provided fron                                                                                       |             |                   |                  |                 |       |  |  |  |

#### REGISTER 15-8: PxDTCON2: PWMx DEAD-TIME CONTROL REGISTER 2

#### 18.1 UART Helpful Tips

- In multi-node, direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 18.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en554109          |

#### 18.2.1 KEY RESOURCES

- "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33/PIC24 Family Reference Manual"* sections

- Development Tools

|                                          | 19-5: AD1C                                                                                                                                                                |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                           | CT REGISTE             | IN IN             |          |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------|-------------------|----------|

| R/W-0                                    | U-0                                                                                                                                                                       | U-0                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                    | R/W-0                                                     | R/W-0                  | R/W-0             | R/W-0    |

| CH0NB                                    | —                                                                                                                                                                         | —                                                                                                                                                                                                                                      | CH0SB4                                                                                                                                                                                                                   | CH0SB3                                                    | CH0SB2                 | CH0SB1            | CH0SB0   |

| bit 15                                   |                                                                                                                                                                           |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                           |                        |                   | bit 8    |

| R/W-0                                    | U-0                                                                                                                                                                       | U-0                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                    | R/W-0                                                     | R/W-0                  | R/W-0             | R/W-0    |

| CH0NA                                    |                                                                                                                                                                           | _                                                                                                                                                                                                                                      | CH0SA4                                                                                                                                                                                                                   | CH0SA3                                                    | CH0SA2                 | CH0SA1            | CH0SA0   |

| bit 7                                    |                                                                                                                                                                           |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          | 1                                                         |                        |                   | bit (    |

| Legend:                                  |                                                                                                                                                                           |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                           |                        |                   |          |

| R = Readable                             | e bit                                                                                                                                                                     | W = Writable                                                                                                                                                                                                                           | bit                                                                                                                                                                                                                      | U = Unimplen                                              | nented bit, read       | d as '0'          |          |

| -n = Value at I                          | POR                                                                                                                                                                       | '1' = Bit is se                                                                                                                                                                                                                        | t                                                                                                                                                                                                                        | '0' = Bit is clea                                         |                        | x = Bit is unkr   | nown     |

|                                          |                                                                                                                                                                           |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                           |                        |                   |          |

| bit 15                                   |                                                                                                                                                                           | -                                                                                                                                                                                                                                      | e Input Select f                                                                                                                                                                                                         | or Sample B bi                                            | t                      |                   |          |

|                                          |                                                                                                                                                                           | 0 negative inpu<br>0 negative inpu                                                                                                                                                                                                     |                                                                                                                                                                                                                          |                                                           |                        |                   |          |

| bit 14-13                                |                                                                                                                                                                           | ited: Read as                                                                                                                                                                                                                          |                                                                                                                                                                                                                          |                                                           |                        |                   |          |

| bit 12-8                                 | -                                                                                                                                                                         |                                                                                                                                                                                                                                        | ositive Input Se                                                                                                                                                                                                         | lect for Sample                                           | B hits                 |                   |          |

| 511 12 0                                 |                                                                                                                                                                           | 0 = Reserved:                                                                                                                                                                                                                          | -                                                                                                                                                                                                                        | loot for Gampie                                           | Disto                  |                   |          |

|                                          |                                                                                                                                                                           |                                                                                                                                                                                                                                        | input is AN15                                                                                                                                                                                                            | 2)                                                        |                        |                   |          |

|                                          |                                                                                                                                                                           |                                                                                                                                                                                                                                        | ected, all inputs                                                                                                                                                                                                        |                                                           |                        |                   |          |

|                                          |                                                                                                                                                                           |                                                                                                                                                                                                                                        | input is connect                                                                                                                                                                                                         |                                                           | emperature se          | nsor              |          |

|                                          |                                                                                                                                                                           |                                                                                                                                                                                                                                        | input is AN12 <sup>(2</sup><br>input is AN11 <sup>(2</sup>                                                                                                                                                               |                                                           |                        |                   |          |

|                                          | 01011 = Cha                                                                                                                                                               | annel 0 positive                                                                                                                                                                                                                       | input is AN10 <sup>(;</sup>                                                                                                                                                                                              | 3)                                                        |                        |                   |          |

|                                          |                                                                                                                                                                           |                                                                                                                                                                                                                                        | input is AN9 <sup>(3)</sup>                                                                                                                                                                                              |                                                           |                        |                   |          |

|                                          |                                                                                                                                                                           |                                                                                                                                                                                                                                        | input is AN8 <sup>(2)</sup>                                                                                                                                                                                              |                                                           |                        |                   |          |

|                                          |                                                                                                                                                                           |                                                                                                                                                                                                                                        | input is AN7 <sup>(2)</sup>                                                                                                                                                                                              |                                                           |                        |                   |          |

|                                          |                                                                                                                                                                           | nnel 0 positive                                                                                                                                                                                                                        | input is AN6 <sup>•-</sup>                                                                                                                                                                                               |                                                           |                        |                   |          |

|                                          |                                                                                                                                                                           |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |                                                           |                        |                   |          |