Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp102t-i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 PRODUCT FAMILIES

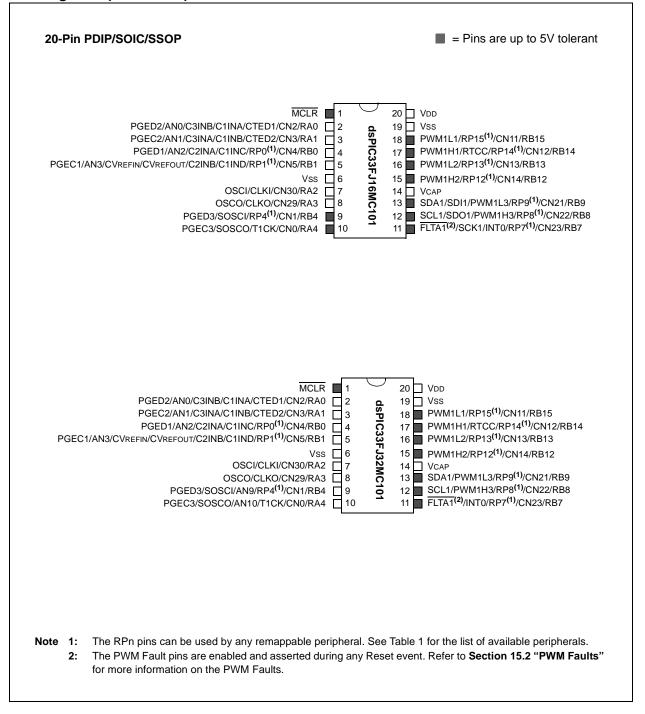

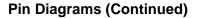

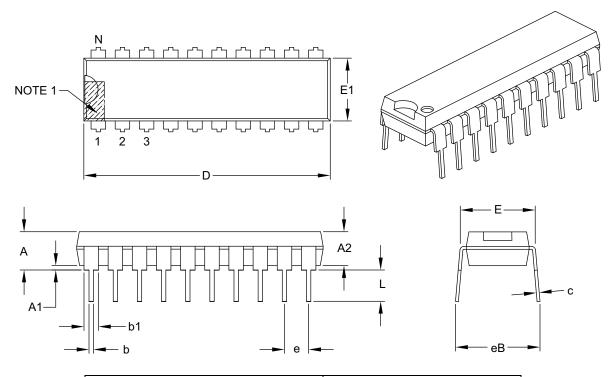

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. The following pages show their pinout diagrams.

|                  |      | rte)                  |              |                 | Rem                           | appa          | ble l          | Perip | herals                             | 5   | М                 |            | Ŋ                    |      |      |             |      |          |                                 |

|------------------|------|-----------------------|--------------|-----------------|-------------------------------|---------------|----------------|-------|------------------------------------|-----|-------------------|------------|----------------------|------|------|-------------|------|----------|---------------------------------|

| Device           | Pins | Program Flash (Kbyte) | RAM (Kbytes) | Remappable Pins | 16-bit Timer <sup>(1,2)</sup> | Input Capture | Output Compare | UART  | External Interrupts <sup>(3)</sup> | SPI | Motor Control PWM | PWM Faults | 10-Bit, 1.1 Msps ADC | RTCC | I²C™ | Comparators | CTMU | I/O Pins | Packages                        |

| dsPIC33FJ16GP101 | 18   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 13       | PDIP,<br>SOIC                   |

|                  | 20   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | SSOP                            |

| dsPIC33FJ16GP102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | _          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

| dsPIC33FJ16MC101 | 20   | 16                    | 1            | 10              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 1          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | PDIP,<br>SOIC,<br>SSOP          |

| dsPIC33FJ16MC102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

#### TABLE 1:dsPIC33FJ16(GP/MC)101/102 DEVICE FEATURES

**Note 1:** Two out of three timers are remappable.

2: One pair can be combined to create one 32-bit timer.

**3**: Two out of three interrupts are remappable.

### Pin Diagrams (Continued)

|           |             |                    |                      |        |        |        |          |                      |         |             |       |       |        |        |          | 1        |         |               |

|-----------|-------------|--------------------|----------------------|--------|--------|--------|----------|----------------------|---------|-------------|-------|-------|--------|--------|----------|----------|---------|---------------|

| File Name | SFR<br>Addr | Bit 15             | Bit 14               | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9                | Bit 8   | Bit 7       | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300        | ADC1 Data Buffer 0 |                      |        |        |        |          |                      |         |             |       | xxxx  |        |        |          |          |         |               |

| ADC1BUF1  | 0302        |                    |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 1     |       |        |        |          |          |         | xxxx          |

| ADC1BUF2  | 0304        |                    | ADC1 Data Buffer 2 x |        |        |        |          |                      |         |             |       |       | xxxx   |        |          |          |         |               |

| ADC1BUF3  | 0306        |                    |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 3     |       |        |        |          |          |         | xxxx          |

| ADC1BUF4  | 0308        |                    |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 4     |       |        |        |          |          |         | xxxx          |

| ADC1BUF5  | 030A        |                    |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 5     |       |        |        |          |          |         | xxxx          |

| ADC1BUF6  | 030C        |                    |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 6     |       |        |        |          |          |         | xxxx          |

| ADC1BUF7  | 030E        |                    |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 7     |       |        |        |          |          |         | xxxx          |

| ADC1BUF8  | 0310        |                    |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 8     |       |        |        |          |          |         | xxxx          |

| ADC1BUF9  | 0312        |                    |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 9     |       |        |        |          |          |         | xxxx          |

| ADC1BUFA  | 0314        |                    |                      |        |        |        |          |                      | ADC1 D  | ata Buffer  | 10    |       |        |        |          |          |         | xxxx          |

| ADC1BUFB  | 0316        |                    |                      |        |        |        |          |                      | ADC1 D  | ata Buffer  | 11    |       |        |        |          |          |         | xxxx          |

| ADC1BUFC  | 0318        |                    |                      |        |        |        |          |                      | ADC1 D  | ata Buffer  | 12    |       |        |        |          |          |         | xxxx          |

| ADC1BUFD  | 031A        |                    |                      |        |        |        |          |                      | ADC1 D  | ata Buffer  | 13    |       |        |        |          |          |         | xxxx          |

| ADC1BUFE  | 031C        |                    |                      |        |        |        |          |                      | ADC1 D  | ata Buffer  | 14    |       |        |        |          |          |         | xxxx          |

| ADC1BUFF  | 031E        |                    |                      |        |        |        |          |                      | ADC1 D  | ata Buffer  | 15    |       |        |        |          |          |         | xxxx          |

| AD1CON1   | 0320        | ADON               | _                    | ADSIDL | _      | _      | _        | FORM1                | FORM0   | SSRC2       | SSRC1 | SSRC0 | _      | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322        | VCFG2              | VCFG1                | VCFG0  | _      | _      | CSCNA    | CHPS1                | CHPS0   | BUFS        | _     | SMPI3 | SMPI2  | SMPI1  | SMPI0    | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324        | ADRC               | _                    | —      | SAMC4  | SAMC3  | SAMC2    | SAMC1                | SAMC0   | ADCS7       | ADCS6 | ADCS5 | ADCS4  | ADCS3  | ADCS2    | ADCS1    | ADCS0   | 0000          |

| AD1CHS123 | 0326        |                    | _                    | —      | _      | _      | CH123NB1 | CH123NB0             | CH123SB | _           | —     | _     | _      | _      | CH123NA1 | CH123NA0 | CH123SA | 0000          |

| AD1CHS0   | 0328        | CH0NB              | —                    | —      | CH0SB4 | CH0SB3 | CH0SB2   | CH0SB1               | CH0SB0  | CH0NA       | —     |       | CH0SA4 | CH0SA3 | CH0SA2   | CH0SA1   | CH0SA0  | 0000          |

| AD1PCFGL  | 032C        | _                  | —                    | —      | —      |        | PCFG<    | 10:9> <sup>(1)</sup> | —       | _           | —     |       | —      |        | PCF      | G<3:0>   |         | 0000          |

| AD1CSSL   | 0330        | _                  | —                    | —      | —      |        | CSS<1    | 0:9> <sup>(1)</sup>  | —       | _           | —     |       | —      |        | CSS      | S<3:0>   |         | 0000          |

## TABLE 4-15: ADC1 REGISTER MAP FOR dsPIC33FJXX(GP/MC)101 DEVICES

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PCFG<10:9> and CSS<10:9> bits are available in dsPIC33FJ32(GP/MC)101/102 devices only.

dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| TABLE 4-16:       ADC1 REGISTER MAP FOR dsPIC33FJXX(GP/MC)102 DEVICES |             |                                      |                    |        |        |        |          |                      |             |           |       |       |        |        |          |          |         |               |

|-----------------------------------------------------------------------|-------------|--------------------------------------|--------------------|--------|--------|--------|----------|----------------------|-------------|-----------|-------|-------|--------|--------|----------|----------|---------|---------------|

| File Name                                                             | SFR<br>Addr | Bit 15                               | Bit 14             | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9                | Bit 8       | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

| ADC1BUF0                                                              | 0300        |                                      |                    |        |        |        |          |                      | ADC1 Data   | Buffer 0  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF1                                                              | 0302        |                                      | ADC1 Data Buffer 1 |        |        |        |          |                      |             |           |       |       | xxxx   |        |          |          |         |               |

| ADC1BUF2                                                              | 0304        |                                      |                    |        |        |        |          |                      | ADC1 Data   | Buffer 2  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF3                                                              | 0306        |                                      |                    |        |        |        |          |                      | ADC1 Data   | Buffer 3  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF4                                                              | 0308        |                                      |                    |        |        |        |          |                      | ADC1 Data   | Buffer 4  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF5                                                              | 030A        |                                      |                    |        |        |        |          |                      | ADC1 Data   | Buffer 5  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF6                                                              | 030C        |                                      |                    |        |        |        |          |                      | ADC1 Data   | Buffer 6  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF7                                                              | 030E        |                                      |                    |        |        |        |          |                      | ADC1 Data   | Buffer 7  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF8                                                              | 0310        |                                      |                    |        |        |        |          |                      | ADC1 Data   | Buffer 8  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF9                                                              | 0312        |                                      | ADC1 Data Buffer 9 |        |        |        |          |                      |             |           |       | xxxx  |        |        |          |          |         |               |

| ADC1BUFA                                                              | 0314        |                                      |                    |        |        |        |          | A                    | ADC1 Data E | Buffer 10 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFB                                                              | 0316        |                                      |                    |        |        |        |          | ŀ                    | ADC1 Data B | Buffer 11 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFC                                                              | 0318        |                                      |                    |        |        |        |          | ŀ                    | ADC1 Data E | Buffer 12 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFD                                                              | 031A        |                                      |                    |        |        |        |          | ŀ                    | ADC1 Data E | Buffer 13 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFE                                                              | 031C        |                                      |                    |        |        |        |          | A                    | ADC1 Data E | Buffer 14 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFF                                                              | 031E        |                                      |                    |        |        |        |          | A                    | ADC1 Data E | Buffer 15 |       |       |        |        |          |          |         | xxxx          |

| AD1CON1                                                               | 0320        | ADON                                 | _                  | ADSIDL | _      | —      | _        | FORM1                | FORM0       | SSRC2     | SSRC1 | SSRC0 | _      | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2                                                               | 0322        | VCFG2                                | VCFG1              | VCFG0  | _      | —      | CSCNA    | CHPS1                | CHPS0       | BUFS      |       | SMPI3 | SMPI2  | SMPI1  | SMPI0    | BUFM     | ALTS    | 0000          |

| AD1CON3                                                               | 0324        | ADRC                                 | _                  | —      | SAMC4  | SAMC3  | SAMC2    | SAMC1                | SAMC0       | ADCS7     | ADCS6 | ADCS5 | ADCS4  | ADCS3  | ADCS2    | ADCS1    | ADCS0   | 0000          |

| AD1CHS123                                                             | 0326        | —                                    | _                  | _      | _      | —      | CH123NB1 | CH123NB0             | CH123SB     | _         |       |       | _      | _      | CH123NA1 | CH123NA0 | CH123SA | 0000          |

| AD1CHS0                                                               | 0328        | CH0NB                                | _                  | _      | CH0SB4 | CH0SB3 | CH0SB2   | CH0SB1               | CH0SB0      | CH0NA     |       |       | CH0SA4 | CH0SA3 | CH0SA2   | CH0SA1   | CH0SA0  | 0000          |

| AD1PCFGL                                                              | 032C        | —                                    | _                  | —      | _      | —      |          | 10:9> <sup>(1)</sup> | _           | _         | _     |       |        | PC     | FG<5:0>  |          |         | 0000          |

| AD1CSSL                                                               | 0330        | CSS<10:9> <sup>(1)</sup> CSS<5:0> 00 |                    |        |        |        |          |                      | 0000        |           |       |       |        |        |          |          |         |               |

### TABLE 4-16: ADC1 REGISTER MAP FOR dsPIC33FJXX(GP/MC)102 DEVICES

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PCFG<10:9> and CSS<10:9> bits are available in dsPIC33FJ32(GP/MC)101/102 devices only.

### 5.2 RTSP Operation

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions); and to program one word. Table 26-12 shows typical erase and programming times. The 8-row erase pages are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes.

### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the operation is finished.

The programming time depends on the FRC accuracy (see Table 26-18) and the value of the FRC Oscillator Tuning register (see Register 8-3). Use the following formula to calculate the minimum and maximum values for the Word write time and page erase time (see Parameters D138a and D138b, and Parameters D137a and D137b in Table 26-12, respectively).

#### EQUATION 5-1: PROGRAMMING TIME

$\frac{T}{7.37 \text{ MHz} \times (FRC \text{ Accuracy})\% \times (FRC \text{ Tuning})\%}$

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 2\%$ . If the TUN<5:0> bits (see Register 8-3) are set to `b000000, the minimum row write time is equal to Equation 5-2.

#### EQUATION 5-2: MINIMUM ROW WRITE TIME

$T_{RW} = \frac{355 \ Cycles}{7.37 \ MHz \times (1 + 0.02) \times (1 - 0.00375)} = 47.4 \mu s$

The maximum row write time is equal to Equation 5-3.

# EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{355 \ Cycles}{7.37 \ MHz \times (1 - 0.02) \times (1 - 0.00375)} = 49.3 \mu s$$

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program one word (24 bits) of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

| Note: | Performing a page erase operation on the   |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | last page of program memory will clear the |  |  |  |  |  |  |  |  |  |

|       | Flash Configuration Words, thereby         |  |  |  |  |  |  |  |  |  |

|       | enabling code protection as a result.      |  |  |  |  |  |  |  |  |  |

|       | Therefore, users should avoid performing   |  |  |  |  |  |  |  |  |  |

|       | page erase operations on the last page of  |  |  |  |  |  |  |  |  |  |

|       | program memory.                            |  |  |  |  |  |  |  |  |  |

Refer to **"Flash Programming"** (DS70191) in the *"dsPIC33/PIC24 Family Reference Manual"* for details and codes examples on programming using RTSP.

## 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

| D / M A       | D 444 A                                                                                                                                                        | D.4.4. 0                                                                                                                           | DAMA            | DALLA             | DALLA           | DAMA            | D 44/ 6 |  |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|---------|--|--|--|--|--|--|

| R/W-0         | R/W-0                                                                                                                                                          | R/W-0                                                                                                                              | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |  |  |

| NSTDIS        | OVAERR                                                                                                                                                         | OVBERR                                                                                                                             | COVAERR         | COVBERR           | OVATE           | OVBTE           | COVTE   |  |  |  |  |  |  |

| bit 15        |                                                                                                                                                                |                                                                                                                                    |                 |                   |                 |                 | bi      |  |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                          | U-0                                                                                                                                | R/W-0           | R/W-0             | R/W-0           | R/W-0           | U-0     |  |  |  |  |  |  |

| SFTACERR      |                                                                                                                                                                | <u> </u>                                                                                                                           | MATHERR         | ADDRERR           | STKERR          | OSCFAIL         |         |  |  |  |  |  |  |

| bit 7         | BIVOLINI                                                                                                                                                       |                                                                                                                                    |                 | ABBRERR           | OTTLETT         | 00017112        | bi      |  |  |  |  |  |  |

|               |                                                                                                                                                                |                                                                                                                                    |                 |                   |                 |                 |         |  |  |  |  |  |  |

| Legend:       |                                                                                                                                                                |                                                                                                                                    |                 |                   |                 |                 |         |  |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                                                                          | W = Writable                                                                                                                       | bit             | U = Unimplem      | ented bit, read | 1 as '0'        |         |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                            | '1' = Bit is set                                                                                                                   |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |  |  |  |  |  |  |

| 6:4 <i>7</i>  |                                                                                                                                                                | www.unt.Nie.otie.ev.F                                                                                                              | Niachla hit     |                   |                 |                 |         |  |  |  |  |  |  |

| bit 15        |                                                                                                                                                                | rrupt Nesting E                                                                                                                    |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               | <ul> <li>1 = Interrupt nesting is disabled</li> <li>0 = Interrupt nesting is enabled</li> </ul>                                                                |                                                                                                                                    |                 |                   |                 |                 |         |  |  |  |  |  |  |

| bit 14        | -                                                                                                                                                              | cumulator A O                                                                                                                      |                 | lag bit           |                 |                 |         |  |  |  |  |  |  |

|               | 1 = Trap was                                                                                                                                                   | <ul> <li>1 = Trap was caused by overflow of Accumulator A</li> <li>0 = Trap was not caused by overflow of Accumulator A</li> </ul> |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               | 0 = Trap was                                                                                                                                                   | not caused by                                                                                                                      | overflow of Ad  | ccumulator A      |                 |                 |         |  |  |  |  |  |  |

| bit 13        |                                                                                                                                                                | cumulator B O                                                                                                                      | -               | -                 |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                                                | caused by ove<br>not caused by                                                                                                     |                 |                   |                 |                 |         |  |  |  |  |  |  |

| bit 12        | -                                                                                                                                                              | -                                                                                                                                  | Dverflow Trap F | lag hit           |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                                                |                                                                                                                                    | •               | flow of Accumu    | •               |                 |         |  |  |  |  |  |  |

|               | •                                                                                                                                                              | •                                                                                                                                  | •               | overflow of Accu  |                 |                 |         |  |  |  |  |  |  |

| bit 11        | COVBERR: Accumulator B Catastrophic Overflow Trap Flag bit                                                                                                     |                                                                                                                                    |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                                                |                                                                                                                                    |                 | flow of Accumu    |                 |                 |         |  |  |  |  |  |  |

|               | -                                                                                                                                                              | -                                                                                                                                  | -               | overflow of Accu  | umulator B      |                 |         |  |  |  |  |  |  |

| bit 10        | OVATE: Accumulator A Overflow Trap Enable bit                                                                                                                  |                                                                                                                                    |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               | 1 = Trap overflow of Accumulator A<br>0 = Trap is disabled                                                                                                     |                                                                                                                                    |                 |                   |                 |                 |         |  |  |  |  |  |  |

| bit 9         |                                                                                                                                                                | umulator B Ove                                                                                                                     | erflow Trap En  | able bit          |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                                                | flow of Accum                                                                                                                      |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               | 0 = Trap is di                                                                                                                                                 | sabled                                                                                                                             |                 |                   |                 |                 |         |  |  |  |  |  |  |

| bit 8         | COVTE: Cata                                                                                                                                                    | astrophic Overf                                                                                                                    | low Trap Enab   | ole bit           |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                                                |                                                                                                                                    | erflow of Accur | mulator A or B i  | s enabled       |                 |         |  |  |  |  |  |  |

| hit 7         | 0 = Trap is dis                                                                                                                                                | sabled<br>Shift Accumula                                                                                                           | tor Error State | ia hit            |                 |                 |         |  |  |  |  |  |  |

| bit 7         |                                                                                                                                                                |                                                                                                                                    |                 |                   | chift           |                 |         |  |  |  |  |  |  |

|               | <ol> <li>1 = Math error trap was caused by an invalid accumulator shift</li> <li>0 = Math error trap was not caused by an invalid accumulator shift</li> </ol> |                                                                                                                                    |                 |                   |                 |                 |         |  |  |  |  |  |  |

| bit 6         |                                                                                                                                                                | ithmetic Error :                                                                                                                   | -               |                   |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                                                | or trap was cau                                                                                                                    | •               | •                 |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                                                | r trap was not                                                                                                                     | -               | ivide-by-zero     |                 |                 |         |  |  |  |  |  |  |

| bit 5         | Unimplemented: Read as '0'                                                                                                                                     |                                                                                                                                    |                 |                   |                 |                 |         |  |  |  |  |  |  |

| it 4          | MATHERR: Arithmetic Error Status bit<br>1 = Math error trap has occurred                                                                                       |                                                                                                                                    |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               | 1 14-41                                                                                                                                                        |                                                                                                                                    | una al          |                   |                 |                 |         |  |  |  |  |  |  |

#### INTOONA, INTERDURT CONTROL DECISTER A

## 8.2 Oscillator Control Registers

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0           | R-0                                                                                          | R-0                                                                                                                                                       | R-0                                                                                       | U-0              | R/W-y                                 | R/W-y                   | R/W-y                |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|---------------------------------------|-------------------------|----------------------|--|--|--|--|--|

| _             | COSC2                                                                                        | COSC1                                                                                                                                                     | COSC0                                                                                     | —                | NOSC2 <sup>(2)</sup>                  | NOSC1 <sup>(2)</sup>    | NOSC0 <sup>(2)</sup> |  |  |  |  |  |

| bit 15        |                                                                                              |                                                                                                                                                           |                                                                                           |                  | •                                     |                         | bit 8                |  |  |  |  |  |

| DAMA          | DAMO                                                                                         |                                                                                                                                                           |                                                                                           | D/0 0            |                                       | DANO                    | DAVA                 |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                        | R-0                                                                                                                                                       | U-0                                                                                       | R/C-0            | U-0                                   | R/W-0                   | R/W-0                |  |  |  |  |  |

| CLKLOCK       | IOLOCK                                                                                       | LOCK                                                                                                                                                      |                                                                                           | CF               |                                       | LPOSCEN                 | OSWEN                |  |  |  |  |  |

| bit 7         |                                                                                              |                                                                                                                                                           |                                                                                           |                  |                                       |                         | bit (                |  |  |  |  |  |

| Legend:       |                                                                                              | C = Clearable                                                                                                                                             | e bit                                                                                     | y = Value set    | from Configura                        | tion bits on PO         | R                    |  |  |  |  |  |

| R = Readabl   | le bit                                                                                       | W = Writable                                                                                                                                              | bit                                                                                       | U = Unimpler     | mented bit, read                      | l as '0'                |                      |  |  |  |  |  |

| -n = Value at | t POR                                                                                        | '1' = Bit is set                                                                                                                                          |                                                                                           | '0' = Bit is cle | ared                                  | x = Bit is unkn         | iown                 |  |  |  |  |  |

|               |                                                                                              |                                                                                                                                                           |                                                                                           |                  |                                       |                         |                      |  |  |  |  |  |

| bit 15        | Unimplemen                                                                                   | ted: Read as '                                                                                                                                            | 0'                                                                                        |                  |                                       |                         |                      |  |  |  |  |  |

| bit 14-12     | COSC<2:0>:                                                                                   | Current Oscilla                                                                                                                                           | ator Selection                                                                            | bits (read-only  | )                                     |                         |                      |  |  |  |  |  |

|               | 101 = Low-Po<br>100 = Second<br>011 = Primary<br>010 = Primary<br>001 = Fast R               | C Oscillator (Fl<br>ower RC Oscill<br>dary Oscillator<br>y Oscillator (M<br>y Oscillator (M<br>C Oscillator (Fl<br>C Oscillator (Fl                       | ator (LPRC)<br>(SOSC)<br>S, EC) with PL<br>S, HS, EC)<br>RC) with Divid                   | L                | L (FRCPLL)                            |                         |                      |  |  |  |  |  |

| bit 11        | Unimplemented: Read as '0'                                                                   |                                                                                                                                                           |                                                                                           |                  |                                       |                         |                      |  |  |  |  |  |

| bit 10-8      | NOSC<2:0>:                                                                                   | NOSC<2:0>: New Oscillator Selection bits <sup>(2)</sup>                                                                                                   |                                                                                           |                  |                                       |                         |                      |  |  |  |  |  |

|               | 110 = Fast R<br>101 = Low-Po<br>100 = Second<br>011 = Primar<br>010 = Primar<br>001 = Fast R | C Oscillator (FI<br>C Oscillator (FI<br>ower RC Oscill<br>dary Oscillator<br>y Oscillator (Mi<br>y Oscillator (Mi<br>C Oscillator (FI<br>C Oscillator (FI | RC) with Divid<br>ator (LPRC)<br>(SOSC)<br>S, EC) with PL<br>S, HS, EC)<br>RC) with Divid | le-by-16<br>_L   | L (FRCPLL)                            |                         |                      |  |  |  |  |  |

| bit 7         | CLKLOCK: C                                                                                   | lock Lock Ena                                                                                                                                             | ble bit                                                                                   |                  |                                       |                         |                      |  |  |  |  |  |

|               |                                                                                              |                                                                                                                                                           |                                                                                           |                  | KSM<1:0> (FO                          | SC<7:6>) = 0b           | 01):                 |  |  |  |  |  |

|               |                                                                                              | itching is disab<br>itching is enab                                                                                                                       |                                                                                           |                  | n be modified by                      | / clock switchin        | a                    |  |  |  |  |  |

| bit 6         |                                                                                              | ipheral Pin Sel                                                                                                                                           | -                                                                                         |                  |                                       | ,                       | ~                    |  |  |  |  |  |

|               | 1 = Periphera                                                                                | al Pin Select is                                                                                                                                          | locked, a write                                                                           |                  | l Pin Select regi<br>ieral Pin Select |                         |                      |  |  |  |  |  |

| bit 5         | LOCK: PLL L                                                                                  | ock Status bit                                                                                                                                            | (read-only)                                                                               |                  |                                       |                         |                      |  |  |  |  |  |

|               |                                                                                              | that PLL is in that PLL is ou                                                                                                                             |                                                                                           |                  | satisfied<br>progress or PLL          | is disabled             |                      |  |  |  |  |  |

| bit 4         | Unimplemen                                                                                   | ted: Read as '                                                                                                                                            | 0'                                                                                        |                  |                                       |                         |                      |  |  |  |  |  |

|               | /rites to this regis                                                                         |                                                                                                                                                           |                                                                                           |                  | Oscillator (Part                      | t <b>VI)</b> " (DS7064∠ | 1) in the            |  |  |  |  |  |

|               | irect clock switch<br>his applies to cloc                                                    |                                                                                                                                                           |                                                                                           |                  |                                       |                         |                      |  |  |  |  |  |

mode as a transitional clock source between the two PLL modes.

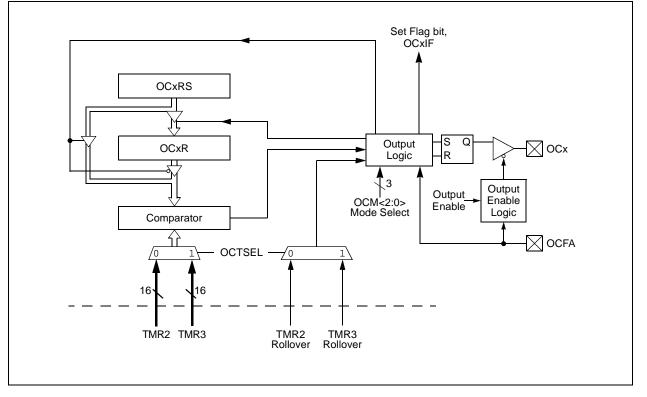

## 14.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70209) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The output compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Output Compare Control register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

The output compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault Protection

- PWM mode with Fault Protection

#### FIGURE 14-1: OUTPUT COMPARE x MODULE BLOCK DIAGRAM

| REGISTER            | 16-2: SPIXC                      | ON1: SPIx C                                   | ONTROL RE            | EGISTER 1                              |                      |                                       |                      |

|---------------------|----------------------------------|-----------------------------------------------|----------------------|----------------------------------------|----------------------|---------------------------------------|----------------------|

| U-0                 | U-0                              | U-0                                           | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                                 | R/W-0                |

| _                   | —                                | —                                             | DISSCK               | DISSDO                                 | MODE16               | SMP                                   | CKE <sup>(1)</sup>   |

| bit 15              |                                  |                                               |                      |                                        |                      |                                       | bit 8                |

| R/W-0               | R/W-0                            | R/W-0                                         | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                                 | R/W-0                |

| SSEN <sup>(2)</sup> | CKP                              | MSTEN                                         | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup>                   | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup>                  | PPRE0 <sup>(3)</sup> |

| bit 7               |                                  | l                                             |                      | 1                                      |                      |                                       | bit (                |

| Legend:             |                                  |                                               |                      |                                        |                      |                                       |                      |

| R = Readab          | le bit                           | W = Writable                                  | bit                  | U = Unimplen                           | nented bit, read     | l as '0'                              |                      |

| -n = Value a        | t POR                            | '1' = Bit is set                              |                      | '0' = Bit is cle                       | ared                 | x = Bit is unkr                       | nown                 |

| bit 15-13           | Unimplemen                       | ted: Read as '                                | 0'                   |                                        |                      |                                       |                      |

| bit 12              | DISSCK: Disa                     | able SCKx pin                                 | bit (SPI Maste       | r modes only)                          |                      |                                       |                      |

|                     |                                  | PI clock is disa                              | •                    | tions as I/O                           |                      |                                       |                      |

|                     |                                  | PI clock is ena                               |                      |                                        |                      |                                       |                      |

| bit 11              |                                  | able SDOx pin                                 |                      |                                        |                      |                                       |                      |

|                     |                                  | is not used by is controlled b                |                      | oin functions as                       | s I/O                |                                       |                      |

| pit 10              | -                                | ord/Byte Comm                                 | -                    | ect bit                                |                      |                                       |                      |

|                     | 1 = Communi                      | cation is word-                               | wide (16 bits)       |                                        |                      |                                       |                      |

|                     | 0 = Communi                      | cation is byte-                               | wide (8 bits)        |                                        |                      |                                       |                      |

| bit 9               | SMP: SPIx D                      | ata Input Samp                                | ole Phase bit        |                                        |                      |                                       |                      |

|                     |                                  | <u>:</u><br>a sampled at er<br>a sampled at m |                      |                                        |                      |                                       |                      |

|                     | Slave mode:                      | -                                             |                      | n Slave mode.                          |                      |                                       |                      |

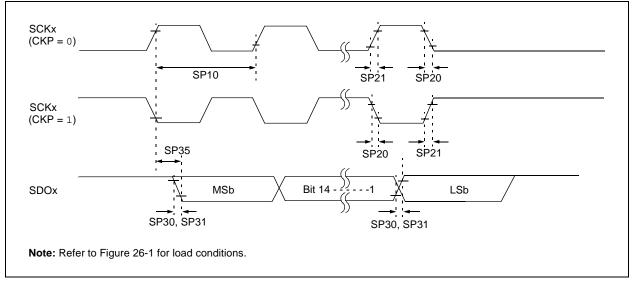

| bit 8               | CKE: Clock E                     | dge Select bit                                | (1)                  |                                        |                      |                                       |                      |

|                     |                                  |                                               |                      |                                        |                      | lle clock state (<br>ve clock state ( |                      |

| bit 7               | SSEN: SPIX S                     | Slave Select E                                | nable bit (Slav      | e mode) <sup>(2)</sup>                 |                      |                                       |                      |

|                     |                                  | s used for Slav<br>s not used by th           |                      | is controlled b                        | by port function     |                                       |                      |

| oit 6               | CKP: Clock F                     | Polarity Select I                             | oit                  |                                        |                      |                                       |                      |

|                     |                                  |                                               |                      | ve state is a lov<br>e state is a high |                      |                                       |                      |

| bit 5               | MSTEN: Mas                       | ter Mode Enab                                 | ole bit              |                                        |                      |                                       |                      |

|                     | 1 = Master m<br>0 = Slave mo     |                                               |                      |                                        |                      |                                       |                      |

|                     | he CKE bit is not<br>FRMEN = 1). | used in the Fra                               | amed SPI moo         | des. Program ti                        | his bit to '0' for   | the Framed SP                         | 'l modes             |

|                     | his bit must be cl               |                                               |                      |                                        |                      |                                       |                      |

| 3: D                | o not set both pri               | mary and seco                                 | ondary prescal       | ers to a value o                       | of 1:1.              |                                       |                      |

## REGISTER 16-2: SPIxCON1: SPIx CONTROL REGISTER 1

## REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6 | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that will be transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                         |

| bit 4 | <ul> <li>ACKEN: Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master, applicable during master receive)</li> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit; hardware clears at end of master Acknowledge sequence</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as $I^2C$ master)<br>1 = Enables Receive mode for $I^2C$ ; hardware clears at end of eighth bit of the master receive data byte<br>0 = Receive sequence is not in progress                                                                                                                        |

| bit 2 | <ul> <li>PEN: Stop Condition Enable bit (when operating as l<sup>2</sup>C master)</li> <li>1 = Initiates Stop condition on SDAx and SCLx pins; hardware clears at end of the master Stop sequence</li> <li>0 = Stop condition not in progress</li> </ul>                                                                                          |

| bit 1 | <ul> <li>RSEN: Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins; hardware clears at end of the master Repeated Start sequence</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                                              |

| bit 0 | <ul> <li>SEN: Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiates Start condition on SDAx and SCLx pins; hardware clears at end of master Start sequence</li> <li>0 = Start condition is not in progress</li> </ul>                                                                                       |

|                 | REGI                                                                                                               | STER                                                   |                                        | X WASK GA        | ATING CONTI                            | ROL             |       |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------|------------------|----------------------------------------|-----------------|-------|--|--|--|

| R/W-0           | U-0                                                                                                                | R/W-0                                                  | R/W-0                                  | R/W-0            | R/W-0                                  | R/W-0           | R/W-0 |  |  |  |

| HLMS            |                                                                                                                    | OCEN                                                   | OCNEN                                  | OBEN             | OBNEN                                  | OAEN            | OANEN |  |  |  |

| bit 15          |                                                                                                                    |                                                        |                                        |                  |                                        |                 | bit 8 |  |  |  |

| R/W-0           | R/W-0                                                                                                              | R/W-0                                                  | R/W-0                                  | R/W-0            | R/W-0                                  | R/W-0           | R/W-0 |  |  |  |

| NAGS            | PAGS                                                                                                               | ACEN                                                   | ACNEN                                  | ABEN             | ABNEN                                  | AAEN            | AANEN |  |  |  |

| bit 7           |                                                                                                                    |                                                        |                                        |                  |                                        |                 | bit 0 |  |  |  |

| Legend:         |                                                                                                                    |                                                        |                                        |                  |                                        |                 |       |  |  |  |

| R = Readable b  | oit                                                                                                                | W = Writable                                           | bit                                    | U = Unimple      | mented bit, read                       | d as '0'        |       |  |  |  |

| -n = Value at P | OR                                                                                                                 | '1' = Bit is se                                        | t                                      | '0' = Bit is cle | eared                                  | x = Bit is unki | nown  |  |  |  |

| bit 15          | 1 = The mas<br>0 = The mas                                                                                         | king (blanking)                                        | function will pro<br>function will pro | event any asse   | erted ('0') compa<br>erted ('1') compa |                 |       |  |  |  |

| bit 14          | -                                                                                                                  | nted: Read as                                          |                                        | L :4             |                                        |                 |       |  |  |  |

| bit 13          | 1 = MCI is c                                                                                                       | Gate C Input In<br>connected to OF<br>not connected to | R gate                                 | DIT              |                                        |                 |       |  |  |  |

| bit 12          | OCNEN: OF                                                                                                          | R Gate C Input                                         | Inverted Enabl                         | e bit            |                                        |                 |       |  |  |  |

|                 | <ul> <li>1 = Inverted MCI is connected to OR gate</li> <li>0 = Inverted MCI is not connected to OR gate</li> </ul> |                                                        |                                        |                  |                                        |                 |       |  |  |  |

| bit 11          | OBEN: OR                                                                                                           | R Gate B Input Inverted Enable bit                     |                                        |                  |                                        |                 |       |  |  |  |

|                 |                                                                                                                    | onnected to OF<br>ot connected to                      |                                        |                  |                                        |                 |       |  |  |  |

| bit 10          |                                                                                                                    | R Gate B Input                                         |                                        |                  |                                        |                 |       |  |  |  |

|                 |                                                                                                                    | MBI is connect<br>MBI is not con                       |                                        |                  |                                        |                 |       |  |  |  |

| bit 9           | OAEN: OR                                                                                                           | Gate A Input Er                                        | nable bit                              |                  |                                        |                 |       |  |  |  |

|                 |                                                                                                                    | onnected to OF<br>ot connected to                      |                                        |                  |                                        |                 |       |  |  |  |

| bit 8           | OANEN: OF                                                                                                          | R Gate A Input                                         | Inverted Enabl                         | e bit            |                                        |                 |       |  |  |  |

|                 |                                                                                                                    | MAI is connect<br>MAI is not con                       | •                                      |                  |                                        |                 |       |  |  |  |