Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 14x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp104-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

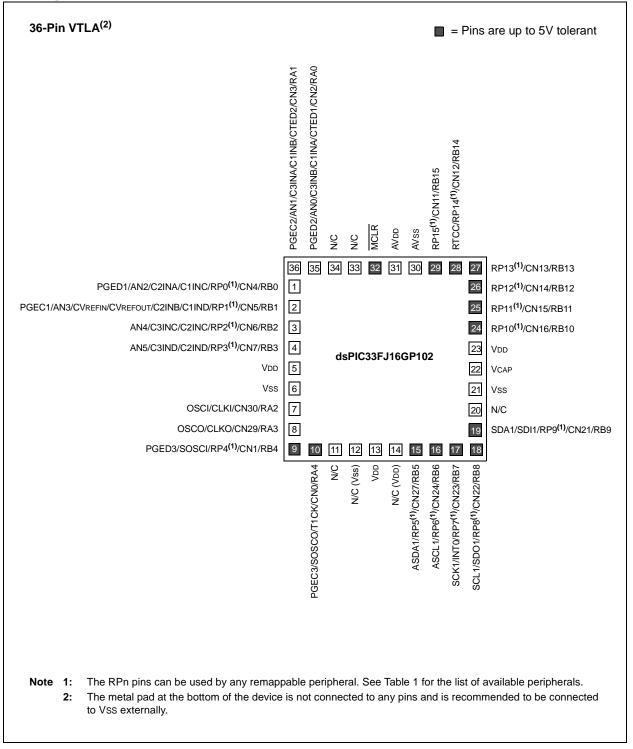

### Pin Diagrams (Continued)

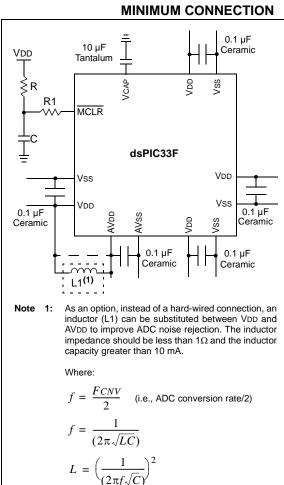

### FIGURE 2-1: RECOMMENDED

### TANK CAPACITORS 2.2.1

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7 µF to 47 µF.

### 2.3 **CPU Logic Filter Capacitor Connection (VCAP)**

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7 µF and 10 µF, 16V connected to ground. The type can be ceramic or tantalum. Refer to Section 26.0 "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to Section 23.2 "On-Chip Voltage Regulator" for details.

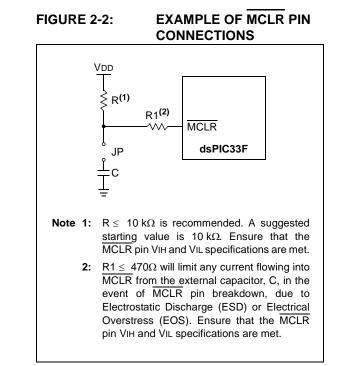

### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

### 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70204) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33FJ16(GP/MC)101/102 The and dsPIC33FJ32(GP/MC)101/102/104 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can serve as a data, address, or address offset register. The 16th Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

There are two classes of instruction in the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices are capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model for the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 is shown in Figure 3-2.

### 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

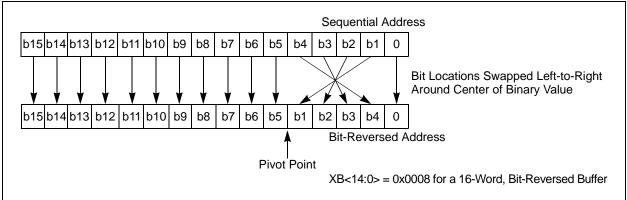

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program-to-data-space mapping feature lets any instruction access program space as if it were data space.

### 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory, while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain Working registers to each address space.

### TABLE 4-41: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

|    | Normal Address |    |    |         |    |    | Bit-Rev | ersed Ac | ldress  |

|----|----------------|----|----|---------|----|----|---------|----------|---------|

| A3 | A2             | A1 | A0 | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0              | 0  | 0  | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0              | 0  | 1  | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0              | 1  | 0  | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0              | 1  | 1  | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1              | 0  | 0  | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1              | 0  | 1  | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1              | 1  | 0  | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1              | 1  | 1  | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0              | 0  | 0  | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0              | 0  | 1  | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0              | 1  | 0  | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0              | 1  | 1  | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1              | 0  | 0  | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1              | 0  | 1  | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1              | 1  | 0  | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1              | 1  | 1  | 15      | 1  | 1  | 1       | 1        | 15      |

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>                                                          |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit                                                                                                     |

|       | 1 = Interrupt request has occurred                                                                                                                           |

|       | 0 = Interrupt request has not occurred                                                                                                                       |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit                                                                                                                 |

|       | 1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                                                                                 |

|       | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>INTOIF: External Interrupt 0 Flag Status bit</li> </ul> |

| U-0                            | R/W-1                                                                                                                          | R/W-0                                | R/W-0             | U-0             | R/W-1             | R/W-0           | R/W-0          |  |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------|-----------------|-------------------|-----------------|----------------|--|--|--|--|--|

| —                              | U1RXIP2                                                                                                                        | U1RXIP1                              | U1RXIP0           | —               | SPI1IP2           | SPI1IP1         | SPI1IP0        |  |  |  |  |  |

| bit 15                         |                                                                                                                                |                                      |                   |                 |                   |                 | bit            |  |  |  |  |  |

|                                | D 444                                                                                                                          | DAMA                                 | DAMA              |                 | D 44/ 4           | DAMA            | DAMO           |  |  |  |  |  |

| U-0                            | R/W-1<br>SPI1EIP2                                                                                                              | R/W-0<br>SPI1EIP1                    | R/W-0<br>SPI1EIP0 | U-0             | R/W-1<br>T3IP2    | R/W-0<br>T3IP1  | R/W-0<br>T3IP0 |  |  |  |  |  |

| bit 7                          | OTTEN 2                                                                                                                        | OFFICIENT                            | OFFICIENT         |                 | 10112             | 1011 1          | bit            |  |  |  |  |  |

|                                |                                                                                                                                |                                      |                   |                 |                   |                 | _              |  |  |  |  |  |

| <b>Legend:</b><br>R = Readable | hit.                                                                                                                           |                                      | <b>b</b> :+       |                 | mantad hit raa    |                 |                |  |  |  |  |  |

|                                |                                                                                                                                | W = Writable                         |                   | -               | emented bit, read |                 |                |  |  |  |  |  |

| -n = Value at                  | POR                                                                                                                            | '1' = Bit is set                     |                   | '0' = Bit is cl | eared             | x = Bit is unkı | lown           |  |  |  |  |  |

| bit 15                         | Unimplemen                                                                                                                     | ted: Read as '                       | 0'                |                 |                   |                 |                |  |  |  |  |  |

| bit 14-12                      | -                                                                                                                              |                                      |                   | Priority bits   |                   |                 |                |  |  |  |  |  |

|                                | <b>U1RXIP&lt;2:0&gt;:</b> UART1 Receiver Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              |                                      | 3                 | 5               |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •<br>001 = Interrupt is Priority 1                                                                                             |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                |                                                                                                                                | pt is Friding 1<br>pt source is dis  | abled             |                 |                   |                 |                |  |  |  |  |  |

| bit 11                         |                                                                                                                                | ted: Read as '                       |                   |                 |                   |                 |                |  |  |  |  |  |

| bit 10-8                       | -                                                                                                                              |                                      |                   | v bits          |                   |                 |                |  |  |  |  |  |

|                                | <b>SPI1IP&lt;2:0&gt;:</b> SPI1 Event Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)     |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              | pt le 1 llell, j 1 l                 | (geet pe          | .,              |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •<br>001 = Interrupt is Priority 1                                                                                             |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                |                                                                                                                                | pt is Phonity 1<br>pt source is dis  | abled             |                 |                   |                 |                |  |  |  |  |  |

| bit 7                          |                                                                                                                                | ited: Read as '                      |                   |                 |                   |                 |                |  |  |  |  |  |

| bit 6-4                        | -                                                                                                                              |                                      |                   | ty hite         |                   |                 |                |  |  |  |  |  |

|                                | <b>SPI1EIP&lt;2:0&gt;:</b> SPI1 Error Interrupt Priority bits                                                                  |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul>                                                 |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | 001 = Interru                                                                                                                  | pt is Priority 1<br>pt source is dis | abled             |                 |                   |                 |                |  |  |  |  |  |

| bit 3                          |                                                                                                                                | ited: Read as '                      |                   |                 |                   |                 |                |  |  |  |  |  |

| bit 2-0                        | -                                                                                                                              | imer3 Interrupt                      |                   |                 |                   |                 |                |  |  |  |  |  |

| Dit 2-0                        |                                                                                                                                | pt is Priority 7                     | -                 | ty interrupt)   |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              | prist nonty /                        | (ingriest priorit | ly interrupt)   |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |  |

|                                | 001 = Interru                                                                                                                  | nt in Driarity 1                     |                   |                 |                   |                 |                |  |  |  |  |  |

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| 11.0            | 11.0               | 11.0               | U-0             | U-0              | U-0                     | U-0                     | U-0                    |

|-----------------|--------------------|--------------------|-----------------|------------------|-------------------------|-------------------------|------------------------|

| U-0             | U-0                | U-0                | 0-0             | 0-0              | 0-0                     | 0-0                     | 0-0                    |

|                 | —                  | —                  |                 | —                | —                       | —                       |                        |

| bit 15          |                    |                    |                 |                  |                         |                         | bit                    |

|                 |                    |                    |                 |                  |                         |                         |                        |

| U-0             | R/W-1              | R/W-0              | R/W-0           | U-0              | R/W-0                   | R/W-0                   | R/W-0                  |

|                 | U1EIP2             | U1EIP1             | U1EIP0          | —                | FLTB1IP2 <sup>(1)</sup> | FLTB1IP1 <sup>(1)</sup> | FLTB1IP0 <sup>(1</sup> |

| bit 7           |                    |                    |                 |                  |                         |                         | bit (                  |

|                 |                    |                    |                 |                  |                         |                         |                        |

| Legend:         |                    |                    |                 |                  |                         |                         |                        |

| R = Readable    | bit                | W = Writable       | bit             | U = Unimpler     | mented bit, read        | as '0'                  |                        |

| -n = Value at P | OR                 | '1' = Bit is set   |                 | '0' = Bit is cle | ared                    | x = Bit is unkr         | nown                   |

|                 |                    |                    |                 |                  |                         |                         |                        |

| bit 15-7        | Unimplemen         | ted: Read as '     | 0'              |                  |                         |                         |                        |

| bit 6-4         | U1EIP<2:0>:        | UART1 Error I      | nterrupt Priori | ty bits          |                         |                         |                        |

|                 | 111 = Interrup     | ot is Priority 7 ( | highest priorit | y interrupt)     |                         |                         |                        |

|                 | •                  |                    |                 |                  |                         |                         |                        |

|                 | •                  |                    |                 |                  |                         |                         |                        |

|                 | •                  |                    |                 |                  |                         |                         |                        |

|                 | 001 = Interrup     |                    |                 |                  |                         |                         |                        |

|                 |                    | ot source is dis   |                 |                  |                         |                         |                        |

| bit 3           | -                  | ted: Read as '     |                 | (4)              |                         |                         |                        |

| bit 2-0         |                    | >: PWM1 Faul       |                 | •                |                         |                         |                        |

|                 | 111 = Interrup     | ot is Priority 7 ( | highest priorit | y interrupt)     |                         |                         |                        |

|                 | •                  |                    |                 |                  |                         |                         |                        |

|                 | •                  |                    |                 |                  |                         |                         |                        |

|                 | •                  |                    |                 |                  |                         |                         |                        |

|                 | 001 = Interrup     |                    | a b la d        |                  |                         |                         |                        |

|                 | 000 = interruption | ot source is dis   | abied           |                  |                         |                         |                        |

### REGISTER 7-26: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| Input Name              | Function Name | Register | Configuration<br>Bits     |

|-------------------------|---------------|----------|---------------------------|

| External Interrupt 1    | INT1          | RPINR0   | INT1R<4:0>                |

| External Interrupt 2    | INT2          | RPINR1   | INT2R<4:0>                |

| Timer2 External Clock   | T2CK          | RPINR3   | T2CKR<4:0>                |

| Timer3 External Clock   | T3CK          | RPINR3   | T3CKR<4:0>                |

| Timer4 External Clock   | T4CK          | RPINR4   | T4CKR<4:0> <sup>(2)</sup> |

| Timer5 External Clock   | T5CK          | RPINR4   | T5CKR<4:0> <sup>(2)</sup> |

| Input Capture 1         | IC1           | RPINR7   | IC1R<4:0>                 |

| Input Capture 2         | IC2           | RPINR7   | IC2R<4:0>                 |

| Input Capture 3         | IC3           | RPINR8   | IC3R<4:0>                 |

| Output Compare Fault A  | OCFA          | RPINR11  | OCFAR<4:0>                |

| UART1 Receive           | U1RX          | RPINR18  | U1RXR<4:0>                |

| UART1 Clear-to-Send     | U1CTS         | RPINR18  | U1CTSR<4:0>               |

| SDI1 SPI Data Input 1   | SDI1          | RPINR20  | SDI1R<4:0> <sup>(2)</sup> |

| SCK1 SPI Clock Input 1  | SCK1          | RPINR20  | SCK1R<4:0> <sup>(2)</sup> |

| SPI1 Slave Select Input | SS1           | RPINR21  | SS1R<4:0> <sup>(2)</sup>  |

### TABLE 10-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)<sup>(1)</sup>

Note 1: Unless otherwise noted, all inputs use the Schmitt input buffers.

2: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

NOTES:

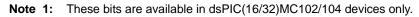

## FIGURE 12-1: TIMER2/3 AND TIMER4/5 (32-BIT) BLOCK DIAGRAM<sup>(1,3,4)</sup>

**4:** Where 'x' or 'y' is present, x = 2 or 4; y = 3 or 5.

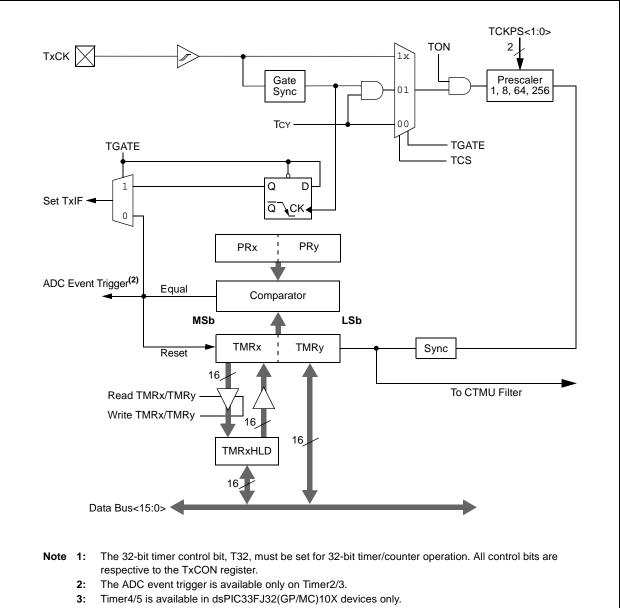

FIGURE 12-2: TIMER2 AND TIMER4 (16-BIT) BLOCK DIAGRAM<sup>(1)</sup>

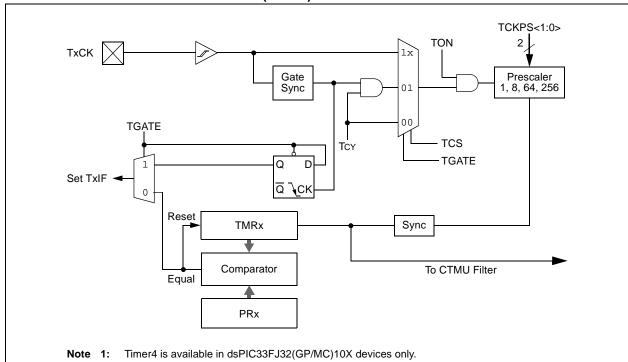

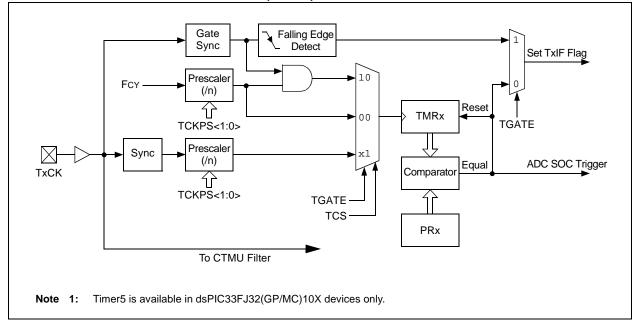

### FIGURE 12-3: TIMER3 AND TIMER5 (16-BIT) BLOCK DIAGRAM<sup>(1)</sup>

| REGISTER              | 12-3: T4CO                                                                                         | N: TIMER4 C                           | ONTROL RI      | EGISTER <sup>(1)</sup> |                 |                 |      |  |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------|---------------------------------------|----------------|------------------------|-----------------|-----------------|------|--|--|--|--|--|

| R/W-0                 | U-0                                                                                                | R/W-0                                 | U-0            | U-0                    | U-0             | U-0             | U-0  |  |  |  |  |  |

| TON                   | —                                                                                                  | TSIDL                                 | —              | —                      | —               | —               | —    |  |  |  |  |  |

| bit 15                |                                                                                                    |                                       |                |                        |                 |                 | bita |  |  |  |  |  |

| U-0                   | R/W-0                                                                                              | R/W-0                                 | R/W-0          | R/W-0                  | U-0             | R/W-0           | U-0  |  |  |  |  |  |

| _                     | TGATE                                                                                              | TCKPS1                                | TCKPS0         | T32                    | _               | TCS             | _    |  |  |  |  |  |

| bit 7                 |                                                                                                    |                                       |                |                        |                 |                 | bit  |  |  |  |  |  |

|                       |                                                                                                    |                                       |                |                        |                 |                 |      |  |  |  |  |  |

| Legend:<br>R = Readab | le hit                                                                                             | W = Writable                          | hit            | II – Unimpler          | mented bit, rea | nd as 'O'       |      |  |  |  |  |  |

| -n = Value a          |                                                                                                    | '1' = Bit is set                      |                | '0' = Bit is cle       |                 | x = Bit is unkn | own  |  |  |  |  |  |

|                       |                                                                                                    |                                       |                |                        |                 |                 |      |  |  |  |  |  |

| bit 15                | TON: Timer4                                                                                        |                                       |                |                        |                 |                 |      |  |  |  |  |  |

|                       | $\frac{\text{When T32}}{1 = \text{Starts 32}}$                                                     |                                       |                |                        |                 |                 |      |  |  |  |  |  |

|                       | 1 = Starts 32 - 0 = Stops 32 - 0 = Stops 32 - 0 = Stops 32 - 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 |                                       |                |                        |                 |                 |      |  |  |  |  |  |

|                       | When T32 =                                                                                         |                                       |                |                        |                 |                 |      |  |  |  |  |  |

|                       | 1 = Starts 16-                                                                                     |                                       |                |                        |                 |                 |      |  |  |  |  |  |

|                       | 0 = Stops 16-                                                                                      | bit Timer4                            |                |                        |                 |                 |      |  |  |  |  |  |

| bit 14                | Unimplemen                                                                                         | ted: Read as '                        | 0'             |                        |                 |                 |      |  |  |  |  |  |

| bit 13                | TSIDL: Time                                                                                        | TSIDL: Timer4 Stop in Idle Mode bit   |                |                        |                 |                 |      |  |  |  |  |  |

|                       |                                                                                                    | ues module op<br>s module opera       |                | device enters l<br>ode | ldle mode       |                 |      |  |  |  |  |  |

| bit 12-7              | Unimplemen                                                                                         | ted: Read as '                        | 0'             |                        |                 |                 |      |  |  |  |  |  |

| bit 6                 | TGATE: Time                                                                                        | er4 Gated Time                        | e Accumulation | n Enable bit           |                 |                 |      |  |  |  |  |  |

|                       |                                                                                                    | When $TCS = 1$ :                      |                |                        |                 |                 |      |  |  |  |  |  |

|                       | -                                                                                                  | This bit is ignored.                  |                |                        |                 |                 |      |  |  |  |  |  |

|                       | <u>When TCS = 0:</u><br>1 = Gated time accumulation is enabled                                     |                                       |                |                        |                 |                 |      |  |  |  |  |  |

|                       |                                                                                                    | ne accumulatio                        |                |                        |                 |                 |      |  |  |  |  |  |

| bit 5-4               |                                                                                                    | : Timer4 Input                        |                | le Select bits         |                 |                 |      |  |  |  |  |  |

|                       | 11 = 1:256                                                                                         | · · · · · · · · · · · · · · · · · · · | 0.000.00000    |                        |                 |                 |      |  |  |  |  |  |

|                       | 10 <b>= 1:64</b>                                                                                   |                                       |                |                        |                 |                 |      |  |  |  |  |  |

|                       | 01 = 1:8                                                                                           |                                       |                |                        |                 |                 |      |  |  |  |  |  |

|                       | 00 = 1:1                                                                                           |                                       |                |                        |                 |                 |      |  |  |  |  |  |

| bit 3                 |                                                                                                    | imer Mode Sel                         |                | •                      |                 |                 |      |  |  |  |  |  |

|                       |                                                                                                    | nd Timer5 form<br>nd Timer5 act a     | •              |                        |                 |                 |      |  |  |  |  |  |

| bit 2                 |                                                                                                    | ited: Read as '                       |                | inters                 |                 |                 |      |  |  |  |  |  |

| bit 1                 | -                                                                                                  | Clock Source                          |                |                        |                 |                 |      |  |  |  |  |  |

|                       |                                                                                                    | clock from pin,                       |                | rising edge)           |                 |                 |      |  |  |  |  |  |

|                       | 0 = Internal c                                                                                     |                                       |                | nonig ougo)            |                 |                 |      |  |  |  |  |  |

| bit 0                 | Unimplemen                                                                                         | ted: Read as '                        | 0'             |                        |                 |                 |      |  |  |  |  |  |

| Note 1: ⊤             | his register is ava                                                                                | ailable in dsPIC                      | C33FJ32(GP/N   | MC)10X device          | s only.         |                 |      |  |  |  |  |  |

|                       | -                                                                                                  |                                       | `              |                        | -               |                 |      |  |  |  |  |  |

# REGISTER 12-3: T4CON: TIMER4 CONTROL REGISTER<sup>(1)</sup>

# EXAMPLE 15-1: ASSEMBLY CODE FOR WRITE-PROTECTED REGISTER UNLOCK AND FAULT CLEARING SEQUENCE

| ; FLTA1 pin must be pulled high externally in order to clear and disable the Fault<br>; Writing to P1FLTBCON register requires unlock sequence                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 ; Load first unlock key to w10 register<br/>mov #0x4321,w11 ; Load second unlock key to w11 register<br/>mov #0x0000,w0 ; Load desired value of P1FLTACON register in w0<br/>mov w10, PWM1KEY ; Write first unlock key to PWM1KEY register<br/>mov w11, PWM1KEY ; Write second unlock key to PWM1KEY register<br/>mov w0,P1FLTACON ; Write desired value to P1FLTACON register</pre> |

| ; FLTB1 pin must be pulled high externally in order to clear and disable the Fault ; Writing to P1FLTBCON register requires unlock sequence                                                                                                                                                                                                                                                               |

| <pre>mov #0xabcd,w10 ; Load first unlock key to w10 register<br/>mov #0x4321,w11 ; Load second unlock key to w11 register<br/>mov #0x0000,w0 ; Load desired value of P1FLTBCON register in w0<br/>mov w10, PWM1KEY ; Write first unlock key to PWM1KEY register<br/>mov w11, PWM1KEY ; Write second unlock key to PWM1KEY register<br/>mov w0,P1FLTBCON ; Write desired value to P1FLTBCON register</pre> |

| ; Enable all PWMs using PWM1CON1 register<br>; Writing to PWM1CON1 register requires unlock sequence                                                                                                                                                                                                                                                                                                      |

| <pre>mov #0xabcd,w10 ; Load first unlock key to w10 register<br/>mov #0x4321,w11 ; Load second unlock key to w11 register<br/>mov #0x0077,w0 ; Load desired value of PWM1CON1 register in w0<br/>mov w10, PWM1KEY ; Write first unlock key to PWM1KEY register<br/>mov w11, PWM1KEY ; Write second unlock key to PWM1KEY register<br/>mov w0,PWM1CON1 ; Write desired value to PWM1CON1 register</pre>    |

# EXAMPLE 15-2: C CODE FOR WRITE-PROTECTED REGISTER UNLOCK AND FAULT CLEARING SEQUENCE

// FLTAl pin must be pulled high externally in order to clear and disable the Fault // Writing to PIFLTACON register requires unlock sequence // Use builtin function to write 0x0000 to PIFLTACON register \_\_builtin\_write\_PWMSFR(&PIFLTACON, 0x0000, &PWM1KEY); // FLTBl pin must be pulled high externally in order to clear and disable the Fault // Writing to PIFLTBCON register requires unlock sequence // Use builtin function to write 0x0000 to PIFLTBCON register \_\_builtin\_write\_PWMSFR(&PIFLTBCON, 0x0000, &PWM1KEY); // Enable all PWMs using PWM1CON1 register // Writing to PWM1CON1 register requires unlock sequence // Use builtin function to write 0x0077 to PWM1CON1 register \_\_builtin\_write\_PWMSFR(&PWM1CON1, 0x0077, &PWM1KEY);

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

### 15.4 **PWM Control Registers**

### R/W-0 U-0 R/W-0 U-0 U-0 U-0 U-0 U-0 PTEN PTSIDL bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 PTOPS3 PTOPS2 PTOPS1 PTOPS0 PTCKPS1 PTCKPS0 PTMOD1 PTMOD0 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 PTEN: PWMx Time Base Timer Enable bit 1 = PWMx time base is on 0 = PWMx time base is off bit 14 Unimplemented: Read as '0' bit 13 PTSIDL: PWMx Time Base Stop in Idle Mode bit 1 = PWMx time base halts in CPU Idle mode 0 = PWMx time base runs in CPU Idle mode bit 12-8 Unimplemented: Read as '0' bit 7-4 PTOPS<3:0>: PWMx Time Base Output Postscale Select bits 1111 = 1:16 postscale 0001 = 1:2 postscale 0000 = 1:1 postscale bit 3-2 PTCKPS<1:0>: PWMx Time Base Input Clock Prescale Select bits 11 = PWMx time base input clock period is 64 Tcy (1:64 prescale) 10 = PWMx time base input clock period is 16 Tcy (1:16 prescale) 01 = PWMx time base input clock period is 4 Tcy (1:4 prescale) 00 = PWMx time base input clock period is TCY (1:1 prescale) bit 1-0 PTMOD<1:0>: PWMx Time Base Mode Select bits 11 = PWMx time base operates in a Continuous Up/Down Count mode with interrupts for double **PWM updates** 10 = PWMx time base operates in a Continuous Up/Down Count mode 01 = PWMx time base operates in Single Pulse mode

### **REGISTER 15-1: PxTCON: PWMx TIME BASE CONTROL REGISTER**

00 = PWMx time base operates in a Free-Running mode

| R/W-0                                                                  | R/W-0                                                                                                                                               | R/W-0                              | R/W-0          | R/W-0            | R/W-0            | R/W-0              | R/W-0 |  |  |  |  |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|------------------|------------------|--------------------|-------|--|--|--|--|

| DTBPS1                                                                 | DTBPS0                                                                                                                                              | DTB5                               | DTB4           | DTB3             | DTB2             | DTB1               | DTB0  |  |  |  |  |

| bit 15                                                                 | •                                                                                                                                                   | •                                  |                | ·                |                  |                    | bit 8 |  |  |  |  |

|                                                                        |                                                                                                                                                     |                                    |                |                  |                  |                    |       |  |  |  |  |

| R/W-0                                                                  | R/W-0                                                                                                                                               | R/W-0                              | R/W-0          | R/W-0            | R/W-0            | R/W-0              | R/W-0 |  |  |  |  |

| DTAPS1                                                                 | DTAPS0                                                                                                                                              | DTA5                               | DTA4           | DTA3             | DTA2             | DTA1               | DTA0  |  |  |  |  |

| bit 7                                                                  |                                                                                                                                                     |                                    |                |                  |                  |                    | bit 0 |  |  |  |  |

|                                                                        |                                                                                                                                                     |                                    |                |                  |                  |                    |       |  |  |  |  |

| Legend:                                                                |                                                                                                                                                     |                                    |                |                  |                  |                    |       |  |  |  |  |

| R = Readabl                                                            | le bit                                                                                                                                              | W = Writable                       | bit            | U = Unimpler     | mented bit, read | l as '0'           |       |  |  |  |  |

| -n = Value at                                                          | t POR                                                                                                                                               | '1' = Bit is set                   |                | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |  |  |  |

|                                                                        |                                                                                                                                                     |                                    |                |                  |                  |                    |       |  |  |  |  |

| bit 15-14                                                              | DTBPS<1:0>                                                                                                                                          | : Dead-Time U                      | nit B Prescale | e Select bits    |                  |                    |       |  |  |  |  |

|                                                                        | 11 = Clock period for Dead-Time Unit B is 8 TCY                                                                                                     |                                    |                |                  |                  |                    |       |  |  |  |  |

|                                                                        | 10 = Clock period for Dead-Time Unit B is 4 Tcy                                                                                                     |                                    |                |                  |                  |                    |       |  |  |  |  |

|                                                                        |                                                                                                                                                     | eriod for Dead-<br>eriod for Dead- |                |                  |                  |                    |       |  |  |  |  |

| bit 13-8                                                               | <ul> <li>00 = Clock period for Dead-Time Unit B is TCY</li> <li>DTB&lt;5:0&gt;: Unsigned 6-Bit Dead-Time Value for Dead-Time Unit B bits</li> </ul> |                                    |                |                  |                  |                    |       |  |  |  |  |

| bit 7-6 <b>DTAPS&lt;1:0&gt;:</b> Dead-Time Unit A Prescale Select bits |                                                                                                                                                     |                                    |                |                  |                  |                    |       |  |  |  |  |

|                                                                        | 11 = Clock period for Dead-Time Unit A is 8 TCY                                                                                                     |                                    |                |                  |                  |                    |       |  |  |  |  |

|                                                                        |                                                                                                                                                     | eriod for Dead-                    |                |                  |                  |                    |       |  |  |  |  |

|                                                                        | 01 = Clock period for Dead-Time Unit A is 2 Tcy                                                                                                     |                                    |                |                  |                  |                    |       |  |  |  |  |

### REGISTER 15-7: PxDTCON1: PWMx DEAD-TIME CONTROL REGISTER 1

- 00 = Clock period for Dead-Time Unit A is TCY

- bit 5-0 DTA<5:0>: Unsigned 6-Bit Dead-Time Value for Dead-Time Unit A bits

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

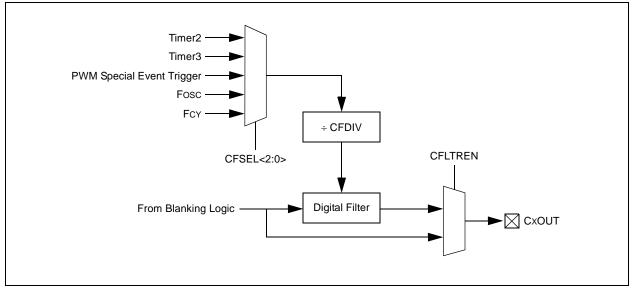

### FIGURE 20-4: DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

### REGISTER 20-3: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT REGISTER (CONTINUED)

| bit 3-0 | SELSRCA<3:0>: Mask A Input Select bits |

|---------|----------------------------------------|

| bit 5-0 |                                        |

|         | 1111 = Reserved                        |

|         | 1110 = Reserved                        |

|         | 1101 = Reserved                        |

|         | 1100 = Reserved                        |

|         | 1011 = Reserved                        |

|         | 1010 = Reserved                        |

|         | 1001 = Reserved                        |

|         | 1000 = Reserved                        |

|         | 0111 = Reserved                        |

|         | 0110 = Reserved                        |

|         | 0101 = PWM1H3                          |

|         | 0100 = PWM1L3                          |

|         | 0011 = PWM1H2                          |

|         | 0010 = PWM1L2                          |

|         | 0001 = PWM1H1                          |

|         | 0000 = PWM1L1                          |

|         |                                        |

|         |                                        |

| DC CHARACTERISTICS |        |                                                                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |            |        |                                                                                                                                                 |  |  |

|--------------------|--------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                                                                 | Min                                                                                                                                                                                                                                                                                     | Тур <sup>(1)</sup> | Мах        | Units  | Conditions                                                                                                                                      |  |  |

|                    | VIL    | Input Low Voltage                                                              |                                                                                                                                                                                                                                                                                         |                    |            |        |                                                                                                                                                 |  |  |

| DI10               |        | I/O Pins                                                                       | Vss                                                                                                                                                                                                                                                                                     | —                  | 0.2 Vdd    | V      |                                                                                                                                                 |  |  |

| DI15               |        | MCLR                                                                           | Vss                                                                                                                                                                                                                                                                                     | _                  | 0.2 Vdd    | V      |                                                                                                                                                 |  |  |

| DI18               |        | I/O Pins with SDAx, SCLx                                                       | Vss                                                                                                                                                                                                                                                                                     | _                  | 0.3 Vdd    | V      | SMBus disabled                                                                                                                                  |  |  |

| DI19               |        | I/O Pins with SDAx, SCLx                                                       | Vss                                                                                                                                                                                                                                                                                     | —                  | 0.8        | V      | SMBus enabled                                                                                                                                   |  |  |

|                    | Vih    | Input High Voltage                                                             |                                                                                                                                                                                                                                                                                         |                    |            |        |                                                                                                                                                 |  |  |

| DI20               |        | I/O Pins Not 5V Tolerant <sup>(4)</sup><br>I/O Pins 5V Tolerant <sup>(4)</sup> | 0.7 Vdd<br>0.7 Vdd                                                                                                                                                                                                                                                                      | _                  | Vdd<br>5.5 | V<br>V |                                                                                                                                                 |  |  |

| DI28               |        | SDAx, SCLx                                                                     | 0.7 Vdd                                                                                                                                                                                                                                                                                 | _                  | 5.5        | V      | SMBus disabled                                                                                                                                  |  |  |

| DI29               |        | SDAx, SCLx                                                                     | 2.1                                                                                                                                                                                                                                                                                     | —                  | 5.5        | V      | SMBus enabled                                                                                                                                   |  |  |

|                    | ICNPU  | CNx Pull-up Current                                                            |                                                                                                                                                                                                                                                                                         |                    |            |        |                                                                                                                                                 |  |  |

| DI30               |        |                                                                                | 50                                                                                                                                                                                                                                                                                      | 250                | 450        | μΑ     | VDD = 3.3V, $VPIN = VSS$                                                                                                                        |  |  |

|                    | lı∟    | Input Leakage Current <sup>(2,3)</sup>                                         |                                                                                                                                                                                                                                                                                         |                    |            |        |                                                                                                                                                 |  |  |

| DI50               |        | I/O Pins 5V Tolerant <sup>(4)</sup>                                            | —                                                                                                                                                                                                                                                                                       | —                  | ±2         | μΑ     | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance                                                                                               |  |  |

| DI51               |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                        | —                                                                                                                                                                                                                                                                                       | _                  | ±1         | μA     | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \text{ at high-impedance}, \\ -40^\circ C \leq TA \leq +85^\circ C \end{array}$ |  |  |

| DI51a              |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                        | —                                                                                                                                                                                                                                                                                       | _                  | ±2         | μA     | Shared with external<br>reference pins,<br>-40°C ≤ TA ≤ +85°C                                                                                   |  |  |

| DI51b              |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                        | —                                                                                                                                                                                                                                                                                       | _                  | ±3.5       | μA     | VSS $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance,<br>-40°C $\leq$ TA $\leq$ +125°C                                                          |  |  |

| DI51c              |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                        | _                                                                                                                                                                                                                                                                                       | _                  | ±8         | μA     | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$                                                  |  |  |

| DI55               |        | MCLR                                                                           | —                                                                                                                                                                                                                                                                                       | —                  | ±2         | μA     | $VSS \leq VPIN \leq VDD$                                                                                                                        |  |  |

| DI56               |        | OSC1                                                                           | —                                                                                                                                                                                                                                                                                       | —                  | ±2         | μΑ     | $\label{eq:VSS} \begin{array}{l} {\sf VSS} \leq {\sf VPIN} \leq {\sf VDD}, \\ {\sf XT} \text{ and } {\sf HS} \text{ modes} \end{array}$         |  |  |

### TABLE 26-10: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 5: VIL source < (Vss 0.3). Characterized but not tested.

**6:** Non-5V tolerant pins, VIH source > (VDD + 0.3), 5V tolerant pins, VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins, not excluded under IICL or IICH conditions, are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

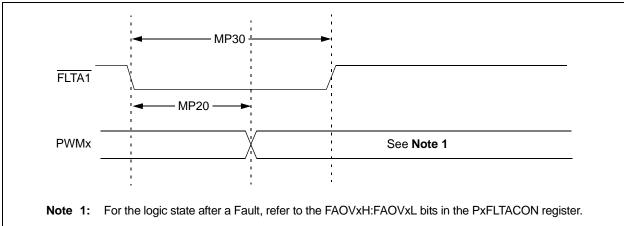

### FIGURE 26-9: MOTOR CONTROL PWMx MODULE FAULT TIMING CHARACTERISTICS

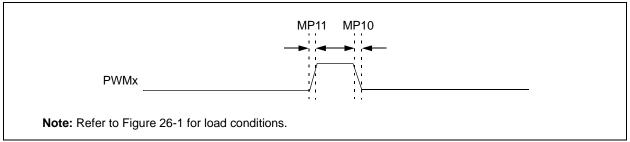

### FIGURE 26-10: MOTOR CONTROL PWMx MODULE TIMING CHARACTERISTICS

### TABLE 26-28: MOTOR CONTROL PWMx MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}\mbox{C} \leq \mbox{TA} \leq +85^{\circ}\mbox{C for Industrial} \\ & -40^{\circ}\mbox{C} \leq \mbox{TA} \leq +125^{\circ}\mbox{C for Extended} \end{array}$ |                              |    |    |                    |  |

|--------------------|--------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----|----|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>      | Min                                                                                                                                                                                                                                                                                                               | Min Typ Max Units Conditions |    |    |                    |  |

| MP10               | TFPWM  | PWM Output Fall Time               | —                                                                                                                                                                                                                                                                                                                 | _                            | —  | ns | See Parameter DO32 |  |

| MP11               | TRPWM  | PWM Output Rise Time               | —                                                                                                                                                                                                                                                                                                                 | —                            | —  | ns | See Parameter DO31 |  |

| MP20               | Tfd    | Fault Input ↓ to PWM<br>I/O Change | —                                                                                                                                                                                                                                                                                                                 |                              | 50 | ns |                    |  |

| MP30               | Tfh    | Minimum Pulse Width                | 50                                                                                                                                                                                                                                                                                                                | _                            |    | ns |                    |  |

**Note 1:** These parameters are characterized by similarity, but are not tested in manufacturing.

### TABLE 26-50: COMPARATOR TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                       | Standard Operating Co<br>(unless otherwise stat<br>Operating temperature |     |      | ,     |            |  |

|--------------------|--------|-------------------------------------------------------|--------------------------------------------------------------------------|-----|------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic                                        | Min.                                                                     | Тур | Max. | Units | Conditions |  |

| 300                | TRESP  | Response Time <sup>(1,2)</sup>                        | _                                                                        | 150 | 400  | ns    |            |  |

| 301                | TMC20V | Comparator Mode Change to Output Valid <sup>(1)</sup> | —                                                                        |     | 10   | μS    |            |  |

| 302                | Ton2ov | Comparator Enabled to<br>Output Valid <sup>(1)</sup>  | —                                                                        | _   | 10   | μs    |            |  |

Note 1: Parameters are characterized but not tested.

2: Response time is measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

### TABLE 26-51: COMPARATOR MODULE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |             |       |            |  |

|--------------------|--------|--------------------------------------------|-------------------------------------------------------|------|-------------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic                             | Min.                                                  | Тур  | Max.        | Units | Conditions |  |