Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 14x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

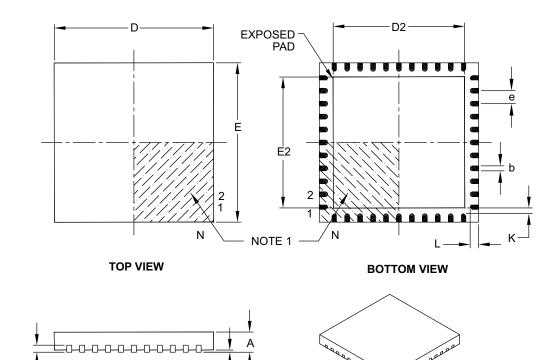

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp104t-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. The following pages show their pinout diagrams.

|                  |      | rte)                  |              |                 | Rem                           | appa          | ble l          | Perip | herals                             | 5   | М                 |            | Ŋ                    |      |      |             |      |          |                                 |

|------------------|------|-----------------------|--------------|-----------------|-------------------------------|---------------|----------------|-------|------------------------------------|-----|-------------------|------------|----------------------|------|------|-------------|------|----------|---------------------------------|

| Device           | Pins | Program Flash (Kbyte) | RAM (Kbytes) | Remappable Pins | 16-bit Timer <sup>(1,2)</sup> | Input Capture | Output Compare | UART  | External Interrupts <sup>(3)</sup> | SPI | Motor Control PWM | PWM Faults | 10-Bit, 1.1 Msps ADC | RTCC | I²C™ | Comparators | CTMU | I/O Pins | Packages                        |

| dsPIC33FJ16GP101 | 18   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 13       | PDIP,<br>SOIC                   |

|                  | 20   | 16                    | 1            | 8               | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | —          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | SSOP                            |

| dsPIC33FJ16GP102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | _                 | _          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

| dsPIC33FJ16MC101 | 20   | 16                    | 1            | 10              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 1          | 1 ADC,<br>4-ch       | Y    | 1    | 3           | Y    | 15       | PDIP,<br>SOIC,<br>SSOP          |

| dsPIC33FJ16MC102 | 28   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 16                    | 1            | 16              | 3                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>6-ch       | Y    | 1    | 3           | Y    | 21       | VTLA                            |

#### TABLE 1:dsPIC33FJ16(GP/MC)101/102 DEVICE FEATURES

**Note 1:** Two out of three timers are remappable.

2: One pair can be combined to create one 32-bit timer.

**3**: Two out of three interrupts are remappable.

| TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED) |             |                   |           |                                                                                                                                       |  |  |  |  |

|------------------------------------------------|-------------|-------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                       | Pin<br>Type | Buffer<br>Type    | PPS       | Description                                                                                                                           |  |  |  |  |

| SCL1                                           | I/O         | ST                | No        | Synchronous serial clock input/output for I2C1.                                                                                       |  |  |  |  |

| SDA1                                           | I/O         | ST                | No        | Synchronous serial data input/output for I2C1.                                                                                        |  |  |  |  |

| ASCL1                                          | I/O         | ST                | No        | Alternate synchronous serial clock input/output for I2C1.                                                                             |  |  |  |  |

| ASDA1                                          | I/O         | ST                | No        | Alternate synchronous serial data input/output for I2C1.                                                                              |  |  |  |  |

| FLTA1(1,2,4)                                   | 1           | ST                | No        | PWM1 Fault A input.                                                                                                                   |  |  |  |  |

| FLTB1 <sup>(3,4)</sup>                         | 1           | ST                | No        | PWM1 Fault B input.                                                                                                                   |  |  |  |  |

| PWM1L1                                         | 0           |                   | No        | PWM1 Low Output 1.                                                                                                                    |  |  |  |  |

| PWM1H1                                         | 0           |                   | No        | PWM1 High Output 1.                                                                                                                   |  |  |  |  |

| PWM1L2                                         | 0           |                   | No        | PWM1 Low Output 2.                                                                                                                    |  |  |  |  |

| PWM1H2                                         | 0           |                   | No        | PWM1 High Output 2.                                                                                                                   |  |  |  |  |

| PWM1L3                                         | 0           |                   | No        | PWM1 Low Output 3.                                                                                                                    |  |  |  |  |

| PWM1H3                                         | Ō           | _                 | No        | PWM1 High Output 3.                                                                                                                   |  |  |  |  |

| RTCC                                           | 0           | Digital           | No        | RTCC Alarm output.                                                                                                                    |  |  |  |  |

| CTPLS                                          | 0           | Digital           | Yes       | CTMU pulse output.                                                                                                                    |  |  |  |  |

| CTED1                                          | I           | Digital           | No        | CTMU External Edge Input 1.                                                                                                           |  |  |  |  |

| CTED2                                          | I           | Digital           | No        | CTMU External Edge Input 2.                                                                                                           |  |  |  |  |

| CVREFIN                                        | I           | Analog            | No        | Comparator Voltage Positive Reference Input.                                                                                          |  |  |  |  |

| CVREFOUT                                       | 0           | Analog            | No        | Comparator Voltage Positive Reference Output.                                                                                         |  |  |  |  |

| C1INA                                          | I           | Analog            | No        | Comparator 1 Positive Input A.                                                                                                        |  |  |  |  |

| C1INB                                          | i           | Analog            | No        | Comparator 1 Negative Input B.                                                                                                        |  |  |  |  |

| C1INC                                          | i           | Analog            | No        | Comparator 1 Negative Input C.                                                                                                        |  |  |  |  |

| C1IND                                          | i           | Analog            | No        | Comparator 1 Negative Input D.                                                                                                        |  |  |  |  |

| C1OUT                                          | Ō           | Digital           | Yes       | Comparator 1 Output.                                                                                                                  |  |  |  |  |

| C2INA                                          | Ĩ           | Analog            | No        | Comparator 2 Positive Input A.                                                                                                        |  |  |  |  |

| C2INB                                          | l i         | Analog            | No        | Comparator 2 Negative Input B.                                                                                                        |  |  |  |  |

| C2INC                                          | i           | Analog            | No        | Comparator 2 Negative Input D.                                                                                                        |  |  |  |  |

| C2INC<br>C2IND                                 |             | Analog            | No        | Comparator 2 Negative Input C.                                                                                                        |  |  |  |  |

| C2OUT                                          | 0           | Digital           | Yes       | Comparator 2 Output.                                                                                                                  |  |  |  |  |

|                                                |             | •                 |           |                                                                                                                                       |  |  |  |  |

| C3INA                                          |             | Analog            | No        | Comparator 3 Positive Input A.                                                                                                        |  |  |  |  |

| C3INB                                          |             | Analog            | No        | Comparator 3 Negative Input B.                                                                                                        |  |  |  |  |

| C3INC                                          |             | Analog            | No        | Comparator 3 Negative Input C.                                                                                                        |  |  |  |  |

| C3IND<br>C3OUT                                 |             | Analog<br>Digital | No<br>Yes | Comparator 3 Negative Input D.<br>Comparator 3 Output.                                                                                |  |  |  |  |

|                                                |             | ST                |           | Data I/O pin for Programming/Debugging Communication Channel 1.                                                                       |  |  |  |  |

| PGED1                                          | I/O         |                   | No        |                                                                                                                                       |  |  |  |  |

| PGEC1                                          |             | ST                | No        | Clock input pin for Programming/Debugging Communication Channel 1.                                                                    |  |  |  |  |

| PGED2                                          | I/O         | ST                | No        | Data I/O pin for Programming/Debugging Communication Channel 2.                                                                       |  |  |  |  |

| PGEC2                                          | I           | ST                | No        | Clock input pin for Programming/Debugging Communication Channel 2.                                                                    |  |  |  |  |

| PGED3<br>PGEC3                                 | I/O         | ST<br>ST          | No<br>No  | Data I/O pin for Programming/Debugging Communication Channel 3.<br>Clock input pin for Programming/Debugging Communication Channel 3. |  |  |  |  |

|                                                | - ·         |                   |           |                                                                                                                                       |  |  |  |  |

| MCLR                                           | I/P         | ST                | No        | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                            |  |  |  |  |

|                                                |             |                   |           | input or output Analog = Analog input P = Power                                                                                       |  |  |  |  |

| S                                              | I = Schr    | nitt Frigger      | input w   | ith CMOS levels O = Output I = Input                                                                                                  |  |  |  |  |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: An external pull-down resistor is required for the FLTA1 pin in dsPIC33FJXXMC101 (20-pin) devices.

- 2: The FLTA1 pin and the PWM1Lx/PWM1Hx pins are available in dsPIC(16/32)MC10X devices only.

- 3: The FLTB1 pin is available in dsPIC(16/32)MC102/104 devices only.

PPS = Peripheral Pin Select

- 4: The PWM Fault pins are enabled during any Reset event. Refer to **Section 15.2 "PWM Faults"** for more information on the PWM Faults.

- 5: Not all pins are available on all devices. Refer to the specific device in the "**Pin Diagrams**" section for availability.

- 6: These pins are available in dsPIC33FJ32(GP/MC)104 (44-pin) devices only.

### 3.4 CPU Control Registers

| R-0                 | R-0                 | R/C-0                                                                                                                                       | R/C-0             | R-0                     | R/C-0              | R-0               | R/W-0         |  |  |  |  |

|---------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------|--------------------|-------------------|---------------|--|--|--|--|

| OA                  | OB                  | SA <sup>(1)</sup>                                                                                                                           | SB <sup>(1)</sup> | OAB                     | SAB                | DA                | DC            |  |  |  |  |

| bit 15              | ·                   |                                                                                                                                             |                   |                         |                    |                   | bit 8         |  |  |  |  |

| (2)                 | )) (2)              | (2)                                                                                                                                         |                   |                         |                    |                   |               |  |  |  |  |

| R/W-0 <sup>(3</sup> |                     | R/W-0 <sup>(3)</sup>                                                                                                                        | R-0               | R/W-0                   | R/W-0              | R/W-0             | R/W-0         |  |  |  |  |

| IPL2 <sup>(2)</sup> | IPL1 <sup>(2)</sup> | IPL0 <sup>(2)</sup>                                                                                                                         | RA                | N                       | OV                 | Z                 | С             |  |  |  |  |

| bit 7               |                     |                                                                                                                                             |                   |                         |                    |                   | bit           |  |  |  |  |

| Legend:             |                     | C = Clearable                                                                                                                               | bit               |                         |                    |                   |               |  |  |  |  |

| R = Reada           | able bit            | W = Writable I                                                                                                                              | oit               | U = Unimpler            | mented bit, read   | l as '0'          |               |  |  |  |  |

| -n = Value          | at POR              | '1' = Bit is set                                                                                                                            |                   | '0' = Bit is cle        | ared               | x = Bit is unkn   | own           |  |  |  |  |

|                     |                     |                                                                                                                                             |                   |                         |                    |                   |               |  |  |  |  |

| bit 15              |                     | ator A Overflow                                                                                                                             |                   |                         |                    |                   |               |  |  |  |  |

|                     |                     | ator A has overf<br>ator A has not o                                                                                                        |                   |                         |                    |                   |               |  |  |  |  |

| bit 14              |                     | ator B Overflow                                                                                                                             |                   |                         |                    |                   |               |  |  |  |  |

| DIL 14              |                     | ator B has overf                                                                                                                            |                   |                         |                    |                   |               |  |  |  |  |

|                     |                     | ator B has not o                                                                                                                            |                   |                         |                    |                   |               |  |  |  |  |

| bit 13              | SA: Accumul         | ator A Saturatio                                                                                                                            | on 'Sticky' Sta   | itus bit <sup>(1)</sup> |                    |                   |               |  |  |  |  |

|                     | 1 = Accumula        | ator A is saturat                                                                                                                           | ed or has be      | en saturated at         | some time          |                   |               |  |  |  |  |

|                     |                     | ator A is not sat                                                                                                                           |                   | (4)                     |                    |                   |               |  |  |  |  |

| bit 12              |                     | <b>SB:</b> Accumulator B Saturation 'Sticky' Status bit <sup>(1)</sup><br>1 = Accumulator B is saturated or has been saturated at some time |                   |                         |                    |                   |               |  |  |  |  |

|                     |                     | ator B is saturat<br>ator B is not sat                                                                                                      |                   | en saturated at         | some time          |                   |               |  |  |  |  |

| bit 11              | <b>OAB:</b> OA    C | OAB: OA    OB Combined Accumulator Overflow Status bit                                                                                      |                   |                         |                    |                   |               |  |  |  |  |

|                     |                     | ators A or B hav                                                                                                                            |                   |                         |                    |                   |               |  |  |  |  |

| bit 10              | <b>SAB:</b> SA    S | SAB: SA    SB Combined Accumulator 'Sticky' Status bit                                                                                      |                   |                         |                    |                   |               |  |  |  |  |

|                     |                     |                                                                                                                                             |                   |                         | urated at some     | time in the past  |               |  |  |  |  |

|                     |                     | ccumulator A o                                                                                                                              |                   |                         | it will clear SA a | and SB            |               |  |  |  |  |

| bit 9               | -                   |                                                                                                                                             |                   | Cleaning this bi        |                    |                   |               |  |  |  |  |

|                     | •                   | <b>DA:</b> DO Loop Active bit<br>1 = DO loop is in progress                                                                                 |                   |                         |                    |                   |               |  |  |  |  |

|                     |                     | not in progres                                                                                                                              | 5                 |                         |                    |                   |               |  |  |  |  |

| bit 8               | DC: MCU AL          | U Half Carry/Bo                                                                                                                             | prrow bit         |                         |                    |                   |               |  |  |  |  |

|                     |                     |                                                                                                                                             | ow-order bit      | (for byte-sized o       | data) or 8th low-  | order bit (for wo | rd-sized data |  |  |  |  |

|                     |                     | sult occurred                                                                                                                               | h low-order       | hit (for hyte-siz       | ed data) or 8th    | low-order bit (f  | or word-sized |  |  |  |  |

|                     | •                   | he result occur                                                                                                                             |                   |                         |                    |                   |               |  |  |  |  |

| Note 1:             | This bit can be rea | nd or cleared (ne                                                                                                                           | ot set).          |                         |                    |                   |               |  |  |  |  |

|                     | The IPL<2:0> bits   |                                                                                                                                             |                   |                         |                    |                   |               |  |  |  |  |

|                     | Level. The value in | n parentheses i                                                                                                                             | ndicates the      | IPL if IPL<3> =         | 1. User interru    | ots are disabled  | when          |  |  |  |  |

|                     | IPL<3> = 1.         |                                                                                                                                             |                   |                         |                    |                   |               |  |  |  |  |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

**3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

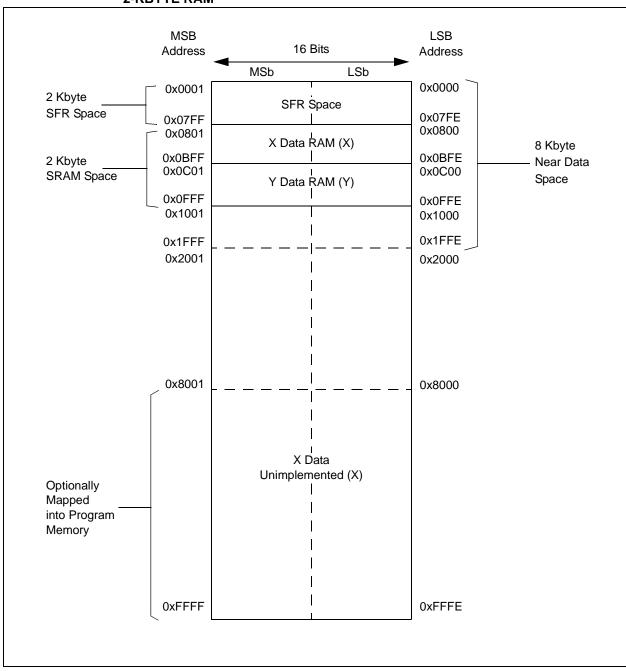

## FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJ32(GP/MC)101/102/104 DEVICES WITH 2-KBYTE RAM

| REGISTER                      | <i>i</i> -J. II 30. I | NTERRUPT                                                                                            |                   |                  |                  |                 |        |  |  |  |  |  |

|-------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|-----------------|--------|--|--|--|--|--|

| U-0                           | U-0                   | R/W-0                                                                                               | R/W-0             | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

| —                             | —                     | AD1IF                                                                                               | U1TXIF            | U1RXIF           | SPI1IF           | SPI1EIF         | T3IF   |  |  |  |  |  |

| pit 15                        |                       |                                                                                                     |                   |                  |                  |                 | bi     |  |  |  |  |  |

| R/W-0                         | R/W-0                 | R/W-0                                                                                               | U-0               | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

| T2IF                          | OC2IF                 | IC2IF                                                                                               | _                 | T1IF             | OC1IF            | IC1IF           | INTOIF |  |  |  |  |  |

| bit 7                         |                       |                                                                                                     |                   |                  |                  |                 | bi     |  |  |  |  |  |

|                               |                       |                                                                                                     |                   |                  |                  |                 |        |  |  |  |  |  |

| Legend:                       | - h:4                 |                                                                                                     | h.:4              |                  |                  |                 |        |  |  |  |  |  |

| R = Readable<br>-n = Value at |                       | W = Writable<br>'1' = Bit is se                                                                     |                   | 0 = Unimplem     | nented bit, read |                 |        |  |  |  |  |  |

| -n = value at                 | POR                   | I = DILIS SE                                                                                        | l                 |                  | areu             | x = Bit is unkn | own    |  |  |  |  |  |

| bit 15-14                     | Unimplemen            | ted: Read as                                                                                        | 'O'               |                  |                  |                 |        |  |  |  |  |  |

| bit 13                        | AD1IF: ADC1           | Conversion (                                                                                        | Complete Interi   | rupt Flag Status | s bit            |                 |        |  |  |  |  |  |

|                               |                       | AD1IF: ADC1 Conversion Complete Interrupt Flag Status bit<br>1 = Interrupt request has occurred     |                   |                  |                  |                 |        |  |  |  |  |  |

|                               | -                     | request has no                                                                                      |                   | <b>.</b>         |                  |                 |        |  |  |  |  |  |

| bit 12                        |                       | <b>U1TXIF:</b> UART1 Transmitter Interrupt Flag Status bit<br>1 = Interrupt request has occurred    |                   |                  |                  |                 |        |  |  |  |  |  |

|                               | •                     | request has oc<br>request has no                                                                    |                   |                  |                  |                 |        |  |  |  |  |  |

| bit 11                        | -                     | -                                                                                                   | nterrupt Flag S   | Status bit       |                  |                 |        |  |  |  |  |  |

|                               |                       | request has or                                                                                      |                   |                  |                  |                 |        |  |  |  |  |  |

|                               | •                     | request has no                                                                                      |                   |                  |                  |                 |        |  |  |  |  |  |

| bit 10                        |                       | -                                                                                                   | ot Flag Status k  | bit              |                  |                 |        |  |  |  |  |  |

|                               | •                     | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |                   |                  |                  |                 |        |  |  |  |  |  |

| bit 9                         | -                     | SPI1EIF: SPI1 Fault Interrupt Flag Status bit                                                       |                   |                  |                  |                 |        |  |  |  |  |  |

|                               |                       | request has or                                                                                      |                   |                  |                  |                 |        |  |  |  |  |  |

|                               | -                     | request has no                                                                                      |                   |                  |                  |                 |        |  |  |  |  |  |

| bit 8                         |                       | Interrupt Flag                                                                                      |                   |                  |                  |                 |        |  |  |  |  |  |

|                               |                       | request has or<br>request has no                                                                    |                   |                  |                  |                 |        |  |  |  |  |  |

| bit 7                         | •                     | •                                                                                                   |                   |                  |                  |                 |        |  |  |  |  |  |

|                               |                       | <b>T2IF:</b> Timer2 Interrupt Flag Status bit<br>1 = Interrupt request has occurred                 |                   |                  |                  |                 |        |  |  |  |  |  |

|                               | 0 = Interrupt i       | request has no                                                                                      | ot occurred       |                  |                  |                 |        |  |  |  |  |  |

| bit 6                         | -                     | OC2IF: Output Compare Channel 2 Interrupt Flag Status bit                                           |                   |                  |                  |                 |        |  |  |  |  |  |

|                               | •                     | request has oc<br>request has no                                                                    |                   |                  |                  |                 |        |  |  |  |  |  |

| bit 5                         | -                     | -                                                                                                   | nel 2 Interrupt F | -lag Status bit  |                  |                 |        |  |  |  |  |  |

|                               | -                     | request has or                                                                                      | -                 | <u>.</u>         |                  |                 |        |  |  |  |  |  |

|                               |                       | request has no                                                                                      |                   |                  |                  |                 |        |  |  |  |  |  |

| bit 4                         | -                     | ted: Read as                                                                                        |                   |                  |                  |                 |        |  |  |  |  |  |

| bit 3                         | T1IF: Timer1          | Interrupt Flag                                                                                      | Status bit        |                  |                  |                 |        |  |  |  |  |  |

|                               |                       | request has or                                                                                      |                   |                  |                  |                 |        |  |  |  |  |  |

#### -. חוור - - -• •

| U-0                                                                     | U-0 | U-0   | U-0 | U-0  | U-0 | U-0 | U-0   |

|-------------------------------------------------------------------------|-----|-------|-----|------|-----|-----|-------|

| —                                                                       | —   | —     | _   | —    | —   | —   | —     |

| bit 15                                                                  |     |       |     |      |     |     | bit 8 |

|                                                                         |     |       |     |      |     |     |       |

| U-0                                                                     | U-0 | R/W-0 | U-0 | U-0  | U-0 | U-0 | U-0   |

|                                                                         | —   | IC3IF |     | —    | —   |     | _     |

| bit 7                                                                   |     |       |     |      |     |     | bit 0 |

|                                                                         |     |       |     |      |     |     |       |

| Legend:                                                                 |     |       |     |      |     |     |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'    |     |       |     |      |     |     |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkn |     |       |     | nown |     |     |       |

#### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| bit 15-6 | Unimplemented: Read as '0'                               |

|----------|----------------------------------------------------------|

| bit 5    | IC3IF: Input Capture Channel 3 Interrupt Flag Status bit |

|          | <ol> <li>I = Interrupt request has occurred</li> </ol>   |

|          | 0 = Interrupt request has not occurred                   |

| bit 4-0  | Unimplemented: Read as '0'                               |

#### REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| R/W-0                  | R/W-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                 | U-0   |

|------------------------|-------|-----|-----|-----|-----|-----------------------|-------|

| FLTA1IF <sup>(1)</sup> | RTCIF | —   | —   | —   | _   | PWM1IF <sup>(1)</sup> | _     |

| bit 15                 |       |     |     |     |     |                       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   |     |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15    | FLTA1IF: PWM1 Fault A Interrupt Flag Status bit <sup>(1)</sup> |

|-----------|----------------------------------------------------------------|

|           | 1 = Interrupt request has occurred                             |

|           | 0 = Interrupt request has not occurred                         |

| bit 14    | RTCIF: RTCC Interrupt Flag Status bit                          |

|           | <ol> <li>I = Interrupt request has occurred</li> </ol>         |

|           | 0 = Interrupt request has not occurred                         |

| bit 13-10 | Unimplemented: Read as '0'                                     |

| bit 9     | PWM1IF: PWM1 Interrupt Flag Status bit <sup>(1)</sup>          |

|           | 1 = Interrupt request has occurred                             |

|           | 0 = Interrupt request has not occurred                         |

| bit 8-0   | Unimplemented: Read as '0'                                     |

|           |                                                                |

**Note 1:** These bits are available in dsPIC(16/32)MC10X devices only.

| U-0          | R/W-1                                         | R/W-0                                | R/W-0                 | U-0              | R/W-1             | R/W-0           | R/W-0    |  |  |  |  |  |  |

|--------------|-----------------------------------------------|--------------------------------------|-----------------------|------------------|-------------------|-----------------|----------|--|--|--|--|--|--|

| —            | CNIP2                                         | CNIP1                                | CNIP0                 | —                | CMIP2             | CMIP1           | CMIP0    |  |  |  |  |  |  |

| bit 15       |                                               |                                      |                       |                  |                   |                 | bit      |  |  |  |  |  |  |

|              | <b>D A A A</b>                                | <b>D</b> 444 o                       | <b>D M</b> ( <b>a</b> |                  | <b>D</b> 444 4    | <b>D</b> 444 o  |          |  |  |  |  |  |  |

| U-0          | R/W-1                                         | R/W-0                                | R/W-0                 | U-0              | R/W-1             | R/W-0           | R/W-0    |  |  |  |  |  |  |

|              | MI2C1IP2                                      | MI2C1IP1                             | MI2C1IP0              | —                | SI2C1IP2          | SI2C1IP1        | SI2C1IP0 |  |  |  |  |  |  |

| bit 7        |                                               |                                      |                       |                  |                   |                 | bit      |  |  |  |  |  |  |

| Legend:      |                                               |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

| R = Readab   | le bit                                        | W = Writable                         | bit                   | U = Unimple      | emented bit, read | d as '0'        |          |  |  |  |  |  |  |

| -n = Value a | t POR                                         | '1' = Bit is set                     |                       | '0' = Bit is cl  | eared             | x = Bit is unkr | nown     |  |  |  |  |  |  |

|              |                                               |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

| bit 15       | -                                             | ted: Read as '                       |                       |                  |                   |                 |          |  |  |  |  |  |  |

| bit 14-12    |                                               | Change Notifica                      |                       | -                |                   |                 |          |  |  |  |  |  |  |

|              | 111 = Interru                                 | pt is Priority 7 (                   | highest priorit       | y interrupt)     |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | 001 = Interru                                 | 001 = Interrupt is Priority 1        |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | 000 = Interru                                 | pt source is dis                     | abled                 |                  |                   |                 |          |  |  |  |  |  |  |

| bit 11       | Unimplemen                                    | ted: Read as '                       | 0'                    |                  |                   |                 |          |  |  |  |  |  |  |

| bit 10-8     | CMIP<2:0>: Comparator Interrupt Priority bits |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | 111 = Interru                                 | pt is Priority 7 (                   | highest priorit       | y interrupt)     |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •<br>001 = Interrupt is Priority 1            |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | 000 = Interrupt source is disabled            |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

| bit 7        |                                               | Ited: Read as '                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

| bit 6-4      | -                                             | >: I2C1 Master                       |                       | upt Priority bi  | ts                |                 |          |  |  |  |  |  |  |

|              |                                               | pt is Priority 7 (                   |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •                                             | . ,                                  |                       | , i ,            |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •<br>001 – Intorru                            | •<br>001 = Interrupt is Priority 1   |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              |                                               | pt is Fliolity 1<br>pt source is dis | abled                 |                  |                   |                 |          |  |  |  |  |  |  |

| bit 3        |                                               | ited: Read as '                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

| bit 2-0      | -                                             | >: I2C1 Slave E                      |                       | ot Priority bits |                   |                 |          |  |  |  |  |  |  |

|              |                                               | pt is Priority 7 (                   | -                     | -                |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •<br>•<br>001 = Interru                       | pt is Prioritv 1                     |                       |                  |                   |                 |          |  |  |  |  |  |  |

#### REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0          | U-0           | U-0                | U-0                         | U-0              | U-0                  | U-0                  | U-0                  |

|--------------|---------------|--------------------|-----------------------------|------------------|----------------------|----------------------|----------------------|

| _            | —             | _                  | —                           | —                | —                    | —                    | —                    |

| bit 15       | ·             |                    |                             | ·                |                      |                      | bit 8                |

|              |               |                    |                             |                  |                      |                      |                      |

| U-0          | R/W-1         | R/W-0              | R/W-0                       | U-0              | R/W-1                | R/W-0                | R/W-0                |

| _            | INT2IP2       | INT2IP1            | INT2IP0                     | —                | T5IP2 <sup>(1)</sup> | T5IP1 <sup>(1)</sup> | T5IP0 <sup>(1)</sup> |

| bit 7        |               |                    |                             |                  |                      |                      | bit 0                |

|              |               |                    |                             |                  |                      |                      |                      |

| Legend:      |               |                    |                             |                  |                      |                      |                      |

| R = Readab   | le bit        | W = Writable       | bit                         | U = Unimple      | mented bit, read     | 1 as '0'             |                      |

| -n = Value a | t POR         | '1' = Bit is set   |                             | '0' = Bit is cle | eared                | x = Bit is unknown   |                      |

|              |               |                    |                             |                  |                      |                      |                      |

| bit 15-7     | Unimplemen    | ted: Read as '     | 0'                          |                  |                      |                      |                      |

| bit 6-4      | INT2IP<2:0>:  | External Inter     | rupt 2 Priority             | bits             |                      |                      |                      |

|              | 111 = Interru | pt is Priority 7 ( | highest priorit             | ty interrupt)    |                      |                      |                      |

|              | •             |                    |                             |                  |                      |                      |                      |

|              | •             |                    |                             |                  |                      |                      |                      |

|              | 001 = Interru |                    |                             |                  |                      |                      |                      |

|              | 000 = Interru | pt source is dis   | abled                       |                  |                      |                      |                      |

| bit 3        | Unimplemen    | ted: Read as '     | 0'                          |                  |                      |                      |                      |

| bit 2-0      | T5IP<2:0>: ⊺  | ïmer5 Interrupt    | Priority bits <sup>(1</sup> | )                |                      |                      |                      |

|              | 111 = Interru | pt is Priority 7 ( | highest priorit             | ty interrupt)    |                      |                      |                      |

|              | •             |                    |                             |                  |                      |                      |                      |

|              | •             |                    |                             |                  |                      |                      |                      |

|              | 001 = Interru | pt is Priority 1   |                             |                  |                      |                      |                      |

|              | 000 = Interru | pt source is dis   | abled                       |                  |                      |                      |                      |

|              | h h :         |                    |                             |                  |                      |                      |                      |

#### REGISTER 7-22: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

**Note 1:** These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

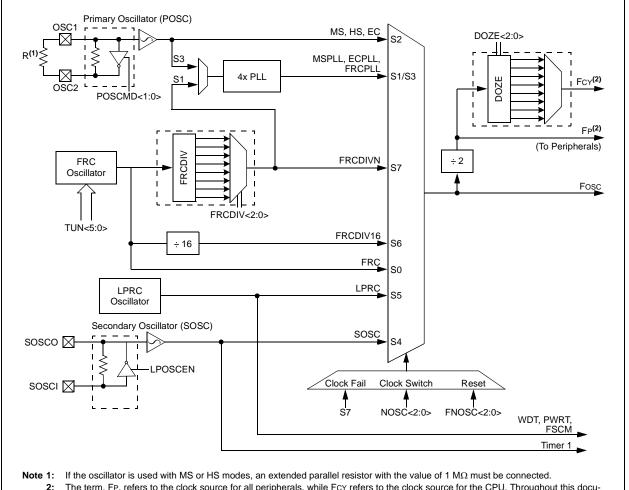

#### 8.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator (Part VI)" (DS70644) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The oscillator system for dsPIC33FJ16(GP/MC)101/ 102 and dsPIC33FJ32(GP/MC)101/102/104 devices provides:

- External and internal oscillator options as clock sources

- An on-chip, 4x Phase Lock Loop (PLL) to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection

- A simplified diagram of the oscillator system is shown in Figure 8-1.

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a Doze ratio of 1:2 or lower.

#### FIGURE 8-1: OSCILLATOR SYSTEM DIAGRAM

#### 9.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 9.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

#### 9.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

#### 9.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this may not be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the UART module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the UART module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 9.4 Peripheral Module Disable

The Peripheral Module Disable (PMDx) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMDx control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is enabled only if both the associated bit in the PMDx register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMDx register by default.

**Note:** If a PMDx bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMDx bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

| U-0                               | U-0        | U-0              | U-0                                | U-0                  | R/W-0 | R/W-0              | U-0   |

|-----------------------------------|------------|------------------|------------------------------------|----------------------|-------|--------------------|-------|

|                                   | —          | —                | _                                  | —                    | CMPMD | RTCCMD             | _     |

| bit 15                            |            |                  |                                    |                      |       |                    | bit 8 |

|                                   |            |                  |                                    |                      |       |                    |       |

| U-0                               | U-0        | U-0              | U-0                                | U-0                  | U-0   | U-0                | U-0   |

|                                   | —          | —                | _                                  | —                    | —     | —                  | —     |

| bit 7                             |            |                  |                                    |                      |       |                    | bit 0 |

|                                   |            |                  |                                    |                      |       |                    |       |

| Legend:                           |            |                  |                                    |                      |       |                    |       |

| R = Readable bit W = Writable bit |            | bit              | U = Unimplemented bit, read as '0' |                      |       |                    |       |

| -n = Value at POR '1              |            | '1' = Bit is set |                                    | '0' = Bit is cleared |       | x = Bit is unknown |       |

|                                   |            |                  |                                    |                      |       |                    |       |

| bit 15-11                         | Unimplemen | ted: Read as '0  | ,                                  |                      |       |                    |       |

#### REGISTER 9-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 10  | CMPMD: Comparator Module Disable bit |

|---------|--------------------------------------|

|         | 1 = Comparator module is disabled    |

|         | 0 = Comparator module is enabled     |

| bit 9   | RTCCMD: RTCC Module Disable bit      |

|         | 1 = RTCC module is disabled          |

|         | 0 = RTCC module is enabled           |

| bit 8-0 | Unimplemented: Read as '0'           |

#### REGISTER 9-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0               | U-0 | U-0              | U-0 | U-0                                | U-0    | U-0                | U-0   |

|-------------------|-----|------------------|-----|------------------------------------|--------|--------------------|-------|

| —                 | —   |                  | —   | —                                  | —      |                    | _     |

| bit 15            |     |                  |     |                                    |        |                    | bit 8 |

|                   |     |                  |     |                                    |        |                    |       |

| U-0               | U-0 | U-0              | U-0 | U-0                                | R/W-0  | U-0                | U-0   |

| —                 | —   | —                | —   | —                                  | CTMUMD | —                  | —     |

| bit 7             |     |                  |     |                                    |        |                    | bit C |

|                   |     |                  |     |                                    |        |                    |       |

| Legend:           |     |                  |     |                                    |        |                    |       |

| R = Readable bit  |     | W = Writable bit |     | U = Unimplemented bit, read as '0' |        |                    |       |

| -n = Value at POR |     | '1' = Bit is set |     | '0' = Bit is cleared               |        | x = Bit is unknown |       |

bit 15-3 Unimplemented: Read as '0'

bit 2 CTMUMD: CTMU Module Disable bit

1 = CTMU module is disabled

0 = CTMU module is enabled

bit 1-0 Unimplemented: Read as '0'

| R/W-1 R/W-1<br>CTSR1 U1CTSR0<br>bit 8<br>R/W-1 R/W-1<br>1RXR1 U1RXR0<br>bit 0 |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| bit 8<br>R/W-1 R/W-1<br>1RXR1 U1RXR0                                          |  |  |  |  |  |  |  |  |

| R/W-1 R/W-1<br>1RXR1 U1RXR0                                                   |  |  |  |  |  |  |  |  |

| 1RXR1 U1RXR0                                                                  |  |  |  |  |  |  |  |  |

| 1RXR1 U1RXR0                                                                  |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

| )'                                                                            |  |  |  |  |  |  |  |  |

| ,<br>Bit is unknown                                                           |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

| RPn Pin bits                                                                  |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

| 00001 = Input tied to RP1<br>00000 = Input tied to RP0                        |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

| hita                                                                          |  |  |  |  |  |  |  |  |

| n bits                                                                        |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

|                                                                               |  |  |  |  |  |  |  |  |

#### REGISTER 10-8: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

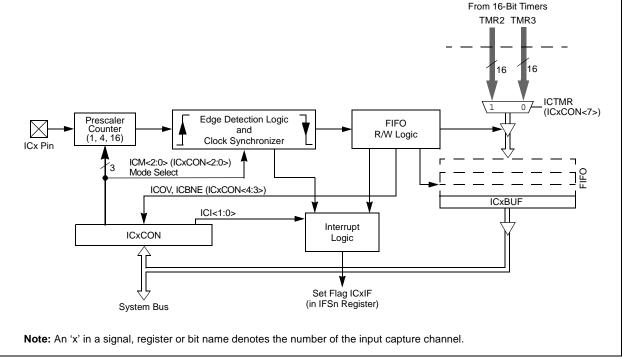

#### 13.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70198) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices support up to three input capture channels. The input capture module captures the 16-bit value of the selected Time Base register when an event occurs on the ICx pin. The events that cause a capture event are listed below in three categories:

- 1. Simple Capture Event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- 2. Capture timer value on every edge (rising and falling).

- 3. Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values:

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Use of input capture to provide additional sources of external interrupts

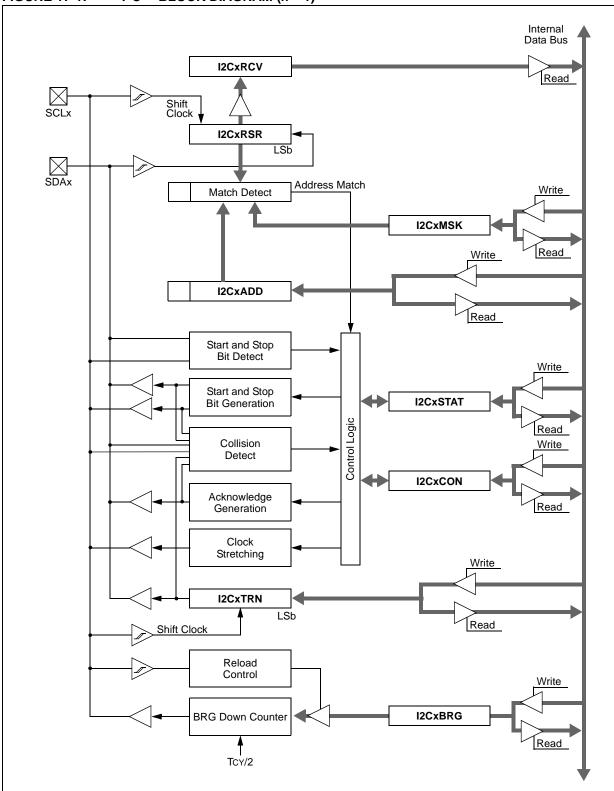

FIGURE 17-1:  $I^2C^{TM}$  BLOCK DIAGRAM (x = 1)

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (Bit 8 of received data = $1$ )<br>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect    |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 0 = Address Detect mode is disabled                                                                                                                                           |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                          |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                         |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                     |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>   |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                    |

|       | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul> |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read-only/clear only)                                                                                                          |

|       | 1 = Receive buffer has overflowed                                                                                                                                             |