Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

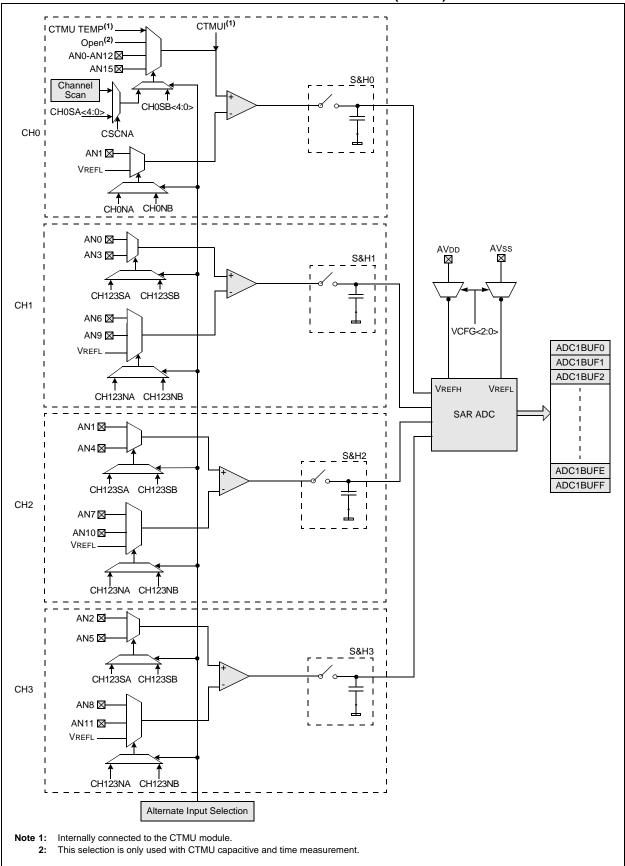

| Data Converters            | A/D 14x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp104t-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

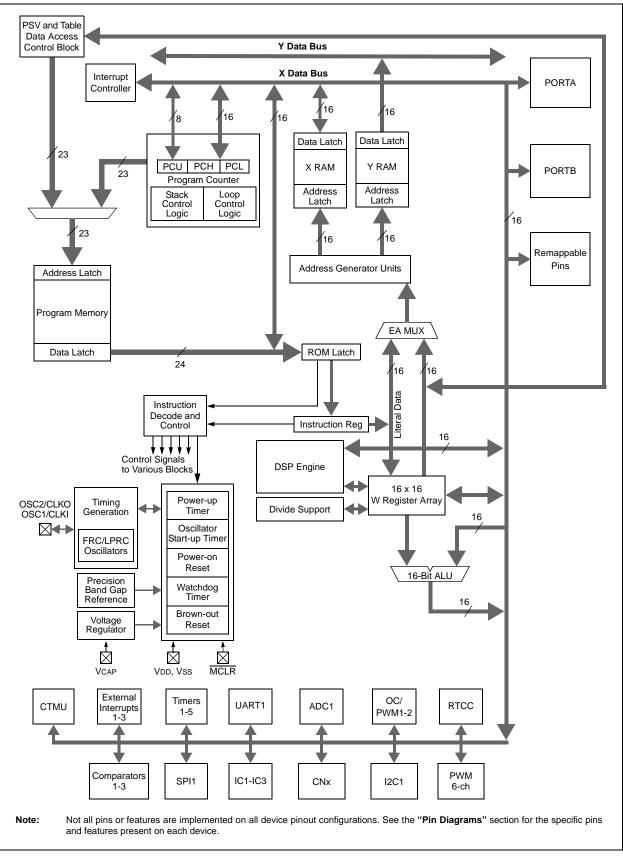

## FIGURE 1-1: dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 BLOCK DIAGRAM

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz < FIN < 8 MHz (for MSPLL mode) or 3 MHz < FIN < 8 MHz (for ECPLL mode) to comply with device PLL start-up conditions. HSPLL mode is not supported. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The fixed PLL settings of 4x after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can enable the PLL and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

#### 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator is selected as a debugger, it automatically initializes all of the Analog-to-Digital input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in the register that correspond to the Analog-to-Digital pins that are initialized by MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain Analog-to-Digital pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all Analog-to-Digital pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

#### 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternately, connect a 1k to 10k resistor between Vss and unused pins.

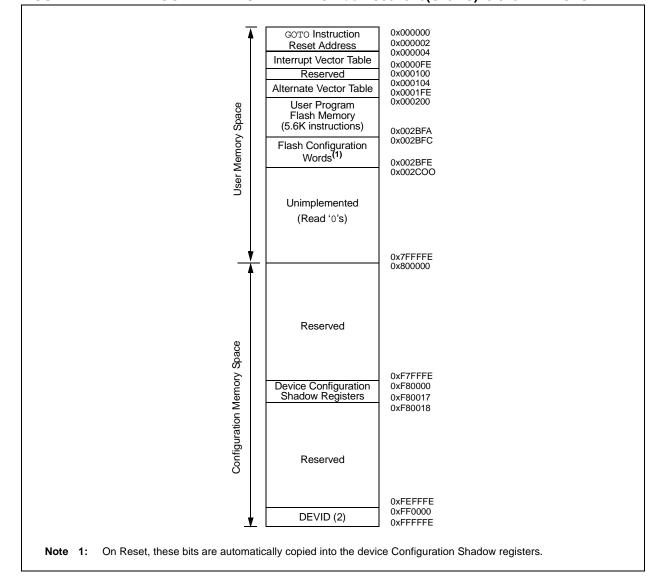

#### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Data Memory" (DS70202) and "Program Memory" (DS70203) in the "dsPIC33/PIC24 Family Reference Manual", which are available from the Microchip web site (www.microchip.com).

The device architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The memory maps for the dsPIC33FJ16(GP/MC)101/ 102 and dsPIC33FJ32(GP/MC)101/102/104 family of devices are shown in Figure 4-1 and Figure 4-2.

#### FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33FJ16(GP/MC)101/102 DEVICES

#### TABLE 4-23: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJXXGP101 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| RPOR0        | 06C0        |        | _      |        |        |        | RP1R<4:0> | •     |       | —     |       |       |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR2        | 06C4        | _      | _      | _      | _      | —      | —         | _     | _     | _     | _     | _     |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3        | 06C6        | _      | _      | _      |        |        | RP7R<4:0> | •     |       | —     | _     | _     | _     | _     | _          | _     | _     | 0000          |

| RPOR4        | 06C8        | _      | _      |        |        |        | RP9R<4:0> | >     |       | —     |       |       |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR7        | 06CE        | _      | _      |        |        |        | RP15R<4:0 | >     |       | —     |       |       |       | F     | RP14R<4:0> | >     |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJXXMC101 DEVICES

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|------------|-----------|-------|-------|-------|-------|-------|-------|------------|------------|-------|-------|---------------|

| RPOR0        | 06C0        | _      | _      | _      |        |            | RP1R<4:0> | •     |       | _     | _     | _     |       |            | RP0R<4:0>  |       |       | 0000          |

| RPOR2        | 06C4        | _      | _      | _      | —      | _          | _         | _     | _     | _     | _     | _     |       |            | RP4R<4:0>  |       |       | 0000          |

| RPOR3        | 06C6        | _      | _      | _      |        |            | RP7R<4:0> | •     |       | _     | _     | _     | _     | _          | _          | _     | _     | 0000          |

| RPOR4        | 06C8        | _      | _      | _      |        |            | RP9R<4:0> | •     |       | _     | _     | _     |       |            | RP8R<4:0>  |       |       | 0000          |

| RPOR6        | 06CC        | _      | _      | _      |        |            | RP13R<4:0 | >     |       | _     | _     | _     |       | F          | RP12R<4:0> |       |       | 0000          |

| RPOR7        | 06CE        |        | _      | -      |        | RP15R<4:0> |           |       | _     | _     | _     |       | F     | RP14R<4:0> |            |       | 0000  |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-25: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJXX(GP/MC)102 DEVICES

|              |             |        |        |        |        |           |           |       |       |       |       | •····•, |       |       |            |       |       |               |

|--------------|-------------|--------|--------|--------|--------|-----------|-----------|-------|-------|-------|-------|---------|-------|-------|------------|-------|-------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11    | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

| RPOR0        | 06C0        | -      | —      | —      |        |           | RP1R<4:0> | >     |       | -     | —     | —       |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR1        | 06C2        | _      | _      | _      |        |           | RP3R<4:0> | >     |       | _     | _     | —       |       |       | RP2R<4:0>  |       |       | 0000          |

| RPOR2        | 06C4        | _      | _      | _      |        | RP5R<4:0> |           |       |       | _     | _     | —       |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3        | 06C6        | _      | _      | _      |        |           | RP7R<4:0> | >     |       | _     | _     | —       |       |       | RP6R<4:0>  |       |       | 0000          |

| RPOR4        | 06C8        | _      | _      | _      |        |           | RP9R<4:0> | >     |       | _     | _     | —       |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR5        | 06CA        | _      | _      | _      |        |           | RP11R<4:0 | >     |       | _     | _     | —       |       | I     | RP10R<4:0> |       |       | 0000          |

| RPOR6        | 06CC        | _      | _      | _      |        |           | RP13R<4:0 | >     |       | _     | _     | —       |       | I     | RP12R<4:0> |       |       | 0000          |

| RPOR7        | 06CE        | _      | —      | _      |        |           | RP15R<4:0 | >     |       | _     | —     | —       |       |       | RP14R<4:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2014 Microchip Technology Inc.

#### FIGURE 7-1: dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 INTERRUPT VECTOR TABLE

| 1                                 |                                            | 7                    |                                                        |

|-----------------------------------|--------------------------------------------|----------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction                   | 0x000000             |                                                        |

|                                   | Reset – GOTO Address                       | 0x000002             |                                                        |

|                                   | Reserved                                   | 0x000004             |                                                        |

|                                   | Oscillator Fail Trap Vector                | _                    |                                                        |

|                                   | Address Error Trap Vector                  | _                    |                                                        |

|                                   | Stack Error Trap Vector                    | _                    |                                                        |

|                                   | Math Error Trap Vector                     | _                    |                                                        |

|                                   | Reserved                                   | -                    |                                                        |

|                                   | Reserved                                   | _                    |                                                        |

|                                   | Reserved<br>Interrupt Vector 0             | 0x000014             |                                                        |

|                                   | Interrupt Vector 1                         | 0,000014             |                                                        |

|                                   |                                            | -                    |                                                        |

|                                   | ~                                          |                      |                                                        |

|                                   | ~                                          | _                    |                                                        |

|                                   | Interrupt Vector 52                        | 0x00007C             | (4)                                                    |

|                                   | Interrupt Vector 53                        | 0x00007E             | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ity                               | Interrupt Vector 54                        | 0x000080             |                                                        |

| iori                              | ~                                          |                      |                                                        |

| ā                                 | ~                                          |                      |                                                        |

| der                               | ~                                          |                      |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 116                       | 0x0000FC             |                                                        |

| ra                                | Interrupt Vector 117                       | 0x0000FE             |                                                        |

| atu                               | Reserved                                   | 0x000100             |                                                        |

| Z                                 | Reserved                                   | 0x000102             |                                                        |

| sing                              | Reserved                                   |                      |                                                        |

| eas                               | Oscillator Fail Trap Vector                |                      |                                                        |

| ecr                               | Address Error Trap Vector                  |                      |                                                        |

| ă                                 | Stack Error Trap Vector                    |                      |                                                        |

|                                   | Math Error Trap Vector                     |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Interrupt Vector 0                         | 0x000114             |                                                        |

|                                   | Interrupt Vector 1                         | _                    |                                                        |

|                                   | ~                                          | 4                    |                                                        |

|                                   | ~                                          | 4                    |                                                        |

|                                   | ~<br>Interrupt Vector 52                   | 0x000470             | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   |                                            | 0x00017C             |                                                        |

|                                   | Interrupt Vector 53<br>Interrupt Vector 54 | 0x00017E<br>0x000180 |                                                        |

|                                   | ~                                          | 0000180              |                                                        |

|                                   | ~                                          | -                    |                                                        |

|                                   | ~ ~                                        |                      |                                                        |

|                                   | -<br>Interrupt Vector 116                  | -                    |                                                        |

|                                   | Interrupt Vector 117                       | 0x0001FE             |                                                        |

| *                                 | Start of Code                              | 0x000200             | L                                                      |

|                                   |                                            |                      |                                                        |

| Note 1: See                       | e Table 7-1 for the list of impleme        | ented interrupt v    | ectors.                                                |

| D / M A       | D 444 A                                                                                                                                      | D.4.4. 0                                                                                                                                               | DAMA            | DALLA             | DALLA           | DAMA            | D 44/ 6 |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|---------|--|--|--|--|--|

| R/W-0         | R/W-0                                                                                                                                        | R/W-0                                                                                                                                                  | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |  |

| NSTDIS        | OVAERR                                                                                                                                       | OVBERR                                                                                                                                                 | COVAERR         | COVBERR           | OVATE           | OVBTE           | COVTE   |  |  |  |  |  |

| bit 15        |                                                                                                                                              |                                                                                                                                                        |                 |                   |                 |                 | bi      |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                        | U-0                                                                                                                                                    | R/W-0           | R/W-0             | R/W-0           | R/W-0           | U-0     |  |  |  |  |  |

| SFTACERR      |                                                                                                                                              | <u> </u>                                                                                                                                               | MATHERR         | ADDRERR           | STKERR          | OSCFAIL         |         |  |  |  |  |  |

| bit 7         | BIVOLINI                                                                                                                                     |                                                                                                                                                        |                 | ABBRERR           | OTTLETT         | 00017112        | bi      |  |  |  |  |  |

|               |                                                                                                                                              |                                                                                                                                                        |                 |                   |                 |                 |         |  |  |  |  |  |

| Legend:       |                                                                                                                                              |                                                                                                                                                        |                 |                   |                 |                 |         |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                                                        | W = Writable                                                                                                                                           | bit             | U = Unimplem      | ented bit, read | 1 as '0'        |         |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                          | '1' = Bit is set                                                                                                                                       |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |  |  |  |  |  |

| 6:4 <i>7</i>  |                                                                                                                                              | www.unt.Nie.otie.ev.F                                                                                                                                  | Niaahla hit     |                   |                 |                 |         |  |  |  |  |  |

| bit 15        |                                                                                                                                              | rrupt Nesting E<br>nesting is disat                                                                                                                    |                 |                   |                 |                 |         |  |  |  |  |  |

|               |                                                                                                                                              | nesting is cloat                                                                                                                                       |                 |                   |                 |                 |         |  |  |  |  |  |

| bit 14        | -                                                                                                                                            | cumulator A O                                                                                                                                          |                 | lag bit           |                 |                 |         |  |  |  |  |  |

|               | 1 = Trap was                                                                                                                                 | caused by ove                                                                                                                                          | erflow of Accur | nulator A         |                 |                 |         |  |  |  |  |  |

|               | 0 = Trap was                                                                                                                                 | not caused by                                                                                                                                          | overflow of Ad  | ccumulator A      |                 |                 |         |  |  |  |  |  |

| bit 13        |                                                                                                                                              | cumulator B O                                                                                                                                          | -               | -                 |                 |                 |         |  |  |  |  |  |

|               |                                                                                                                                              | caused by ove                                                                                                                                          |                 |                   |                 |                 |         |  |  |  |  |  |

| bit 12        | <ul> <li>0 = Trap was not caused by overflow of Accumulator B</li> <li>COVAERR: Accumulator A Catastrophic Overflow Trap Flag bit</li> </ul> |                                                                                                                                                        |                 |                   |                 |                 |         |  |  |  |  |  |

|               |                                                                                                                                              | 1 = Trap was caused by catastrophic overflow of Accumulator A                                                                                          |                 |                   |                 |                 |         |  |  |  |  |  |

|               | •                                                                                                                                            | •                                                                                                                                                      | •               | overflow of Accu  |                 |                 |         |  |  |  |  |  |

| bit 11        | COVBERR: A                                                                                                                                   | Accumulator B                                                                                                                                          | Catastrophic C  | Overflow Trap F   | lag bit         |                 |         |  |  |  |  |  |

|               |                                                                                                                                              |                                                                                                                                                        |                 | flow of Accumu    |                 |                 |         |  |  |  |  |  |

|               | -                                                                                                                                            | -                                                                                                                                                      | -               | overflow of Accu  | umulator B      |                 |         |  |  |  |  |  |

| bit 10        |                                                                                                                                              | OVATE: Accumulator A Overflow Trap Enable bit                                                                                                          |                 |                   |                 |                 |         |  |  |  |  |  |

|               | 1 = Trap overflow of Accumulator A<br>0 = Trap is disabled                                                                                   |                                                                                                                                                        |                 |                   |                 |                 |         |  |  |  |  |  |

| bit 9         |                                                                                                                                              | umulator B Ove                                                                                                                                         | erflow Trap En  | able bit          |                 |                 |         |  |  |  |  |  |

|               |                                                                                                                                              | flow of Accum                                                                                                                                          |                 |                   |                 |                 |         |  |  |  |  |  |

|               | 0 = Trap is di                                                                                                                               | sabled                                                                                                                                                 |                 |                   |                 |                 |         |  |  |  |  |  |

| bit 8         | COVTE: Cata                                                                                                                                  | astrophic Overf                                                                                                                                        | low Trap Enab   | ole bit           |                 |                 |         |  |  |  |  |  |

|               |                                                                                                                                              |                                                                                                                                                        | erflow of Accur | mulator A or B i  | s enabled       |                 |         |  |  |  |  |  |

| hit 7         | 0 = Trap is dis                                                                                                                              |                                                                                                                                                        | tor Error State | ia hit            |                 |                 |         |  |  |  |  |  |

| bit 7         |                                                                                                                                              | SFTACERR: Shift Accumulator Error Status bit                                                                                                           |                 |                   |                 |                 |         |  |  |  |  |  |

|               |                                                                                                                                              | <ol> <li>Math error trap was caused by an invalid accumulator shift</li> <li>Math error trap was not caused by an invalid accumulator shift</li> </ol> |                 |                   |                 |                 |         |  |  |  |  |  |

| bit 6         |                                                                                                                                              | ithmetic Error :                                                                                                                                       | -               |                   |                 |                 |         |  |  |  |  |  |

|               |                                                                                                                                              | or trap was cau                                                                                                                                        | -               | -                 |                 |                 |         |  |  |  |  |  |

|               |                                                                                                                                              | r trap was not                                                                                                                                         | -               | ivide-by-zero     |                 |                 |         |  |  |  |  |  |

| bit 5         | •                                                                                                                                            | ted: Read as '                                                                                                                                         |                 |                   |                 |                 |         |  |  |  |  |  |

| bit 4         | <b>MATHERR:</b> Arithmetic Error Status bit<br>1 = Math error trap has occurred                                                              |                                                                                                                                                        |                 |                   |                 |                 |         |  |  |  |  |  |

|               | 1 14-41                                                                                                                                      |                                                                                                                                                        | una al          |                   |                 |                 |         |  |  |  |  |  |

#### INTOONA, INTERDURT CONTROL DECISTER A

| REGISTER      | 7-10: IEC0:   | INTERRUPT                        | ENABLE C         | ONTROL RE        | GISTER 0        |                 |        |

|---------------|---------------|----------------------------------|------------------|------------------|-----------------|-----------------|--------|

| U-0           | U-0           | R/W-0                            | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

| _             | —             | AD1IE                            | U1TXIE           | U1RXIE           | SPI1IE          | SPI1EIE         | T3IE   |

| bit 15        |               |                                  |                  |                  |                 |                 | bit    |

| R/W-0         | R/W-0         | R/W-0                            | U-0              | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

| T2IE          | OC2IE         | IC2IE                            |                  | T1IE             | OC1IE           | IC1IE           | INT0IE |

| bit 7         |               |                                  |                  |                  |                 |                 | bit    |

| Legend:       |               |                                  |                  |                  |                 |                 |        |

| R = Readabl   | e bit         | W = Writable                     | e bit            | U = Unimple      | mented bit, rea | d as '0'        |        |

| -n = Value at | POR           | '1' = Bit is se                  | t                | '0' = Bit is cle |                 | x = Bit is unkn | nown   |

|               |               |                                  | ( - <b>1</b>     |                  |                 |                 |        |

| bit 15-14     | -             | nted: Read as                    |                  |                  |                 |                 |        |

| bit 13        |               |                                  | •                | rupt Enable bit  | t               |                 |        |

|               |               | request is ena<br>request is not |                  |                  |                 |                 |        |

| bit 12        | •             | •                                | er Interrupt Ena | able hit         |                 |                 |        |

|               |               | request is ena                   |                  |                  |                 |                 |        |

|               |               | request is not                   |                  |                  |                 |                 |        |

| bit 11        | U1RXIE: UA    | RT1 Receiver                     | Interrupt Enab   | le bit           |                 |                 |        |

|               |               | request is ena                   |                  |                  |                 |                 |        |

|               | •             | request is not                   |                  |                  |                 |                 |        |

| bit 10        |               | Event Interru                    |                  |                  |                 |                 |        |

|               | •             | request is ena<br>request is not |                  |                  |                 |                 |        |

| bit 9         | -             | 11 Error Interru                 |                  |                  |                 |                 |        |

| DIL 9         |               | request is ena                   | -                |                  |                 |                 |        |

|               |               | request is not                   |                  |                  |                 |                 |        |

| bit 8         |               | Interrupt Enal                   |                  |                  |                 |                 |        |

|               |               | request is ena                   |                  |                  |                 |                 |        |

|               | •             | request is not                   |                  |                  |                 |                 |        |

| bit 7         |               | Interrupt Enal                   |                  |                  |                 |                 |        |

|               |               | request is ena                   |                  |                  |                 |                 |        |

| h:4 C         | -             | request is not                   |                  | unt Enchla hit   |                 |                 |        |

| bit 6         |               | request is ena                   |                  | upt Enable bit   |                 |                 |        |

|               |               | request is ena                   |                  |                  |                 |                 |        |

| bit 5         | •             | •                                | nel 2 Interrupt  | Enable bit       |                 |                 |        |

|               | •             | request is ena                   |                  |                  |                 |                 |        |

|               | 0 = Interrupt | request is not                   | enabled          |                  |                 |                 |        |

| bit 4         | Unimplemer    | nted: Read as                    | '0'              |                  |                 |                 |        |

| bit 3         |               | Interrupt Enal                   |                  |                  |                 |                 |        |

|               |               | request is ena                   |                  |                  |                 |                 |        |

| 1.11.0        | -             | request is not                   |                  |                  |                 |                 |        |

| bit 2         | -             | -                                |                  | upt Enable bit   |                 |                 |        |

|               |               | request is ena<br>request is not |                  |                  |                 |                 |        |

| bit 1         | -             | -                                | nel 1 Interrupt  | Enable bit       |                 |                 |        |

| ~             |               | request is ena                   | -                |                  |                 |                 |        |

|               |               | request is not                   |                  |                  |                 |                 |        |

| bit 0         | -             | rnal Interrupt (                 |                  |                  |                 |                 |        |

|               |               | request is ena                   |                  |                  |                 |                 |        |

|               | 0 = Interrupt | request is not                   | enabled          |                  |                 |                 |        |

|               |               |                                  |                  |                  |                 |                 |        |

### REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

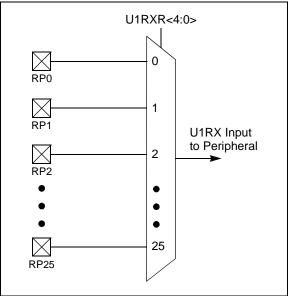

#### 10.4 Peripheral Pin Select (PPS)

Peripheral Pin Select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral Pin Select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

#### 10.4.1 AVAILABLE PINS

The Peripheral Pin Select feature is used with a range of up to 16 pins. The number of available pins depends on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

#### 10.4.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of Special Function Registers: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 10.4.2.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-10). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

Figure 10-2 Illustrates remappable pin selection for U1RX input.

Note: For input mapping only, the Peripheral Pin Select (PPS) functionality does not have priority over the TRISx settings. Therefore, when configuring the RPx pin for input, the corresponding bit in the TRISx register must also be configured for input (i.e., set to '1').

#### FIGURE 10-2: REMAPPABLE MUX INPUT FOR U1RX

| REGISTER              | 10-8: RPINF               | (18: PERIPH                                         | ERAL PIN S   | ELECT INPU       | T REGISTER       | 18              |         |  |  |  |  |  |

|-----------------------|---------------------------|-----------------------------------------------------|--------------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| U-0                   | U-0                       | U-0                                                 | R/W-1        | R/W-1            | R/W-1            | R/W-1           | R/W-1   |  |  |  |  |  |

|                       |                           |                                                     | U1CTSR4      | U1CTSR3          | U1CTSR2          | U1CTSR1         | U1CTSR0 |  |  |  |  |  |

| bit 15                |                           |                                                     |              |                  |                  |                 | bit 8   |  |  |  |  |  |

| U-0                   | U-0                       | U-0                                                 | R/W-1        | R/W-1            | R/W-1            | R/W-1           | R/W-1   |  |  |  |  |  |

| _                     | _                         | _                                                   | U1RXR4       | U1RXR3           | U1RXR2           | U1RXR1          | U1RXR0  |  |  |  |  |  |

| bit 7                 |                           |                                                     |              |                  |                  |                 | bit (   |  |  |  |  |  |

| <del></del>           |                           |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

| Legend:<br>R = Readab | le hit                    | W = Writable                                        | bit          | U = Unimpler     | mented bit, reac | las '0'         |         |  |  |  |  |  |

| -n = Value a          |                           | '1' = Bit is set                                    |              | '0' = Bit is cle |                  | x = Bit is unkr | าดพท    |  |  |  |  |  |

|                       |                           |                                                     |              |                  |                  |                 | -       |  |  |  |  |  |

| bit 15-13<br>bit 12-8 | -                         | i <b>ted:</b> Read as '<br><b>)&gt;:</b> Assign UAF |              | end (U1CTS) t    | to the Correspo  | ndina RPn Pin   | bits    |  |  |  |  |  |

|                       | 11111 = Inpu              | -                                                   |              | (2 . 2 . 2)      |                  |                 |         |  |  |  |  |  |

|                       | 11110 = Res               |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       |                           |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       | -                         |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       | 11010 = Res               | 11010 = Reserved                                    |              |                  |                  |                 |         |  |  |  |  |  |

|                       | 11001 = Inpu              | ut tied to RP25                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       | •                         |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       |                           |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       | 00001 = Input tied to RP1 |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       | 00000 = Inpu              | ut tied to RP0                                      |              |                  |                  |                 |         |  |  |  |  |  |

| bit 7-5               | Unimplemen                | ted: Read as '                                      | 0'           |                  |                  |                 |         |  |  |  |  |  |

| bit 4-0               |                           | -                                                   | 1 Receive (U | 1RX) to the Co   | rresponding RF   | Pn Pin bits     |         |  |  |  |  |  |

|                       | 11111 = Inpu              |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       | 11110 <b>= Res</b>        | served                                              |              |                  |                  |                 |         |  |  |  |  |  |

|                       |                           |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       |                           |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       | 11010 = Res               |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       | 11001 = inpu              | ut tied to RP25                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       |                           |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       | •                         |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       | 00001 = Inpu              |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       | 00000 = Inpu              |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

|                       |                           |                                                     |              |                  |                  |                 |         |  |  |  |  |  |

#### REGISTER 10-8: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| U-0          | U-0                                                                                                                                                                   | U-0                                                                                                                                                            | U-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| —            | —                                                                                                                                                                     | —                                                                                                                                                              |               |                  | SEVO            | PS<3:0>         |       |  |  |  |  |  |

| bit 15       |                                                                                                                                                                       |                                                                                                                                                                |               |                  |                 |                 | bit 8 |  |  |  |  |  |

|              |                                                                                                                                                                       |                                                                                                                                                                |               |                  |                 |                 |       |  |  |  |  |  |

| U-0          | U-0                                                                                                                                                                   | U-0                                                                                                                                                            | U-0           | U-0              | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

| _            | —                                                                                                                                                                     | —                                                                                                                                                              | _             | —                | IUE             | OSYNC           | UDIS  |  |  |  |  |  |

| bit 7        | ·                                                                                                                                                                     |                                                                                                                                                                |               |                  |                 |                 | bit 0 |  |  |  |  |  |

|              |                                                                                                                                                                       |                                                                                                                                                                |               |                  |                 |                 |       |  |  |  |  |  |

| Legend:      |                                                                                                                                                                       |                                                                                                                                                                |               |                  |                 |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                                                                | W = Writable I                                                                                                                                                 | oit           | U = Unimplen     | nented bit, rea | d as '0'        |       |  |  |  |  |  |

| -n = Value a | n = Value at POR '1' = Bit is set                                                                                                                                     |                                                                                                                                                                |               |                  | ared            | x = Bit is unkn | own   |  |  |  |  |  |

|              |                                                                                                                                                                       |                                                                                                                                                                |               |                  |                 |                 |       |  |  |  |  |  |

| bit 15-12    | Unimplemen                                                                                                                                                            | ted: Read as '                                                                                                                                                 | )'            |                  |                 |                 |       |  |  |  |  |  |

| bit 11-8     | SEVOPS<3:0                                                                                                                                                            | <b>0&gt;:</b> PWMx Spec                                                                                                                                        | ial Event Tri | gger Output Pos  | stscale Select  | oits            |       |  |  |  |  |  |

|              | 1111 = 1:16                                                                                                                                                           | postscale                                                                                                                                                      |               |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                                                     |                                                                                                                                                                |               |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                                                     |                                                                                                                                                                |               |                  |                 |                 |       |  |  |  |  |  |

|              | •<br>0001 = 1:2 p                                                                                                                                                     | netecale                                                                                                                                                       |               |                  |                 |                 |       |  |  |  |  |  |

|              | 0000 = 1.2 p                                                                                                                                                          |                                                                                                                                                                |               |                  |                 |                 |       |  |  |  |  |  |

| bit 7-3      | •                                                                                                                                                                     | ted: Read as 'd                                                                                                                                                | )'            |                  |                 |                 |       |  |  |  |  |  |

| bit 2        | IUE: Immedia                                                                                                                                                          | ate Update Enal                                                                                                                                                | ole bit       |                  |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                                                                       | to the active Px                                                                                                                                               |               | are immediate    |                 |                 |       |  |  |  |  |  |

|              | 0 = Updates                                                                                                                                                           | to the active Px                                                                                                                                               | DC registers  | are synchroniz   | ed to the PWN   | lx time base    |       |  |  |  |  |  |

| bit 1        | OSYNC: Output Override Synchronization bit                                                                                                                            |                                                                                                                                                                |               |                  |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                                                                       | Output overrides via the PxOVDCON register are synchronized to the PWMx time base<br>Output overrides via the PxOVDCON register occur on the next Tcy boundary |               |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                                                     |                                                                                                                                                                |               | register occur o | on the next TCN | / boundary      |       |  |  |  |  |  |

| bit 0        | UDIS: PWMx Update Disable bit                                                                                                                                         |                                                                                                                                                                |               |                  |                 |                 |       |  |  |  |  |  |

|              | <ul> <li>1 = Updates from Duty Cycle and Period Buffer registers are disabled</li> <li>0 = Updates from Duty Cycle and Period Buffer registers are enabled</li> </ul> |                                                                                                                                                                |               |                  |                 |                 |       |  |  |  |  |  |

|              | 0 – Opuales                                                                                                                                                           |                                                                                                                                                                |               | Duilei registers |                 |                 |       |  |  |  |  |  |

#### REGISTER 15-6: PWMxCON2: PWMx CONTROL REGISTER 2

#### 16.3 SPI Control Registers

#### REGISTER 16-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0  | U-0    | R/W-0   | U-0 | U-0 | U-0 | U-0    | U-0    |

|--------|--------|---------|-----|-----|-----|--------|--------|

| SPIEN  | —      | SPISIDL | —   | —   | —   | —      | —      |

| bit 15 |        |         |     |     |     |        | bit 8  |

|        |        |         |     |     |     |        |        |

| U-0    | R/C-0  | U-0     | U-0 | U-0 | U-0 | R-0    | R-0    |

| _      | SPIROV | _       | —   | _   | —   | SPITBF | SPIRBF |

| bit 7  |        |         |     |     |     |        | bit 0  |

| bit 7  |        |         |     |     |     |        |        |

| Legend:           | C = Clearable bit |                            |                    |

|-------------------|-------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15   | SPIEN: SPIx Enable bit                                                                                                                                                                                                                                                                                                    |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Enables module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables module                                                                                                                                                                                                           |

| bit 14   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                |

| bit 13   | SPISIDL: SPIx Stop in Idle Mode bit                                                                                                                                                                                                                                                                                       |

|          | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                                                                                                                   |

| bit 12-7 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                |

| bit 6    | SPIROV: SPIx Receive Overflow Flag bit                                                                                                                                                                                                                                                                                    |

|          | <ul> <li>1 = A new byte/word is completely received and discarded; the user software has not read the previous data in the SPIxBUF register</li> <li>0 = No overflow has occurred.</li> </ul>                                                                                                                             |

| bit 5-2  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                |

| bit 1    | SPITBF: SPIx Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                              |

|          | <ul> <li>1 = Transmit has not yet started, SPIxTXB is full</li> <li>0 = Transmit has started, SPIxTXB is empty</li> <li>Automatically set in hardware when the CPU writes the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.</li> </ul> |

| bit 0    | SPIRBF: SPIx Receive Buffer Full Status bit                                                                                                                                                                                                                                                                               |

|          | <ul> <li>1 = Receive complete, SPIxRXB is full</li> <li>0 = Receive is not complete, SPIxRXB is empty</li> <li>Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.</li> </ul>                     |

| R/W-0                                           | R/W-0                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                 | U-0                                                                                                                                                                         | U-0                | U-0                  | U-0                   | U-0                |  |  |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|-----------------------|--------------------|--|--|

| FRMEN                                           | SPIFSD                                                                                                                                                                   | FRMPOL                                                                                                                                                                                                                |                                                                                                                                                                             | —                  |                      | —                     | _                  |  |  |

| bit 15                                          |                                                                                                                                                                          |                                                                                                                                                                                                                       |                                                                                                                                                                             |                    |                      |                       | bit 8              |  |  |