Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betuils                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 14x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

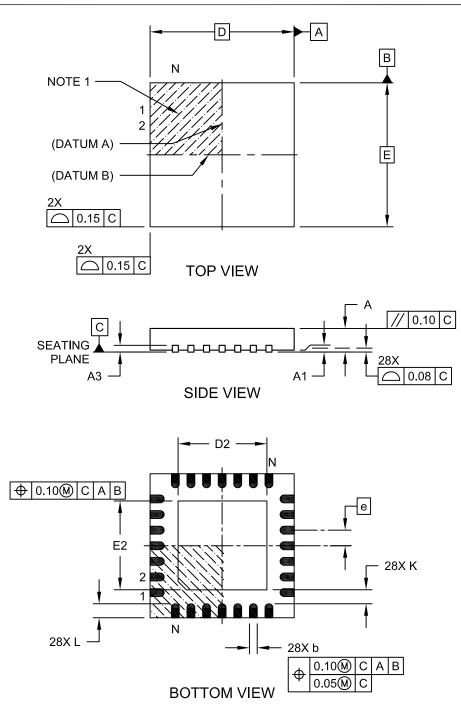

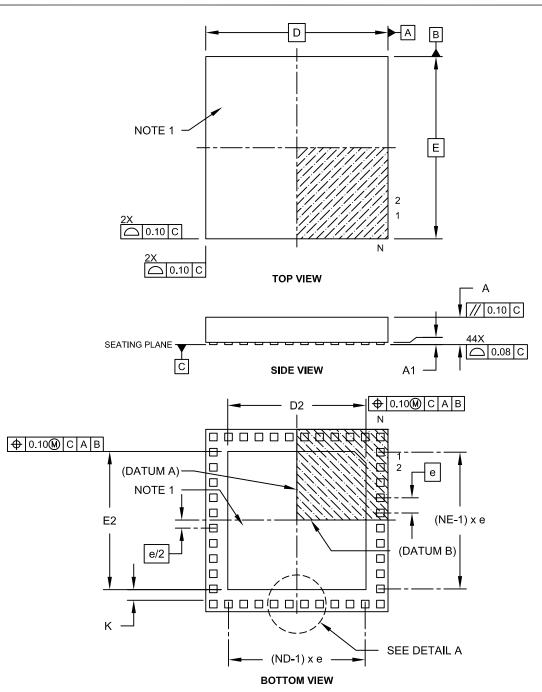

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp104t-i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

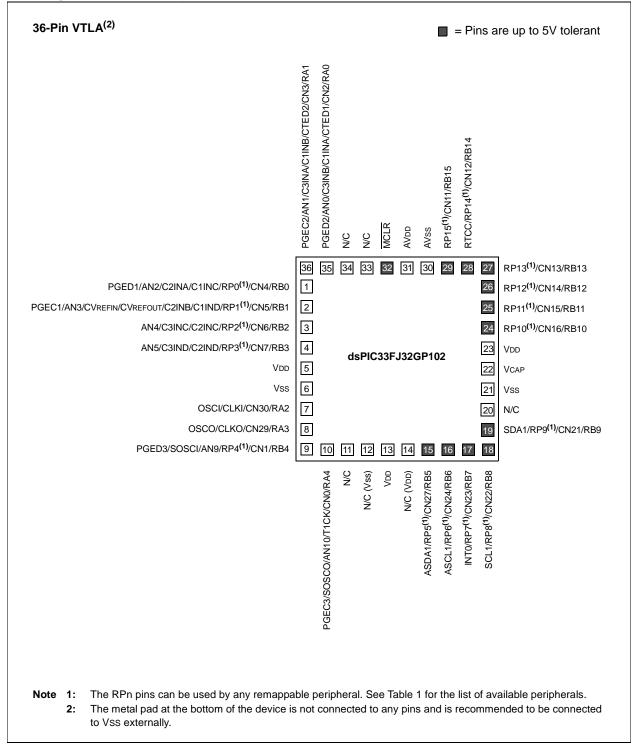

#### Pin Diagrams (Continued)

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz < Fin < 8 MHz (for MSPLL mode) or 3 MHz < Fin < 8 MHz (for ECPLL mode) to comply with device

| TABLE 4-  | 16:         | ADC1   | REGIST             | ER MA  | P FOR c | ISPIC33 | FJXX(G   | P/MC)102             | 2 DEVIC     | ES        | -     |       |        |        |          | -        |         |               |

|-----------|-------------|--------|--------------------|--------|---------|---------|----------|----------------------|-------------|-----------|-------|-------|--------|--------|----------|----------|---------|---------------|

| File Name | SFR<br>Addr | Bit 15 | Bit 14             | Bit 13 | Bit 12  | Bit 11  | Bit 10   | Bit 9                | Bit 8       | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300        |        |                    |        |         |         |          |                      | ADC1 Data   | Buffer 0  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF1  | 0302        |        |                    |        |         |         |          |                      | ADC1 Data   | Buffer 1  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF2  | 0304        |        |                    |        |         |         |          |                      | ADC1 Data   | Buffer 2  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF3  | 0306        |        |                    |        |         |         |          |                      | ADC1 Data   | Buffer 3  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF4  | 0308        |        |                    |        |         |         |          |                      | ADC1 Data   | Buffer 4  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF5  | 030A        |        |                    |        |         |         |          |                      | ADC1 Data   | Buffer 5  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF6  | 030C        |        |                    |        |         |         |          |                      | ADC1 Data   | Buffer 6  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF7  | 030E        |        |                    |        |         |         |          |                      | ADC1 Data   | Buffer 7  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF8  | 0310        |        |                    |        |         |         |          |                      | ADC1 Data   | Buffer 8  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF9  | 0312        |        | ADC1 Data Buffer 9 |        |         |         |          |                      |             |           | xxxx  |       |        |        |          |          |         |               |

| ADC1BUFA  | 0314        |        |                    |        |         |         |          | A                    | ADC1 Data E | Buffer 10 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFB  | 0316        |        |                    |        |         |         |          | ŀ                    | ADC1 Data B | Buffer 11 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFC  | 0318        |        |                    |        |         |         |          | ŀ                    | ADC1 Data E | Buffer 12 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFD  | 031A        |        |                    |        |         |         |          | ŀ                    | ADC1 Data E | Buffer 13 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFE  | 031C        |        |                    |        |         |         |          | A                    | ADC1 Data E | Buffer 14 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFF  | 031E        |        |                    |        |         |         |          | A                    | ADC1 Data E | Buffer 15 |       |       |        |        |          |          |         | xxxx          |

| AD1CON1   | 0320        | ADON   | _                  | ADSIDL | _       | —       | _        | FORM1                | FORM0       | SSRC2     | SSRC1 | SSRC0 | _      | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322        | VCFG2  | VCFG1              | VCFG0  | _       | —       | CSCNA    | CHPS1                | CHPS0       | BUFS      |       | SMPI3 | SMPI2  | SMPI1  | SMPI0    | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324        | ADRC   | _                  | —      | SAMC4   | SAMC3   | SAMC2    | SAMC1                | SAMC0       | ADCS7     | ADCS6 | ADCS5 | ADCS4  | ADCS3  | ADCS2    | ADCS1    | ADCS0   | 0000          |

| AD1CHS123 | 0326        | —      | _                  | _      | _       | —       | CH123NB1 | CH123NB0             | CH123SB     | _         |       |       | _      | _      | CH123NA1 | CH123NA0 | CH123SA | 0000          |

| AD1CHS0   | 0328        | CH0NB  | _                  | _      | CH0SB4  | CH0SB3  | CH0SB2   | CH0SB1               | CH0SB0      | CH0NA     |       |       | CH0SA4 | CH0SA3 | CH0SA2   | CH0SA1   | CH0SA0  | 0000          |

| AD1PCFGL  | 032C        | —      | _                  | —      | _       | —       |          | 10:9> <sup>(1)</sup> | _           | _         | _     |       |        | PC     | FG<5:0>  |          |         | 0000          |

| AD1CSSL   | 0330        | —      | _                  | —      | —       | _       | CSS<1    | 0:9> <sup>(1)</sup>  | —           | _         | —     |       |        | С      | SS<5:0>  |          |         | 0000          |

#### TABLE 4-16: ADC1 REGISTER MAP FOR dsPIC33FJXX(GP/MC)102 DEVICES

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PCFG<10:9> and CSS<10:9> bits are available in dsPIC33FJ32(GP/MC)101/102 devices only.

### 8.2 Oscillator Control Registers

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0          | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                         | R-0                                                                                                                                                                                                                                                                                                                                                                           | R-0                                | U-0              | R/W-y                        | R/W-y                   | R/W-y    |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|------------------------------|-------------------------|----------|--|--|--|

| —            | COSC2                                                                                                                                                                                                                                                                                                                                                                                                                                       | COSC1                                                                                                                                                                                                                                                                                                                                                                         | COSC0                              | _                | NOSC2 <sup>(2)</sup>         | NOSC1 <sup>(2)</sup>    | NOSCO(2) |  |  |  |

| bit 15       |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                               |                                    |                  |                              |                         | bit 8    |  |  |  |

| R/W-0        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                       | R-0                                                                                                                                                                                                                                                                                                                                                                           | U-0                                | R/C-0            | U-0                          | R/W-0                   | R/W-0    |  |  |  |

| CLKLOC       |                                                                                                                                                                                                                                                                                                                                                                                                                                             | LOCK                                                                                                                                                                                                                                                                                                                                                                          | 0-0                                | CF               | 0-0                          | LPOSCEN                 | OSWEN    |  |  |  |

| bit 7        | IOLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                      | LOOK                                                                                                                                                                                                                                                                                                                                                                          |                                    | UF               | _                            | LFUSCEN                 | bit (    |  |  |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                               |                                    |                  |                              |                         | bit (    |  |  |  |

| Legend:      |                                                                                                                                                                                                                                                                                                                                                                                                                                             | C = Clearable                                                                                                                                                                                                                                                                                                                                                                 | e bit                              | y = Value set    | from Configura               | tion bits on POI        | २        |  |  |  |

| R = Readab   | ole bit                                                                                                                                                                                                                                                                                                                                                                                                                                     | W = Writable                                                                                                                                                                                                                                                                                                                                                                  | bit                                | U = Unimpler     | mented bit, read             | l as '0'                |          |  |  |  |

| -n = Value a | at POR                                                                                                                                                                                                                                                                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                              |                                    | '0' = Bit is cle | ared                         | x = Bit is unkn         | own      |  |  |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                               |                                    |                  |                              |                         |          |  |  |  |

| bit 15       | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                  | ted: Read as '                                                                                                                                                                                                                                                                                                                                                                | 0'                                 |                  |                              |                         |          |  |  |  |

| bit 14-12    |                                                                                                                                                                                                                                                                                                                                                                                                                                             | Current Oscilla                                                                                                                                                                                                                                                                                                                                                               |                                    | · ·              | <b>'</b> )                   |                         |          |  |  |  |

|              | <ul> <li>111 = Fast RC Oscillator (FRC) with Divide-by-n</li> <li>110 = Fast RC Oscillator (FRC) with Divide-by-16</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator (MS, EC) with PLL</li> <li>010 = Primary Oscillator (MS, HS, EC)</li> <li>001 = Fast RC Oscillator (FRC) with Divide-by-n and PLL (FRCPLL)</li> <li>000 = Fast RC Oscillator (FRC)</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                               |                                    |                  |                              |                         |          |  |  |  |

| bit 11       | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                    |                                    |                  |                              |                         |          |  |  |  |

| bit 10-8     | NOSC<2:0>:                                                                                                                                                                                                                                                                                                                                                                                                                                  | New Oscillator                                                                                                                                                                                                                                                                                                                                                                | Selection bits                     | <sub>S</sub> (2) |                              |                         |          |  |  |  |

|              | 110 = Fast R<br>101 = Low-Pc<br>100 = Second<br>011 = Primar<br>010 = Primar<br>001 = Fast R                                                                                                                                                                                                                                                                                                                                                | 111 = Fast RC Oscillator (FRC) with Divide-by-n<br>110 = Fast RC Oscillator (FRC) with Divide-by-16<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Secondary Oscillator (SOSC)<br>011 = Primary Oscillator (MS, EC) with PLL<br>010 = Primary Oscillator (MS, HS, EC)<br>001 = Fast RC Oscillator (FRC) with Divide-by-n and PLL (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |                                    |                  |                              |                         |          |  |  |  |

| bit 7        | CLKLOCK: C                                                                                                                                                                                                                                                                                                                                                                                                                                  | lock Lock Ena                                                                                                                                                                                                                                                                                                                                                                 | ble bit                            |                  |                              |                         |          |  |  |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                               |                                    |                  | KSM<1:0> (FO                 | SC<7:6>) = 0b           | 01):     |  |  |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                             | itching is disab<br>itching is enab                                                                                                                                                                                                                                                                                                                                           |                                    |                  | n be modified by             | / clock switchin        | q        |  |  |  |

| bit 6        |                                                                                                                                                                                                                                                                                                                                                                                                                                             | ipheral Pin Sel                                                                                                                                                                                                                                                                                                                                                               | -                                  |                  |                              |                         | -        |  |  |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                             | = Peripheral Pin Select is locked, a write to Peripheral Pin Select registers is not allowed                                                                                                                                                                                                                                                                                  |                                    |                  |                              |                         |          |  |  |  |

| L:4 F        | -                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |                                    | write to Periph  | eral Pin Select              | registers is allo       | wed      |  |  |  |

| bit 5        |                                                                                                                                                                                                                                                                                                                                                                                                                                             | LOCK: PLL Lock Status bit (read-only)<br>1 = Indicates that PLL is in lock or PLL start-up timer is satisfied                                                                                                                                                                                                                                                                 |                                    |                  |                              |                         |          |  |  |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                               |                                    |                  | satisfied<br>progress or PLL | is disabled             |          |  |  |  |

| bit 4        |                                                                                                                                                                                                                                                                                                                                                                                                                                             | ted: Read as '                                                                                                                                                                                                                                                                                                                                                                |                                    |                  | -                            |                         |          |  |  |  |

|              | Nrites to this regis<br>dsPIC33/PIC24                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                               |                                    |                  | Oscillator (Part             | : <b>VI)</b> " (DS70644 | ) in the |  |  |  |

| <b>2:</b> [  | Direct clock switch<br>This applies to cloo<br>mode as a transitio                                                                                                                                                                                                                                                                                                                                                                          | es between an<br>ck switches in o                                                                                                                                                                                                                                                                                                                                             | y primary osci<br>either directior | llator mode wit  | ances, the appli             |                         |          |  |  |  |

mode as a transitional clock source between the two PLL modes.

# 12.3 Timer2/3 and Timer4/5 Control Registers

| _             |                                       |                              |                |                  |                 |                 |       |  |  |  |

|---------------|---------------------------------------|------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|

| R/W-0         | U-0                                   | R/W-0                        | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |

| TON           |                                       | TSIDL                        | _              |                  | —               |                 | _     |  |  |  |

| bit 15        |                                       |                              |                |                  |                 |                 | bit 8 |  |  |  |

|               |                                       |                              |                |                  |                 |                 |       |  |  |  |

| U-0           | R/W-0                                 | R/W-0                        | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |

| _             | TGATE                                 | TCKPS1                       | TCKPS0         | T32              | —               | TCS             | —     |  |  |  |

| bit 7         |                                       |                              |                |                  |                 |                 | bit C |  |  |  |

|               |                                       |                              |                |                  |                 |                 |       |  |  |  |

| Legend:       |                                       |                              |                |                  |                 |                 |       |  |  |  |

| R = Readabl   | e bit                                 | W = Writable I               | oit            | U = Unimpler     | mented bit, rea | ad as '0'       |       |  |  |  |

| -n = Value at | POR                                   | '1' = Bit is set             |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |

|               |                                       |                              |                |                  |                 |                 |       |  |  |  |

| bit 15        | TON: Timer2                           | On bit                       |                |                  |                 |                 |       |  |  |  |

|               | When T32 = 2                          |                              |                |                  |                 |                 |       |  |  |  |

|               | 1 = Starts 32-                        |                              |                |                  |                 |                 |       |  |  |  |

|               | 0 = Stops 32-                         |                              |                |                  |                 |                 |       |  |  |  |

|               | <u>When T32 = 0</u><br>1 = Starts 16- |                              |                |                  |                 |                 |       |  |  |  |

|               | 0 = Stops 16-                         |                              |                |                  |                 |                 |       |  |  |  |

| bit 14        | Unimplemen                            | Unimplemented: Read as '0'   |                |                  |                 |                 |       |  |  |  |

| bit 13        | TSIDL: Timer                          | 2 Stop in Idle M             | lode bit       |                  |                 |                 |       |  |  |  |

|               |                                       | ues module ope               |                |                  | lle mode        |                 |       |  |  |  |

|               |                                       | s module opera               |                | de               |                 |                 |       |  |  |  |

| bit 12-7      | Unimplemen                            | ted: Read as '0              | )'             |                  |                 |                 |       |  |  |  |

| bit 6         |                                       | er2 Gated Time               | Accumulation   | Enable bit       |                 |                 |       |  |  |  |

|               | When TCS =                            |                              |                |                  |                 |                 |       |  |  |  |

|               | This bit is igno<br>When TCS =        |                              |                |                  |                 |                 |       |  |  |  |

|               |                                       | <u>o.</u><br>e accumulatior  | is enabled     |                  |                 |                 |       |  |  |  |

|               |                                       | e accumulation               |                |                  |                 |                 |       |  |  |  |

| bit 5-4       | TCKPS<1:0>                            | : Timer2 Input               | Clock Prescale | e Select bits    |                 |                 |       |  |  |  |

|               | 11 <b>= 1:256</b>                     |                              |                |                  |                 |                 |       |  |  |  |

|               | 10 = 1:64                             |                              |                |                  |                 |                 |       |  |  |  |

|               | 01 = 1:8<br>00 = 1:1                  |                              |                |                  |                 |                 |       |  |  |  |

| bit 3         |                                       | imer Mode Sele               | ct bit         |                  |                 |                 |       |  |  |  |

| Sit 0         |                                       | nd Timer3 form               |                | timer            |                 |                 |       |  |  |  |

|               |                                       | nd Timer3 act a              |                |                  |                 |                 |       |  |  |  |

| bit 2         | Unimplemen                            | ted: Read as '               | )'             |                  |                 |                 |       |  |  |  |

| bit 1         | TCS: Timer2                           | Clock Source S               | elect bit      |                  |                 |                 |       |  |  |  |

|               |                                       | clock from pin, <sup>-</sup> | Γ2CK (on the r | ising edge)      |                 |                 |       |  |  |  |

|               | 0 = Internal cl                       |                              |                |                  |                 |                 |       |  |  |  |

| bit 0         | Unimplemen                            | ted: Read as '0              | ) <b>'</b>     |                  |                 |                 |       |  |  |  |

#### REGISTER 12-1: T2CON: TIMER2 CONTROL REGISTER

### 13.1 Input Capture Control Register

#### **REGISTER 13-1: ICXCON: INPUT CAPTURE X CONTROL REGISTER**

| U-0           | U-0                                                                                                                                                                                    | R/W-0                                                                                                                            | U-0             | U-0               | U-0              | U-0                | U-0           |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|--------------------|---------------|--|--|--|--|

| _             |                                                                                                                                                                                        | ICSIDL                                                                                                                           | _               | _                 | _                | _                  | —             |  |  |  |  |

| bit 15        |                                                                                                                                                                                        |                                                                                                                                  |                 |                   |                  |                    | bit 8         |  |  |  |  |

|               |                                                                                                                                                                                        |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                                                  | R/W-0                                                                                                                            | R-0, HC         | R-0, HC           | R/W-0            | R/W-0              | R/W-0         |  |  |  |  |

| ICTMR         | ICI1                                                                                                                                                                                   | ICI0                                                                                                                             | ICOV            | ICBNE             | ICM2             | ICM1               | ICM0          |  |  |  |  |

| bit 7         |                                                                                                                                                                                        |                                                                                                                                  |                 |                   |                  |                    | bit           |  |  |  |  |

| Legend:       |                                                                                                                                                                                        | HC = Hardwa                                                                                                                      | are Clearable b | oit               |                  |                    |               |  |  |  |  |

| R = Readable  | e bit                                                                                                                                                                                  | W = Writable                                                                                                                     | bit             | U = Unimplem      | nented bit, read | d as '0'           |               |  |  |  |  |

| -n = Value at | POR                                                                                                                                                                                    | '1' = Bit is set                                                                                                                 |                 | '0' = Bit is clea |                  | x = Bit is unkr    | nown          |  |  |  |  |

|               |                                                                                                                                                                                        |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

| bit 15-14     | Unimplement                                                                                                                                                                            | ted: Read as '                                                                                                                   | 0'              |                   |                  |                    |               |  |  |  |  |

| bit 13        | ICSIDL: Input                                                                                                                                                                          | Capture x Sto                                                                                                                    | p in Idle Cont  | rol bit           |                  |                    |               |  |  |  |  |

|               | 1 = Input Cap                                                                                                                                                                          | -                                                                                                                                | -               |                   |                  |                    |               |  |  |  |  |

|               | 0 = Input Cap                                                                                                                                                                          | ture x module                                                                                                                    | will continue t | o operate in CF   | PU Idle mode     |                    |               |  |  |  |  |

| bit 12-8      | Unimplement                                                                                                                                                                            | ted: Read as '                                                                                                                   | 0'              |                   |                  |                    |               |  |  |  |  |

| oit 7         | ICTMR: Input Capture x Timer Select bits                                                                                                                                               |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

|               |                                                                                                                                                                                        | <ul> <li>1 = TMR2 contents are captured on a capture event</li> <li>0 = TMR3 contents are captured on a capture event</li> </ul> |                 |                   |                  |                    |               |  |  |  |  |

| bit 6-5       | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                                                 |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

|               | <ul> <li>11 = Interrupt on every fourth capture event</li> <li>10 = Interrupt on every third capture event</li> </ul>                                                                  |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

|               | 01 = Interrupt on every second capture event                                                                                                                                           |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

|               | 00 = Interrupt                                                                                                                                                                         |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

| bit 4         | ICOV: Input Capture x Overflow Status Flag bit (read-only)                                                                                                                             |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

|               | 1 = Input Capt<br>0 = No Input C                                                                                                                                                       |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

| bit 3         | ICBNE: Input Capture x Buffer Empty Status bit (read-only)                                                                                                                             |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

|               | 1 = Input Capt<br>0 = Input Capt                                                                                                                                                       |                                                                                                                                  |                 | least one more    | capture value    | can be read        |               |  |  |  |  |

| bit 2-0       | ICM<2:0>: Input Capture x Mode Select bits                                                                                                                                             |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

|               | <ul> <li>111 = Input Capture x functions as an interrupt pin only when device is in Sleep or Idle mode (rising edge detect only, all other control bits are not applicable)</li> </ul> |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

|               | 110 = Unuse                                                                                                                                                                            |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

|               |                                                                                                                                                                                        |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

|               | <ul><li>101 = Capture mode, every 16th rising edge</li><li>100 = Capture mode, every 4th rising edge</li></ul>                                                                         |                                                                                                                                  |                 |                   |                  |                    |               |  |  |  |  |

|               | 011 = Captur                                                                                                                                                                           | e mode, even                                                                                                                     |                 |                   |                  |                    |               |  |  |  |  |

|               | 011 = Captur<br>010 = Captur                                                                                                                                                           | e mode, every                                                                                                                    | / falling edge  |                   |                  |                    |               |  |  |  |  |

|               | 010 = Captur<br>001 = Captur                                                                                                                                                           | e mode, every                                                                                                                    | / falling edge  | and falling (ICI< | :1:0> bits do no | ot control interru | upt generatio |  |  |  |  |

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| U-0          | U-0                                                                                                     | R/W-0                                                 | R/W-0            | R/W-0                                | R/W-0             | R/W-0           | R/W-0         |  |  |

|--------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|--------------------------------------|-------------------|-----------------|---------------|--|--|

| _            |                                                                                                         | FBOV3H                                                | FBOV3L           | FBOV2H                               | FBOV2L            | FBOV1H          | FBOV1L        |  |  |

| bit 15       |                                                                                                         |                                                       |                  |                                      |                   |                 | bit 8         |  |  |

| R/W-0        | U-0                                                                                                     | U-0                                                   | U-0              | U-0                                  | R/W-1             | R/W-1           | R/W-1         |  |  |

| FLTBM        |                                                                                                         | _                                                     | _                | —                                    | FBEN3             | FBEN2           | FBEN1         |  |  |

| bit 7        |                                                                                                         |                                                       |                  |                                      |                   |                 | bit (         |  |  |

| Legend:      |                                                                                                         |                                                       |                  |                                      |                   |                 |               |  |  |

| R = Readal   | ble bit                                                                                                 | W = Writable                                          | bit              | U = Unimplem                         | nented bit, read  | 1 as '0'        |               |  |  |

| -n = Value a | at POR                                                                                                  | '1' = Bit is set                                      |                  | '0' = Bit is clea                    | ared              | x = Bit is unkr | iown          |  |  |

|              |                                                                                                         |                                                       |                  |                                      |                   |                 |               |  |  |

| bit 15-14    | Unimplemer                                                                                              | nted: Read as '                                       | 0'               |                                      |                   |                 |               |  |  |

| bit 13-8     | FBOV<3:1>F                                                                                              | H:FBOV<3:1>L                                          | .: Fault Input E | B PWMx Overrid                       | de Value bits     |                 |               |  |  |

|              |                                                                                                         |                                                       | -                | on an external                       |                   | ent             |               |  |  |

|              | 0 = The PWN                                                                                             | ۰.<br>۸x output pin is                                | driven inactiv   | e on an externa                      | al Fault input ev | vent            |               |  |  |

| bit 7        | FLTBM: Fau                                                                                              | It B Mode bit                                         |                  |                                      |                   |                 |               |  |  |

|              | 1 = The Faul                                                                                            | t B input pin fur                                     | nctions in the ( | Cycle-by-Cycle                       | mode              |                 |               |  |  |

|              | 0 = The Faul                                                                                            | t B input pin lat                                     | ches all contro  | ol pins to the pro                   | ogrammed stat     | tes in PxFLTBC  | ON<13:8>      |  |  |

| bit 6-3      | Unimplemer                                                                                              | nted: Read as '                                       | 0'               |                                      |                   |                 |               |  |  |

| bit 2        | FBEN3: Fau                                                                                              | lt Input B Enabl                                      | e bit            |                                      |                   |                 |               |  |  |

|              |                                                                                                         |                                                       |                  | ed by Fault Inpu                     |                   |                 |               |  |  |

|              |                                                                                                         |                                                       |                  | trolled by Fault                     | Input B           |                 |               |  |  |

| bit 1        |                                                                                                         | lt Input B Enabl                                      |                  |                                      |                   |                 |               |  |  |

|              |                                                                                                         |                                                       |                  | ed by Fault Inpu                     |                   |                 |               |  |  |

|              |                                                                                                         |                                                       |                  | trolled by Fault                     | Input B           |                 |               |  |  |

| bit 0        |                                                                                                         | It Input B Enabl                                      |                  |                                      |                   |                 |               |  |  |

|              |                                                                                                         |                                                       |                  | ed by Fault Inpu<br>trolled by Fault |                   |                 |               |  |  |

|              | 0 = F  VIVIXI I                                                                                         |                                                       | Dall is not com  | trolled by Fault                     | пригв             |                 |               |  |  |

|              | Comparator outpu                                                                                        |                                                       |                  |                                      |                   |                 |               |  |  |

|              | modules for Fault dedicated FLTA1                                                                       |                                                       |                  | ternally connec                      | t the desired c   | omparator outp  | ut pin to the |  |  |

|              |                                                                                                         | •                                                     | •                | lotaile                              |                   |                 |               |  |  |

|              |                                                                                                         | Refer to Table 15-1 for FLTB1 implementation details. |                  |                                      |                   |                 |               |  |  |

|              | The PxFLTACON register is a write-protected register. Refer to Section 15.3 "Write-Protected Registers" |                                                       |                  |                                      |                   |                 |               |  |  |

| 3:           |                                                                                                         |                                                       |                  | gister. Refer to                     | Section 15.3 "    | Write-Protecte  | d Registers   |  |  |

| 3:           | The PxFLTACON<br>for more information<br>During any Reset                                               | on on the unloc                                       | k sequence.      | •                                    |                   |                 | •             |  |  |

## **REGISTER 15-10: PxFLTBCON: PWMx FAULT B CONTROL REGISTER**<sup>(1,2,3,4)</sup>

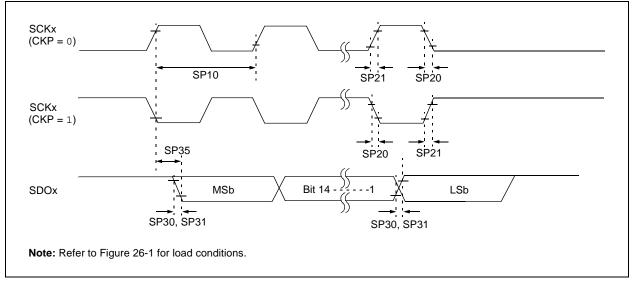

#### 16.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on  $\overline{SSx}$ .

- b) If FRMPOL = 0, use a pull-up resistor on  $\overline{SSx}$ .

| Note: | This insures that the first frame transmission    |

|-------|---------------------------------------------------|

|       | after initialization is not shifted or corrupted. |

- 2. In Non-Framed 3-Wire mode (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = <u>0</u>, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization, the master/slave will not lose sync due to an errant SCK transition that would cause the slave to accumulate data shift errors for both transmit and receive, appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- **Note:** Not all third-party devices support Frame mode timing. Refer to the SPI electrical characteristics for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

- 5. To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

- The SPI related pins (SDI1, SDO1, SCK1) are located at fixed positions in the dsPIC33FJ16(GP/ MC)10X devices. The same pins are remappable in the dsPIC33FJ32(GP/MC)10X devices.

#### 16.2 SPI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en554109          |

#### 16.2.1 KEY RESOURCES

- "Serial Peripheral Interface (SPI)" (DS70206) in the "dsPIC33/PIC24 Family Reference Manual

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual' sections

- Development Tools

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (Bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                   |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                                    |

| bit 3 | <ul> <li>PERR: Parity Error Status bit (read-only)</li> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                                            |

| bit 2 | <ul> <li>FERR: Framing Error Status bit (read-only)</li> <li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul>                                                                         |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (read-only/clear only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) will reset the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                         |

**Note 1:** Refer to "**UART**" (DS70188) in the dsPIC33/PIC24 Family Reference Manu**f** for mation on enabling the UART module for transmit operation.

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

REGISTER 21-9: ALRMVAL (WHEN ALRMPTR<1:0> = 01): ALARM WEEKDAY AND HOURS

|                   | VALUI |                  | (1)    | -                                  |        |                    |        |  |

|-------------------|-------|------------------|--------|------------------------------------|--------|--------------------|--------|--|

| U-0               | U-0   | U-0              | U-0    | U-0                                | R/W-x  | R/W-x              | R/W-x  |  |

| _                 | _     |                  | _      | —                                  | WDAY2  | WDAY1              | WDAY0  |  |

| bit 15            |       |                  |        |                                    |        |                    | bit 8  |  |

|                   |       |                  |        |                                    |        |                    |        |  |

| U-0               | U-0   | R/W-x            | R/W-x  | R/W-x                              | R/W-x  | R/W-x              | R/W-x  |  |

| —                 | —     | HRTEN1           | HRTEN0 | HRONE3                             | HRONE2 | HRONE1             | HRONE0 |  |

| bit 7             |       |                  |        |                                    |        |                    | bit (  |  |

|                   |       |                  |        |                                    |        |                    |        |  |

| Legend:           |       |                  |        |                                    |        |                    |        |  |

| R = Readable bit  | t     | W = Writable     | bit    | U = Unimplemented bit, read as '0' |        |                    |        |  |

| -n = Value at POR |       | '1' = Bit is set |        | '0' = Bit is cleared               |        | x = Bit is unknown |        |  |

| Dit 15-11 | Unimplemented: Read as '0'                                       |