Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 14x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp104t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

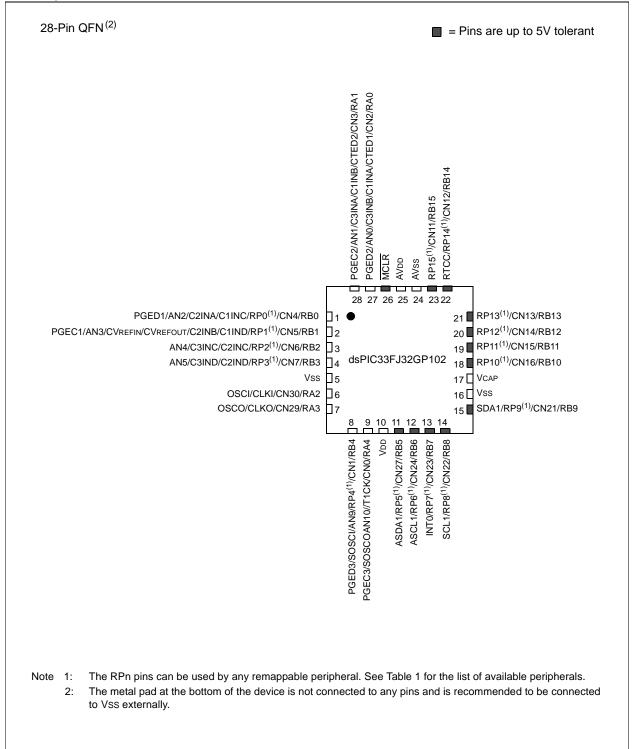

## Pin Diagrams (Continued)

# Table of Contents

| 1.0   | Device Overview                                                        |      |

|-------|------------------------------------------------------------------------|------|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers  | . 33 |

| 3.0   | CPU                                                                    |      |

| 4.0   | Memory Organization                                                    | . 49 |

| 5.0   | Flash Program Memory                                                   | . 83 |

| 6.0   | Resets                                                                 | . 87 |

| 7.0   | Interrupt Controller                                                   | . 95 |

| 8.0   | Oscillator Configuration                                               | 125  |

| 9.0   | Power-Saving Features                                                  | 133  |

| 10.0  | I/O Ports                                                              | 139  |

| 11.0  | Timer1                                                                 | 165  |

| 12.0  | Timer2/3 and Timer4/5                                                  | 167  |

| 13.0  | Input Capture                                                          | 175  |

| 14.0  | Output Compare                                                         | 177  |

| 15.0  | Motor Control PWM Module                                               | 181  |

| 16.0  | Serial Peripheral Interface (SPI)                                      |      |

| 17.0  | Inter-Integrated Circuit <sup>™</sup> (I <sup>2</sup> C <sup>™</sup> ) | 203  |

|       | Universal Asynchronous Receiver Transmitter (UART)                     |      |

|       | 10-Bit Analog-to-Digital Converter (ADC)                               |      |

| 20.0  | Comparator Module                                                      | 231  |

| 21.0  | Real-Time Clock and Calendar (RTCC)                                    |      |

| 22.0  | Charge Time Measurement Unit (CTMU)                                    | 255  |

| 23.0  | Special Features                                                       | 261  |

| 24.0  | Instruction Set Summary                                                | 269  |

| 25.0  | Development Support                                                    | 277  |

| 26.0  | Electrical Characteristics                                             |      |

| 27.0  | High-Temperature Electrical Characteristics                            |      |

| 28.0  | Packaging Information                                                  | 343  |

| Appe  | ndix A: Revision History                                               | 373  |

| Index |                                                                        | 381  |

| The N | /icrochip Web Site                                                     | 387  |

| Custo | mer Change Notification Service                                        | 387  |

|       | mer Support                                                            |      |

| Produ | Ict Identification System                                              | 389  |

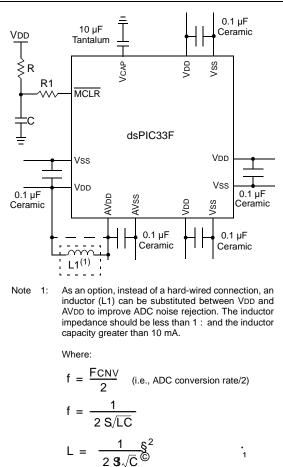

## FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

## 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.3 CPU Logic Filter Capacitor Connection (V CAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to Section 26.0 "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to Section 23.2 "On-Chip Voltage Regulator" for details.

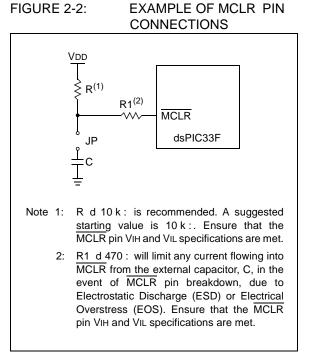

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the  $\overline{MCLR}$  pin.

| U-0              | <u>U-0</u>                                                                                                      | U-0                                                           | R/W-0                              | R/W-0               | R-0              | R-0              | R-0   |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------|---------------------|------------------|------------------|-------|--|--|--|--|--|

| _                |                                                                                                                 | _                                                             | US                                 | EDT <sup>(1)</sup>  | DL2              | DL1              | DL0   |  |  |  |  |  |

| bit 15           |                                                                                                                 |                                                               |                                    |                     |                  |                  | bit 8 |  |  |  |  |  |

| R/W-0            | R/W-0                                                                                                           | R/W-1                                                         | R/W-0                              | R/C-0               | R/W-0            | R/W-0            | R/W-0 |  |  |  |  |  |

| SATA             | SATB                                                                                                            | SATDW                                                         | ACCSAT                             | IPL3 <sup>(2)</sup> | PSV              | RND              | IF    |  |  |  |  |  |

| bit 7            |                                                                                                                 | _                                                             |                                    | -                   | _                | 11               | bit ( |  |  |  |  |  |

|                  |                                                                                                                 |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

| Legend:          |                                                                                                                 | C = Clearable                                                 |                                    |                     |                  |                  |       |  |  |  |  |  |

| R = Readable     |                                                                                                                 | W = Writable                                                  |                                    | -n = Value at       | -                | '1' = Bit is set |       |  |  |  |  |  |

| 0' = Bit is clea | ared                                                                                                            | 'x = Bit is unk                                               | nown                               | U = Unimpier        | mented bit, read |                  |       |  |  |  |  |  |

| bit 15-13        | Unimplement                                                                                                     | ed: Read as '                                                 | 0'                                 |                     |                  |                  |       |  |  |  |  |  |

| bit 12           | US: DSP Mul                                                                                                     | tiply Unsigned                                                | Signed Contro                      | ol bit              |                  |                  |       |  |  |  |  |  |

|                  | •                                                                                                               | ne multiplies a                                               | •                                  |                     |                  |                  |       |  |  |  |  |  |

| L:4.4.4          | -                                                                                                               | ne multiplies a                                               | -                                  |                     |                  |                  |       |  |  |  |  |  |

| bit 11           | -                                                                                                               | -                                                             | ation Control bi                   |                     | on itoration     |                  |       |  |  |  |  |  |

|                  | <ul> <li>1 = Terminates executing DOloop at the end of current loop iteration</li> <li>0 = No effect</li> </ul> |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

| bit 10-8         | DL<2:0>: DO                                                                                                     | Loop Nesting                                                  | Level Status bi                    | ts                  |                  |                  |       |  |  |  |  |  |

|                  | 111 = 7 DOloops are active                                                                                      |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

|                  | :                                                                                                               |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

|                  | •<br>001 = 1 DOloop is active                                                                                   |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

|                  | 000 = 0 DOloops are active                                                                                      |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

| bit 7            | SATA: ACCA                                                                                                      | SATA: ACCA Saturation Enable bit                              |                                    |                     |                  |                  |       |  |  |  |  |  |

|                  |                                                                                                                 | tor A saturatio                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

| bit 6            |                                                                                                                 | tor A saturatio                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

| DILO             | SATB: ACCB Saturation Enable bit<br>1 = Accumulator B saturation is enabled                                     |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

|                  | <ul> <li>1 = Accumulator B saturation is enabled</li> <li>0 = Accumulator B saturation is disabled</li> </ul>   |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

| bit 5            | SATDW: Data                                                                                                     | SATDW: Data Space Write from DSP Engine Saturation Enable bit |                                    |                     |                  |                  |       |  |  |  |  |  |

|                  | 1 = Data space write saturation is enabled                                                                      |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

| 1.1.4            | 0 = Data space write saturation is disabled<br>ACCSAT: Accumulator Saturation Mode Select bit                   |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

| bit 4            |                                                                                                                 |                                                               |                                    | elect bit           |                  |                  |       |  |  |  |  |  |

|                  | 1 = 9.31 saturation (super saturation)<br>0 = 1.31 saturation (normal saturation)                               |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

| bit 3            | IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                                  |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

|                  | 1 = CPU Interrupt Priority Level is greater than 7                                                              |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

|                  |                                                                                                                 |                                                               | evel is 7 or less                  |                     |                  |                  |       |  |  |  |  |  |

| bit 2            | •                                                                                                               | •                                                             | ity in Data Spa                    |                     |                  |                  |       |  |  |  |  |  |

|                  | 1 = Program space is visible in data space<br>0 = Program space is not visible in data space                    |                                                               |                                    |                     |                  |                  |       |  |  |  |  |  |

| bit 1            | •                                                                                                               | ng Mode Selec                                                 | •                                  |                     |                  |                  |       |  |  |  |  |  |

|                  | 1 = Biased (c                                                                                                   | onventional) ro                                               | ounding is enal                    |                     |                  |                  |       |  |  |  |  |  |

| <b>h</b> it 0    |                                                                                                                 |                                                               | ounding is ena                     |                     |                  |                  |       |  |  |  |  |  |

| bit 0            | -                                                                                                               |                                                               | tiplier Mode Se<br>I for DSP multi |                     |                  |                  |       |  |  |  |  |  |

|                  |                                                                                                                 |                                                               | led for DSP multi                  |                     |                  |                  |       |  |  |  |  |  |

|                  |                                                                                                                 |                                                               |                                    | 1.2.1.5.200         |                  |                  |       |  |  |  |  |  |

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

|           | SFR  |        |                      |        |        |        |          |                      |         |             |         |         |         |        |          |          |         | All    |

|-----------|------|--------|----------------------|--------|--------|--------|----------|----------------------|---------|-------------|---------|---------|---------|--------|----------|----------|---------|--------|

| File Name | Addr | Bit 15 | Bit 14               | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9                | Bit 8   | Bit 7       | Bit 6 I | Bit 5 E | Bit 4 E | it 3   | Bit 2 E  | Sit1 B   | it O    | Resets |

| ADC1BUF0  | 0300 |        | ADC1 Data Buffer 0 x |        |        |        |          |                      |         |             |         |         |         | хххх   |          |          |         |        |

| ADC1BUF1  | 0302 |        |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 1       |         |         |        |          |          |         | xxxx   |

| ADC1BUF2  | 0304 |        |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 2       |         |         |        |          |          |         | xxxx   |

| ADC1BUF3  | 0306 |        |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 3       |         |         |        |          |          |         | xxxx   |

| ADC1BUF4  | 0308 |        |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 4       |         |         |        |          |          |         | хххх   |

| ADC1BUF5  | 030A |        |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 5       |         |         |        |          |          |         | хххх   |

| ADC1BUF6  | 030C |        |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 6       |         |         |        |          |          |         | хххх   |

| ADC1BUF7  | 030E |        |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 7       |         |         |        |          |          |         | хххх   |

| ADC1BUF8  | 0310 |        |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 8       |         |         |        |          |          |         | хххх   |

| ADC1BUF9  | 0312 |        |                      |        |        |        |          |                      | ADC1 D  | Data Buffer | 9       |         |         |        |          |          |         | хххх   |

| ADC1BUFA  | 0314 |        |                      |        |        |        |          |                      | ADC1 D  | ata Buffer  | 10      |         |         |        |          |          |         | хххх   |

| ADC1BUFB  | 0316 |        |                      |        |        |        |          |                      | ADC1 D  | ata Buffer  | 11      |         |         |        |          |          |         | xxxx   |

| ADC1BUFC  | 0318 |        |                      |        |        |        |          |                      |         | ata Buffer  |         |         |         |        |          |          |         | xxxx   |

| ADC1BUFD  | 031A |        |                      |        |        |        |          |                      | ADC1 D  | ata Buffer  | 13      |         |         |        |          |          |         | хххх   |

| ADC1BUFE  | 031C |        |                      |        |        |        |          |                      |         | ata Buffer  |         |         |         |        |          |          |         | XXXX   |

| ADC1BUFF  | 031E |        |                      |        |        |        |          |                      |         | ata Buffer  |         |         |         |        |          |          | 1       | XXXX   |

| AD1CON1   | 0320 | ADON   | —                    | ADSIDL |        | _      | _        | FORM1                | FORM0   | SSRC2       | SSRC1   | SSRC0   | _       | SIMSAM | ASAM     | SAMP     | DONE    | 0000   |

| AD1CON2   | 0322 | VCFG2  | VCFG1                | VCFG0  |        | —      | CSCNA    | CHPS1                | CHPS0   | BUFS        | _       | SMPI3   | SMPI2   | SMPI1  | SMPI0    | BUFM     | ALTS    | 0000   |

| AD1CON3   | 0324 | ADRC   | —                    |        | SAMC4  | SAMC3  | SAMC2    | SAMC1                | SAMC0   | ADCS7       | ADCS6   | ADCS5   | ADCS4   | ADCS3  | ADCS2    | ADCS1    | ADCS0   | 0000   |

| AD1CHS123 | 0326 | _      | —                    |        |        | —      | CH123NB1 | CH123NB0             | CH123SB | —           | —       |         | —       | —      | CH123NA1 | CH123NA0 | CH123SA | 0000   |

| AD1CHS0   | 0328 | CH0NB  |                      |        | CH0SB4 | CH0SB3 | CH0SB2   | CH0SB1               | CH0SB0  | CH0NA       | _       |         | CH0SA4  | CH0SA3 |          | CH0SA1   | CH0SA0  | 0000   |

| AD1PCFGL  | 032C |        | _                    |        |        |        |          | 10:9> <sup>(1)</sup> |         | —           | _       |         |         |        |          | G<3:0>   |         | 0000   |

| AD1CSSL   | 0330 | —      | —                    | —      | —      |        | CSS<1    | 0:9> <sup>(1)</sup>  | —       | —           | —       | —       | —       |        | CSS      | 8<3:0>   |         | 0000   |

# TABLE 4-15: ADC1 REGISTER MAP FOR dsPIC33FJXX(GP/MC)101 DEVICES

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PCFG<10:9> and CSS<10:9> bits are available in dsPIC33FJ32(GP/MC)101/102 devices only.

# 6.3 POR

A POR circuit ensures the device is reset from poweron. The POR circuit is active until VDD crosses the VPOR threshold and the delay, TPOR, has elapsed. The delay, TPOR, ensures that the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 26.0 "Electrical Characteristics" for details.

The Power-on Reset (POR) status bit in the Reset Control (RCON<0>) register is set to indicate the Power-on Reset.

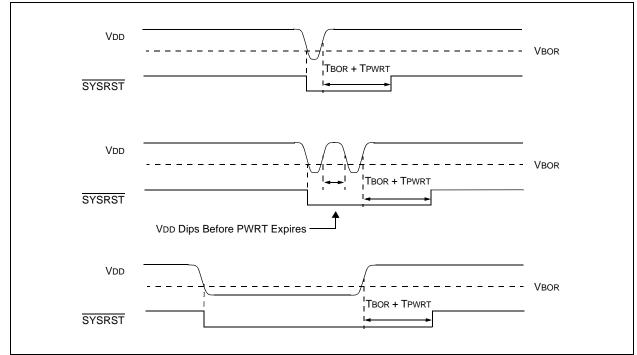

# 6.4 BOR and PWRT

The on-chip regulator has a BOR circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses the VBOR threshold and the delay, TBOR, has elapsed. The delay, TBOR, ensures the voltage regulator output becomes stable.

The Brown-out Reset (BOR) status bit in the Reset Control (RCON<1>) register is set to indicate the Brown-out Reset.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The Power-up Timer (PWRT) provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

Refer to Section 23.0 "Special Features" for further details.

Figure 6-3 shows the typical brown-out scenarios. The Reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point.

#### FIGURE 6-3: BROWN-OUT RESET SITUATIONS

#### 6.10.2 UNINITIALIZED W REGISTER RESET

Any attempts to use the Uninitialized W register as an Address Pointer will reset the device. The W register array (with the exception of W15) is cleared during all Resets and is considered uninitialized until written to.

#### 6.10.3 SECURITY RESET

If a Program Flow Change (PFC) or Vector Flow Change (VFC) targets a restricted location in a protected segment (Boot and Secure Segment), that operation will cause a Security Reset.

The PFC occurs when the Program Counter is reloaded as a result of a Call, Jump, Computed Jump, Return, Return from Subroutine or other form of branch instruction.

The VFC occurs when the Program Counter is reloaded with an interrupt or trap vector.

## 6.11 Using the RCON Status Bits

The user application can read the Reset Control (RCON) register after any device Reset to determine the cause of the Reset.

| Note: | The status bits in the RCON register      |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|

|       | should be cleared after they are read so  |  |  |  |  |  |  |

|       | that the next RCON register value after a |  |  |  |  |  |  |

|       | device Reset will be meaningful.          |  |  |  |  |  |  |

Table 6-3 provides a summary of Reset flag bit operation.

### TABLE 6-3: RESET FLAG BIT OPERATION

| Flag Bit         | Set by:                                                                | Cleared by:                                     |

|------------------|------------------------------------------------------------------------|-------------------------------------------------|

| TRAPR (RCON<15>) | Trap conflict event                                                    | POR, BOR                                        |

| IOPWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access or Security Reset | POR, BOR                                        |

| CM (RCON<9>)     | Configuration Mismatch                                                 | POR, BOR                                        |

| EXTR (RCON<7>)   | MCLR Reset                                                             | POR                                             |

| SWR (RCON<6>)    | RESETinstruction                                                       | POR, BOR                                        |

| WDTO (RCON<4>)   | WDT Time-out                                                           | PWRSAWnstruction,<br>CLRWDTnstruction, POR, BOR |

| SLEEP (RCON<3>)  | PWRSAV #SLEEPInstruction                                               | POR, BOR                                        |

| IDLE (RCON<2>)   | PWRSAV #IDLE instruction                                               | POR, BOR                                        |

| BOR (RCON<1>)    | POR, BOR                                                               | —                                               |

| POR (RCON<0>)    | POR                                                                    | —                                               |

Note: All Reset flag bits can be set or cleared by user software.

# 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70196) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. Devices can manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

# 9.1 Clock Frequency and Clock Switching

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC<2:0> bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in Section 8.0 "Oscillator Configuration"

## 9.2 Instruction-Based Power-Saving Modes

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices have two special powersaving modes that are entered through the execution of a special PWRSAWhstruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAWhstruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

# 9.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device will wake-up from Sleep mode on any of the these events:

- · Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 9-1: PWRSAWNSTRUCTION SYNTAX

PWRSAV

#SLEEP\_MODE

; Put the device into SLEEP mode

PWRSAV

#IDLE\_MODE

; Put the device into IDLE mode

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| REGISTER 10        | -3: RPINR                                                                                                                                       | 3: PERIPHE                                                                                                                                                               | RAL PIN SEI |                  | REGISTER 3       | }               |        |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------|------------------|-----------------|--------|

| U-0                | U-0                                                                                                                                             | U-0                                                                                                                                                                      | R/W-1       | R/W-1            | R/W-1            | R/W-1           | R/W-1  |

| _                  | —                                                                                                                                               | —                                                                                                                                                                        | T3CKR4      | T3CKR3           | T3CKR2           | T3CKR1          | T3CKR0 |

| bit 15             |                                                                                                                                                 |                                                                                                                                                                          |             |                  |                  |                 | bit 8  |

| U-0                | U-0                                                                                                                                             | U-0                                                                                                                                                                      | R/W-1       | R/W-1            | R/W-1            | R/W-1           | R/W-1  |

|                    |                                                                                                                                                 |                                                                                                                                                                          | T2CKR4      | T2CKR3           | T2CKR2           | T2CKR1          | T2CKR0 |

| bit 7              |                                                                                                                                                 |                                                                                                                                                                          | 1201(14     | 1201(10          | 1201112          | 120101          | bit    |

|                    |                                                                                                                                                 |                                                                                                                                                                          |             |                  |                  |                 |        |

| Legend:            |                                                                                                                                                 |                                                                                                                                                                          |             |                  |                  |                 |        |

| R = Readable b     | it                                                                                                                                              | W = Writable                                                                                                                                                             | bit         | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at PC   | )R                                                                                                                                              | '1' = Bit is set                                                                                                                                                         |             | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 7-5<br>bit 4-0 | 11111 = Input11110 = Rest11010 = Rest11001 = Input100001 = Input000001 = Input000000 = Input100000 = Input11111 = Input11110 = Rest11010 = Rest | It tied to Vss<br>erved<br>It tied to RP25<br>It tied to RP1<br>It tied to RP0<br>ed: Read as '<br>: Assign Timer<br>It tied to Vss<br>erved<br>erved<br>It tied to RP25 | 0'          |                  |                  | ng RPn Pin bits |        |

# REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

# 11.1 Timer1 Control Register

| R/W-0              | U-0                                                            | R/W-0            | U-0                       | U-0              | U-0              | U-0                | U-0   |  |  |  |  |

|--------------------|----------------------------------------------------------------|------------------|---------------------------|------------------|------------------|--------------------|-------|--|--|--|--|

| TON <sup>(1)</sup> | _                                                              | TSIDL            |                           | —                | —                | —                  | _     |  |  |  |  |

| bit 15             |                                                                |                  |                           |                  |                  |                    | bit 8 |  |  |  |  |

|                    |                                                                |                  |                           |                  |                  |                    |       |  |  |  |  |

| U-0                | R/W-0                                                          | R/W-0            | R/W-0                     | U-0              | R/W-0            | R/W-0              | U-0   |  |  |  |  |

| —                  | TGATE                                                          | TCKPS1           | TCKPS0                    | —                | TSYNC            | TCS <sup>(1)</sup> | _     |  |  |  |  |

| bit 7              |                                                                |                  |                           |                  |                  |                    | bit ( |  |  |  |  |

|                    |                                                                |                  |                           |                  |                  |                    |       |  |  |  |  |

| Legend:            |                                                                |                  |                           |                  |                  |                    |       |  |  |  |  |

| R = Readable       |                                                                | W = Writable     |                           | -                | mented bit, read | as '0'             |       |  |  |  |  |

| -n = Value at F    | POR                                                            | '1' = Bit is set |                           | '0' = Bit is cle | ared             | x = Bit is unkn    | own   |  |  |  |  |

|                    |                                                                | O +:+(1)         |                           |                  |                  |                    |       |  |  |  |  |

| bit 15             | TON: Timer1<br>1 = Starts 16-                                  |                  |                           |                  |                  |                    |       |  |  |  |  |

|                    | 0 = Stops 16-                                                  |                  |                           |                  |                  |                    |       |  |  |  |  |

| bit 14             | -                                                              | ed: Read as '    | 0'                        |                  |                  |                    |       |  |  |  |  |

| bit 13             | TSIDL: Timer                                                   | 1 Stop in Idle N | Mode bit                  |                  |                  |                    |       |  |  |  |  |

|                    | 1 = Discontinues module operation when device enters Idle mode |                  |                           |                  |                  |                    |       |  |  |  |  |

|                    |                                                                | s module opera   |                           | ode              |                  |                    |       |  |  |  |  |

| bit 12-7           | •                                                              | ed: Read as '    |                           |                  |                  |                    |       |  |  |  |  |

| bit 6              | TGATE: Timer1 Gated Time Accumulation Enable bit               |                  |                           |                  |                  |                    |       |  |  |  |  |

|                    | When TCS = 1:<br>This bit is ignored.                          |                  |                           |                  |                  |                    |       |  |  |  |  |

|                    | When $TCS = 0$ :                                               |                  |                           |                  |                  |                    |       |  |  |  |  |

|                    | 1 = Gated time accumulation is enabled                         |                  |                           |                  |                  |                    |       |  |  |  |  |

|                    | 0 = Gated tim                                                  | e accumulation   | n is disabled             |                  |                  |                    |       |  |  |  |  |

| bit 5-4            | TCKPS<1:0> Timer1 Input Clock Prescale Select bits             |                  |                           |                  |                  |                    |       |  |  |  |  |

|                    | 11 = 1:256<br>10 = 1:64                                        |                  |                           |                  |                  |                    |       |  |  |  |  |

|                    | 10 = 1.64<br>01 = 1.8                                          |                  |                           |                  |                  |                    |       |  |  |  |  |

|                    | 00 = 1:1                                                       |                  |                           |                  |                  |                    |       |  |  |  |  |

| bit 3              | Unimplement                                                    | ed: Read as '    | 0'                        |                  |                  |                    |       |  |  |  |  |

| bit 2              | TSYNC: Time                                                    | er1 External Cl  | ock Input Synd            | chronization Se  | elect bit        |                    |       |  |  |  |  |

|                    | When TCS = 1:                                                  |                  |                           |                  |                  |                    |       |  |  |  |  |

|                    | 1 = Synchronizes external clock input                          |                  |                           |                  |                  |                    |       |  |  |  |  |

|                    | 0 = Does not synchronize external clock input<br>When TCS = 0: |                  |                           |                  |                  |                    |       |  |  |  |  |

|                    | This bit is igno                                               |                  |                           |                  |                  |                    |       |  |  |  |  |

| bit 1              | TCS: Timer1                                                    | Clock Source S   | Select bit <sup>(1)</sup> |                  |                  |                    |       |  |  |  |  |

|                    |                                                                | clock from pin,  | T1CK (on the              | rising edge)     |                  |                    |       |  |  |  |  |

|                    | 0 = Internal cl                                                | lock (ECY)       |                           |                  |                  |                    |       |  |  |  |  |

| bit 0              | Unimplemented: Read as '0'                                     |                  |                           |                  |                  |                    |       |  |  |  |  |

# REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER

NOTES:

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| U-0                                         | U-0                  | U-0                  | U-0                  | U-0                                | R/W-0                | R/W-0                | R/W-0                |  |

|---------------------------------------------|----------------------|----------------------|----------------------|------------------------------------|----------------------|----------------------|----------------------|--|

| —                                           | —                    | —                    | —                    | —                                  | PMOD3                | PMOD2                | PMOD1                |  |

| bit 15                                      |                      |                      |                      |                                    |                      |                      | bit 8                |  |

|                                             |                      |                      |                      |                                    |                      |                      |                      |  |

| U-0                                         | R/W-0                | R/W-0                | R/W-0                | U-0                                | R/W-0                | R/W-0                | R/W-0                |  |

|                                             | PEN3H <sup>(2)</sup> | PEN2H <sup>(2)</sup> | PEN1H <sup>(2)</sup> | —                                  | PEN3L <sup>(2)</sup> | PEN2L <sup>(2)</sup> | PEN1L <sup>(2)</sup> |  |

| bit 7                                       |                      |                      |                      |                                    |                      |                      | bit 0                |  |

|                                             |                      |                      |                      |                                    |                      |                      |                      |  |

| Legend:                                     |                      |                      |                      |                                    |                      |                      |                      |  |

| R = Readable                                | bit                  | W = Writable         | bit                  | U = Unimplemented bit, read as '0' |                      |                      |                      |  |

| -n = Value at POR                           |                      | '1' = Bit is set     |                      | '0' = Bit is cle                   | ared                 | x = Bit is unknown   |                      |  |

|                                             |                      |                      |                      |                                    |                      |                      |                      |  |

| bit 15-11                                   | Unimplement          | ed: Read as '(       | )'                   |                                    |                      |                      |                      |  |

| bit 10-8 PMOD<3:1>: PWMx I/O Pair Mode bits |                      |                      |                      |                                    |                      |                      |                      |  |

|                                             |                      |                      |                      |                                    |                      |                      |                      |  |

# REGISTER 15-5: PWMxCON1: PWMx CONTROL REGISTER 1<sup>(1)</sup>

| Note 1: | The PWMxCON1 register is a write-protected register. Refer to Section 15.3 "Write-Protected |

|---------|---------------------------------------------------------------------------------------------|

|         | Registers" for more information on the unlock sequence.                                     |

1 = PWMx I/O pin pair is in the Independent PWM Output mode 0 = PWMx I/O pin pair is in the Complementary Output mode

0 = PWMxH pin is disabled, I/O pin becomes a general purpose I/O

0 = PWMxL pin is disabled, I/O pin becomes a general purpose I/O

Unimplemented: Read as '0'

Unimplemented: Read as '0'

PEN3H:PEN1H: PWMxH I/O Enable bits<sup>(2)</sup>

1 = PWMxH pin is enabled for PWMx output

PEN3L:PEN1L: PWMxL I/O Enable bits<sup>(2)</sup>

1 = PWMxL pin is enabled for PWMx output

- 2: The Reset status for these bits depends on the setting of the PWMPIN Configuration bit (FPOR<7>):

- If PWMPIN = 1 (default), the PWM pins are controlled by the PORT register at Reset, meaning they are initially programmed as inputs (i.e., tri-stated).

- If PWMPIN = 0, the PWM pins are controlled by the PWM module at Reset and are therefore, initially programmed as output pins.

bit 7

bit 3

bit 2-0

bit 6-4

REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- bit 4-2 SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup>

- 111 = Secondary prescale 1:1

- 110 = Secondary prescale 2:1

- 000 = Secondary prescale 8:1

- bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup>

- 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in the Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to a value of 1:1.