Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Becano                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 14x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

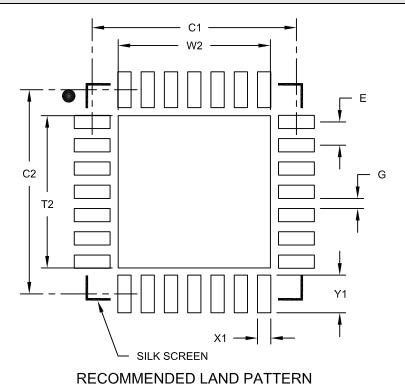

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp104t-i-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

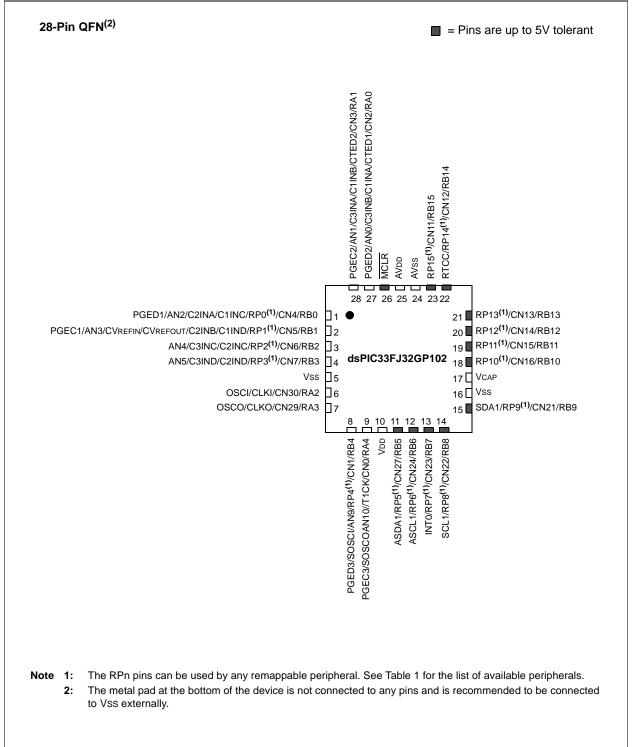

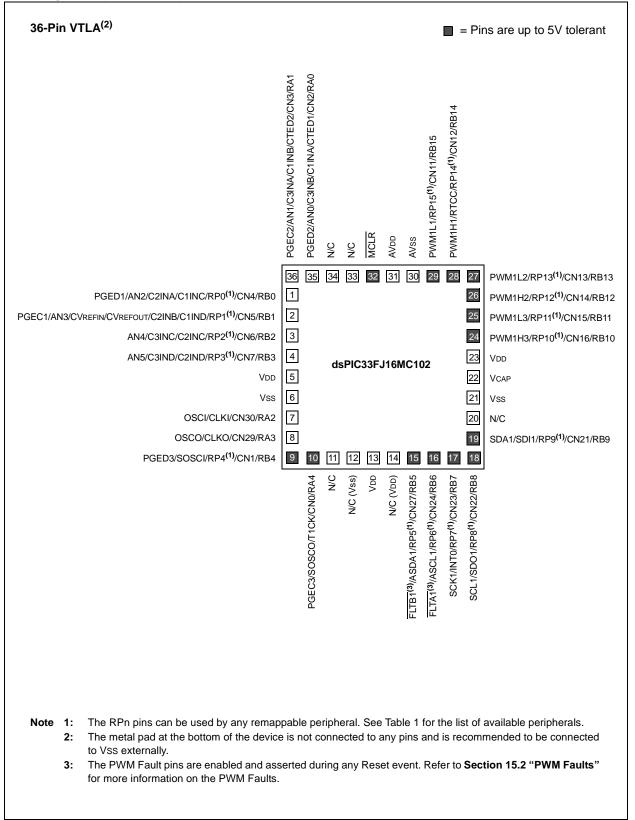

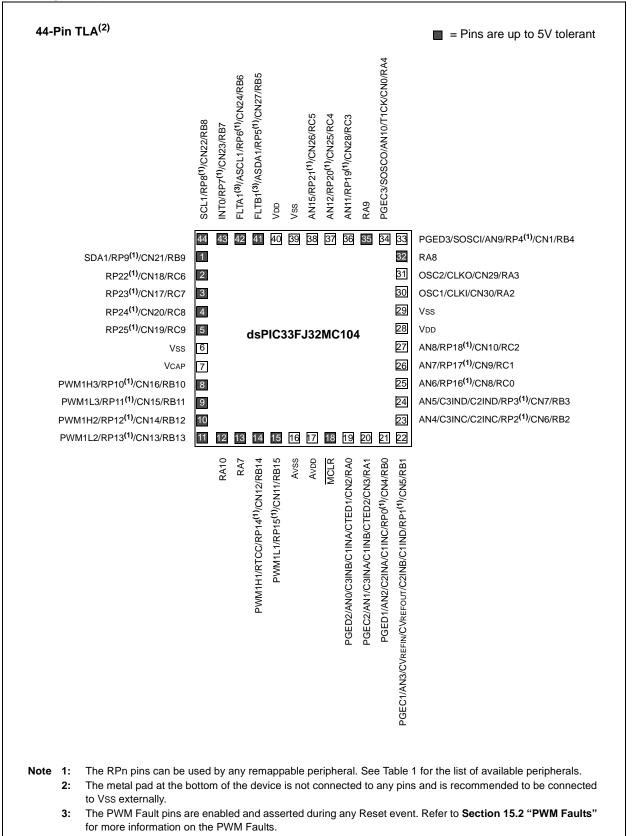

### Pin Diagrams (Continued)

### **Pin Diagrams (Continued)**

| TABLE 1-1              | TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED) |                   |           |                                                                            |  |  |  |  |

|------------------------|------------------------------------------------|-------------------|-----------|----------------------------------------------------------------------------|--|--|--|--|

| Pin Name               | Pin<br>Type                                    | Buffer<br>Type    | PPS       | Description                                                                |  |  |  |  |

| SCL1                   | I/O                                            | ST                | No        | Synchronous serial clock input/output for I2C1.                            |  |  |  |  |

| SDA1                   | I/O                                            | ST                | No        | Synchronous serial data input/output for I2C1.                             |  |  |  |  |

| ASCL1                  | I/O                                            | ST                | No        | Alternate synchronous serial clock input/output for I2C1.                  |  |  |  |  |

| ASDA1                  | I/O                                            | ST                | No        | Alternate synchronous serial data input/output for I2C1.                   |  |  |  |  |

| FLTA1(1,2,4)           | 1                                              | ST                | No        | PWM1 Fault A input.                                                        |  |  |  |  |

| FLTB1 <sup>(3,4)</sup> | 1                                              | ST                | No        | PWM1 Fault B input.                                                        |  |  |  |  |

| PWM1L1                 | 0                                              |                   | No        | PWM1 Low Output 1.                                                         |  |  |  |  |

| PWM1H1                 | 0                                              |                   | No        | PWM1 High Output 1.                                                        |  |  |  |  |

| PWM1L2                 | 0                                              |                   | No        | PWM1 Low Output 2.                                                         |  |  |  |  |

| PWM1H2                 | 0                                              |                   | No        | PWM1 High Output 2.                                                        |  |  |  |  |

| PWM1L3                 | 0                                              |                   | No        | PWM1 Low Output 3.                                                         |  |  |  |  |

| PWM1H3                 | Ō                                              | _                 | No        | PWM1 High Output 3.                                                        |  |  |  |  |

| RTCC                   | 0                                              | Digital           |           |                                                                            |  |  |  |  |

| CTPLS                  | 0                                              | Digital           | Yes       | CTMU pulse output.                                                         |  |  |  |  |

| CTED1                  | I                                              | Digital           | No        | CTMU External Edge Input 1.                                                |  |  |  |  |

| CTED2                  | I                                              | Digital           | No        | CTMU External Edge Input 2.                                                |  |  |  |  |

| CVREFIN                | I                                              | Analog            | No        | Comparator Voltage Positive Reference Input.                               |  |  |  |  |

| CVREFOUT               | 0                                              | Analog            | No        | Comparator Voltage Positive Reference Output.                              |  |  |  |  |

| C1INA                  | I                                              | Analog            | No        | Comparator 1 Positive Input A.                                             |  |  |  |  |

| C1INB                  | i                                              | Analog            | No        | Comparator 1 Negative Input B.                                             |  |  |  |  |

| C1INC                  | i                                              | Analog            | No        | Comparator 1 Negative Input C.                                             |  |  |  |  |

| C1IND                  | i                                              | Analog            | No        | Comparator 1 Negative Input D.                                             |  |  |  |  |

| C1OUT                  | Ō                                              | Digital           | Yes       | Comparator 1 Output.                                                       |  |  |  |  |

| C2INA                  | Ĩ                                              | Analog            | No        | Comparator 2 Positive Input A.                                             |  |  |  |  |

| C2INB                  | l i                                            | Analog            | No        | Comparator 2 Negative Input B.                                             |  |  |  |  |

| C2INC                  | i                                              | Analog            | No        | Comparator 2 Negative Input D.                                             |  |  |  |  |

| C2INC<br>C2IND         |                                                | Analog            | No        | Comparator 2 Negative Input C.                                             |  |  |  |  |

| C2OUT                  | 0                                              | Digital           | Yes       | Comparator 2 Output.                                                       |  |  |  |  |

|                        |                                                | •                 |           |                                                                            |  |  |  |  |

| C3INA                  |                                                | Analog            | No        | Comparator 3 Positive Input A.                                             |  |  |  |  |

| C3INB                  |                                                | Analog            | No        | Comparator 3 Negative Input B.                                             |  |  |  |  |

| C3INC                  |                                                | Analog            | No        | Comparator 3 Negative Input C.                                             |  |  |  |  |

| C3IND<br>C3OUT         |                                                | Analog<br>Digital | No<br>Yes | Comparator 3 Negative Input D.<br>Comparator 3 Output.                     |  |  |  |  |

|                        |                                                | ST                |           | Data I/O pin for Programming/Debugging Communication Channel 1.            |  |  |  |  |

| PGED1                  | I/O                                            |                   | No        |                                                                            |  |  |  |  |

| PGEC1                  |                                                | ST                | No        | Clock input pin for Programming/Debugging Communication Channel 1.         |  |  |  |  |

| PGED2                  | I/O                                            | ST                | No        |                                                                            |  |  |  |  |

| PGEC2                  | I                                              | ST                | No        |                                                                            |  |  |  |  |

| PGED3<br>PGEC3         | I/O                                            | ST<br>ST          | No<br>No  |                                                                            |  |  |  |  |

|                        | - ·                                            |                   |           | Clock input pin for Programming/Debugging Communication Channel 3.         |  |  |  |  |

| MCLR                   | I/P                                            | ST                | No        | Master Clear (Reset) input. This pin is an active-low Reset to the device. |  |  |  |  |

|                        |                                                |                   |           | input or output Analog = Analog input P = Power                            |  |  |  |  |

| S                      | I = Schr                                       | nitt Frigger      | input w   | ith CMOS levels O = Output I = Input                                       |  |  |  |  |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: An external pull-down resistor is required for the FLTA1 pin in dsPIC33FJXXMC101 (20-pin) devices.

- 2: The FLTA1 pin and the PWM1Lx/PWM1Hx pins are available in dsPIC(16/32)MC10X devices only.

- 3: The FLTB1 pin is available in dsPIC(16/32)MC102/104 devices only.

PPS = Peripheral Pin Select

- 4: The PWM Fault pins are enabled during any Reset event. Refer to **Section 15.2 "PWM Faults"** for more information on the PWM Faults.

- 5: Not all pins are available on all devices. Refer to the specific device in the "**Pin Diagrams**" section for availability.

- 6: These pins are available in dsPIC33FJ32(GP/MC)104 (44-pin) devices only.

The SAC and SAC.R instructions store either a truncated (SAC), or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see **Section 3.6.3.2 "Data Space Write Saturation**"). For the MAC class of instructions, the accumulator writeback operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

### 3.6.3.2 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly:

- For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF.

- For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000.

The MSb of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

### 3.6.4 BARREL SHIFTER

The barrel shifter can perform up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts, in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between Bit Positions 16 and 31 for right shifts, and between Bit Positions 0 and 16 for left shifts.

### 10.4 Peripheral Pin Select (PPS)

Peripheral Pin Select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral Pin Select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

#### 10.4.1 AVAILABLE PINS

The Peripheral Pin Select feature is used with a range of up to 16 pins. The number of available pins depends on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

### 10.4.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of Special Function Registers: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

### 10.4.2.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-10). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

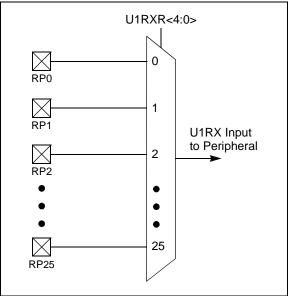

Figure 10-2 Illustrates remappable pin selection for U1RX input.

Note: For input mapping only, the Peripheral Pin Select (PPS) functionality does not have priority over the TRISx settings. Therefore, when configuring the RPx pin for input, the corresponding bit in the TRISx register must also be configured for input (i.e., set to '1').

### FIGURE 10-2: REMAPPABLE MUX INPUT FOR U1RX

| REGISTE            | R 12-4: 15CO                                       | N: IIMER5 C                                             | UNIKOL RE               | GISTER                      |                 |                    |             |  |  |  |

|--------------------|----------------------------------------------------|---------------------------------------------------------|-------------------------|-----------------------------|-----------------|--------------------|-------------|--|--|--|

| R/W-0              | U-0                                                | R/W-0                                                   | U-0                     | U-0                         | U-0             | U-0                | U-0         |  |  |  |

| TON <sup>(3)</sup> | —                                                  | TSIDL <sup>(2)</sup>                                    | —                       | —                           | —               | —                  | —           |  |  |  |

| bit 15             |                                                    |                                                         |                         |                             |                 |                    | bit 8       |  |  |  |

|                    |                                                    |                                                         |                         |                             |                 |                    |             |  |  |  |

| U-0                | R/W-0                                              | R/W-0                                                   | R/W-0                   | U-0                         | U-0             | R/W-0              | U-0         |  |  |  |

| —                  | TGATE <sup>(3)</sup>                               | TCKPS1 <sup>(3)</sup>                                   | TCKPS0 <sup>(3)</sup>   | —                           | —               | TCS <sup>(3)</sup> | —           |  |  |  |

| bit 7              |                                                    |                                                         |                         |                             |                 |                    | bit 0       |  |  |  |

| 1                  |                                                    |                                                         |                         |                             |                 |                    |             |  |  |  |

| Legend:            | b.1. b.34                                          |                                                         | L.14                    | II II.                      |                 | -l (Q)             |             |  |  |  |

| R = Reada          |                                                    | W = Writable                                            |                         | -                           | mented bit, rea |                    |             |  |  |  |

| -n = Value         | at POR                                             | '1' = Bit is set                                        |                         | '0' = Bit is cle            | eared           | x = Bit is unkn    | own         |  |  |  |

| bit 15             | TON: Timer5                                        | On hit(3)                                               |                         |                             |                 |                    |             |  |  |  |

| bit 10             | 1 = Starts 16-                                     |                                                         |                         |                             |                 |                    |             |  |  |  |

|                    | 0 = Stops 16-                                      |                                                         |                         |                             |                 |                    |             |  |  |  |

| bit 14             | Unimplemen                                         | nted: Read as '                                         | 0'                      |                             |                 |                    |             |  |  |  |

| bit 13             | TSIDL: Time                                        | r5 Stop in Idle I                                       | Node bit <sup>(2)</sup> |                             |                 |                    |             |  |  |  |

|                    |                                                    | ues timer opera                                         |                         |                             | e mode          |                    |             |  |  |  |

|                    | 0 = Continue                                       | s timer operatio                                        | on in Idle mode         | 9                           |                 |                    |             |  |  |  |

| bit 12-7           | Unimplemen                                         | nted: Read as '                                         | 0'                      | (-)                         |                 |                    |             |  |  |  |

| bit 6              |                                                    | er5 Gated Time                                          | Accumulation            | n Enable bit <sup>(3)</sup> |                 |                    |             |  |  |  |

|                    | <u>When TCS =</u><br>This bit is ign               |                                                         |                         |                             |                 |                    |             |  |  |  |

|                    | •                                                  |                                                         |                         |                             |                 |                    |             |  |  |  |

|                    |                                                    | When TCS = 0:<br>1 = Gated time accumulation is enabled |                         |                             |                 |                    |             |  |  |  |

|                    | 0 = Gated tim                                      | ne accumulatio                                          | n is disabled           |                             |                 |                    |             |  |  |  |

| bit 5-4            | TCKPS<1:0>                                         | : Timer5 Input                                          | Clock Prescal           | e Select bits <sup>(3</sup> | )               |                    |             |  |  |  |

|                    |                                                    | rescale value                                           |                         |                             |                 |                    |             |  |  |  |

|                    | 10 = 1:64 pre                                      |                                                         |                         |                             |                 |                    |             |  |  |  |

|                    | 01 = 1:8 pres<br>00 = 1:1 pres                     |                                                         |                         |                             |                 |                    |             |  |  |  |

| bit 3-2            | -                                                  | nted: Read as '                                         | 0'                      |                             |                 |                    |             |  |  |  |

| bit 1              | TCS: Timer5 Clock Source Select bit <sup>(3)</sup> |                                                         |                         |                             |                 |                    |             |  |  |  |

|                    |                                                    | clock from T5C                                          |                         |                             |                 |                    |             |  |  |  |

|                    |                                                    | lock (Fosc/2)                                           |                         |                             |                 |                    |             |  |  |  |

| bit 0              | Unimplemen                                         | nted: Read as '                                         | 0'                      |                             |                 |                    |             |  |  |  |

| Note 1:            | This register is ava                               | ailable in dsPIC                                        | 33FJ32(GP/N             | IC)10X device               | es only.        |                    |             |  |  |  |

|                    | When 32-bit timer                                  |                                                         |                         | -                           | -               | ster (T4CON<3>)    | , the TSIDL |  |  |  |

|                    | hit must be cleared                                | •                                                       | •                       | ,                           | Ŭ               | . ,                |             |  |  |  |

### REGISTER 12-4: T5CON: TIMER5 CONTROL REGISTER<sup>(1)</sup>

2: When 32-bit timer operation is enabled (132 = 1) in the Timer4 Control register (14CON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

**3:** When the 32-bit timer operation is enabled (T32 = 1) in the Timer4 Control register (T4CON<3>), these bits have no effect.

### 15.0 MOTOR CONTROL PWM MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Motor Control PWM" (DS70187) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ16MC10X devices have a 6-channel Pulse-Width Modulation (PWM) module.

The PWM module has the following features:

- Up to 16-bit resolution

- On-the-fly PWM frequency changes

- Edge-Aligned and Center-Aligned Output modes

- Single Pulse Generation mode

- Interrupt support for asymmetrical updates in Center-Aligned mode

- Output override control for Electrically Commutative Motor (ECM) operation or BLDC

- Special event comparator for scheduling other peripheral events

- Fault pins to optionally drive each of the PWM output pins to a defined state

- Duty cycle updates configurable to be immediate or synchronized to the PWM time base

### 15.1 PWM1: 6-Channel PWM Module

This module simplifies the task of generating multiple synchronized PWM outputs. The following power and motion control applications are supported by the PWM module:

- 3-Phase AC Induction Motor

- Switched Reluctance (SR) Motor

- Brushless DC (BLDC) Motor

- Uninterruptible Power Supply (UPS)

This module contains three duty cycle generators, numbered 1 through 3. The module has six PWM output pins, numbered PWM1H1/PWM1L1 through PWM1H3/PWM1L3. The six I/O pins are grouped into high/low numbered pairs, denoted by the suffix H or L, respectively. For complementary loads, the low PWM pins are always the complement of the corresponding high I/O pin.

### 15.2 PWM Faults

The Motor Control PWM module incorporates up to two Fault inputs, FLTA1 and FLTB1. These Fault inputs are implemented with Class B safety features. These features ensure that the PWM outputs enter a safe state when either of the Fault inputs is asserted.

The FLTA1 and FLTB1 pins, when enabled and having ownership of a pin, also enable a soft internal pull-down resistor. The soft pull-down provides a safety feature by automatically asserting the Fault should a break occur in the Fault signal connection.

The implementation of internal pull-down resistors is dependent on the device variant. Table 15-1 describes which devices and pins implement the internal pull-down resistors.

#### TABLE 15-1: INTERNAL PULL-DOWN RESISTORS ON PWM FAULT PINS

| Device           | Fault Pin | Internal<br>Pull-Down<br>Implemented? |  |  |  |  |  |  |

|------------------|-----------|---------------------------------------|--|--|--|--|--|--|

| dsPIC33FJXXMC101 | FLTA1     | No                                    |  |  |  |  |  |  |

| dsPIC33FJXXMC102 | FLTA1     | Yes                                   |  |  |  |  |  |  |

|                  | FLTB1     | Yes                                   |  |  |  |  |  |  |

| dsPIC33FJ32MC104 | FLTA1     | Yes                                   |  |  |  |  |  |  |

|                  | FLTB1     | Yes                                   |  |  |  |  |  |  |

On devices without internal pull-downs on the Fault pin, it is recommended to connect an external pull-down resistor for Class B safety features.

### 15.2.1 PWM FAULTS AT RESET

During any Reset event, the PWM module maintains ownership of both PWM Fault pins. At Reset, both Faults are enabled in latched mode to guarantee the fail-safe power-up of the application. The application software must clear both of the PWM Faults before enabling the Motor Control PWM module.

The Fault condition must be cleared by the external circuitry driving the Fault input pin high and clearing the Fault interrupt flag. After the Fault pin condition has been cleared, the PWM module restores the PWM output signals on the next PWM period or half-period boundary. Refer to **"Motor Control PWM"** (DS70187) in the *"dsPIC33/PIC24 Family Reference Manual"* for more information on the PWM Faults.

Note: The number of PWM Faults mapped to the device pins depend on the specific variant. Regardless of the variant, both Faults will be enabled during any Reset <u>event.</u> The <u>application</u> must clear both FLTA1 and FLTB1 before enabling the Motor Control PWM module. Refer to the specific device pin diagrams to see which Fault pins are mapped to the device pins.

### 15.3 Write-Protected Registers

On dsPIC33FJ(16/32)MC10X devices, write protection is implemented for the PWMxCON1, PxFLTACON and PxFLTBCON registers. The write protection feature prevents any inadvertent writes to these registers. The write protection feature can be controlled by the PWMLOCK Configuration bit in the FOSCSEL Configuration register. The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring PWMLOCK (FOSCSEL<6>) = 0.

The user application can gain access to these locked registers either by configuring the PWMLOCK bit (FOSCSEL<6>) = 0 or by performing the unlock sequence. To perform the unlock sequence, the user application must write two consecutive values (0xABCD and 0x4321) to the PWMxKEY register to perform the unlock operation. The write access to the PWMxCON1, PxFLTACON or PxFLTBCON registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access.

To write to all registers, the PWMxCON1, PxFLTACON and PxFLTBCON registers require three unlock operations.

The correct unlocking sequence is described in Example 15-1 and Example 15-2.

| U-0        | U-0                                 | U-0                                      | U-0                        | U-0             | R/W-0                | R/W-0                | R/W-0                |

|------------|-------------------------------------|------------------------------------------|----------------------------|-----------------|----------------------|----------------------|----------------------|

|            | —                                   |                                          |                            | —               | PMOD3                | PMOD2                | PMOD1                |

| bit 15     |                                     |                                          |                            |                 |                      |                      | bit 8                |

|            |                                     |                                          |                            |                 |                      |                      |                      |

| U-0        | R/W-0                               | R/W-0                                    | R/W-0                      | U-0             | R/W-0                | R/W-0                | R/W-0                |

| —          | PEN3H <sup>(2)</sup>                | PEN2H <sup>(2)</sup>                     | PEN1H <sup>(2)</sup>       | —               | PEN3L <sup>(2)</sup> | PEN2L <sup>(2)</sup> | PEN1L <sup>(2)</sup> |

| bit 7      |                                     |                                          |                            |                 |                      |                      | bit (                |

| Legend:    |                                     |                                          |                            |                 |                      |                      |                      |

| R = Read   | able bit                            | W = Writable                             | bit                        | U = Unimple     | mented bit, read     | d as '0'             |                      |

| -n = Value | e at POR                            | '1' = Bit is set                         |                            | '0' = Bit is cl | eared                | x = Bit is unkr      | nown                 |

|            |                                     | ) pin pair is in t<br>) pin pair is in t |                            |                 |                      |                      |                      |

| bit 7      |                                     | ted: Read as '                           | •                          | intary output   |                      |                      |                      |

| bit 6-4    | •                                   | IH: PWMxH I/(                            |                            | 2)              |                      |                      |                      |

|            | 1 = PWMxH p                         | oin is enabled f<br>oin is disabled,     | or PWMx outp               | out             | purpose I/O          |                      |                      |

| bit 3      | Unimplemen                          | ted: Read as '                           | 0'                         |                 |                      |                      |                      |

| bit 2-0    | PEN3L:PEN1                          | IL: PWMxL I/O                            | Enable bits <sup>(2)</sup> | )               |                      |                      |                      |

|            |                                     | in is enabled fo<br>in is disabled,      |                            |                 | purpose I/O          |                      |                      |

| Note 1:    | The PWMxCON1 I<br>Registers" for mo |                                          |                            |                 | to Section 15.3      | Write-Protec         | ted                  |

| 2:         | The Reset status f                  |                                          |                            |                 | PWMPIN Confi         | guration bit (FP     | POR<7>):             |

|            | • If PWMPIN = 1 (                   |                                          |                            |                 |                      |                      |                      |

### REGISTER 15-5: PWMxCON1: PWMx CONTROL REGISTER 1<sup>(1)</sup>

are initially programmed as inputs (i.e., tri-stated).

If PWMPIN = 0, the PWM pins are controlled by the PWM module at Reset and are therefore, initially programmed as output pins.

### 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit<sup>TM</sup> (I<sup>2</sup>C<sup>TM</sup>)" (DS70195) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit<sup>TM</sup> ( $I^2C^{TM}$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addresses

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addresses

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

### 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7-Bit and 10-Bit Addressing.

The I<sup>2</sup>C module can operate either as a slave or a master on an I<sup>2</sup>C bus.

The following types of  $I^2C$  operation are supported:

- I<sup>2</sup>C slave operation with 7-Bit Addressing

- I<sup>2</sup>C slave operation with 10-Bit Addressing

- I<sup>2</sup>C master operation with 7-Bit or 10-Bit Addressing

For details about the communication sequence in each of these modes, refer to the Microchip web site (www.microchip.com) for the latest *"dsPIC33/PIC24 Family Reference Manual"* sections.

### 17.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CxSTAT are read/write.

- I2CxRSR is the shift register used for shifting data

- I2CxRCV is the receive buffer and the register to which data bytes are written or from which data bytes are read

- I2CxTRN is the transmit register to which bytes are written during a transmit operation

- · I2CxADD register holds the slave address

- ADD10 status bit indicates 10-Bit Addressing mode

- I2CxBRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV and an interrupt pulse is generated.

## 17.3 I<sup>2</sup>C Control Registers

### REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0      | U-0                             | R/W-0                                                                                                                                                                 | R/W-1, HC                     | R/W-0                        | R/W-0                                             | R/W-0            | R/W-0           |  |  |  |  |

|------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------|---------------------------------------------------|------------------|-----------------|--|--|--|--|

| I2CEN      |                                 | I2CSIDL                                                                                                                                                               | SCLREL                        | IPMIEN                       | A10M                                              | DISSLW           | SMEN            |  |  |  |  |

| bit 15     |                                 |                                                                                                                                                                       |                               |                              |                                                   |                  | bit 8           |  |  |  |  |

|            |                                 |                                                                                                                                                                       |                               |                              |                                                   |                  |                 |  |  |  |  |

| R/W-0      | R/W-0                           | R/W-0                                                                                                                                                                 | R/W-0, HC                     | R/W-0, HC                    | R/W-0, HC                                         | R/W-0, HC        | R/W-0, HC       |  |  |  |  |

| GCEN       | STREN                           | ACKDT                                                                                                                                                                 | ACKEN                         | RCEN                         | PEN                                               | RSEN             | SEN             |  |  |  |  |

| bit 7      |                                 |                                                                                                                                                                       |                               |                              |                                                   |                  | bit (           |  |  |  |  |

| Legend:    |                                 | HC = Hardwa                                                                                                                                                           | re Clearable b                | it                           |                                                   |                  |                 |  |  |  |  |

| R = Reada  | able bit                        | W = Writable                                                                                                                                                          | bit                           | U = Unimpler                 | nented bit, read                                  | as '0'           |                 |  |  |  |  |

| -n = Value | at POR                          | '1' = Bit is set                                                                                                                                                      |                               | '0' = Bit is cle             |                                                   | x = Bit is unkno | own             |  |  |  |  |

| bit 15     | <b>12CEN:</b> 12Cx              | Enable bit                                                                                                                                                            |                               |                              |                                                   |                  |                 |  |  |  |  |

|            | 0 = Disables                    | the I2Cx modu                                                                                                                                                         | le; all l <sup>2</sup> C™ pir |                              | and SCLx pins a<br>ed by port function            |                  | 8               |  |  |  |  |

| bit 14     | Unimplemer                      | nted: Read as '                                                                                                                                                       | 0'                            |                              |                                                   |                  |                 |  |  |  |  |

| oit 13     |                                 | Cx Stop in Idle N                                                                                                                                                     |                               |                              |                                                   |                  |                 |  |  |  |  |

|            |                                 | ues module op                                                                                                                                                         |                               |                              | in Idle mode                                      |                  |                 |  |  |  |  |

|            |                                 | s module opera                                                                                                                                                        |                               |                              | $2^{\circ}$                                       |                  |                 |  |  |  |  |

| oit 12     |                                 | SCLREL: SCLx Release Control bit (when operating as I <sup>2</sup> C slave)                                                                                           |                               |                              |                                                   |                  |                 |  |  |  |  |

|            |                                 | 1 = Releases SCLx clock<br>0 = Holds SCLx clock low (clock stretch)                                                                                                   |                               |                              |                                                   |                  |                 |  |  |  |  |

|            | If STREN = 1                    |                                                                                                                                                                       | ,                             |                              |                                                   |                  |                 |  |  |  |  |

|            | Bit is R/W (i.e<br>beginning of | e., software car<br>every slave da                                                                                                                                    | ata byte transn               | nission. Hardw               | d write '1' to rele<br>are clears at er<br>ption. |                  |                 |  |  |  |  |

|            | -                               | reception. Hardware clears at every slave data byte reception.<br>If STREN = 0:                                                                                       |                               |                              |                                                   |                  |                 |  |  |  |  |

|            |                                 |                                                                                                                                                                       |                               |                              | k). Hardware cle<br>slave address b               |                  | g of every slav |  |  |  |  |

| bit 11     | -                               | data byte transmission. Hardware clears at end of every slave address byte reception.<br><b>IPMIEN:</b> Intelligent Peripheral Management Interface (IPMI) Enable bit |                               |                              |                                                   |                  |                 |  |  |  |  |

|            | 1 = IPMI mod                    | de is enabled; a                                                                                                                                                      | -                             |                              | -                                                 |                  |                 |  |  |  |  |

|            | 0 = IPMI mod                    | de is disabled                                                                                                                                                        |                               |                              |                                                   |                  |                 |  |  |  |  |

| bit 10     |                                 | 10-Bit Slave Ac                                                                                                                                                       |                               |                              |                                                   |                  |                 |  |  |  |  |

|            | -                               | ) is a 10-bit slav                                                                                                                                                    |                               |                              |                                                   |                  |                 |  |  |  |  |

|            |                                 | is a 7-bit slave                                                                                                                                                      |                               |                              |                                                   |                  |                 |  |  |  |  |

| bit 9      |                                 | able Slew Rate<br>control is disa                                                                                                                                     |                               |                              |                                                   |                  |                 |  |  |  |  |

|            |                                 | e control is enal                                                                                                                                                     |                               |                              |                                                   |                  |                 |  |  |  |  |

| bit 8      |                                 | us Input Levels                                                                                                                                                       |                               |                              |                                                   |                  |                 |  |  |  |  |

|            | 1 = Enables                     | I/O pin threshol<br>SMBus input th                                                                                                                                    | ds compliant v                | vith SMBus sp                | ecification                                       |                  |                 |  |  |  |  |

| bit 7      | GCEN: Gene                      | eral Call Enable                                                                                                                                                      | bit (when ope                 | rating as I <sup>2</sup> C s | lave)                                             |                  |                 |  |  |  |  |

|            |                                 | interrupt when                                                                                                                                                        |                               | -                            | ceived in the I2                                  | CxRSR (module    | e is enabled fo |  |  |  |  |

|            |                                 | , call address is                                                                                                                                                     | disabled                      |                              |                                                   |                  |                 |  |  |  |  |

0 = General call address is disabled

|                 | 0 2. 0 0.017                              |                                                                                                         |                            |                                          | OIOTEIX              |       |       |

|-----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------|----------------------|-------|-------|

| R/W-0           | R/W-0                                     | R/W-0                                                                                                   | U-0                        | R/W-0, HC                                | R/W-0                | R-0   | R-1   |

| UTXISEL1        | UTXINV                                    | UTXISEL0                                                                                                |                            | UTXBRK                                   | UTXEN <sup>(1)</sup> | UTXBF | TRMT  |

| bit 15          |                                           |                                                                                                         |                            |                                          |                      |       | bit 8 |

|                 |                                           |                                                                                                         |                            |                                          |                      |       |       |

| R/W-0           | R/W-0                                     | R/W-0                                                                                                   | R-1                        | R-0                                      | R-0                  | R/C-0 | R-0   |

| URXISEL1        | URXISEL0                                  | ADDEN                                                                                                   | RIDLE                      | PERR                                     | FERR                 | OERR  | URXDA |

| bit 7           |                                           |                                                                                                         |                            |                                          |                      |       | bit C |

|                 |                                           |                                                                                                         |                            |                                          |                      |       |       |

| Legend:         |                                           | C = Clearable b                                                                                         | oit                        | HC = Hardware Clearable bit              |                      |       |       |

| R = Readable    | bit                                       | W = Writable bit                                                                                        |                            | U = Unimplemented bit, read as '0'       |                      |       |       |

| -n = Value at F | POR                                       | '1' = Bit is set                                                                                        |                            | 0' = Bit is cleared $x = Bit is unknown$ |                      |       | nown  |

| bit 15,13       | 11 = Reserve<br>10 = Interrup<br>transmit | D>: UARTx Trans<br>ed; do not use<br>t when a charact<br>buffer becomes<br>t when the last ch<br>pleted | ter is transferre<br>empty | ed to the Transr                         | mit Shift Registe    | . ,   |       |

### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| 00 = Interrupt when a character is transferred to the | Transmit Shift Register (this implies there is at least |

|-------------------------------------------------------|---------------------------------------------------------|

| one character open in the transmit buffer)            |                                                         |

| bit 14  | UTXINV: UARTx Transmit Polarity Inversion bit                                                                                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If IREN = 0:                                                                                                                                                          |

|         | 1 = UxTX Idle state is '0'                                                                                                                                            |

|         | 0 = UxTX Idle state is '1'                                                                                                                                            |

|         | <u>If IREN = 1:</u>                                                                                                                                                   |

|         | 1 = IrDA encoded, UxTX Idle state is '1'                                                                                                                              |

|         | 0 = IrDA encoded, UxTX Idle state is '0'                                                                                                                              |

| bit 12  | Unimplemented: Read as '0'                                                                                                                                            |

| bit 11  | UTXBRK: UARTx Transmit Break bit                                                                                                                                      |

|         | <ul> <li>1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br/>cleared by hardware upon completion</li> </ul> |

|         | 0 = Sync Break transmission is disabled or completed                                                                                                                  |

| bit 10  | UTXEN: UARTx Transmit Enable bit <sup>(1)</sup>                                                                                                                       |

|         | 1 = Transmit is enabled, UxTX pin is controlled by UARTx                                                                                                              |

|         | <ul> <li>0 = Transmit is disabled, any pending transmission is aborted and the buffer is reset; UxTX pin is controlled by port</li> </ul>                             |

| bit 9   | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                                              |

|         | 1 = Transmit buffer is full                                                                                                                                           |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                                           |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                   |

|         | 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)                                                               |

|         | 0 = Transmit Shift Register is not empty, a transmission is in progress or queued                                                                                     |

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                             |

|         | 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)                                                                 |

|         | 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)                                                             |

|         | 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive                                                                    |

|         | buffer; receive buffer has one or more characters                                                                                                                     |

| Note 1  | Pater to "ILAPT" (DS70199) in the "doDIC22/DIC24 Family Pateroneo Manual" for information on applying                                                                 |

## **Note 1:** Refer to "**UART**" (DS70188) in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UART module for transmit operation.

# **REGISTER 21-8:** ALRMVAL (WHEN ALRMPTR<1:0> = 10): ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | _   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15-13 | Unimplemented: Read as '0'                                         |

|-----------|--------------------------------------------------------------------|

| bit 12    | MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit      |

|           | Contains a value of 0 or 1.                                        |

| bit 11-8  | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits |

|           | Contains a value from 0 to 9.                                      |

| bit 7-6   | Unimplemented: Read as '0'                                         |

| bit 5-4   | DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit bits   |

|           | Contains a value from 0 to 3.                                      |

| bit 3-0   | DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits   |

|           | Contains a value from 0 to 9.                                      |

|           |                                                                    |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

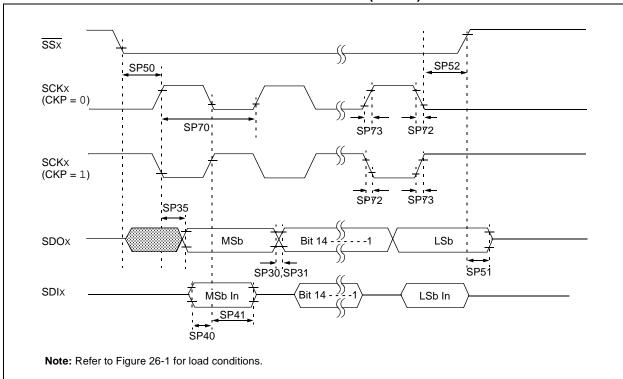

# TABLE 26-34:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ16(GP/MC)10X

| AC CHARACTERISTICS |                       |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.4V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |  |

|--------------------|-----------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                                                                                                                                                                                                                                                 | Тур <sup>(2)</sup> | Max | Units | Conditions                           |  |

| SP70               | TscP                  | Maximum SCKx Input Frequency                                 | —                                                                                                                                                                                                                                                                                   | —                  | 11  | MHz   | See Note 3                           |  |

| SP72               | TscF                  | SCKx Input Fall Time                                         | —                                                                                                                                                                                                                                                                                   | _                  |     | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP73               | TscR                  | SCKx Input Rise Time                                         | _                                                                                                                                                                                                                                                                                   |                    |     | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                   | —                                                                                                                                                                                                                                                                                   | _                  |     | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                   | —                                                                                                                                                                                                                                                                                   | —                  |     | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                                                                                                                                                                                                                                                   | 6                  | 20  | ns    |                                      |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                                                                                                                                                                                                                                                  |                    |     | ns    |                                      |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                                                                                                                                                                                                                                                  | _                  | —   | ns    |                                      |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                                                                                                                                                                                                                                                  | _                  | _   | ns    |                                      |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                                                                                                                                                                                                                                                 | —                  | _   | ns    |                                      |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10                                                                                                                                                                                                                                                                                  | —                  | 50  | ns    | See Note 4                           |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40                                                                                                                                                                                                                                                                        | —                  | _   | ns    | See Note 4                           |  |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                     | —                                                                                                                                                                                                                                                                                   | _                  | 50  | ns    |                                      |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

### FIGURE 26-17: SPIx SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ16(GP/MC)10X

### TABLE 26-50: COMPARATOR TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |      |       |            |  |

|--------------------|--------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic                                        | Min.                                                                                                                                                                                                                                                                                    | Тур | Max. | Units | Conditions |  |

| 300                | TRESP  | Response Time <sup>(1,2)</sup>                        | _                                                                                                                                                                                                                                                                                       | 150 | 400  | ns    |            |  |

| 301                | TMC20V | Comparator Mode Change to Output Valid <sup>(1)</sup> | —                                                                                                                                                                                                                                                                                       |     | 10   | μS    |            |  |