Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\cdot \mathbf{X} \mathbf{F}$

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 16 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                       |

| Number of I/O              | 15                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · ·                                                                            |

| RAM Size                   | 1K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 20-PDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc101-e-p |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### 4.2.6 SOFTWARE STACK

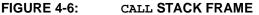

In addition to its use as a working register, the W15 register in the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices is also used as a Software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | concatenates the SRL register to the MSb |

|       | of the PC prior to the push.             |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned.

Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. However, the stack error trap will occur on a subsequent push operation. For example, to cause a stack error trap when the stack grows beyond address 0x0C00 in RAM, initialize the SPLIM with the value 0x0BFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the SFR space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### 4.2.7 DATA RAM PROTECTION FEATURE

The dsPIC33F product family supports data RAM protection features that enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM Segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM Segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

#### 4.3 Instruction Addressing Modes

The addressing modes shown in Table 4-40 form the basis of the addressing modes that are optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those provided in other instruction types.

#### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

#### 4.3.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all of the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

#### 6.3 POR

A POR circuit ensures the device is reset from poweron. The POR circuit is active until VDD crosses the VPOR threshold and the delay, TPOR, has elapsed. The delay, TPOR, ensures that the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to **Section 26.0** "**Electrical Characteristics**" for details.

The Power-on Reset (POR) status bit in the Reset Control (RCON<0>) register is set to indicate the Power-on Reset.

#### 6.4 BOR and PWRT

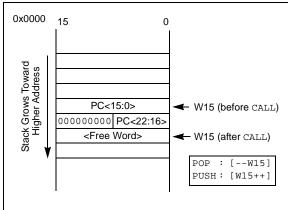

The on-chip regulator has a BOR circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses the VBOR threshold and the delay, TBOR, has elapsed. The delay, TBOR, ensures the voltage regulator output becomes stable.

The Brown-out Reset (BOR) status bit in the Reset Control (RCON<1>) register is set to indicate the Brown-out Reset.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The Power-up Timer (PWRT) provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

Refer to **Section 23.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The Reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point.

#### FIGURE 6-3: BROWN-OUT RESET SITUATIONS

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit             |

|-------|----------------------------------------------------|

|       | 1 = Address error trap has occurred                |

|       | 0 = Address error trap has not occurred            |

| bit 2 | STKERR: Stack Error Trap Status bit                |

|       | 1 = Stack error trap has occurred                  |

|       | 0 = Stack error trap has not occurred              |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit |

|       | 1 = Oscillator failure trap has occurred           |

|       | 0 = Oscillator failure trap has not occurred       |

| bit 0 | Unimplemented: Read as '0'                         |

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| U-0                                  | U-0                                                             | R/W-0            | U-0           | U-0                                      | U-0              | U-0      | U-0                    |  |

|--------------------------------------|-----------------------------------------------------------------|------------------|---------------|------------------------------------------|------------------|----------|------------------------|--|

| —                                    |                                                                 | CTMUIE           | —             | —                                        | —                | —        | —                      |  |

| bit 15                               |                                                                 |                  |               |                                          |                  |          | bit 8                  |  |

|                                      |                                                                 |                  |               |                                          |                  |          |                        |  |

| U-0                                  | U-0                                                             | U-0              | U-0           | U-0                                      | U-0              | R/W-0    | R/W-0                  |  |

|                                      |                                                                 |                  | —             | —                                        | —                | U1EIE    | FLTB1IE <sup>(1)</sup> |  |

| bit 7                                |                                                                 |                  |               |                                          |                  |          | bit 0                  |  |

|                                      |                                                                 |                  |               |                                          |                  |          |                        |  |

| Legend:                              |                                                                 |                  |               |                                          |                  |          |                        |  |

| R = Readable b                       | bit                                                             | W = Writable     | bit           | U = Unimpler                             | mented bit, read | l as '0' |                        |  |

| -n = Value at P                      | OR                                                              | '1' = Bit is set |               | 0' = Bit is cleared $x = Bit is unknown$ |                  |          | nown                   |  |

|                                      |                                                                 |                  |               |                                          |                  |          |                        |  |

| bit 15-14                            | Unimplemen                                                      | ted: Read as '   | 0'            |                                          |                  |          |                        |  |

| bit 13                               | CTMUIE: CTM                                                     | MU Interrupt Er  | nable bit     |                                          |                  |          |                        |  |

|                                      |                                                                 | request is enab  |               |                                          |                  |          |                        |  |

|                                      | -                                                               | request is not e |               |                                          |                  |          |                        |  |

| bit 12-2                             | Unimplemen                                                      | ted: Read as '   | 0'            |                                          |                  |          |                        |  |

| bit 1                                | <b>U1EIE:</b> UART                                              | 1 Error Interru  | pt Enable bit |                                          |                  |          |                        |  |

|                                      | 1 = Interrupt request is enabled                                |                  |               |                                          |                  |          |                        |  |

| 0 = Interrupt request is not enabled |                                                                 |                  |               |                                          |                  |          |                        |  |

| bit 0                                | bit 0 FLTB1IE: PWM1 Fault B Interrupt Enable bit <sup>(1)</sup> |                  |               |                                          |                  |          |                        |  |

|                                      | •                                                               | request has occ  |               |                                          |                  |          |                        |  |

|                                      | 0 = Interrupt r                                                 | request has not  | occurred      |                                          |                  |          |                        |  |

| Note 1: This                         | bit is available                                                | e in dsPIC(16/3  | 2)MC102/104   | devices only.                            |                  |          |                        |  |

#### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

#### 9.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 9.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

#### 9.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

#### 9.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this may not be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the UART module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the UART module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 9.4 Peripheral Module Disable

The Peripheral Module Disable (PMDx) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMDx control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is enabled only if both the associated bit in the PMDx register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMDx register by default.

**Note:** If a PMDx bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMDx bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

#### **PMD Control Registers** 9.5

| R/W-0       U-0       R/W-0       U-0       R/W-0       U-0       R/W-0         I2C1MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0               | R/W-0               | R/W-0            | R/W-0                  | R/W-0          | U-0            | R/W-0     | U-0                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|------------------|------------------------|----------------|----------------|-----------|----------------------|

| R/W-0       U-0       R/W-0       U-0       R/W-0       U-0       R/W-0         I2C1MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | T5MD <sup>(1)</sup> | T4MD <sup>(1)</sup> | T3MD             | T2MD                   | T1MD           | _              | PWM1MD    | _                    |

| I2C1MD       -       U1MD       -       SPI1MD       -       AD1MDf2         bit 7       bit       -       bit       bit       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       nn = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is disabled       0 = Timer7 module is disabled         bit 14       T4MD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer7 module is disabled       0 = Timer7 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is enabled         bit 14       T4MD: Timer2 Module Disable bit       1 = Timer2 module is enabled       0 = Timer7 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled         bit 11       Timer1 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15              | •                   |                  | 1                      |                |                |           | bit                  |

| I2C1MD       -       U1MD       -       SPI1MD       -       AD1MDf2         bit 7       bit       -       bit       bit       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       nn = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is disabled       0 = Timer7 module is disabled         bit 14       T4MD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer7 module is disabled       0 = Timer7 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is enabled         bit 14       T4MD: Timer2 Module Disable bit       1 = Timer2 module is enabled       0 = Timer7 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 11       Timer2 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled         bit 11       Timer1 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled       0 = Timer4 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                     |                  |                        |                |                |           |                      |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 T5MD: Timer5 Module Disable bit <sup>(1)</sup><br>1 = Timer5 module is enabled<br>0 = Timer5 module is enabled<br>0 = Timer4 module is enabled<br>0 = Timer4 module is disabled<br>0 = Timer3 module is enabled<br>0 = Timer3 module is enabled<br>0 = Timer4 module Disable bit<br>1 = Timer2 Module Disable bit<br>1 = Timer2 Module Disable bit<br>1 = Timer2 module is disabled<br>0 = Timer4 module is enabled<br>0 = Timer7 module is enabled<br>0 = Timer7 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer1 module is disabled<br>0 = UART1 modul | R/W-0               | U-0                 | R/W-0            | U-0                    | R/W-0          | U-0            | U-0       | R/W-0                |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>in = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 T5MD: Timer5 Module Disable bit <sup>(1)</sup><br>1 = Timer5 module is disabled<br>0 = Timer5 module is disabled<br>0 = Timer4 module is disabled<br>0 = Timer4 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is enabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer3 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is enabled<br>0 = Timer2 module is enabled<br>0 = Timer1 module is disabled<br>0 = Timer1 module is disabled<br>0 = Timer2 module is disabled<br>0 = Timer2 module is enabled<br>0 = Timer4 module is disabled<br>0 = UXM11 module is disabled<br>0 = UXM11 module is disabled<br>0 = UART1 module is disabled<br>0 = UART4 module i | I2C1MD              |                     | U1MD             |                        | SPI1MD         | _              | —         | AD1MD <sup>(2)</sup> |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         Dit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is enabled         0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 14       T4MD: Timer6 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is disabled         Dit 12       T2MD: Timer1 Module Disable bit       1 = Timer2 module is disabled       0 = Timer2 module is disabled         Dit 11       T1MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer4 module is disabled         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 11       T1MD: PWM1 Module Disable bit       1 = PWM1 module is disabled       0 = PWM1 module is disabled       0         Dit 10       Unimplemented: Read as '0'       0       0       0       0       0         Dit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 7               |                     |                  |                        |                |                |           | bit                  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         Dit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer6 module is enabled         0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 14       T4MD: Timer6 Module Disable bit <sup>(1)</sup> 1 = Timer6 module is enabled       0 = Timer6 module is enabled         Dit 13       T3MD: Timer3 Module Disable bit       1 = Timer7 module is disabled       0 = Timer7 module is disabled         Dit 12       T2MD: Timer1 Module Disable bit       1 = Timer2 module is disabled       0 = Timer2 module is disabled         Dit 11       T1MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer4 module is disabled         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 10       Unimplemented: Read as '0'       0       0       0         Dit 11       T1MD: PWM1 Module Disable bit       1 = PWM1 module is disabled       0 = PWM1 module is disabled       0         Dit 10       Unimplemented: Read as '0'       0       0       0       0       0         Dit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Legend:             |                     |                  |                        |                |                |           |                      |

| m = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       TSMD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled       0 = Timer5 module is disabled         bit 14       TAMD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer4 module is disabled       0 = Timer4 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer3 module is disabled       0 = Timer3 module is disabled         bit 13       T3MD: Timer3 Module Disable bit       1 = Timer3 module is disabled       0 = Timer3 module is disabled         bit 12       T2MD: Timer2 Module Disable bit       1 = Timer3 module is disabled       0 = Timer3 module is disabled         bit 12       T2MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 11       T1MD: Timer1 Module Disable bit       1 = Timer1 module is disabled       0 = Timer1 module is disabled         bit 10       Unimplemented: Read as '0'       0       0       0         bit 8       Unimplemented: Read as '0'       0       1 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 7       I2C1MD: I2C1 Module Disable bit       1 = I2C1 module is disabled       0 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 6       Unimplemented: Read as '0'       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                   | le bit              | W = Writable     | bit                    | U = Unimplem   | ented bit, rea | ad as '0' |                      |

| bit 15       T5MD: Timer5 Module Disable bit <sup>(1)</sup> 1 = Timer5 module is disabled         0 = Timer5 module is disabled         1 = Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer4 module is disabled         0 = Timer4 module is disabled         0 = Timer4 module is disabled         0 = Timer3 module is disabled         0 = Timer3 module is disabled         0 = Timer3 module is enabled         0 = Timer3 module is disabled         0 = Timer1 module Disable bit         1 = Timer1 module is disabled         0 = WM1MD: PVM1 Module Disable bit         1 = PWM1 module is disabled         0 = PVWM1 module is disabled         0 = PVW1 module is disabled         0 = VIM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -n = Value a        | t POR               | '1' = Bit is set | t                      | •              |                |           | nown                 |

| 1 = Timer5 module is disabled         0 = Timer5 module is enabled         0 = Timer4 Module Disable bit         1 = Timer4 module is enabled         0 = Timer4 module is enabled         0 = Timer3 module is enabled         0 = Timer3 module is disable bit         1 = Timer3 module is disabled         0 = Timer2 module is enabled         0 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 module is disabled         0 = PWM1 MD: PWM1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is enabled         0 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module Disable bit         1 = UART1 module is disabled         0 = UART1 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                     |                  |                        |                |                |           |                      |

| 0 = Timer5 module is enabled         bit 14       T4MD: Timer4 Module Disable bit         1 = Timer4 module is disabled         0 = Timer3 Module Disable bit         1 = Timer3 module is enabled         0 = Timer4 module is disabled         0 = Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer2 module is enabled         0 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWM1 module is disabled         0 = I2C1 Module Disable bit         1 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 15              | T5MD: Time          | r5 Module Disa   | ble bit <sup>(1)</sup> |                |                |           |                      |

| bit 14       T4MD: Timer4 Module Disable bit <sup>(1)</sup> 1 = Timer4 module is disabled         0 = Timer4 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer1 module is disabled         0 = PWM1 module is disabled         0 = I2C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is disabled         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     | 1 = Timer5 n        | nodule is disabl | ed                     |                |                |           |                      |

| 1 = Timer4 module is disabled         0 = Timer4 module is enabled         0 = Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer3 module is enabled         0 = Timer3 module is enabled         0 = Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is disabled         0 = Timer2 module is enabled         0 = Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWM1 module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module Disable bit         1 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled         0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     | 0 <b>= Timer5 n</b> | nodule is enable | ed                     |                |                |           |                      |

| 0 = Timer4 module is enabled         bit 13       T3MD: Timer3 Module Disable bit         1 = Timer3 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is enabled         0 = Timer3 module is enabled         0 = Timer2 module is enabled         0 = Timer2 module is enabled         0 = Timer1 module is disabled         0 = PWM1MD: PVW1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PUM1 module is disabled         0 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = 12C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled         0 = UART1 module is enabled         0 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14              |                     |                  |                        |                |                |           |                      |

| bit 13       T3MD: Timer3 Module Disable bit         1 = Timer3 module is disabled       0 = Timer3 module is enabled         0 = Timer3 module is enabled       0 = Timer2 Module Disable bit         1 = Timer2 module is disabled       0 = Timer2 module is enabled         0 = Timer2 module is disabled       0 = Timer2 module is disabled         0 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is disabled       0 = PWM1 MD: PWM1 Module Disable bit         1 = PWM1 module is disabled       0 = PWM1 module is disabled         0 = PWM1 module is disabled       0 = PWM1 module is enabled         0 = PWM1 module is disabled       0 = PUM1 module is disabled         0 = PWM1 module is disabled       0 = I2C1 module is disabled         0 = I2C1 module is disabled       0 = I2C1 module is enabled         0 = I2C1 module is disabled       0 = I2C1 module is disabled         0 = UART1 module is disabled       0 = UART1 module is disabled         0 = UART1 module is disabled       0 = UART1 module is disabled         0 = UART1 module is disabled       0 = UART1 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                     |                  |                        |                |                |           |                      |

| 1 = Timer3 module is disabled         0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is enabled         bit 11       T1MD: Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = Timer1 module is disabled         0 = Timer1 module is enabled         0 = Timer1 module is disabled         0 = Timer1 module is enabled         0 = Timer1 module is enabled         0 = Timer1 module is disabled         0 = Timer1 module is enabled         0 = Timer1 module is disabled         0 = PWM1MD: PWM1 Module Disable bit         1 = PVWM1 module is enabled         0 = PWM1 module is enabled         0 = PWM1 module is enabled         0 = VATI module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module is disabled         0 = I2C1 module is disabled         0 = UART1 module is disabled         0 = UART1 module is enabled         0 = UART1 module is enabled         0 = UART1 modu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | h:: 40              |                     |                  |                        |                |                |           |                      |

| 0 = Timer3 module is enabled         bit 12       T2MD: Timer2 Module Disable bit         1 = Timer2 module is disabled         0 = Timer2 module is enabled         bit 11       T1MD: Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = PWM1 MD: PWM1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module is disabled         0 = PWM1 module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is enabled         0 = I2C1 module is disabled         0 = I2C1 module Disable bit         1 = UART1 Module Disable bit         1 = UART1 module is disabled         0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DIT 13              |                     |                  |                        |                |                |           |                      |

| bit 12 <b>T2MD</b> : Timer2 Module Disable bit         1 = Timer2 module is disabled       0 = Timer2 module is enabled         bit 11 <b>T1MD</b> : Timer1 Module Disable bit         1 = Timer1 module is disabled       0 = Timer1 module is disabled         0 = Timer1 module is enabled       0 = Timer1 module is disabled         0 = Timer1 module is enabled       0 = Timer1 module is enabled         bit 10 <b>Unimplemented:</b> Read as '0'         bit 3 <b>PWM1MD</b> : PWM1 Module Disable bit         1 = PWM1 module is enabled       0 = PWM1 module is enabled         bit 4 <b>Unimplemented:</b> Read as '0'         bit 5 <b>Unimplemented:</b> Read as '0'         bit 6 <b>Unimplemented:</b> Read as '0'         bit 7 <b>I2C1MD</b> : I2C1 Module Disable bit         1 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 6 <b>Unimplemented:</b> Read as '0'         bit 5 <b>U1MD</b> : UART1 Module Disable bit         1 = UART1 module is disabled       0 = UART1 module is enabled         bit 4 <b>Unimplemented:</b> Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |                     |                  |                        |                |                |           |                      |

| 1 = Timer2 module is disabled         0 = Timer2 module is enabled         bit 11       T1MD: Timer1 Module Disable bit         1 = Timer1 module is disabled         0 = Timer1 module is enabled         bit 10       Unimplemented: Read as '0'         bit 9       PWM1MD: PWM1 Module Disable bit         1 = PWM1 module is disabled       0 = PWM1 module is disabled         0 = PWM1 module is disabled       0 = PWM1 module is enabled         bit 8       Unimplemented: Read as '0'         bit 7       I2C1 Module Disable bit         1 = I2C1 module is disabled       0 = I2C1 module is disabled         0 = I2C1 module is disabled       0 = I2C1 module is disabled         bit 6       Unimplemented: Read as '0'         bit 5       U1MD: UART1 Module Disable bit         1 = UART1 module is disabled       0 = UART1 module is enabled         0 = UART1 module is enabled       0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 12              | T2MD: Time          | r2 Module Disa   | ble bit                |                |                |           |                      |

| bit 11 <b>T1MD:</b> Timer1 Module Disable bit<br>$1 = Timer1$ module is disabled<br>$0 = Timer1$ module is enabledbit 10 <b>Unimplemented:</b> Read as '0'bit 9 <b>PWM1MD:</b> PWM1 Module Disable bit<br>$1 = PWM1$ module is disabled<br>$0 = PWM1$ module is enabledbit 8 <b>Unimplemented:</b> Read as '0'bit 7 <b>I2C1MD:</b> I2C1 Module Disable bit<br>$1 = I2C1$ module is disabled<br>$0 = I2C1$ module is enabledbit 6 <b>Unimplemented:</b> Read as '0'bit 5 <b>U1MD:</b> UART1 Module Disable bit<br>$1 = UART1$ module is disabled<br>$0 = UART1$ module is disabled<br>bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | 1 = Timer2 n        | nodule is disabl | ed                     |                |                |           |                      |

| 1 = Timer1 module is disabled         0 = Timer1 module is enabled         0 = Timer1 module is enabled         0 = Timer1 module is enabled         0 = PWM1MD: PWM1 Module Disable bit         1 = PWM1 module is disabled         0 = PWM1 module is enabled         0 = I2C1 Module Disable bit         1 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = I2C1 module is disabled         0 = I2C1 module is enabled         0 = UART1 Module Disable bit         1 = UART1 module is disabled         0 = UART1 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     | 0 = Timer2 n        | nodule is enable | ed                     |                |                |           |                      |

| 0 = Timer1 module is enabled         bit 10       Unimplemented: Read as '0'         bit 9       PWM1MD: PWM1 Module Disable bit         1 = PWM1 module is disabled       0 = PWM1 module is disabled         0 = PWM1 module is enabled       0 = PWM1 module is enabled         bit 8       Unimplemented: Read as '0'         bit 7       I2C1MD: I2C1 Module Disable bit         1 = I2C1 module is disabled       0 = I2C1 module is enabled         0 = I2C1 module is enabled       0 = I2C1 module is enabled         bit 6       Unimplemented: Read as '0'         bit 5       U1MD: UART1 Module Disable bit         1 = UART1 module is disabled       0 = UART1 module is enabled         bit 4       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 11              | T1MD: Time          | r1 Module Disa   | ble bit                |                |                |           |                      |

| bit 10       Unimplemented: Read as '0'         bit 9       PWM1MD: PWM1 Module Disable bit         1 = PWM1 module is disabled       0 = PWM1 module is enabled         bit 8       Unimplemented: Read as '0'         bit 7       I2C1MD: I2C1 Module Disable bit         1 = I2C1 module is disabled       0 = I2C1 module is disabled         0 = I2C1 module is enabled       0 = I2C1 module is enabled         bit 6       Unimplemented: Read as '0'         bit 5       U1MD: UART1 Module Disable bit         1 = UART1 module is disabled       0 = UART1 module is enabled         bit 4       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                     |                  |                        |                |                |           |                      |

| bit 9PWM1MD: PWM1 Module Disable bit1 = PWM1 module is disabled<br>0 = PWM1 module is enabledbit 8Unimplemented: Read as '0'bit 7I2C1MD: I2C1 Module Disable bit<br>1 = I2C1 module is disabled<br>0 = I2C1 module is enabledbit 6Unimplemented: Read as '0'bit 5U1MD: UART1 Module Disable bit<br>1 = UART1 module is disabled<br>0 = UART1 module is enabledbit 4Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |                     |                  |                        |                |                |           |                      |

| 1 = PWM1 module is disabled<br>$0 = PWM1$ module is enabledbit 8Unimplemented: Read as '0'bit 7I2C1MD: I2C1 Module Disable bit<br>$1 = I2C1$ module is disabled<br>$0 = I2C1$ module is enabledbit 6Unimplemented: Read as '0'bit 5U1MD: UART1 Module Disable bit<br>$1 = UART1$ module is disabled<br>$0 = UART1$ module is enabledbit 4Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     | -                   |                  |                        |                |                |           |                      |