#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 15                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 20-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc101-e-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

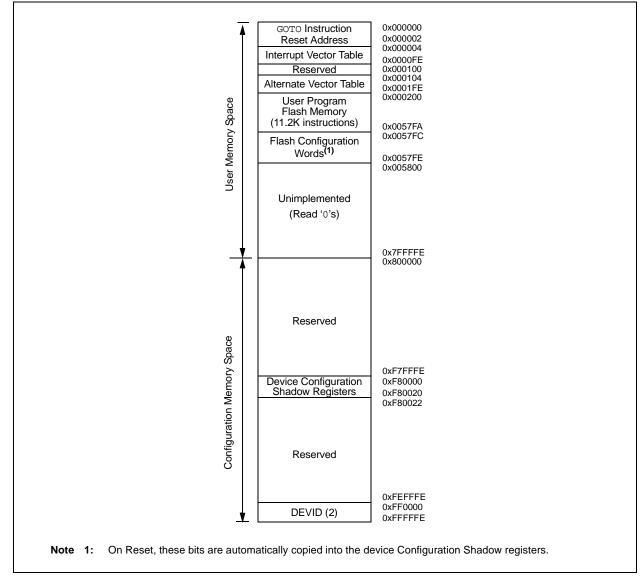

# FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPIC33FJ32(GP/MC)101/102/104 DEVICES

# TABLE 4-12: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                      | Bit 8                          | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|----------------------------|--------------------------------|-------|-------|-------|------------|--------------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       | _      |         | _      |        |        | _                          | – I2C1 Receive Register        |       |       |       |            |              |       | 0000  |       |               |

| I2C1TRN  | 0202        | _       | _      | _       | —      | _      | _      | _                          | _                              |       |       |       | I2C1 Trans | mit Register | •     |       |       | 00FF          |

| I2C1BRG  | 0204        | _       | _      | _       | —      | _      | _      | _                          | - Baud Rate Generator Register |       |       |       |            |              | 0000  |       |       |               |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                     | SMEN                           | GCEN  | STREN | ACKDT | ACKEN      | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                     | ADD10                          | IWCOL | I2COV | D_A   | Р          | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       |        | _       | _      | _      | _      | I2C1 Address Register      |                                |       |       |       |            | 0000         |       |       |       |               |

| I2C1MSK  | 020C        | —       | _      | _       | _      | _      |        | I2C1 Address Mask Register |                                |       |       |       |            | 0000         |       |       |       |               |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-13: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15                        | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7    | Bit 6    | Bit 5 | Bit 4      | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|-------------------------------|--------|----------|--------|--------|--------|-------|------------------------|----------|----------|-------|------------|---------|--------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN                        | _      | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0                   | WAKE     | LPBACK   | ABAUD | URXINV     | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1                      | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXISEL1 | URXISEL0 | ADDEN | RIDLE      | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _                             | _      | -        | _      | _      | _      |       |                        |          |          | UART1 | Transmit R | egister |        |        |       | xxxx          |

| U1RXREG  | 0226        | _                             | _      | -        | _      | _      | _      |       | UART1 Receive Register |          |          |       |            |         | 0000   |        |       |               |

| U1BRG    | 0228        | Baud Rate Generator Prescaler |        |          |        |        |        |       |                        |          |          | 0000  |            |         |        |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: SPI1 REGISTER MAP

|          |             | •••••• |                                             |         |        |        |        |       |       |       | -      |       |       |       |       | -      |        |               |

|----------|-------------|--------|---------------------------------------------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|-------|--------|--------|---------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                                      | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

| SPI1STAT | 0240        | SPIEN  | _                                           | SPISIDL | _      | _      | _      |       |       |       | SPIROV | _     | _     | _     |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242        | _      | _                                           | _       | DISSCK | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000          |

| SPI1CON2 | 0244        | FRMEN  | SPIFSD                                      | FRMPOL  | _      | _      | _      | _     | _     | _     | _      | _     |       | -     | _     | FRMDLY | _      | 0000          |

| SPI1BUF  | 0248        |        | SPI1 Transmit and Receive Buffer Register 0 |         |        |        |        |       |       |       | 0000   |       |       |       |       |        |        |               |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 5.2 RTSP Operation

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions); and to program one word. Table 26-12 shows typical erase and programming times. The 8-row erase pages are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes.

# 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the operation is finished.

The programming time depends on the FRC accuracy (see Table 26-18) and the value of the FRC Oscillator Tuning register (see Register 8-3). Use the following formula to calculate the minimum and maximum values for the Word write time and page erase time (see Parameters D138a and D138b, and Parameters D137a and D137b in Table 26-12, respectively).

#### EQUATION 5-1: PROGRAMMING TIME

$\frac{T}{7.37 \text{ MHz} \times (FRC \text{ Accuracy})\% \times (FRC \text{ Tuning})\%}$

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 2\%$ . If the TUN<5:0> bits (see Register 8-3) are set to `b000000, the minimum row write time is equal to Equation 5-2.

#### EQUATION 5-2: MINIMUM ROW WRITE TIME

$T_{RW} = \frac{355 \ Cycles}{7.37 \ MHz \times (1 + 0.02) \times (1 - 0.00375)} = 47.4 \mu s$

The maximum row write time is equal to Equation 5-3.

# EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{355 \ Cycles}{7.37 \ MHz \times (1 - 0.02) \times (1 - 0.00375)} = 49.3 \mu s$$

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program one word (24 bits) of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

| Note: | Performing a page erase operation on the   |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | last page of program memory will clear the |  |  |  |  |  |  |  |  |

|       | Flash Configuration Words, thereby         |  |  |  |  |  |  |  |  |

|       | enabling code protection as a result.      |  |  |  |  |  |  |  |  |

|       | Therefore, users should avoid performing   |  |  |  |  |  |  |  |  |

|       | page erase operations on the last page of  |  |  |  |  |  |  |  |  |

|       | program memory.                            |  |  |  |  |  |  |  |  |

Refer to **"Flash Programming"** (DS70191) in the *"dsPIC33/PIC24 Family Reference Manual"* for details and codes examples on programming using RTSP.

# 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

|                  | R/W-1                                                                                  | R/W-0                                                                          | R/W-0                                              | U-0                | R/W-1            | R/W-0           | R/W-0  |

|------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------|--------------------|------------------|-----------------|--------|

| _                | T2IP2                                                                                  | T2IP1                                                                          | T2IP0                                              |                    | OC2IP2           | OC2IP1          | OC2IP0 |

| bit 15           |                                                                                        |                                                                                |                                                    |                    |                  |                 | bit 8  |

|                  |                                                                                        |                                                                                |                                                    |                    |                  |                 |        |

| U-0              | R/W-1                                                                                  | R/W-0                                                                          | R/W-0                                              | U-0                | U-0              | U-0             | U-0    |

| _                | IC2IP2                                                                                 | IC2IP1                                                                         | IC2IP0                                             |                    | —                |                 | —      |

| bit 7            |                                                                                        |                                                                                |                                                    |                    |                  |                 | bit    |

| Legend:          |                                                                                        |                                                                                |                                                    |                    |                  |                 |        |

| R = Readab       | le bit                                                                                 | W = Writable                                                                   | bit                                                | U = Unimplen       | nented bit, read | l as '0'        |        |

| -n = Value a     | t POR                                                                                  | '1' = Bit is set                                                               |                                                    | '0' = Bit is cle   |                  | x = Bit is unkr | nown   |

|                  |                                                                                        |                                                                                |                                                    |                    |                  |                 |        |

| bit 15           | Unimplemer                                                                             | nted: Read as '                                                                | 0'                                                 |                    |                  |                 |        |

| bit 14-12        | T2IP<2:0>: 7                                                                           | Fimer2 Interrupt                                                               | Priority bits                                      |                    |                  |                 |        |

|                  | 111 = Interru                                                                          | pt is Priority 7 (                                                             | highest priori                                     | ty interrupt)      |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |

|                  |                                                                                        | ipt is Priority 1<br>ipt source is dis                                         | abled                                              |                    |                  |                 |        |

| bit 11           |                                                                                        | h <b>ted:</b> Read as '                                                        |                                                    |                    |                  |                 |        |

| bit 10-8         | -                                                                                      | : Output Compa                                                                 |                                                    | Interrupt Priori   | ty bits          |                 |        |

|                  |                                                                                        | pt is Priority 7 (                                                             |                                                    | -                  |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |

|                  | 001 = Interr                                                                           | int is Priority 1                                                              |                                                    |                    |                  |                 |        |

|                  |                                                                                        | ipt is Priority 1<br>ipt source is dis                                         | abled                                              |                    |                  |                 |        |

| bit 7            | 000 = Interru                                                                          | ipt is Priority 1<br>ipt source is dis<br>nted: Read as '                      |                                                    |                    |                  |                 |        |

|                  | 000 = Interru<br>Unimplemer                                                            | ipt source is dis<br>nted: Read as '                                           | 0'                                                 | errupt Priority bi | its              |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '<br>Input Capture (                        | 0'<br>Channel 2 Inte                               |                    | its              |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '                                           | 0'<br>Channel 2 Inte                               |                    | its              |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '<br>Input Capture (                        | 0'<br>Channel 2 Inte                               |                    | its              |                 |        |

|                  | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru<br>•<br>•                  | ipt source is dis<br>nted: Read as '<br>Input Capture C<br>ipt is Priority 7 ( | 0'<br>Channel 2 Inte                               |                    | its              |                 |        |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru | ipt source is dis<br>nted: Read as '<br>Input Capture (                        | <sup>0'</sup><br>Channel 2 Inte<br>highest priorit |                    | its              |                 |        |

## REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| U-0          | R/W-1                                         | R/W-0                                | R/W-0                 | U-0              | R/W-1             | R/W-0           | R/W-0    |  |  |  |  |  |  |

|--------------|-----------------------------------------------|--------------------------------------|-----------------------|------------------|-------------------|-----------------|----------|--|--|--|--|--|--|

| —            | CNIP2                                         | CNIP1                                | CNIP0                 | —                | CMIP2             | CMIP1           | CMIP0    |  |  |  |  |  |  |

| bit 15       |                                               |                                      |                       |                  |                   |                 | bit      |  |  |  |  |  |  |

|              | <b>D A A A</b>                                | <b>D</b> 444 o                       | <b>D M</b> ( <b>a</b> |                  | <b>D</b> 444 4    | <b>D</b> 444 o  |          |  |  |  |  |  |  |

| U-0          | R/W-1                                         | R/W-0                                | R/W-0                 | U-0              | R/W-1             | R/W-0           | R/W-0    |  |  |  |  |  |  |

|              | MI2C1IP2                                      | MI2C1IP1                             | MI2C1IP0              | —                | SI2C1IP2          | SI2C1IP1        | SI2C1IP0 |  |  |  |  |  |  |

| bit 7        |                                               |                                      |                       |                  |                   |                 | bit      |  |  |  |  |  |  |

| Legend:      |                                               |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

| R = Readab   | le bit                                        | W = Writable                         | bit                   | U = Unimple      | emented bit, read | d as '0'        |          |  |  |  |  |  |  |

| -n = Value a | t POR                                         | '1' = Bit is set                     |                       | '0' = Bit is cl  | eared             | x = Bit is unkr | nown     |  |  |  |  |  |  |

|              |                                               |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

| bit 15       | -                                             | ted: Read as '                       |                       |                  |                   |                 |          |  |  |  |  |  |  |

| bit 14-12    |                                               | Change Notifica                      |                       | -                |                   |                 |          |  |  |  |  |  |  |

|              | 111 = Interru                                 | pt is Priority 7 (                   | highest priorit       | y interrupt)     |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •                                             | •                                    |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | 001 = Interru                                 | pt is Priority 1                     |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | 000 = Interru                                 | pt source is dis                     | abled                 |                  |                   |                 |          |  |  |  |  |  |  |

| bit 11       | Unimplemen                                    | ted: Read as '                       | 0'                    |                  |                   |                 |          |  |  |  |  |  |  |

| bit 10-8     | CMIP<2:0>: Comparator Interrupt Priority bits |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | 111 = Interru                                 | pt is Priority 7 (                   | highest priorit       | y interrupt)     |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | 001 = Interru                                 | pt is Priority 1                     |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              |                                               | pt source is dis                     | abled                 |                  |                   |                 |          |  |  |  |  |  |  |

| bit 7        |                                               | Ited: Read as '                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

| bit 6-4      | -                                             | >: I2C1 Master                       |                       | upt Priority bi  | ts                |                 |          |  |  |  |  |  |  |

|              |                                               | pt is Priority 7 (                   |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •                                             | . ,                                  |                       | , i ,            |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •<br>001 = Interru                            | nt in Priority 1                     |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              |                                               | pt is Fliolity 1<br>pt source is dis | abled                 |                  |                   |                 |          |  |  |  |  |  |  |

| bit 3        |                                               | ited: Read as '                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

| bit 2-0      | -                                             | >: I2C1 Slave E                      |                       | ot Priority bits |                   |                 |          |  |  |  |  |  |  |

|              |                                               | pt is Priority 7 (                   | -                     | -                |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •                                             |                                      |                       |                  |                   |                 |          |  |  |  |  |  |  |

|              | •<br>•<br>001 = Interru                       | pt is Prioritv 1                     |                       |                  |                   |                 |          |  |  |  |  |  |  |

# REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| REGISTER     | (8-3: 050  | IUN: FRC 05                                              | GILLATOR    | IUNING REG                         | ISIEK   |                 |       |  |  |

|--------------|------------|----------------------------------------------------------|-------------|------------------------------------|---------|-----------------|-------|--|--|

| U-0          | U-0        | U-0                                                      | U-0         | U-0                                | U-0     | U-0             | U-0   |  |  |

| _            | _          | —                                                        | _           | _                                  | —       | —               | _     |  |  |

| bit 15       |            |                                                          |             |                                    |         | ·               | bit   |  |  |

|              |            |                                                          |             |                                    |         |                 |       |  |  |

| U-0          | U-0        | R/W-0                                                    | R/W-0       | R/W-0                              | R/W-0   | R/W-0           | R/W-0 |  |  |

| _            | —          |                                                          |             | TUN                                | N<5:0>  |                 |       |  |  |

| bit 7        |            |                                                          |             |                                    |         |                 | bit ( |  |  |

|              |            |                                                          |             |                                    |         |                 |       |  |  |

| Legend:      |            |                                                          |             |                                    |         |                 |       |  |  |

| R = Readab   | ole bit    | W = Writable                                             | bit         | U = Unimplemented bit, read as '0' |         |                 |       |  |  |

| -n = Value a | at POR     | '1' = Bit is set                                         |             | '0' = Bit is cle                   | ared    | x = Bit is unkı | nown  |  |  |

|              |            |                                                          |             |                                    |         |                 |       |  |  |

| bit 15-6     | Unimpleme  | ented: Read as '                                         | 0'          |                                    |         |                 |       |  |  |

| bit 5-0      | TUN<5:0>:  | FRC Oscillator T                                         | uning bits  |                                    |         |                 |       |  |  |

|              |            | Aaximum frequer<br>Center frequency                      |             |                                    | 77 MHz) |                 |       |  |  |

|              | •          |                                                          |             |                                    |         |                 |       |  |  |

|              | •          |                                                          |             |                                    |         |                 |       |  |  |

|              | •          |                                                          |             |                                    |         |                 |       |  |  |

|              | 000000 = 0 | Center frequency<br>Center frequency<br>Center frequency | (7.37 MHz n | ominal)                            |         |                 |       |  |  |

|              | •          |                                                          |             |                                    |         |                 |       |  |  |

### REGISTER 8-3: OSCTUN: FRC OSCILLATOR TUNING REGISTER

• 100001 = Center frequency – 1.453% (7.263 MHz) 100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

•

# 10.4.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

#### 10.4.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |

|-------|--------------------------------------------------------------------------------------------------|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                     |

|       | See MPLAB IDE Help for more information.                                                         |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

#### 10.4.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

#### 10.4.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| U-0           | U-0           | U-0              | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|---------------|---------------|------------------|----------------|------------------|-----------------|-----------------|-------|

| —             | —             | —                |                |                  | RP1R<4:0>       |                 |       |

| bit 15        |               |                  |                |                  |                 |                 | bit 8 |

|               |               |                  |                |                  |                 |                 |       |

| U-0           | U-0           | U-0              | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| _             | —             | —                |                |                  | RP0R<4:0>       |                 |       |

| bit 7         |               |                  |                |                  |                 |                 | bit 0 |

|               |               |                  |                |                  |                 |                 |       |

| Legend:       |               |                  |                |                  |                 |                 |       |

| R = Readable  | e bit         | W = Writable     | bit            | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at | POR           | '1' = Bit is set |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|               |               |                  |                |                  |                 |                 |       |

| bit 15-13     | Unimplemen    | ted: Read as '   | 0'             |                  |                 |                 |       |

| bit 12-8      | RP1R<4:0>:    | Peripheral Outp  | out Function   | is Assigned to F | RP1 Output Pir  | n bits          |       |

|               | (see Table 10 | -2 for periphera | al function nu | mbers)           |                 |                 |       |

|               |               |                  |                |                  |                 |                 |       |

#### REGISTER 10-11: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| bit 4-0 | <b>RP0R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP0 Output Pin bits |

|---------|---------------------------------------------------------------------------------------|

|         | (see Table 10-2 for peripheral function numbers)                                      |

Unimplemented: Read as '0'

#### REGISTER 10-12: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|--------------------------|-------|-------|

| —      | —   | —   |       |       | RP3R<4:0> <sup>(1)</sup> | 1     |       |

| bit 15 |     |     |       |       |                          |       | bit 8 |

|        |     |     |       |       |                          |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|        |     |     |       |       | RP2R<4:0> <sup>(1)</sup> |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 12-8  | <b>RP3R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP3 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                                     |

| bit 7-5   | Unimplemented: Read as '0'                                                                           |

| bit 4-0   | <b>RP2R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP2 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                                     |

**Note 1:** These bits are not available in dsPIC33FJXX(GP/MC)101 devices.

bit 7-5

bit 7

bit 0

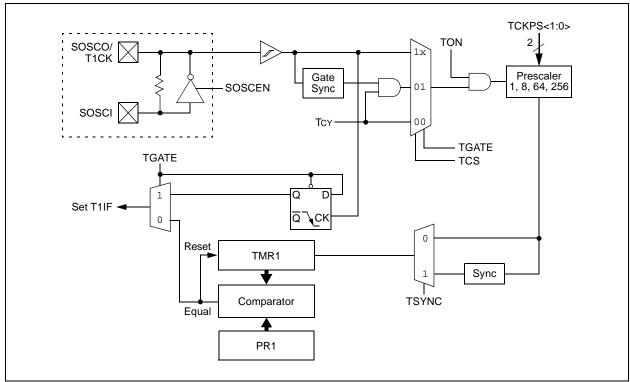

# 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 11-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Load the timer value into the TMR1 register.

- 2. Load the timer period value into the PR1 register.

- 3. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 4. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 5. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

- 7. Set the TON bit (= 1) in the T1CON register.

#### FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

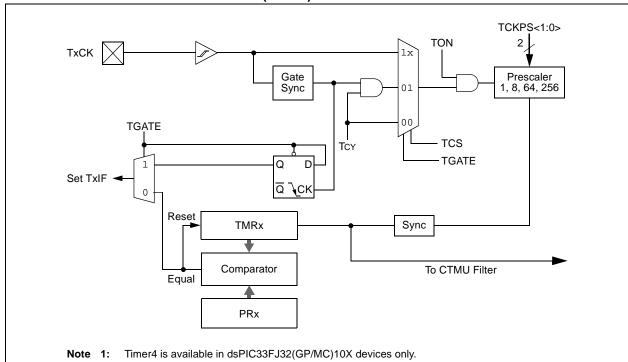

FIGURE 12-2: TIMER2 AND TIMER4 (16-BIT) BLOCK DIAGRAM<sup>(1)</sup>

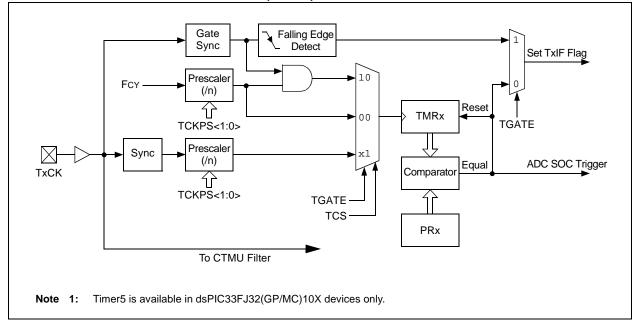

# FIGURE 12-3: TIMER3 AND TIMER5 (16-BIT) BLOCK DIAGRAM<sup>(1)</sup>

NOTES:

# REGISTER 20-4: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

| bit 3 | ABEN: AND Gate A1 B Input Inverted Enable bit                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------|

|       | 1 = MBI is connected to AND gate                                                                                  |

|       | 0 = MBI is not connected to AND gate                                                                              |

| bit 2 | ABNEN: AND Gate A1 B Input Inverted Enable bit                                                                    |

|       | <ul><li>1 = Inverted MBI is connected to AND gate</li><li>0 = Inverted MBI is not connected to AND gate</li></ul> |

| bit 1 | AAEN: AND Gate A1 A Input Enable bit                                                                              |

|       | <ul><li>1 = MAI is connected to AND gate</li><li>0 = MAI is not connected to AND gate</li></ul>                   |

| bit 0 | AANEN: AND Gate A1 A Input Inverted Enable bit                                                                    |

|       | <ul><li>1 = Inverted MAI is connected to AND gate</li><li>0 = Inverted MAI is not connected to AND gate</li></ul> |

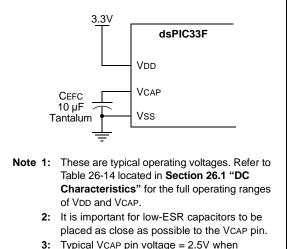

# 23.2 On-Chip Voltage Regulator

All of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 23-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 26-14 located in **Section 26.1** "**DC Characteristics**".

| Note: | It is important for low-ESR capacitors to be |

|-------|----------------------------------------------|

|       | placed as close as possible to the VCAP pin. |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 23-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

**3:** Typical VCAP pin voltage = 2.5V when VDD  $\ge$  VDDMIN.

#### 23.3 BOR: Brown-out Reset

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an Oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

|                    | .E 24-2:             | INSTRU  | ICTION SET OVERVIE         |                                                            |               |                |                          |

|--------------------|----------------------|---------|----------------------------|------------------------------------------------------------|---------------|----------------|--------------------------|

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax            | Description                                                | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

| 9                  | BTG                  | BTG     | f,#bit4                    | Bit Toggle f                                               | 1             | 1              | None                     |

|                    |                      | BTG     | Ws,#bit4                   | Bit Toggle Ws                                              | 1             | 1              | None                     |

| 10                 | BTSC                 | BTSC    | f,#bit4                    | Bit Test f, Skip if Clear                                  | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSC    | Ws,#bit4                   | Bit Test Ws, Skip if Clear                                 | 1             | 1<br>(2 or 3)  | None                     |

| 11                 | BTSS                 | BTSS    | f,#bit4                    | Bit Test f, Skip if Set                                    | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSS    | Ws,#bit4                   | Bit Test Ws, Skip if Set                                   | 1             | 1<br>(2 or 3)  | None                     |

| 12                 | BTST                 | BTST    | f,#bit4                    | Bit Test f                                                 | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,#bit4                   | Bit Test Ws to C                                           | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,#bit4                   | Bit Test Ws to Z                                           | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,Wb                      | Bit Test Ws <wb> to C</wb>                                 | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,Wb                      | Bit Test Ws <wb> to Z</wb>                                 | 1             | 1              | Z                        |

| 13                 | BTSTS                | BTSTS   | f,#bit4                    | Bit Test then Set f                                        | 1             | 1              | Z                        |

|                    |                      | BTSTS.C | Ws,#bit4                   | Bit Test Ws to C, then Set                                 | 1             | 1              | С                        |

|                    |                      | BTSTS.Z | Ws,#bit4                   | Bit Test Ws to Z, then Set                                 | 1             | 1              | Z                        |

| 14                 | CALL                 | CALL    | lit23                      | Call subroutine                                            | 2             | 2              | None                     |

|                    |                      | CALL    | Wn                         | Call indirect subroutine                                   | 1             | 2              | None                     |

| 15                 | CLR                  | CLR     | f                          | f = 0x0000                                                 | 1             | 1              | None                     |

|                    | -                    | CLR     | WREG                       | WREG = 0x0000                                              | 1             | 1              | None                     |

|                    |                      | CLR     | Ws                         | Ws = 0x0000                                                | 1             | 1              | None                     |

|                    |                      | CLR     | Acc, Wx, Wxd, Wy, Wyd, AWB | Clear Accumulator                                          | 1             | 1              | OA,OB,SA,SB              |

| 16                 | CLRWDT               | CLRWDT  |                            | Clear Watchdog Timer                                       | 1             | 1              | WDTO,Sleep               |

| 17                 | COM                  | СОМ     | f                          | $f = \overline{f}$                                         | 1             | 1              | N,Z                      |

| 17                 | COM                  | COM     | f,WREG                     | WREG = Ī                                                   | 1             | 1              | N,Z                      |

|                    |                      |         |                            | $Wd = \overline{Ws}$                                       |               |                | ,                        |

| 40                 |                      | COM     | Ws,Wd                      |                                                            | 1             | 1              | N,Z                      |

| 18                 | CP                   | CP      | f                          | Compare f with WREG                                        | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,#lit5                   | Compare Wb with lit5                                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,Ws                      | Compare Wb with Ws (Wb – Ws)                               | 1             | 1              | C,DC,N,OV,Z              |

| 19                 | CP0                  | CP0     | f                          | Compare f with 0x0000                                      | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPO     | Ws                         | Compare Ws with 0x0000                                     | 1             | 1              | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB     | f                          | Compare f with WREG, with Borrow                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,#lit5                   | Compare Wb with lit5, with Borrow                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,Ws                      | Compare Wb with Ws, with Borrow $(Wb - Ws - \overline{C})$ | 1             | 1              | C,DC,N,OV,Z              |

| 21                 | CPSEQ                | CPSEQ   | Wb, Wn                     | Compare Wb with Wn, skip if =                              | 1             | 1<br>(2 or 3)  | None                     |

| 22                 | CPSGT                | CPSGT   | Wb, Wn                     | Compare Wb with Wn, skip if >                              | 1             | 1<br>(2 or 3)  | None                     |

| 23                 | CPSLT                | CPSLT   | Wb, Wn                     | Compare Wb with Wn, skip if <                              | 1             | 1<br>(2 or 3)  | None                     |

| 24                 | CPSNE                | CPSNE   | Wb, Wn                     | Compare Wb with Wn, skip if $\neq$                         | 1             | 1<br>(2 or 3)  | None                     |

| 25                 | DAW                  | DAW     | Wn                         | Wn = decimal adjust Wn                                     | 1             | 1              | С                        |

| 26                 | DEC                  | DEC     | f                          | f = f - 1                                                  | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC     | f,WREG                     | WREG = f - 1                                               | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC     | Ws,Wd                      | Wd = Ws - 1                                                | 1             | 1              | C,DC,N,OV,Z              |

| 27                 | DEC2                 | DEC2    | f                          | f = f - 2                                                  | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC2    | f,WREG                     | WREG = f - 2                                               | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC2    | Ws,Wd                      | Wd = Ws - 2                                                | 1             | 1              | C,DC,N,OV,Z              |

| 28                 | DISI                 | DISI    | #lit14                     | Disable Interrupts for k instruction cycles                | 1             | 1              | None                     |

# TABLE 24-2: INSTRUCTION SET OVERVIEW (CONTINUED)

# 26.1 DC Characteristics

#### TABLE 26-1: OPERATING MIPS vs. VOLTAGE

|                | Voo Bango                                            | Temp Range      | Max MIPS                                                       |  |  |

|----------------|------------------------------------------------------|-----------------|----------------------------------------------------------------|--|--|

| Characteristic | haracteristic VDD Range Temp Ra<br>(in Volts) (in °C |                 | dsPIC33FJ16(GP/MC)101/102 and<br>dsPIC33FJ32(GP/MC)101/102/104 |  |  |

| DC5            | VBOR-3.6V <sup>(1)</sup>                             | -40°C to +85°C  | 16                                                             |  |  |

|                | VBOR-3.6V <sup>(1)</sup>                             | -40°C to +125°C | 16                                                             |  |  |

**Note 1:** Overall functional device operation at VBOR < VDD < VDDMIN is ensured but not characterized. All device analog modules, such as the ADC, etc., will function but with degraded performance below VDDMIN.

### TABLE 26-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min | Тур         | Max  | Unit |

|---------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| Industrial Temperature Devices                                                              |        |     |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40 | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40 | —           | +85  | °C   |

| Extended Temperature Devices                                                                |        |     |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40 | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40 |             | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     |     | PINT + PIC  | )    | W    |

| I/O Pin Power Dissipation:<br>I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)     |        |     |             |      |      |

| Maximum Allowed Power Dissipation                                                           | PDMAX  | (   | TJ — TA)/θJ | IA   | W    |

#### TABLE 26-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                   | Symbol | Тур  | Max | Unit | Notes |

|--------------------------------------------------|--------|------|-----|------|-------|

| Package Thermal Resistance, 18-pin PDIP          | θJA    | 50   | _   | °C/W | 1     |

| Package Thermal Resistance, 20-pin PDIP          | θJA    | 50   | —   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SPDIP         | θJA    | 50   | —   | °C/W | 1     |

| Package Thermal Resistance, 18-pin SOIC          | θJA    | 63   | —   | °C/W | 1     |

| Package Thermal Resistance, 20-pin SOIC          | θJA    | 63   | —   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SOIC          | θJA    | 55   | —   | °C/W | 1     |

| Package Thermal Resistance, 20-pin SSOP          | θJA    | 90   | —   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SSOP          | θJA    | 71   | —   | °C/W | 1     |

| Package Thermal Resistance, 28-pin QFN (6x6 mm)  | θJA    | 37   | _   | °C/W | 1     |

| Package Thermal Resistance, 36-pin VTLA (5x5 mm) | θJA    | 31.1 | —   | °C/W | 1     |

| Package Thermal Resistance, 44-pin TQFP          | θJA    | 45   | —   | °C/W | 1, 2  |

| Package Thermal Resistance, 44-pin QFN           | θJA    | 32   | —   | °C/W | 1, 2  |

| Package Thermal Resistance, 44-pin VTLA          | θJA    | 30   | —   | °C/W | 1, 2  |

**Note 1:** Junction to ambient thermal resistance; Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

2: This package is available in dsPIC33FJ32(GP/MC)104 devices only.

# TABLE 26-44:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ32(GP/MC)10X

| AC CHARACTERISTICS |                       |                                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                                      |

|--------------------|-----------------------|--------------------------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP70               | TscP                  | Maximum SCKx Input Frequency                                 | —                                                     | _                  | 11  | MHz   | See Note 3                           |

| SP72               | TscF                  | SCKx Input Fall Time                                         | —                                                     |                    |     | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP73               | TscR                  | SCKx Input Rise Time                                         | —                                                     |                    | _   | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                   | —                                                     | _                  | _   | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                   | —                                                     |                    | -   | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                     | 6                  | 20  | ns    |                                      |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                    |                    |     | ns    |                                      |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                    | _                  |     | ns    |                                      |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                    | _                  | _   | ns    |                                      |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                   | —                  | —   | ns    |                                      |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10                                                    | —                  | 50  | ns    | See Note 4                           |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40                                          | _                  | _   | ns    | See Note 4                           |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

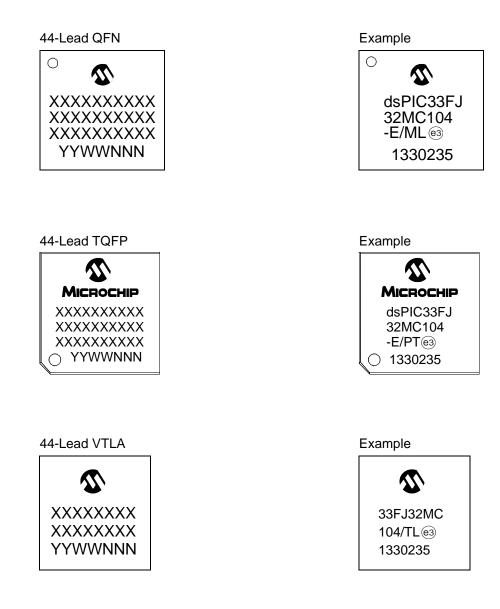

# 28.1 Package Marking Information (Continued)

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

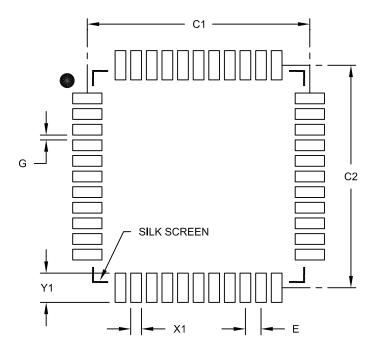

# RECOMMENDED LAND PATTERN

|                          | Ν      | /ILLIMETER | S     |      |

|--------------------------|--------|------------|-------|------|

| Dimension                | Limits | MIN        | NOM   | MAX  |

| Contact Pitch            |        | 0.80 BSC   |       |      |

| Contact Pad Spacing      | C1     |            | 11.40 |      |

| Contact Pad Spacing      |        |            | 11.40 |      |

| Contact Pad Width (X44)  |        |            |       | 0.55 |

| Contact Pad Length (X44) |        |            |       | 1.50 |

| Distance Between Pads    | G      | 0.25       |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

# APPENDIX A: REVISION HISTORY

# **Revision A (January 2011)**

This is the initial released version of the document.

# **Revision B (February 2011)**

All major changes are referenced by their respective section in Table A-1.

In addition, minor text and formatting changes were incorporated throughout the document.

| TABLE A-1: | MAJOR SECTION UPDATES |  |

|------------|-----------------------|--|

|            | - · · ·               |  |

| Section Name                                                          | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Performance, Ultra Low Cost 16-bit<br>Digital Signal Controllers | <ul> <li>Pin diagram updates (see "Pin Diagrams"):</li> <li>20-pin PDIP/SOIC/SSOP (dsPIC33FJ16MC101):<br/>Removed the FLTB1 pin from pin 10</li> <li>28-pin SPDIP/SOIC/SSOP (dsPIC33FJ16MC102):<br/>Relocated the FLTB1 pin from pin 12 to pin 14;<br/>relocated the FLTA1 pin from pin 16 to pin 15</li> <li>28-pin QFN (dsPIC33FJ16MC102):<br/>Relocated the FLTA1 pin from pin 13 to pin 12;<br/>relocated the FLTB1 pin from pin 9 to pin 11</li> </ul> |

|                                                                       | <ul> <li>36-pin TLA (dsPIC33FJ16MC102):<br/>Relocated the FLTA1 pin from pin 17 to pin 16;<br/>relocated the FLTB1 pin from pin 10 to pin 15</li> </ul>                                                                                                                                                                                                                                                                                                     |

| Section 1.0 "Device Overview"                                         | Added Notes 1, 2, and 3 regarding the FLTA1 and FLTB1 pins to the Pinout I/O Descriptions (see Table 1-1).<br>Added <b>Section</b> "".                                                                                                                                                                                                                                                                                                                      |

| Section 4.0 "Memory Organization"                                     | Updated All Resets value for PxFLTACON and PxFLTABCON to the<br>6-Output PWM1 Register Map (see Table 4-9).<br>Added Note 1 to the PMD Register Map (see Table 4-29).                                                                                                                                                                                                                                                                                       |

| Section 6.0 "Resets"                                                  | Removed Reset timing sequence information from <b>Section 6.2</b><br>" <b>System Reset</b> ", as this information is provided in Figure 6-2.                                                                                                                                                                                                                                                                                                                |

| Section 15.0 "Motor Control PWM Module"                               | Added Note 2 and Note 3 regarding the FLTA1 and FLTB1 pins to the<br>6-channel PWM Module Block Diagram (see Figure 15-1).<br>Added Section 15.2 "PWM Faults" and Section 15.3 "Write-<br>protected Registers".<br>Added Note 2 and Note 3 regarding the FLTA1 and FLTB1 pins to the<br>note boxes located below the PxFLTACON and PxFLTBCON<br>registers (see Register 15-9 and Register 15-10).                                                           |

| Section 17.0 "Inter-Integrated Circuit™<br>(I <sup>2</sup> C™)"       | Updated the descriptions for the conditional If STREN = 1 and If STREN = 0 statements for the SCLREL bit in the I2Cx Control Register (see Register 17-1).                                                                                                                                                                                                                                                                                                  |

| Section 23.0 "Special Features"                                       | Added the RTSP Effect column to the dsPIC33F Configuration Bits Description (see Table 23-3).                                                                                                                                                                                                                                                                                                                                                               |

| Section 26.0 "Electrical Characteristics"                             | Added Parameters 300 and D305 (see Table 26-42 and Table 26-43).                                                                                                                                                                                                                                                                                                                                                                                            |

| Section 27.0 "Packaging Information"                                  | Modified the pending TLA packaging page.                                                                                                                                                                                                                                                                                                                                                                                                                    |

© 2011-2014 Microchip Technology Inc.

# **Revision D (April 2012)**

This revision includes updates in support of the following new devices:

- dsPIC33FJ32GP101

- dsPIC33FJ32GP102

- dsPIC33FJ32GP104

- dsPIC33FJ32MC101

- dsPIC33FJ32MC102

- dsPIC33FJ32MC104

#### TABLE A-3: MAJOR SECTION UPDATES

Also, where applicable, new sections were added to peripheral chapters that provide information and links to the related resources, as well as helpful tips. For examples, see Section 18.1 "UART Helpful Tips" and Section 18.2 "UART Resources".

This revision includes text and formatting changes that were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-3.

| Section Name                                                                                 | Update Description                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|